# E·XFL

## Intel - EPM7032AETC44-10N Datasheet

Welcome to E-XFL.COM

## Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

## Applications of Embedded - CPLDs

## Details

| Product Status                  | Obsolete                                                     |

|---------------------------------|--------------------------------------------------------------|

| Programmable Type               | In System Programmable                                       |

| Delay Time tpd(1) Max           | 10 ns                                                        |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                    |

| Number of Logic Elements/Blocks | 2                                                            |

| Number of Macrocells            | 32                                                           |

| Number of Gates                 | 600                                                          |

| Number of I/O                   | 36                                                           |

| Operating Temperature           | 0°C ~ 70°C (TA)                                              |

| Mounting Type                   | Surface Mount                                                |

| Package / Case                  | 44-TQFP                                                      |

| Supplier Device Package         | 44-TQFP (10x10)                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm7032aetc44-10n |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Functional Description

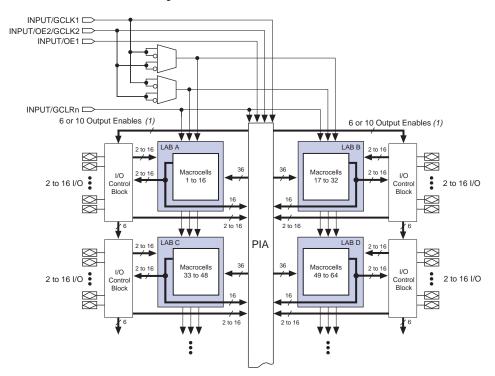

The MAX 7000A architecture includes the following elements:

- Logic array blocks (LABs)

- Macrocells

- Expander product terms (shareable and parallel)

- Programmable interconnect array

- I/O control blocks

The MAX 7000A architecture includes four dedicated inputs that can be used as general-purpose inputs or as high-speed, global control signals (clock, clear, and two output enable signals) for each macrocell and I/O pin. Figure 1 shows the architecture of MAX 7000A devices.

Figure 1. MAX 7000A Device Block Diagram

#### Note:

(1) EPM7032AE, EPM7064AE, EPM7128A, EPM7128AE, EPM7256A, and EPM7256AE devices have six output enables. EPM7512AE devices have 10 output enables.

## Logic Array Blocks

The MAX 7000A device architecture is based on the linking of high-performance LABs. LABs consist of 16-macrocell arrays, as shown in Figure 1. Multiple LABs are linked together via the PIA, a global bus that is fed by all dedicated input pins, I/O pins, and macrocells.

Each LAB is fed by the following signals:

- **3**6 signals from the PIA that are used for general logic inputs

- Global controls that are used for secondary register functions

- Direct input paths from I/O pins to the registers that are used for fast setup times

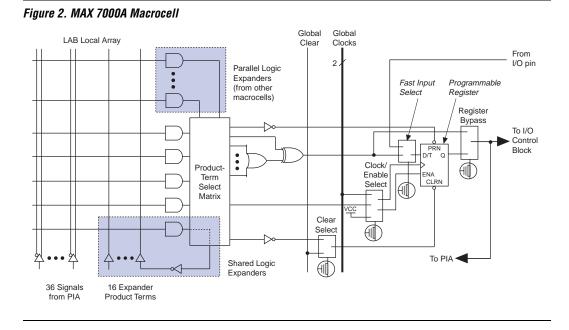

## Macrocells

MAX 7000A macrocells can be individually configured for either sequential or combinatorial logic operation. The macrocells consist of three functional blocks: the logic array, the product-term select matrix, and the programmable register. Figure 2 shows a MAX 7000A macrocell.

Combinatorial logic is implemented in the logic array, which provides five product terms per macrocell. The product-term select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as secondary inputs to the macrocell's register preset, clock, and clock enable control functions.

Two kinds of expander product terms ("expanders") are available to supplement macrocell logic resources:

- Shareable expanders, which are inverted product terms that are fed back into the logic array

- Parallel expanders, which are product terms borrowed from adjacent macrocells

The Altera development system automatically optimizes product-term allocation according to the logic requirements of the design.

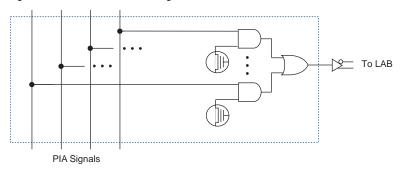

Figure 5. MAX 7000A PIA Routing

While the routing delays of channel-based routing schemes in masked or FPGAs are cumulative, variable, and path-dependent, the MAX 7000A PIA has a predictable delay. The PIA makes a design's timing performance easy to predict.

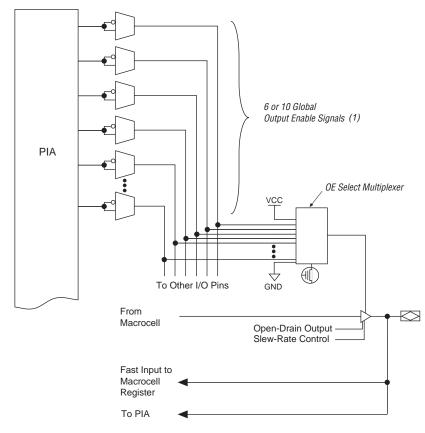

## I/O Control Blocks

The I/O control block allows each I/O pin to be individually configured for input, output, or bidirectional operation. All I/O pins have a tri-state buffer that is individually controlled by one of the global output enable signals or directly connected to ground or  $V_{CC}$ . Figure 6 shows the I/O control block for MAX 7000A devices. The I/O control block has 6 or 10 global output enable signals that are driven by the true or complement of two output enable signals, a subset of the I/O pins, or a subset of the I/O macrocells.

Figure 6. I/O Control Block of MAX 7000A Devices

#### Note:

(1) EPM7032AE, EPM7064AE, EPM7128A, EPM7128AE, EPM7256A, and EPM7256AE devices have six output enable signals. EPM7512AE devices have 10 output enable signals.

When the tri-state buffer control is connected to ground, the output is tri-stated (high impedance) and the I/O pin can be used as a dedicated input. When the tri-state buffer control is connected to  $V_{CC}$ , the output is enabled.

The MAX 7000A architecture provides dual I/O feedback, in which macrocell and pin feedbacks are independent. When an I/O pin is configured as an input, the associated macrocell can be used for buried logic.

| Device              |        | f <sub>TCK</sub> |       |       |         |         |         |        |   |  |  |  |

|---------------------|--------|------------------|-------|-------|---------|---------|---------|--------|---|--|--|--|

|                     | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |   |  |  |  |

| EPM7032AE           | 0.00   | 0.01             | 0.01  | 0.02  | 0.04    | 0.09    | 0.18    | 0.36   | s |  |  |  |

| EPM7064AE           | 0.01   | 0.01             | 0.02  | 0.04  | 0.07    | 0.18    | 0.35    | 0.70   | S |  |  |  |

| EPM7128AE           | 0.01   | 0.02             | 0.04  | 0.07  | 0.14    | 0.34    | 0.68    | 1.36   | S |  |  |  |

| EPM7256AE           | 0.02   | 0.03             | 0.08  | 0.15  | 0.30    | 0.75    | 1.49    | 2.98   | S |  |  |  |

| EPM7512AE           | 0.03   | 0.06             | 0.15  | 0.30  | 0.60    | 1.49    | 2.97    | 5.94   | S |  |  |  |

| EPM7128A <i>(1)</i> | 0.08   | 0.14             | 0.29  | 0.56  | 1.09    | 2.67    | 5.31    | 10.59  | S |  |  |  |

| EPM7256A (1)        | 0.13   | 0.24             | 0.54  | 1.06  | 2.08    | 5.15    | 10.27   | 20.51  | S |  |  |  |

#### Note to tables:

(1) EPM7128A and EPM7256A devices can only be programmed with an adaptive algorithm; users programming these two devices on platforms that cannot use an adaptive algorithm should use EPM7128AE and EPM7256AE devices.

## Programming with External Hardware

MAX 7000A devices can be programmed on Windows-based PCs with an Altera Logic Programmer card, the MPU, and the appropriate device adapter. The MPU performs continuity checks to ensure adequate electrical contact between the adapter and the device.

For more information, see the Altera Programming Hardware Data Sheet.

The Altera software can use text- or waveform-format test vectors created with the Altera Text Editor or Waveform Editor to test the programmed device. For added design verification, designers can perform functional testing to compare the functional device behavior with the results of simulation.

Data I/O, BP Microsystems, and other programming hardware manufacturers provide programming support for Altera devices.

For more information, see *Programming Hardware Manufacturers*.

## IEEE Std. 1149.1 (JTAG) **Boundary-Scan** Support

MAX 7000A devices include the JTAG BST circuitry defined by IEEE Std. 1149.1. Table 8 describes the JTAG instructions supported by MAX 7000A devices. The pin-out tables, available from the Altera web site (http://www.altera.com), show the location of the JTAG control pins for each device. If the JTAG interface is not required, the JTAG pins are available as user I/O pins.

| Power<br>Sequencing &<br>Hot-Socketing | Because MAX 7000A devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The $\rm V_{CCIO}$ and $\rm V_{CCINT}$ power planes can be powered in any order.                                                                                                                                                                                                                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | Signals can be driven into MAX 7000AE devices before and during power-<br>up (and power-down) without damaging the device. Additionally,<br>MAX 7000AE devices do not drive out during power-up. Once operating<br>conditions are reached, MAX 7000AE devices operate as specified by the<br>user.                                                                                                                                                                       |

|                                        | MAX 7000AE device I/O pins will not source or sink more than 300 $\mu A$ of DC current during power-up. All pins can be driven up to 5.75 V during hot-socketing, except the OE1 and GLCRn pins. The OE1 and GLCRn pins can be driven up to 3.6 V during hot-socketing. After V <sub>CCINT</sub> and V <sub>CCIO</sub> reach the recommended operating conditions, these two pins are 5.0-V tolerant.                                                                    |

|                                        | EPM7128A and EPM7256A devices do not support hot-socketing and may drive out during power-up.                                                                                                                                                                                                                                                                                                                                                                            |

| Design Security                        | All MAX 7000A devices contain a programmable security bit that controls access to the data programmed into the device. When this bit is programmed, a design implemented in the device cannot be copied or retrieved. This feature provides a high level of design security because programmed data within EEPROM cells is invisible. The security bit that controls this function, as well as all other programmed data, is reset only when the device is reprogrammed. |

| Generic Testing                        | MAX 7000A devices are fully tested. Complete testing of each<br>programmable EEPROM bit and all internal logic elements ensures 100%<br>programming yield. AC test measurements are taken under conditions<br>equivalent to those shown in Figure 9. Test patterns can be used and then<br>erased during early stages of the production flow.                                                                                                                            |

VCC

To Test

System

C1 (includes jig

Ŧ

capacitance)

#### Figure 9. MAX 7000A AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests 703 Ω [521 Ω] *≶* must not be performed under AC conditions. Large-amplitude, fast-ground-Device Output current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between 586 Ω [481 Ω] *≥* the device ground pin and the test system ground, significant reductions in Device input observable noise immunity can result. rise and fall Numbers in brackets are for 2.5-V times < 2 ns outputs. Numbers without brackets are for 3.3-V outputs.

## Operating Conditions

Tables 13 through 16 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for MAX 7000A devices.

| Table 1          | Table 13. MAX 7000A Device Absolute Maximum Ratings Note (1) |                                                        |      |      |      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------|--------------------------------------------------------|------|------|------|--|--|--|--|--|--|

| Symbol           | Parameter                                                    | Conditions                                             | Min  | Max  | Unit |  |  |  |  |  |  |

| V <sub>CC</sub>  | Supply voltage                                               | With respect to ground (2)                             | -0.5 | 4.6  | V    |  |  |  |  |  |  |

| VI               | DC input voltage                                             |                                                        | -2.0 | 5.75 | V    |  |  |  |  |  |  |

| I <sub>OUT</sub> | DC output current, per pin                                   |                                                        | -25  | 25   | mA   |  |  |  |  |  |  |

| T <sub>STG</sub> | Storage temperature                                          | No bias                                                | -65  | 150  | °C   |  |  |  |  |  |  |

| T <sub>A</sub>   | Ambient temperature                                          | Under bias                                             | -65  | 135  | °C   |  |  |  |  |  |  |

| Τ <sub>J</sub>   | Junction temperature                                         | BGA, FineLine BGA, PQFP, and TQFP packages, under bias |      | 135  | °C   |  |  |  |  |  |  |

| Table 1            | 4. MAX 7000A Device Recomm                          | ended Operating Conditions |      |                   |      |

|--------------------|-----------------------------------------------------|----------------------------|------|-------------------|------|

| Symbol             | Parameter                                           | Conditions                 | Min  | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (13)                  | 3.0  | 3.6               | V    |

| V <sub>CCIO</sub>  | Supply voltage for output drivers, 3.3-V operation  | (3)                        | 3.0  | 3.6               | V    |

|                    | Supply voltage for output drivers, 2.5-V operation  | (3)                        | 2.3  | 2.7               | V    |

| V <sub>CCISP</sub> | Supply voltage during in-<br>system programming     |                            | 3.0  | 3.6               | V    |

| VI                 | Input voltage                                       | (4)                        | -0.5 | 5.75              | V    |

| Vo                 | Output voltage                                      |                            | 0    | V <sub>CCIO</sub> | V    |

| T <sub>A</sub>     | Ambient temperature                                 | Commercial range           | 0    | 70                | °C   |

|                    |                                                     | Industrial range (5)       | -40  | 85                | °C   |

| TJ                 | Junction temperature                                | Commercial range           | 0    | 90                | °C   |

|                    |                                                     | Industrial range (5)       | -40  | 105               | °C   |

|                    |                                                     | Extended range (5)         | -40  | 130               | °C   |

| t <sub>R</sub>     | Input rise time                                     |                            |      | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                            |      | 40                | ns   |

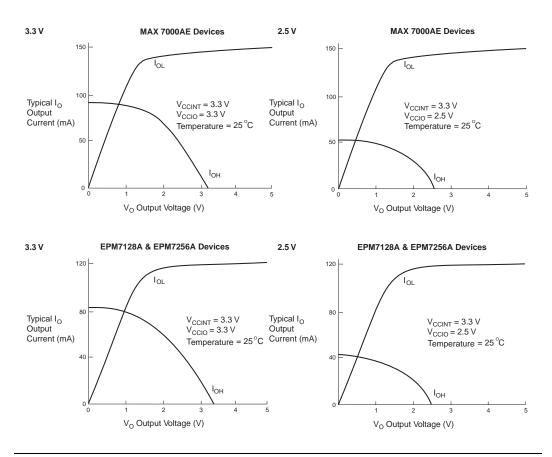

Figure 10 shows the typical output drive characteristics of MAX 7000A devices.

## **Timing Model**

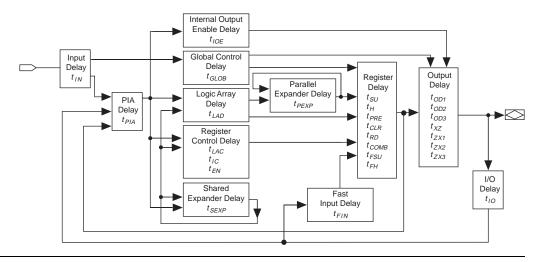

MAX 7000A device timing can be analyzed with the Altera software, a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 11. MAX 7000A devices have predictable internal delays that enable the designer to determine the worst-case timing of any design. The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

Figure 11. MAX 7000A Timing Model

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays, can be calculated as the sum of internal parameters. Figure 12 shows the timing relationship between internal and external delay parameters.

See *Application Note 94 (Understanding MAX 7000 Timing)* for more information.

| Symbol            | Parameter                                                                                   | Conditions        |     |     | Speed | Grade |     |      | Unit |

|-------------------|---------------------------------------------------------------------------------------------|-------------------|-----|-----|-------|-------|-----|------|------|

|                   |                                                                                             |                   | -   | 4   | -     | 7     | -10 |      |      |

|                   |                                                                                             |                   | Min | Max | Min   | Max   | Min | Max  |      |

| t <sub>IN</sub>   | Input pad and buffer delay                                                                  |                   |     | 0.7 |       | 1.2   |     | 1.5  | ns   |

| t <sub>IO</sub>   | I/O input pad and buffer delay                                                              |                   |     | 0.7 |       | 1.2   |     | 1.5  | ns   |

| t <sub>FIN</sub>  | Fast input delay                                                                            |                   |     | 2.3 |       | 2.8   |     | 3.4  | ns   |

| t <sub>SEXP</sub> | Shared expander delay                                                                       |                   |     | 1.9 |       | 3.1   |     | 4.0  | ns   |

| t <sub>PEXP</sub> | Parallel expander delay                                                                     |                   |     | 0.5 |       | 0.8   |     | 1.0  | ns   |

| t <sub>LAD</sub>  | Logic array delay                                                                           |                   |     | 1.5 |       | 2.5   |     | 3.3  | ns   |

| t <sub>LAC</sub>  | Logic control array delay                                                                   |                   |     | 0.6 |       | 1.0   |     | 1.2  | ns   |

| t <sub>IOE</sub>  | Internal output enable delay                                                                |                   |     | 0.0 |       | 0.0   |     | 0.0  | ns   |

| t <sub>OD1</sub>  | Output buffer and pad delay, slow slew rate = off $V_{CCIO} = 3.3 V$                        | C1 = 35 pF        |     | 0.8 |       | 1.3   |     | 1.8  | ns   |

| t <sub>OD2</sub>  | Output buffer and pad delay, slow slew rate = off $V_{CCIO} = 2.5 V$                        | C1 = 35 pF<br>(5) |     | 1.3 |       | 1.8   |     | 2.3  | ns   |

| t <sub>OD3</sub>  | Output buffer and pad<br>delay, slow slew rate = on<br>$V_{CCIO} = 2.5 V \text{ or } 3.3 V$ | C1 = 35 pF        |     | 5.8 |       | 6.3   |     | 6.8  | ns   |

| t <sub>ZX1</sub>  | Output buffer enable delay,<br>slow slew rate = off<br>$V_{CCIO} = 3.3 V$                   | C1 = 35 pF        |     | 4.0 |       | 4.0   |     | 5.0  | ns   |

| t <sub>ZX2</sub>  | Output buffer enable delay,<br>slow slew rate = off<br>$V_{CCIO} = 2.5 V$                   | C1 = 35 pF<br>(5) |     | 4.5 |       | 4.5   |     | 5.5  | ns   |

| t <sub>ZX3</sub>  | Output buffer enable delay,<br>slow slew rate = on<br>$V_{CCIO} = 3.3 V$                    | C1 = 35 pF        |     | 9.0 |       | 9.0   |     | 10.0 | ns   |

| t <sub>XZ</sub>   | Output buffer disable delay                                                                 | C1 = 5 pF         |     | 4.0 |       | 4.0   |     | 5.0  | ns   |

| t <sub>SU</sub>   | Register setup time                                                                         |                   | 1.3 |     | 2.0   |       | 2.8 |      | ns   |

| t <sub>H</sub>    | Register hold time                                                                          |                   | 0.6 |     | 1.0   |       | 1.3 |      | ns   |

| t <sub>FSU</sub>  | Register setup time of fast input                                                           |                   | 1.0 |     | 1.5   |       | 1.5 |      | ns   |

| t <sub>FH</sub>   | Register hold time of fast input                                                            |                   | 1.5 |     | 1.5   |       | 1.5 |      | ns   |

| t <sub>RD</sub>   | Register delay                                                                              |                   |     | 0.7 |       | 1.2   |     | 1.5  | ns   |

| t <sub>COMB</sub> | Combinatorial delay                                                                         |                   |     | 0.6 |       | 1.0   |     | 1.3  | ns   |

| Symbol            | Parameter                                                                             | Conditions        |     |     | Speed | Grade |     |      | Unit |

|-------------------|---------------------------------------------------------------------------------------|-------------------|-----|-----|-------|-------|-----|------|------|

|                   |                                                                                       |                   | -   | 4   | -7    |       | -10 |      |      |

|                   |                                                                                       |                   | Min | Max | Min   | Max   | Min | Max  |      |

| t <sub>IN</sub>   | Input pad and buffer delay                                                            |                   |     | 0.6 |       | 1.1   |     | 1.4  | ns   |

| t <sub>IO</sub>   | I/O input pad and buffer delay                                                        |                   |     | 0.6 |       | 1.1   |     | 1.4  | ns   |

| t <sub>FIN</sub>  | Fast input delay                                                                      |                   |     | 2.5 |       | 3.0   |     | 3.7  | ns   |

| t <sub>SEXP</sub> | Shared expander delay                                                                 |                   |     | 1.8 |       | 3.0   |     | 3.9  | ns   |

| t <sub>PEXP</sub> | Parallel expander delay                                                               |                   |     | 0.4 |       | 0.7   |     | 0.9  | ns   |

| t <sub>LAD</sub>  | Logic array delay                                                                     |                   |     | 1.5 |       | 2.5   |     | 3.2  | ns   |

| t <sub>LAC</sub>  | Logic control array delay                                                             |                   |     | 0.6 |       | 1.0   |     | 1.2  | ns   |

| t <sub>IOE</sub>  | Internal output enable delay                                                          |                   |     | 0.0 |       | 0.0   |     | 0.0  | ns   |

| t <sub>OD1</sub>  | Output buffer and pad delay, slow slew rate = off $V_{CCIO} = 3.3 V$                  | C1 = 35 pF        |     | 0.8 |       | 1.3   |     | 1.8  | ns   |

| t <sub>OD2</sub>  | Output buffer and pad delay, slow slew rate = off $V_{CCIO} = 2.5 V$                  | C1 = 35 pF<br>(5) |     | 1.3 |       | 1.8   |     | 2.3  | ns   |

| t <sub>OD3</sub>  | Output buffer and pad delay, slow slew rate = on $V_{CCIO} = 2.5 V \text{ or } 3.3 V$ | C1 = 35 pF        |     | 5.8 |       | 6.3   |     | 6.8  | ns   |

| t <sub>ZX1</sub>  | Output buffer enable delay,<br>slow slew rate = off<br>$V_{CCIO} = 3.3 V$             | C1 = 35 pF        |     | 4.0 |       | 4.0   |     | 5.0  | ns   |

| t <sub>ZX2</sub>  | Output buffer enable delay,<br>slow slew rate = off<br>$V_{CCIO} = 2.5 V$             | C1 = 35 pF<br>(5) |     | 4.5 |       | 4.5   |     | 5.5  | ns   |

| t <sub>ZX3</sub>  | Output buffer enable delay,<br>slow slew rate = on<br>$V_{CCIO} = 3.3 V$              | C1 = 35 pF        |     | 9.0 |       | 9.0   |     | 10.0 | ns   |

| t <sub>XZ</sub>   | Output buffer disable delay                                                           | C1 = 5 pF         |     | 4.0 |       | 4.0   |     | 5.0  | ns   |

| t <sub>SU</sub>   | Register setup time                                                                   |                   | 1.3 |     | 2.0   |       | 2.9 |      | ns   |

| t <sub>H</sub>    | Register hold time                                                                    |                   | 0.6 |     | 1.0   |       | 1.3 |      | ns   |

| t <sub>FSU</sub>  | Register setup time of fast input                                                     |                   | 1.0 |     | 1.5   |       | 1.5 |      | ns   |

| t <sub>FH</sub>   | Register hold time of fast input                                                      |                   | 1.5 |     | 1.5   |       | 1.5 |      | ns   |

| t <sub>RD</sub>   | Register delay                                                                        |                   |     | 0.7 |       | 1.2   |     | 1.6  | ns   |

| t <sub>COMB</sub> | Combinatorial delay                                                                   |                   |     | 0.6 |       | 0.9   |     | 1.3  | ns   |

| t <sub>IC</sub>   | Array clock delay                                                                     |                   |     | 1.2 |       | 1.9   |     | 2.5  | ns   |

Altera Corporation

| Symbol            | Parameter                                 | Conditions        | Speed Grade |     |       |     |      |      |     |  |

|-------------------|-------------------------------------------|-------------------|-------------|-----|-------|-----|------|------|-----|--|

|                   |                                           |                   |             | 5   | -     | 7   | -1   | 1    |     |  |

|                   |                                           |                   | Min         | Max | Min   | Max | Min  | Max  |     |  |

| t <sub>PD1</sub>  | Input to non-<br>registered output        | C1 = 35 pF<br>(2) |             | 5.0 |       | 7.5 |      | 10   | ns  |  |

| t <sub>PD2</sub>  | I/O input to non-<br>registered output    | C1 = 35 pF<br>(2) |             | 5.0 |       | 7.5 |      | 10   | ns  |  |

| t <sub>SU</sub>   | Global clock setup time                   | (2)               | 3.3         |     | 4.9   |     | 6.6  |      | ns  |  |

| t <sub>H</sub>    | Global clock hold time                    | (2)               | 0.0         |     | 0.0   |     | 0.0  |      | ns  |  |

| t <sub>FSU</sub>  | Global clock setup<br>time of fast input  |                   | 2.5         |     | 3.0   |     | 3.0  |      | ns  |  |

| t <sub>FH</sub>   | Global clock hold time<br>of fast input   |                   | 0.0         |     | 0.0   |     | 0.0  |      | ns  |  |

| t <sub>CO1</sub>  | Global clock to output delay              | C1 = 35 pF        | 1.0         | 3.4 | 1.0   | 5.0 | 1.0  | 6.6  | ns  |  |

| t <sub>CH</sub>   | Global clock high time                    |                   | 2.0         |     | 3.0   |     | 4.0  |      | ns  |  |

| t <sub>CL</sub>   | Global clock low time                     |                   | 2.0         |     | 3.0   |     | 4.0  |      | ns  |  |

| t <sub>ASU</sub>  | Array clock setup time                    | (2)               | 1.8         |     | 2.8   |     | 3.8  |      | ns  |  |

| t <sub>AH</sub>   | Array clock hold time                     | (2)               | 0.2         |     | 0.3   |     | 0.4  |      | ns  |  |

| t <sub>ACO1</sub> | Array clock to output delay               | C1 = 35 pF<br>(2) | 1.0         | 4.9 | 1.0   | 7.1 | 1.0  | 9.4  | ns  |  |

| t <sub>ACH</sub>  | Array clock high time                     |                   | 2.0         |     | 3.0   |     | 4.0  |      | ns  |  |

| t <sub>ACL</sub>  | Array clock low time                      |                   | 2.0         |     | 3.0   |     | 4.0  |      | ns  |  |

| t <sub>CPPW</sub> | Minimum pulse width for clear and preset  | (3)               | 2.0         |     | 3.0   |     | 4.0  |      | ns  |  |

| t <sub>CNT</sub>  | Minimum global clock<br>period            | (2)               |             | 5.2 |       | 7.7 |      | 10.2 | ns  |  |

| fcnt              | Maximum internal global clock frequency   | (2), (4)          | 192.3       |     | 129.9 |     | 98.0 |      | MHz |  |

| t <sub>acnt</sub> | Minimum array clock<br>period             | (2)               |             | 5.2 |       | 7.7 |      | 10.2 | ns  |  |

| f <sub>acnt</sub> | Maximum internal<br>array clock frequency | (2), (4)          | 192.3       |     | 129.9 |     | 98.0 |      | MHz |  |

E

| Table 22. EPM7128AE Internal Timing Parameters (Part 2 of 2) Note (1) |                      |            |             |     |       |     |     |     |    |  |

|-----------------------------------------------------------------------|----------------------|------------|-------------|-----|-------|-----|-----|-----|----|--|

| Symbol                                                                | Parameter            | Conditions | Speed Grade |     |       |     |     |     |    |  |

|                                                                       |                      |            | -5 -7 -10   |     | -5 -7 |     |     | 10  |    |  |

|                                                                       |                      |            | Min         | Max | Min   | Max | Min | Max |    |  |

| t <sub>EN</sub>                                                       | Register enable time |            |             | 0.7 |       | 1.0 |     | 1.3 | ns |  |

| t <sub>GLOB</sub>                                                     | Global control delay |            |             | 1.1 |       | 1.6 |     | 2.0 | ns |  |

| t <sub>PRE</sub>                                                      | Register preset time |            |             | 1.4 |       | 2.0 |     | 2.7 | ns |  |

| t <sub>CLR</sub>                                                      | Register clear time  |            |             | 1.4 |       | 2.0 |     | 2.7 | ns |  |

| t <sub>PIA</sub>                                                      | PIA delay            | (2)        |             | 1.4 |       | 2.0 |     | 2.6 | ns |  |

| t <sub>LPA</sub>                                                      | Low-power adder      | (6)        |             | 4.0 |       | 4.0 |     | 5.0 | ns |  |

| Symbol            | Parameter                                   | Conditions        | Speed Grade |     |       |     |      |      |      |      |     |

|-------------------|---------------------------------------------|-------------------|-------------|-----|-------|-----|------|------|------|------|-----|

|                   |                                             |                   | -           | 6   | -     | 7   | -10  |      | -12  |      | 1   |

|                   |                                             |                   | Min         | Max | Min   | Max | Min  | Мах  | Min  | Max  |     |

| t <sub>PD1</sub>  | Input to non-registered output              | C1 = 35 pF<br>(2) |             | 6.0 |       | 7.5 |      | 10.0 |      | 12.0 | ns  |

| t <sub>PD2</sub>  | I/O input to non-<br>registered output      | C1 = 35 pF<br>(2) |             | 6.0 |       | 7.5 |      | 10.0 |      | 12.0 | ns  |

| t <sub>SU</sub>   | Global clock setup time                     | (2)               | 4.2         |     | 5.3   |     | 7.0  |      | 8.5  |      | ns  |

| t <sub>H</sub>    | Global clock hold time                      | (2)               | 0.0         |     | 0.0   |     | 0.0  |      | 0.0  |      | ns  |

| t <sub>FSU</sub>  | Global clock setup time<br>of fast input    |                   | 2.5         |     | 3.0   |     | 3.0  |      | 3.0  |      | ns  |

| t <sub>FH</sub>   | Global clock hold time of<br>fast input     |                   | 0.0         |     | 0.0   |     | 0.0  |      | 0.0  |      | ns  |

| t <sub>CO1</sub>  | Global clock to output delay                | C1 = 35 pF        | 1.0         | 3.7 | 1.0   | 4.6 | 1.0  | 6.1  | 1.0  | 7.3  | ns  |

| t <sub>CH</sub>   | Global clock high time                      |                   | 3.0         |     | 3.0   |     | 4.0  |      | 5.0  |      | ns  |

| t <sub>CL</sub>   | Global clock low time                       |                   | 3.0         |     | 3.0   |     | 4.0  |      | 5.0  |      | ns  |

| t <sub>ASU</sub>  | Array clock setup time                      | (2)               | 1.9         |     | 2.4   |     | 3.1  |      | 3.8  |      | ns  |

| t <sub>AH</sub>   | Array clock hold time                       | (2)               | 1.5         |     | 2.2   |     | 3.3  |      | 4.3  |      | ns  |

| t <sub>ACO1</sub> | Array clock to output delay                 | C1 = 35 pF<br>(2) | 1.0         | 6.0 | 1.0   | 7.5 | 1.0  | 10.0 | 1.0  | 12.0 | ns  |

| t <sub>ACH</sub>  | Array clock high time                       |                   | 3.0         |     | 3.0   |     | 4.0  |      | 5.0  |      | ns  |

| t <sub>ACL</sub>  | Array clock low time                        |                   | 3.0         |     | 3.0   |     | 4.0  |      | 5.0  |      | ns  |

| t <sub>CPPW</sub> | Minimum pulse width for<br>clear and preset | (3)               | 3.0         |     | 3.0   |     | 4.0  |      | 5.0  |      | ns  |

| t <sub>CNT</sub>  | Minimum global clock<br>period              | (2)               |             | 6.9 |       | 8.6 |      | 11.5 |      | 13.8 | ns  |

| f <sub>CNT</sub>  | Maximum internal global<br>clock frequency  | (2), (4)          | 144.9       |     | 116.3 |     | 87.0 |      | 72.5 |      | MHz |

| t <sub>acnt</sub> | Minimum array clock<br>period               | (2)               |             | 6.9 |       | 8.6 |      | 11.5 |      | 13.8 | ns  |

| f <sub>acnt</sub> | Maximum internal array<br>clock frequency   | (2), (4)          | 144.9       |     | 116.3 |     | 87   |      | 72.5 |      | MHz |

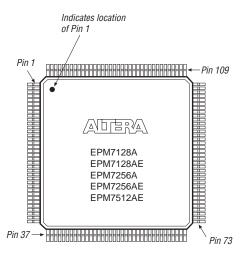

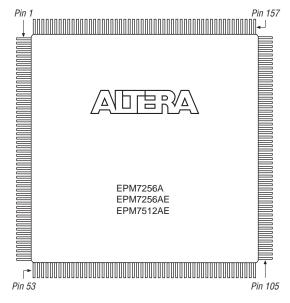

#### Figure 19. 144-Pin TQFP Package Pin-Out Diagram

Package outline not drawn to scale.

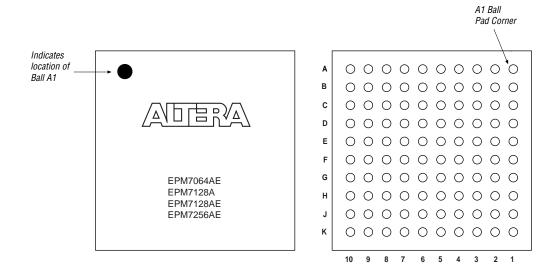

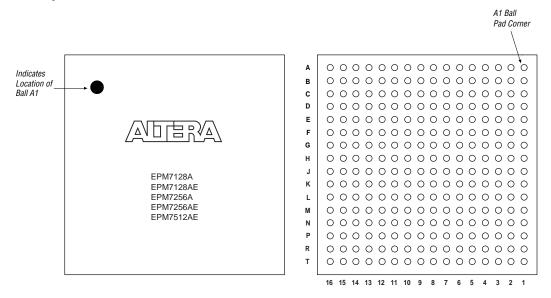

Figure 20. 169-Pin Ultra FineLine BGA Package Pin-Out Diagram

Package outline not drawn to scale.

## Figure 21. 208-Pin PQFP Package Pin-Out Diagram

Package outline not drawn to scale.

Figure 23. 256-Pin FineLine BGA Package Pin-Out Diagram

Package outline not drawn to scale.

## Revision History

The information contained in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.5 supersedes information published in previous versions.

## Version 4.5

The following changes were made in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.5:

■ Updated text in the "Power Sequencing & Hot-Socketing" section.

## Version 4.4

The following changes were made in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.4:

- Added Tables 5 through 7.

- Added "Programming Sequence" on page 17 and "Programming Times" on page 18.

## Version 4.3

The following changes were made in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.3:

- Added extended temperature devices to document

- Updated Table 14.

## Version 4.2

The following changes were made in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.2:

- Removed *Note* (1) from Table 2.

- Removed *Note* (4) from Tables 3 and 4.

## Version 4.1

The following changes were made in the *MAX 7000A Programmable Logic Device Data Sheet* version 4.1:

- Updated leakage current information in Table 15.

- Updated Note (9) of Table 15.

- Updated *Note* (1) of Tables 17 through 30.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_req@altera.com Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera valtera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. **Ex. EN ISO 9001**

101 111 100 000.

Altera Corporation