Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 8-Core                                                |

| Speed                      | 1000MIPS                                                     |

| Connectivity               | USB                                                          |

| Peripherals                | <u>.</u>                                                     |

| Number of I/O              | 27                                                           |

| Program Memory Size        | -                                                            |

| Program Memory Type        | ROMIess                                                      |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128K × 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                 |

| Data Converters            | <u> </u>                                                     |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu208-128-qf48-i10 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1      | xCORE Multicore Microcontrollers    | 2   |

|--------|-------------------------------------|-----|

| 2      | XU208-128-QF48 Features             | 4   |

| 3      |                                     | 5   |

| 4      |                                     | 6   |

| 5      | Example Application Diagram         | 8   |

| 6      | Product Overview                    |     |

| 7      | PLL                                 |     |

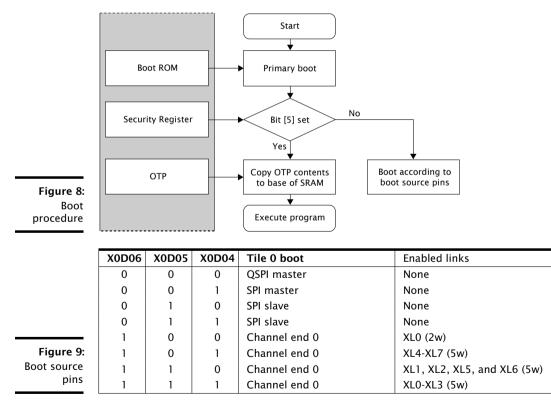

| 8      | Boot Procedure                      |     |

| 9      | Memory                              |     |

| 10     | USB PHY                             |     |

| 11     | JTAG                                |     |

| 12     | Board Integration                   |     |

| 13     | DC and Switching Characteristics    |     |

| 14     | Package Information                 |     |

| 15     | Ordering Information                |     |

| Ann    | endices                             |     |

| Α      | Configuration of the XU208-128-QF48 | g   |

| B      | Processor Status Configuration      |     |

| č      | Tile Configuration                  | , Z |

| D      | Node Configuration                  |     |

| F      | USB Node Configuration              |     |

| Ē      | USB PHY Configuration               |     |

| Ġ      | JTAG, xSCOPE and Debugging          |     |

| н      | Schematics Design Check List        |     |

| 200    | PCB Layout Design Check List        |     |

| 1      | Associated Design Documentation     |     |

| Г<br>Г | Related Documentation               |     |

|        |                                     |     |

| L      | Revision History                    | 4   |

### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 4 Signal Description

This section lists the signals and I/O pins available on the XU208-128-QF48. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- PD/PU: The IO pin has a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled. This resistor is designed to ensure defined logic input state for unconnected pins. It should not be used to pull external circuitry. Note that the resistors are highly non-linear and only a maximum pull current is specified in Section 13.2.

- ST: The IO pin has a Schmitt Trigger on its input.

- ▶ IO: the pin is powered from VDDIO

|           | Power pins (2      | 7)   |            |

|-----------|--------------------|------|------------|

| Signal    | Function           | Туре | Properties |

| GND       | Digital ground     | GND  |            |

| OTP_VCC   | OTP power supply   | PWR  |            |

| PLL_AVDD  | Analog PLL power   | PWR  |            |

| USB_VDD   | Digital tile power | PWR  |            |

| USB_VDD33 | USB Analog power   | PWR  |            |

| VDD       | Digital tile power | PWR  |            |

| VDDIO     | Digital I/O power  | PWR  |            |

|        | JTAG pins (5)      |        |            |  |  |  |  |

|--------|--------------------|--------|------------|--|--|--|--|

| Signal | Function           | Туре   | Properties |  |  |  |  |

| RST_N  | Global reset input | Input  | IO, PU, ST |  |  |  |  |

| ТСК    | Test clock         | Input  | IO, PD, ST |  |  |  |  |

| TDI    | Test data input    | Input  | IO, PU     |  |  |  |  |

| TDO    | Test data output   | Output | IO, PD     |  |  |  |  |

| TMS    | Test mode select   | Input  | IO, PU     |  |  |  |  |

| I/O pins (27) |                  |                 |                 |                  |                   |      |            |

|---------------|------------------|-----------------|-----------------|------------------|-------------------|------|------------|

| Signal        | Function         |                 |                 |                  |                   | Type | Properties |

| X0D00         | 1A <sup>0</sup>  |                 |                 |                  |                   | I/0  | IO, PD     |

| X0D01         | 1 B <sup>0</sup> |                 |                 |                  |                   | I/0  | IO, PD     |

| X0D04         | 4                | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup> | 32A <sup>22</sup> | I/0  | IO, PD     |

| X0D05         | 4                | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup> | 32A <sup>23</sup> | I/0  | IO, PD     |

| X0D06         | 4                | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup> | 32A <sup>24</sup> | I/0  | IO, PD     |

| X0D07         | 4                | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup> | 32A <sup>25</sup> | I/0  | IO, PD     |

| X0D10         | 1C <sup>0</sup>  |                 |                 |                  |                   | I/0  | IO, PD     |

| X0D11         | 1 D <sup>0</sup> |                 |                 |                  |                   | I/0  | IO, PD     |

| X0D14         | 4                | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup> | 32A <sup>28</sup> | I/0  | IO, PD     |

-XM()S

XS2-U8A-128-QF48

6

If the USB PHY is used, then either a 24 MHz or 12 MHz oscillator must be used.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the xCORE-200 Clock Frequency Control document.

## 8 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins have a pull-down enabled. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After 15-150  $\mu$ s (depending on the input clock) the processor boots.

The xCORE Tile boot procedure is illustrated in Figure 8. If bit 5 of the security register (*see* §9.1) is set, the device boots from OTP. To get a high value, a 3K3 pull-up resistor should be strapped onto the pin. To assure a low value, a pull-down resistor is required if other external devices are connected to this port.

The boot image has the following format:

- ► A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

### 8.1 Boot from QSPI master

If set to boot from QSPI master, the processor enables the six pins specified in Figure 10, and drives the SPI clock at 50 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

|                         | Pin        | Signal | Description  |

|-------------------------|------------|--------|--------------|

|                         | X0D01      | SS     | Slave Select |

| Figure 10:<br>QSPI pins | X0D04X0D07 | SPIO   | Data         |

|                         | X0D10      | SCLK   | Clock        |

The xCORE Tile expects each byte to be transferred with the *least-significant nibble first*. Programmers who write bytes into an QSPI interface using the most significant nibble first may have to reverse the nibbles in each byte of the image stored in the QSPI device.

The pins used for QSPI boot are hardcoded in the boot ROM and cannot be changed. If required, an QSPI boot program can be burned into OTP that uses different pins.

### 8.2 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 11, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

|            | Pin   | Signal | Description                |

|------------|-------|--------|----------------------------|

|            | X0D00 | MISO   | Master In Slave Out (Data) |

| Figure 11: | X0D01 | SS     | Slave Select               |

| SPI master | X0D10 | SCLK   | Clock                      |

| pins       | X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant

# 13 DC and Switching Characteristics

| Symbol   | Parameter                                     | MIN   | TYP  | MAX   | UNITS | Notes |

|----------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD      | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIO    | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| USB_VDD  | USB tile DC supply voltage                    | 0.95  | 1.00 | 1.05  | V     |       |

| VDD33    | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance            |       |      | 25    | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|          | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Tj       | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg     | Storage temperature                           | -65   |      | 150   | °C    |       |

## 13.1 Operating Conditions

Figure 20: Operating conditions

## 13.2 DC Characteristics, VDDIO=3V3

| Symbol | Parameter                                | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|------------------------------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage                       | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage                        | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage                      | 2.20  |     |      | V     | B, C  |

| V(OL)  | Output low voltage                       |       |     | 0.40 | V     | B, C  |

| I(PU)  | Internal pull-up current (Vin=0V)        | -100  |     |      | μA    | D     |

| I(PD)  | Internal pull-down current<br>(Vin=3.3V) |       |     | 100  | μA    | D     |

| I(LC)  | Input leakage current                    | -10   |     | 10   | μA    |       |

Figure 21: DC characteristics

A All pins except power supply pins.

B All general-purpose I/Os are nominal 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

-XMOS

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry. In order to pull the pin to the opposite state, a 4K7 resistor is recommended to overome the internal pull current.

## 13.5 Power Consumption

| Symbol     | Parameter              | MIN | TYP  | MAX | UNITS   | Notes      |

|------------|------------------------|-----|------|-----|---------|------------|

| I(DDCQ)    | Quiescent VDD current  |     | 45   |     | mA      | A, B, C    |

| PD         | Tile power dissipation |     | 325  |     | µW/MIPS | A, D, E, F |

| IDD        | Active VDD current     |     | 170  | 375 | mA      | A, G, H    |

| I(ADDPLL)  | PLL_AVDD current       |     | 5    | 7   | mA      | I          |

| I(VDD33)   | VDD33 current          |     | 26.7 |     | mA      | J          |

| I(USB_VDD) | USB_VDD current        |     | 8.27 |     | mA      | К          |

Figure 25: xCORE Tile currents

A Use for budgetary purposes only.

- B Assumes typical tile and I/O voltages with no switching activity.

- C Includes PLL current.

- D Assumes typical tile and I/O voltages with nominal switching activity.

- E Assumes 1 MHz = 1 MIPS.

- F PD(TYP) value is the usage power consumption under typical operating conditions.

- G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25  $^\circ C$ , 500 MHz, average device resource usage.

- H Typical application and conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, USB Audio stereo out @ 192 kHz.

- I PLL\_AVDD = 1.0 V

- J HS mode transmitting while driving all 0's data (constant JKJK on DP/DM). Loading of 10 pF. Transfers do not include any interpacket delay.

- K HS receive mode; no traffic.

Figure 26: Clock The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

More detailed power analysis can be found in the XS1-U Power Consumption document,

### 13.6 Clock

| Symbol | Parameter                 | MIN  | TYP | MAX | UNITS | Notes |

|--------|---------------------------|------|-----|-----|-------|-------|

| f      | Frequency                 | 9    | 24  | 25  | MHz   |       |

| SR     | Slew rate                 | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)  |      |     | 2   | %     | A     |

| f(MAX) | Processor clock frequency |      |     | 500 | MHz   | В     |

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-U Clock Frequency Control document,

A write message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | control-token |

|---------------|------------------------|-----------------|-------|---------------|

| 37            | channel-end identifier | register number | size  | 1             |

The response to the read message comprises either control token 3, data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number                                   | Perm                                   | Description                           |

|------------------------------------------|----------------------------------------|---------------------------------------|

| 0x00                                     | RW                                     | RAM base address                      |

| 0x01                                     | RW                                     | Vector base address                   |

| 0x02                                     | RW                                     | xCORE Tile control                    |

| 0x03                                     | RO                                     | xCORE Tile boot status                |

| 0x05                                     | RW                                     | Security configuration                |

| 0x06                                     | RW                                     | Ring Oscillator Control               |

| 0x07                                     | RO                                     | Ring Oscillator Value                 |

| 0x08                                     | RO                                     | Ring Oscillator Value                 |

| 0x09                                     | RO                                     | Ring Oscillator Value                 |

| 0x0A                                     | RO                                     | Ring Oscillator Value                 |

| 0x0C                                     | RO                                     | RAM size                              |

| 0x10                                     | DRW                                    | Debug SSR                             |

| 0x11                                     | DRW                                    | Debug SPC                             |

| 0x12                                     | DRW                                    | Debug SSP                             |

| 0x13                                     | DRW                                    | DGETREG operand 1                     |

| 0x14 DRW                                 |                                        | DGETREG operand 2                     |

| 0x15                                     | DRW                                    | Debug interrupt type                  |

| 0x16                                     | DRW                                    | Debug interrupt data                  |

| 0x18                                     | DRW                                    | Debug core control                    |

| 0x20 0x27                                | DRW                                    | Debug scratch                         |

| 0x30 0x33                                | DRW                                    | Instruction breakpoint address        |

| 0x40 0x43                                | DRW                                    | Instruction breakpoint control        |

| 0x50 0x53                                | DRW                                    | Data watchpoint address 1             |

| 0x60 0x63                                | DRW                                    | Data watchpoint address 2             |

| 0x70 0x73 DRW Data breakpoint control re |                                        | Data breakpoint control register      |

| 0x80 0x83                                | x80 0x83 DRW Resources breakpoint mask |                                       |

| 0x90 0x93                                | DRW                                    | Resources breakpoint value            |

| 0x9C 0x9F                                | DRW                                    | Resources breakpoint control register |

-XMOS

Figure 33:

Summary

XS2-U8A-128-QF48

| Bits  | Perm | Init | Description                                                                                                                                                                                                                               |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                                |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1     |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                       |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock<br>divider is enabled. In dynamic mode the clock divider is only<br>activated when all active threads are paused. In static mode the<br>clock divider is always enabled. |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                    |

| 3     | RO   | -    | Reserved                                                                                                                                                                                                                                  |

| 2     | RW   |      | Select between UTMI (1) and ULPI (0) mode.                                                                                                                                                                                                |

| 1     | RW   |      | Enable the ULPI Hardware support module                                                                                                                                                                                                   |

| 0     | RO   | -    | Reserved                                                                                                                                                                                                                                  |

0x02: xCORE Tile control

# B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS<sup>®</sup>

| Bits  | Perm | Init | Description                                               |

|-------|------|------|-----------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                  |

| 23:16 | RO   |      | Processor number.                                         |

| 15:9  | RO   | -    | Reserved                                                  |

| 8     | RO   |      | Overwrite BOOT_MODE.                                      |

| 7:6   | RO   | -    | Reserved                                                  |

| 5     | RO   |      | Indicates if core1 has been powered off                   |

| 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| 3     | RO   |      | Boot ROM boots from RAM                                   |

| 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03: xCORE Tile boot status

| 0x07:<br>Ring | Bits  | Perm | Init | Description                   |

|---------------|-------|------|------|-------------------------------|

| Oscillator    | 31:16 | RO   | -    | Reserved                      |

| Value         | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08** Ring Oscillator Value

| 08:<br>ing | Bits  | Perm | Init | Description                   |

|------------|-------|------|------|-------------------------------|

| tor        | 31:16 | RO   | -    | Reserved                      |

| lue        | 15:0  | RO   | 0    | Ring oscillator Counter data. |

### B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

**0x09:** Ring Oscillator Value

| : | Bits  | Perm | Init | Description                   |

|---|-------|------|------|-------------------------------|

|   | 31:16 | RO   | -    | Reserved                      |

|   | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A:** Ring Oscillator Value

| A:      | Bits  | Perm | Init | Description                   |

|---------|-------|------|------|-------------------------------|

| g<br>or | 31:16 | RO   | -    | Reserved                      |

| e       | 15:0  | RO   | 0    | Ring oscillator Counter data. |

-XMOS

### B.11 RAM size: 0x0C

The size of the RAM in bytes

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

## **B.15 DGETREG operand 1: 0x13**

The resource ID of the logical core whose state is to be read.

| 0x13:     | Bits | Perm | Init | Description              |

|-----------|------|------|------|--------------------------|

| DGETREG   | 31:8 | RO   | -    | Reserved                 |

| operand 1 | 7:0  | DRW  |      | Thread number to be read |

### B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

## B.17 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of =HOST=).                                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |

0x15: Debug interrupt type

0x30 .. 0x33: Instruction breakpoint address

| ction<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| dress          | 31:0 | DRW  |      | Value.      |

# B.22 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

|         | Bits  | Perm | Init | Description                                                                                              |

|---------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|         | 31:24 | RO   | -    | Reserved                                                                                                 |

|         | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 3:      | 15:2  | RO   | -    | Reserved                                                                                                 |

| n<br>nt | 1     | DRW  | 0    | When 0 break when PC == IBREAK_ADDR. When 1 = break when PC != IBREAK_ADDR.                              |

| ol      | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

0x40 .. 0x43 Instruction breakpoint control

## B.23 Data watchpoint address 1: 0x50 .. 0x53

This set of registers contains the first address for the four data watchpoints.

| <b>0x50 0x53:</b><br>Data<br>watchpoint |      |      |      |             |

|-----------------------------------------|------|------|------|-------------|

| watchpoint                              | Bits | Perm | Init | Description |

| address 1                               | 31:0 | DRW  |      | Value.      |

## B.24 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

| <b>0x60 0x63:</b><br>Data<br>watchpoint |      |      |      |             |

|-----------------------------------------|------|------|------|-------------|

|                                         | Bits | Perm | Init | Description |

| address 2                               | 31:0 | DRW  |      | Value.      |

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | CRO  | Device identification                          |

| 0x01      | CRO  | xCORE Tile description 1                       |

| 0x02      | CRO  | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | CRW  | xCORE Tile clock divider                       |

| 0x07      | CRO  | Security configuration                         |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | CRO  | PC of logical core 0                           |

| 0x41      | CRO  | PC of logical core 1                           |

| 0x42      | CRO  | PC of logical core 2                           |

| 0x43      | CRO  | PC of logical core 3                           |

| 0x44      | CRO  | PC of logical core 4                           |

| 0x45      | CRO  | PC of logical core 5                           |

| 0x46      | CRO  | PC of logical core 6                           |

| 0x47      | CRO  | PC of logical core 7                           |

| 0x60      | CRO  | SR of logical core 0                           |

| 0x61      | CRO  | SR of logical core 1                           |

| 0x62      | CRO  | SR of logical core 2                           |

| 0x63      | CRO  | SR of logical core 3                           |

| 0x64      | CRO  | SR of logical core 4                           |

| 0x65      | CRO  | SR of logical core 5                           |

| 0x66      | CRO  | SR of logical core 6                           |

| 0x67      | CRO  | SR of logical core 7                           |

Figure 34: Summary

# C.1 Device identification: 0x00

This register identifies the xCORE Tile

-XMOS<sup>®</sup>

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

## C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

0x05: Cause debug interrupts

|     | Bits | Perm | Init | Description                                 |

|-----|------|------|------|---------------------------------------------|

|     | 31:2 | RO   | -    | Reserved                                    |

| · ( | 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

|     | 0    | CRW  | 0    | Request a debug interrupt on the processor. |

## C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |  |

|-------|------|------|---------------------------------------------------------------|--|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |  |

| 30:16 | RO   | -    | Reserved                                                      |  |

| 15:0  | CRW  | 0    | Clock divider.                                                |  |

# C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

-XMOS

# **D** Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x09      | R    | System JTAG device ID register        |

| 0x0A      | R    | System USERCODE register              |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | Reserved                              |

| 0x11      | RW   | Reserved.                             |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x28 | RW   | Link status, direction, and network   |

| 0x40 0x47 | RO   | PLink status and network              |

| 0x80 0x88 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 35: Summary

## D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|                        | Bits  | Perm | Init | Description                                       |

|------------------------|-------|------|------|---------------------------------------------------|

|                        | 31:24 | RO   | -    | Reserved                                          |

| <b>0x00:</b><br>Device | 23:16 | RO   |      | Sampled values of BootCtl pins on Power On Reset. |

|                        | 15:8  | RO   |      | SSwitch revision.                                 |

| tification             | 7:0   | RO   |      | SSwitch version.                                  |

-XMOS<sup>®</sup>

identi

## D.8 System JTAG device ID register: 0x09

**0x09**: System JTAG device ID register

|         | Bits  | Perm | Init | Description |

|---------|-------|------|------|-------------|

| -       | 31:28 | RO   |      |             |

| 9:<br>G | 27:12 | RO   |      |             |

| D       | 11:1  | RO   |      |             |

| er      | 0     | RO   |      |             |

## D.9 System USERCODE register: 0x0A

**0x0A** System USERCODE register

| <b>4:</b><br>n | Bits  | Perm | Init | Description                                |

|----------------|-------|------|------|--------------------------------------------|

| E              | 31:18 | RO   |      | JTAG USERCODE value programmed into OTP SR |

| er             | 17:0  | RO   |      | metal fixable ID code                      |

## D.10 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                     |  |

|-------|------|------|-------------------------------------------------|--|

| 31:28 | RW   | 0    | The direction for packets whose dimension is 7. |  |

| 27:24 | RW   | 0    | The direction for packets whose dimension is 6. |  |

| 23:20 | RW   | 0    | The direction for packets whose dimension is 5. |  |

| 19:16 | RW   | 0    | The direction for packets whose dimension is 4. |  |

| 15:12 | RW   | 0    | The direction for packets whose dimension is 3. |  |

| 11:8  | RW   | 0    | The direction for packets whose dimension is 2. |  |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 1. |  |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 0. |  |

0x0C: Directions 0-7

### D.11 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

# D.18 Static link configuration: 0xA0 .. 0xA7

These registers are used for static (ie, non-routed) links. When a link is made static, all traffic is forwarded to the designated channel end and no routing is attempted. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits | Perm | Init | Description                                                                                     |

|------|------|------|-------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Enable static forwarding.                                                                       |

| 30:9 | RO   | -    | Reserved                                                                                        |

| 8    | RW   | 0    | The destination processor on this node that packets received in static mode are forwarded to.   |

| 7:5  | RO   | -    | Reserved                                                                                        |

| 4:0  | RW   | 0    | The destination channel end on this node that packets received in static mode are forwarded to. |

**0xA0 .. 0xA7:** Static link configuration

# E USB Node Configuration

The USB node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number | Perm                           | Description                       |  |

|--------|--------------------------------|-----------------------------------|--|

| 0x00   | RO                             | RO Device identification register |  |

| 0x04   | RW Node configuration register |                                   |  |

| 0x05   | RW                             | W Node identifier                 |  |

| 0x51   | RW                             | System clock frequency            |  |

| 0x80   | RW                             | Link Control and Status           |  |

Figure 36: Summary

### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

0x00: Device identification register

| Bits  | Perm | Init | Description                      |  |

|-------|------|------|----------------------------------|--|

| 31:24 | RO   | 0x0F | Chip identifier                  |  |

| 23:16 | RO   | -    | Reserved                         |  |

| 15:8  | RO   | 0x02 | Revision number of the USB block |  |

| 7:0   | RO   | 0x00 | Version number of the USB block  |  |

#### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

**0x04:** Node configuration register

|                  | Bits | Perm | Init | Description                                                                                          |  |

|------------------|------|------|------|------------------------------------------------------------------------------------------------------|--|

| <b>)4:</b><br>de | 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |  |

| on               | 30:1 | RO   | -    | Reserved                                                                                             |  |

| er               | 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |  |

|          | Bits | Perm | Init | Description                     |

|----------|------|------|------|---------------------------------|

| 0x2C:    | 31:4 | RO   | -    | Reserved                        |

| UIFM PID | 3:0  | RO   | 0    | Value of the last received PID. |

#### F.13 UIFM Endpoint: 0x30

The last endpoint seen

**0x30** UIFM Endpoint

|                 | Bits | Perm | Init | Description                           |  |

|-----------------|------|------|------|---------------------------------------|--|

| 0:              | 31:5 | RO   | -    | Reserved                              |  |

| <b>О</b> .<br>М | 4    | RO   | 0    | 1 if endpoint contains a valid value. |  |

| nt              | 3:0  | RO   | 0    | A copy of the last received endpoint. |  |

## F.14 UIFM Endpoint match: 0x34

This register can be used to mark UIFM endpoints as special.

**0x34:** UIFM Endpoint match

|   | Bits  | Perm | Init | Description                                                                                                                          |  |

|---|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| ſ | 31:16 | RO   | -    | Reserved                                                                                                                             |  |

|   | 15:0  | RW   | 0    | This register contains a bit for each endpoint. If its bit is set, the endpoint will be supplied on the RX port when ORed with 0x10. |  |

## F.15 OTG Flags mask: 0x38

**0x38**: OTG Flags mask

| 38:<br>ags | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| ask        | 31:0 | RW   | 0    | Data        |

# F.16 UIFM power signalling: 0x3C

|                   | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| 0x3C:             | 31:9 | RO   | -    | Reserved    |

| <b>UIFM</b> power | 8    | RW   | 0    | Valid       |

| signalling        | 7:0  | RW   | 0    | Data        |

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

## G.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section G.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XL0, XL1, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{in}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XL0 for xSCOPE I/O, you need to connect up XL0 ${}^{1}_{out}$ , XL0 ${}^{0}_{out}$ , XL0 ${}^{1}_{in}$ , as follows:

- XL0<sup>1</sup><sub>out</sub> (X0D43) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XL0<sup>0</sup><sub>out</sub> (X0D42) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- >  $XLO_{in}^{0}$  (X0D41) to pin 14 of the xSYS header.

- >  $XLO_{in}^{1}$  (X0D40) to pin 18 of the xSYS header.