# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 48                                                                      |

| Program Memory Size        | 60KB (60K × 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bar9tae |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin    | No.         |          |      | Le    | evel   |       |     | F   | Port |                  |                  | Main               |                     |  |

|--------|-------------|----------|------|-------|--------|-------|-----|-----|------|------------------|------------------|--------------------|---------------------|--|

| P64    | FP44        | Pin name | Type | ut    | out    |       | Inp | out |      | Out              | put              | function<br>(after | Alternate function  |  |

| LQFP64 | LQFI        |          |      | Input | Output | float | ndm | int | ana  | OD               | РР               | reset)             |                     |  |

| 62     | 1           | PE1/RDI  | I/O  | $C_T$ |        | Χ     | Х   |     |      | Х                | Х                | Port E1            | SCI Receive Data In |  |

| 63     | _(1)        | PE2      | I/O  | $C_T$ |        |       | Х   |     |      | X <sup>(6)</sup> | X <sup>(6)</sup> | Port E2            |                     |  |

| 64     | _<br>(2)(1) | PE3      | I/O  | CT    |        | x     | х   |     |      | х                | х                | Port E3            |                     |  |

#### Table 2. Device pin description (continued)

1. On the chip, each I/O port may have up to 8 pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

2. On the chip, each I/O port may have up to eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

3. It is mandatory to connect all available  $V_{DD}$  and  $V_{AREF}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

4. Not connected in 48 Kbyte and 64 Kbyte ROM devices

5. OSC1 and OSC2 pins connect a crystal/ceramic resonator or an external source to the on-chip oscillator; see Section 6.4: *Multi-oscillator (MO)* and Section 19.5: Clock and timing characteristics for more details.

6. Pull-up always activated on PE2; see limitation Section 22.1.8: Pull-up always active on PE2.

|      | Legend / Abbreviations  | s for Table 2:                                                                                   |

|------|-------------------------|--------------------------------------------------------------------------------------------------|

|      | Туре:                   | I = input<br>O = output<br>S = supply                                                            |

|      | Input level:            | A = dedicated analog input                                                                       |

|      | In/Output level:        | C = CMOS $0.3V_{DD}/0.7V_{DD}$<br>C <sub>T</sub> = CMOS $0.3V_{DD}/0.7V_{DD}$ with input trigger |

|      | Output level:           | HS = 20mA high sink (on N-buffer only)                                                           |

|      | Port and control config | juration:                                                                                        |

| solf | • Input:                | float = floating<br>wpu = weak pull-up<br>int = interrupt <sup>(a)</sup><br>ana = analog         |

| 262  | • Output:               | OD = open-drain <sup>(b)</sup><br>PP = push-pull                                                 |

b. In the open-drain output column, "T" defines a true open-drain I/O (P-Buffer and protection diode to V<sub>DD</sub> are not implemented). See *Section 9: I/O ports* and *Section 19.8: I/O port pin characteristics* for more details.

a. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, otherwise the configuration is floating interrupt input.

|     |                 | aprinapping                               |                     |                   |                                          |                   |

|-----|-----------------|-------------------------------------------|---------------------|-------------------|------------------------------------------|-------------------|

| No. | Source<br>block | Description                               | Register<br>label   | Priority<br>order | Exit<br>from<br>Halt /<br>Active<br>Halt | Address<br>vector |

|     | RESET           | Reset                                     | N/A                 |                   | yes                                      | FFFEh-FFFFh       |

|     | TRAP            | Software interrupt                        | N/A                 |                   | no                                       | FFFCh-FFFDh       |

| 0   | TLI             | External top level interrupt              | EICR                |                   | yes                                      | FFFAh-FFFBh       |

| 1   | MCC/RTC         | Main clock controller time base interrupt | MCCSR               | Higher            | yes                                      | FFF8h-FFF9h       |

| 2   | ei0             | External interrupt port A30               |                     | priority          | yes                                      | FFF6h-FFF7h       |

| 3   | ei1             | External interrupt port F20               | N/A                 | P                 | yes                                      | FFF4h-FFF5h       |

| 4   | ei2             | External interrupt port B30               | X                   | S                 | yes                                      | FFF2h-FFF3h       |

| 5   | ei3             | External interrupt port B74               | 26.                 | A                 | yes                                      | FFF0h-FFF1h       |

| 6   |                 | Not used                                  | 5                   |                   |                                          | FFEEh-FFEFh       |

| 7   | SPI             | SPI peripheral interrupts                 | SPICSR              |                   | yes <sup>(1)</sup>                       | FFECh-FFEDh       |

| 8   | TIMER A         | TIMER A peripheral interrupts             | TASR                |                   | no                                       | FFEAh-FFEBh       |

| 9   | TIMER B         | TIMER B peripheral interrupts             | TBSR                |                   | no                                       | FFE8h-FFE9h       |

| 10  | SCI             | SCI peripheral interrupts                 | SCISR               | Lower<br>priority | no                                       | FFE6h-FFE7h       |

| 11  | AVD             | Auxiliary voltage detector interrupt      | SICSR               |                   | no                                       | FFE4h-FFE5h       |

| 12  | I2C             | I2C peripheral interrupts                 | (see<br>peripheral) |                   | no                                       | FFE2h-FFE3h       |

| 13  | PWM ART         | PWM ART interrupt                         | ARTCSR              |                   | yes <sup>(2)</sup>                       | FFE0h-FFE1h       |

## Table 19. Interrupt mapping

1. Exit from HALT possible when SPI is in slave mode.

2. Exit from HALT possible when PWM ART is in external clock mode.

|      | interru | pt sensitivity - eiz (port Do) |                            |  |  |  |  |

|------|---------|--------------------------------|----------------------------|--|--|--|--|

| IS11 | IS10    | External interrupt sensitivity |                            |  |  |  |  |

| 1311 | 1310    | IPB bit = 0                    | IPB bit = 1                |  |  |  |  |

| 0    | 0       | Falling edge and low level     | Rising edge and high level |  |  |  |  |

| 0    | 1       | Rising edge only               | Falling edge only          |  |  |  |  |

| 1    | 0       | Falling edge only              | Rising edge only           |  |  |  |  |

| 1    | 1       | Rising and falling edge        |                            |  |  |  |  |

Table 21. Interrupt sensitivity - ei2 (port B3..0)

Table 22. Interrupt sensitivity - ei3 (port B7..4)

| IS11 | IS10 | External interrupt sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge and low level     |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

## Table 23. Interrupt sensitivity - ei0 (port A3..0)

| IS21 | IS20 | External interrupt sensitivity |                            |  |  |  |  |  |

|------|------|--------------------------------|----------------------------|--|--|--|--|--|

| 1321 | 1520 | IPA bit = 0                    | IPA bit = 1                |  |  |  |  |  |

| 0    | 0    | Falling edge and low level     | Rising edge and high level |  |  |  |  |  |

| 0    | 1    | Rising edge only               | Falling edge only          |  |  |  |  |  |

| 1    | 0    | Falling edge only              | Rising edge only           |  |  |  |  |  |

| 1    | 1    | Rising and falling edge        |                            |  |  |  |  |  |

#### Table 24. Interrupt sensitivity - ei1 (port F2..0)

|     | IS21 | IS20 | External interrupt sensitivity |

|-----|------|------|--------------------------------|

|     | 0    | 0    | Falling edge and low level     |

| 26  | 0    | 1    | Rising edge only               |

| SO. | 1    | 0    | Falling edge only              |

| 00- | 1    | 1    | Rising and falling edge        |

|     |      |      |                                |

| Address (Hex.)     | Register label     | 7            | 6 | 5  | 4 | 3 | 2           | 1  | 0   |

|--------------------|--------------------|--------------|---|----|---|---|-------------|----|-----|

| Reset value of all | I/O port registers | 0            | 0 | 0  | 0 | 0 | 0           | 0  | 0   |

| 0003h              | PBDR               |              |   |    |   |   |             |    |     |

| 0004h              | PBDDR              | MSB          |   |    |   |   |             |    | LSB |

| 0005h              | PBOR               |              |   |    |   |   |             |    |     |

| 0006h              | PCDR               |              |   |    |   |   |             |    |     |

| 0007h              | PCDDR              | MSB          |   |    |   |   |             |    | LSB |

| 0008h              | PCOR               |              |   |    |   |   |             | -  |     |

| 0009h              | PDDR               |              |   |    |   |   |             | 10 | 5   |

| 000Ah              | PDDDR              | MSB          |   |    |   |   | . (         |    | LSB |

| 000Bh              | PDOR               |              |   |    |   |   | $\lambda O$ |    |     |

| 000Ch              | PEDR               |              |   |    |   | 0 |             |    |     |

| 000Dh              | PEDDR              | MSB          |   |    |   |   |             |    | LSB |

| 000Eh              | PEOR               |              |   | X  | 0 |   |             |    |     |

| 000Fh              | PFDR               |              | C | 10 | - |   |             |    |     |

| 0010h              | PFDDR              | MSB          | S |    |   |   |             |    | LSB |

| 0011h              | PFOR               | $\mathbf{O}$ | P |    |   |   |             |    |     |

Table 33.

I/O port register map and reset values (continued)

### **Related documentation**

SPI Communication between ST7 and EEPROM (AN 970) S/W implementation of I2C bus master (AN1045) Software LCD driver (AN1048)

| Address (Hex.) | Register label        | 7         | 6          | 5         | 4          | 3        | 2        | 1        | 0          |

|----------------|-----------------------|-----------|------------|-----------|------------|----------|----------|----------|------------|

| 002Bh          | SICSR<br>Reset value  | AVDS<br>0 | AVDIE<br>0 | AVDF<br>0 | LVDRF<br>x | 0        | 0        | 0        | WDGRF<br>x |

| 002Ch          | MCCSR<br>Reset value  | MCO<br>0  | CP1<br>0   | CP0<br>0  | SMS<br>0   | TB1<br>0 | TB0<br>0 | OIE<br>0 | OIF<br>0   |

| 002Dh          | MCCBCR<br>Reset value | 0         | 0          | 0         | 0          | 0        | 0        | BC1<br>0 | BC0<br>0   |

| osoleta        | e Prod                | JCtl      | 5)         | 0,0       | 3018       | ie P     | , od     | uctl     | 5)         |

Table 43.

Main clock controller register map and reset values

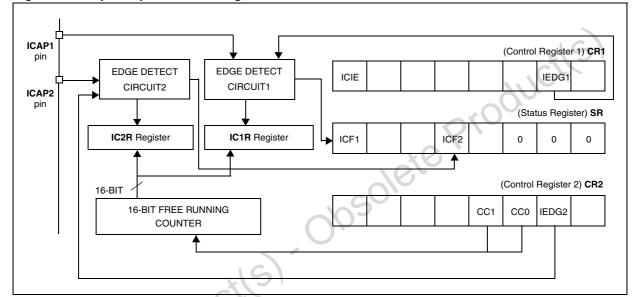

#### 13.3.3 Input capture

In this section, the index, *i*, may be 1 or 2 because there are two input capture functions in the 16-bit timer.

The two 16-bit input capture registers (IC1R and IC2R) are used to latch the value of the free running counter after a transition is detected on the ICAP*i* pin (see *Figure 46*).

|      | MS Byte        | LS Byte        |

|------|----------------|----------------|

| ICiR | IC <i>i</i> HR | IC <i>i</i> LR |

IC/R register is a read-only register.

The active transition is software programmable through the IEDG*i* bit of Control Registers (CR*i*).

Timing resolution is one count of the free running counter: (f<sub>CPU</sub>/CC[1:0]).

Procedure:

To use the input capture function select the following in the CR2 register:

- Select the timer clock (CC[1:0]) (see *Table 60: Timer clock selection*).

- Select the edge of the active transition on the ICAP2 pin with the IEDG2 bit (the ICAP2 pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

And select the following in the CR1 register:

- Set the ICIE bit to generate an interrupt after an input capture coming from either the ICAP1 pin or the ICAP2 pin

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

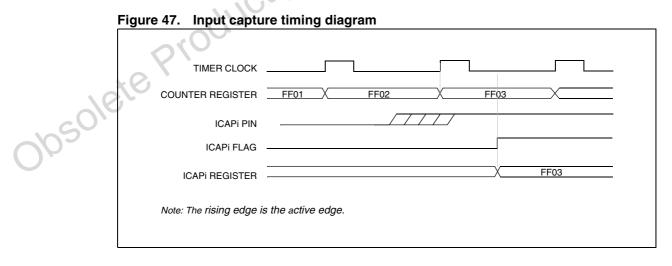

When an input capture occurs:

- ICF*i* bit is set.

- The IC*i*R register contains the value of the free running counter on the active transition on the ICAP*i* pin (see *Figure 47*).

- A timer interrupt is generated if the ICIE bit is set and the I bit is cleared in the CC register. Otherwise, the interrupt remains pending until both conditions become true.

Clearing the input capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set

- 2. An access (read or write) to the ICiLR register

Note: 1 After reading the ICiHR register, transfer of input capture data is inhibited and ICFi will never be set until the ICiLR register is also read.

- 2 The ICiR register contains the free running counter value which corresponds to the most recent input capture.

- 3 The two input capture functions can be used together even if the timer also uses the two output compare functions.

- 4 In One pulse Mode and PWM mode only Input Capture 2 can be used.

- 5 The alternate inputs (ICAP1 and ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function.

- 6 Moreover if one of the ICAPi pins is configured as an input and the second one as an output, an interrupt can be generated if the user toggles the output pin and if the ICIE bit is set.

- 7 This can be avoided if the input capture function i is disabled by reading the ICiHR (see note 1).

- 8 The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFh).

#### Figure 46. Input capture block diagram

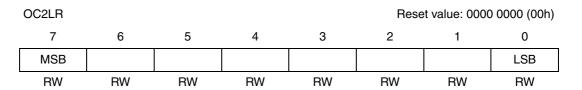

### 13.7.9 Output compare 2 low register (OC2LR)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

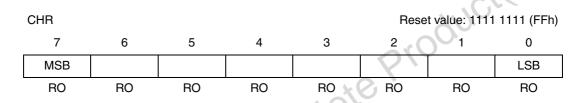

## 13.7.10 Counter high register (CHR)

This is an 8-bit register that contains the high part of the counter value.

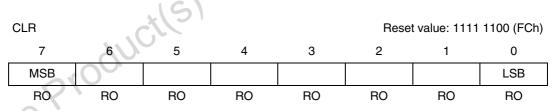

## 13.7.11 Counter low register (CLR)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

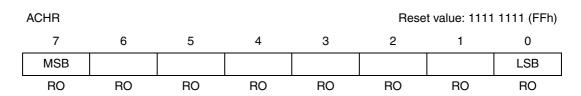

## 13.7.12 Alternate counter high register (ACHR)

This is an 8-bit register that contains the high part of the counter value.

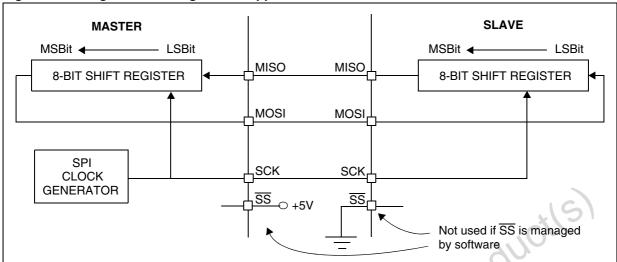

#### Figure 56. Single master/single slave application

#### 14.3.2 Slave select management

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see *Figure 58*)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$  signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode

• SS internal must be held high continuously

#### In Slave mode

There are two cases depending on the data/clock timing relationship (see Figure 57):

If CPHA = 1 (data latched on 2nd clock edge):

• SS internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM = 1 and SSI = 0 in the in the SPICSR register)

If CPHA = 0 (data latched on 1st clock edge):

• SS internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see *Write collision error (WCOL) on page 129*).

| Bit | Name     | Function                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1:0 | SPR[1:0] | Serial Clock Frequency<br>These bits are set and cleared by software. Used with the SPR2 bit, they select<br>the baud rate of the SPI serial clock SCK output by the SPI in master mode.<br>Note: These 2 bits have no effect in slave mode. |  |  |  |  |  |  |

#### **SPICR register description (continued)** Table 65.

#### Table 66. SPI master mode SCK frequency

| Serial clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    | 0    | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    | 0    | 1 DI |

| f <sub>CPU</sub> /32  | 1    | 1    | 0 0  |

| f <sub>CPU</sub> /64  | 0    | 1 0  | 0    |

| f <sub>CPU</sub> /128 | 0    | Oi   | 1    |

#### Control/status register (SPICSR) 14.8.2

|                                  | 010  |     |      | -        |      |                |              |

|----------------------------------|------|-----|------|----------|------|----------------|--------------|

| Control/status register (SPICSR) |      |     |      |          |      |                |              |

| SPICSR                           |      |     |      |          | Rese | et value: 0000 | 0 0000 (00h) |

| 7                                | 6    | 5   | 4    | 3        | 2    | 1              | 0            |

| SPIF                             | WCOL | OVR | MODF | Reserved | SOD  | SSM            | SSI          |

| RO                               | RO   | RO  | RO   | -        | RW   | RW             | RW           |

#### Table 67. SPICSR register description

|        | Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Obsole | 7   | SPIF | <ul> <li>Serial Peripheral Data Transfer Flag</li> <li>This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).</li> <li>0: Data transfer is in progress or the flag has been cleared</li> <li>1: Data transfer between the device and an external device has been completed. While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.</li> </ul> |

|        | 6   | WCOL | <ul> <li>Write Collision status</li> <li>This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see <i>Figure 60</i>).</li> <li>0: No write collision occurred.</li> <li>1: A write collision has been detected.</li> </ul>                                                                                                                                                                                                                                                                                          |

|        | 5   | OVR  | <ul> <li>SPI Overrun error</li> <li>This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see Overrun condition (OVR) on page 129). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.</li> <li>0: No overrun error</li> <li>1: Overrun error detected</li> </ul>                                                                                                                                                          |

#### 15.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### Character transmission

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see *Figure 62*).

#### Procedure

- 1. Select the M bit to define the word length.

- 2. Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- 3. Set the TE bit to assign the TDO pin to the alternate function and to send an idle frame as first transmission.

- 4. Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set.

When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

Note: The TDRE and TC bits are cleared by the same software sequence.

#### **Break characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see *Figure 63*).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this

#### Conventional baud rate generation

The baud rate for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$Tx = \frac{f_{CPU}}{(16 \cdot PR) \cdot TR} \qquad Rx = \frac{f_{CPU}}{(16 \cdot PR) \cdot RR}$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits)

TR = 1, 2, 4, 8, 16, 32, 64,128 (see SCT[2:0] bits)

RR = 1, 2, 4, 8, 16, 32, 64,128 (see SCR[2:0] bits)

All these bits are in the SCIBRR register.

Example: If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### Extended baud rate generation

The extended prescaler option provides a very fine tuning of the baud rate, using a 255 value prescaler, whereas the conventional baud rate generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 64.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCIERPR or the SCIETPR register.

Note:

Note:

The extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$\kappa = \frac{f_{CPU}}{16 \cdot ETPR \cdot (PR \cdot TR)} \qquad Rx = \frac{f_{CPU}}{16 \cdot ERPR \cdot (PR \cdot RR)}$$

with:

ETPR = 1,..,255 (see SCIETPR register)

ERPR = 1,..,255 (see SCIERPR register)

#### Receiver muting and wake-up feature

T

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non-addressed receivers.

The non-addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

- All the reception status bits cannot be set.

- All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset

- by Address Mark detection if the WAKE bit is set

| Interrupt event    | Event flag | Enable control<br>bit | Exit from<br>Wait | Exit from<br>Halt |

|--------------------|------------|-----------------------|-------------------|-------------------|

| Idle Line Detected | IDLE       | ILIE                  | Yes               | No                |

| Parity Error       | PE         | PIE                   | Yes               | No                |

#### Table 71. SCI interrupt control/wake-up capability

#### 15.7 **SCI registers**

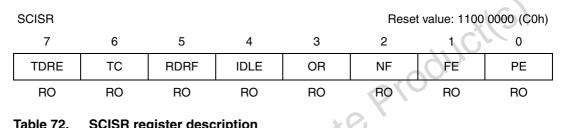

#### Status register (SCISR) 15.7.1

|        | Table | , 12. | SCISH register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Bit   | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | 7     | TDRE  | <ul> <li>Transmit data register empty</li> <li>This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Data is not transferred to the shift register</li> <li>1: Data is transferred to the shift register</li> <li>Note: Data is not transferred to the shift register unless the TDRE bit is cleared.</li> </ul> |

| obsole | 6     | тс    | <ul> <li>Transmission complete</li> <li>This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).</li> <li>0: Transmission is not complete</li> <li>1: Transmission is complete</li> <li>Note: TC is not set after the transmission of a Preamble or a Break.</li> </ul>                                                                                         |

| U.     | 5     | RDRF  | Received data ready flag<br>This bit is set by hardware when the content of the RDR register has been<br>transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2<br>register. It is cleared by a software sequence (an access to the SCISR register<br>followed by a read to the SCIDR register).<br>0: Data is not received<br>1: Received data is ready to be read                                                                                                                                                                           |

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ERPR[7:0] | <ul> <li>8-bit Extended Receive Prescaler Register</li> <li>The extended baud rate generator is activated when a value different from 00h is stored in this register. Therefore the clock frequency issued from the 16 divider (see <i>Figure 64</i>) is divided by the binary factor set in the SCIERPR register (in the range 1 to 255).</li> <li>The extended baud rate generator is not used after a reset.</li> </ul> |

#### Table 76. SCIERPR register description

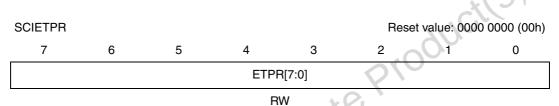

## 15.7.7 Extended transmit prescaler division register (SCIETPR)

This register allows setting of the external prescaler rate division factor for the transmit circuit.

#### Table 77. SCIETPR register description

| Bit | Name      | Function                                                                                                                                                                                                            |  |  |  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7.0 |           | 8-bit Extended Transmit Prescaler Register<br>The extended baud rate generator is activated when a value different from 00h is<br>stored in this register. Therefore the clock frequency issued from the 16 divider |  |  |  |

| 7:0 | ETPR[7:0] | (see <i>Figure 64</i> ) is divided by the binary factor set in the SCIETPR register (in the range 1 to 255).<br>The extended baud rate generator is not used after a reset.                                         |  |  |  |

#### Table 78.Baud rate selection

|   | Y.                                 |                            | Conditions       |                                |                                                                                                                                                                                                                                               |                                                                |           |      |

|---|------------------------------------|----------------------------|------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|------|

|   | Symbol                             | Parameter                  | f <sub>СРU</sub> | Accuracy<br>versus<br>standard | Prescaler                                                                                                                                                                                                                                     | Standard                                                       | Baud rate | Unit |

| O | f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication<br>frequency | 8 MHz            | ~0.16%                         | Conventional mode<br>TR (or RR) = 128, PR = 13<br>TR (or RR) = 32, PR = 13<br>TR (or RR) = 16, PR = 13<br>TR (or RR) = 8, PR = 13<br>TR (or RR) = 4, PR = 13<br>TR (or RR) = 16, PR = 3<br>TR (or RR) = 2, PR = 13<br>TR (or RR) = 1, PR = 13 | 300<br>1200<br>2400<br>4800<br>9600<br>10400<br>19200<br>38400 |           | Hz   |

|   |                                    |                            |                  | ~0.79%                         | Extended mode<br>ETPR (or ERPR) = 35,<br>TR (or RR) = 1, PR = 1                                                                                                                                                                               | 14400                                                          | ~14285.71 |      |

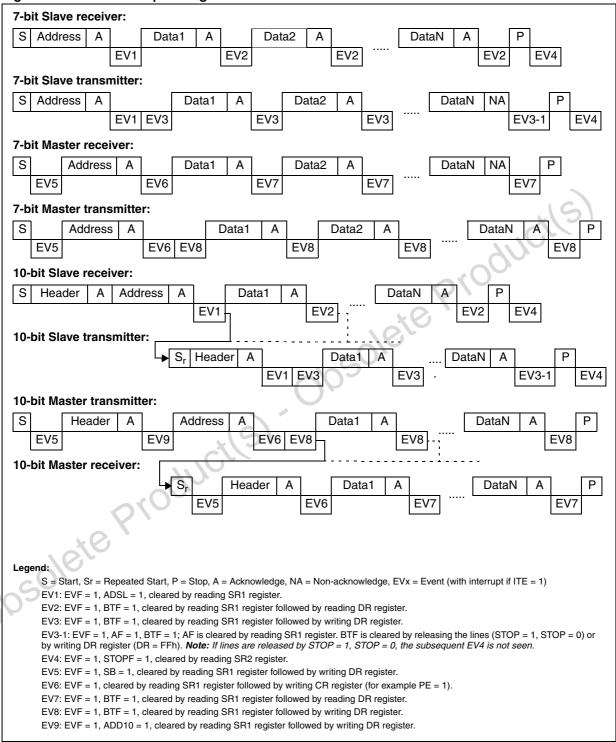

#### Error cases

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and BERR bits are set by hardware with an interrupt if ITE is set. Note that BERR will not be set if an error is detected during the first or second pulse of each 9-bit transaction:

Single Master Mode

If a Start or Stop is issued during the first or second pulse of a 9-bit transaction, the BERR flag will not be set and transfer will continue however the BUSY flag will be reset. To work around this, slave devices should issue a NACK when they receive a misplaced Start or Stop. The reception of a NACK or BUSY by the master in the middle of communication makes it possible to re-initiate transmission.

#### Multimaster Mode

Normally the BERR bit would be set whenever unauthorized transmission takes place while transfer is already in progress. However, an issue will arise if an external master generates an unauthorized Start or Stop while the I<sup>2</sup>C master is on the first or second pulse of a 9-bit transaction. It is possible to work around this by polling the BUSY bit during I<sup>2</sup>C master mode transmission. The resetting of the BUSY bit can then be handled in a similar manner as the BERR flag being set.

- **AF**: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set by hardware with an interrupt if the ITE bit is set. To resume, set the Start or Stop bit. The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

- ARLO: Detection of an arbitration lost condition. In this case the ARLO bit is set by hardware (with an interrupt if the ITE bit is set and the interface goes automatically back to slave mode (the M/SL bit is cleared).

In all these cases, the SCL line is not held low; however, the SDA line can remain low due to

possible '0' bits transmitted last. It is then necessary to release both lines by software.

Josolete

Note:

#### Figure 68. Transfer sequencing

## 16.7 Register description

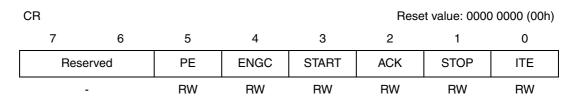

## 16.7.1 I<sup>2</sup>C control register (CR)

Table 82. CR register description

|        | Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | 7:6 | -     | Reserved. Forced to 0 by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|        | 5   | PE    | <ul> <li>Peripheral enable</li> <li>This bit is set and cleared by software.</li> <li>0: Peripheral disabled</li> <li>1: Master/Slave capability</li> <li>Notes:</li> <li>When PE = 0, all the bits of the CR register and the SR register except the Stop bit are reset. All outputs are released while PE = 0</li> <li>When PE = 1, the corresponding I/O pins are selected by hardware as alternate functions.</li> <li>To enable the I<sup>2</sup>C interface, write the CR register TWICE with PE = 1 as the first write only activates the interface (only PE is set).</li> </ul> |  |  |

|        | 4   | ENGC  | <ul> <li>Enable General Call</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0). The 00h General Call address is acknowledged (01h ignored).</li> <li>0: General Call disabled</li> <li>1: General Call enabled</li> <li>Note: In accordance with the I2C standard, when GCAL addressing is enabled, an I2C slave can only receive data. It will not transmit data to the master.</li> </ul>                                                                                                                      |  |  |

| Obsole | 3   | START | <ul> <li>Generation of a Start condition</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0) or when the Start condition is sent (with interrupt generation if ITE = 1).</li> <li>In Master mode</li> <li>0: No start generation</li> <li>1: Repeated start generation</li> <li>In Slave mode</li> <li>0: No start generation</li> <li>1: Start generation when the bus is free</li> </ul>                                                                                                                         |  |  |

|        | 2   | ACK   | <ul> <li>Acknowledge enable</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0).</li> <li>0: No acknowledge returned</li> <li>1: Acknowledge returned after an address byte or a data byte is received</li> </ul>                                                                                                                                                                                                                                                                                                  |  |  |

| Туре                    | Instruction             | Function                     |  |  |  |

|-------------------------|-------------------------|------------------------------|--|--|--|

|                         | CLR                     | Clear                        |  |  |  |

|                         | INC, DEC                | Increment/Decrement          |  |  |  |

|                         | TNZ                     | Test Negative or Zero        |  |  |  |

|                         | CPL, NEG                | 1 or 2 Complement            |  |  |  |

| Short instructions only | BSET, BRES              | Bit Operations               |  |  |  |

|                         | BTJT, BTJF              | Bit Test and Jump Operations |  |  |  |

|                         | SLL, SRL, SRA, RLC, RRC | Shift and Rotate Operations  |  |  |  |

|                         | SWAP                    | Swap Nibbles                 |  |  |  |

|                         | CALL, JP                | Call or Jump subroutine      |  |  |  |

# Table 99.Instructions supporting direct, indexed, indirect, and indirect indexed<br/>addressing modes (continued)

## **18.1.7** Relative (direct, indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

#### Table 100. Available relative direct/indirect instructions

|       | Instruction | -10 | Function         |

|-------|-------------|-----|------------------|

| JRxx  |             |     | Conditional Jump |

| CALLR | 16          |     | Call Relative    |

The relative addressing mode consists of two submodes:

## **Relative (direct)**

The offset is following the opcode.

### **Relative (indirect)**

The offset is defined in memory, which address follows the opcode.

## 18.2 Instruction groups

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may be subdivided into 13 main groups as illustrated in the following table:

#### Table 101. Instruction groups

| Group               | Instructions |     |     |  |  |  |  |

|---------------------|--------------|-----|-----|--|--|--|--|

| Load and Transfer   | LD           | CLR |     |  |  |  |  |

| Stack operation     | PUSH         | POP | RSP |  |  |  |  |

| Increment/Decrement | INC          | DEC |     |  |  |  |  |

| Compare and Tests   | СР           | TNZ | BCP |  |  |  |  |

#### External voltage detector (EVD) thresholds 19.3.4

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},\,\text{and}\,\,T_{\text{A}}.$

Table 109. External voltage detector (EVD) thresholds

| Symbol                | Parameter                                                                         | Conditions                                   | Min  | Тур  | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>IT+(EVD)</sub> | 1 $\Rightarrow$ 0 AVDF flag toggle threshold (V <sub>DD</sub> rise <sup>(1)</sup> |                                              | 1.15 | 1.26 | 1.35 | v    |

| V <sub>IT-(EVD)</sub> | $0 \Rightarrow 1 \text{ AVDF flag toggle threshold } (V_{DD} \text{ fall})^{(1)}$ |                                              | 1.1  | 1.2  | 1.3  | v    |

| V <sub>hys(EVD)</sub> | EVD voltage threshold hysteresis                                                  | V <sub>IT+(EVD)</sub> -V <sub>IT-(EVD)</sub> |      | 200  |      | mV   |

| 1. Data base          | EVD voltage threshold hysteresis                                                  | oleter                                       | 210  | 90   | oile | 5    |

|                       | O'                                                                                | pSU.                                         |      |      |      |      |

#### **Control pin characteristics** 19.9

#### Asynchronous **RESET** pin 19.9.1

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

Table 127. Asynchronous RESET pin characteristics

| Symbol                  | Parameter                                            | Conditions                        | Min                             | Тур | Max                             | Unit |

|-------------------------|------------------------------------------------------|-----------------------------------|---------------------------------|-----|---------------------------------|------|

| V <sub>IL</sub>         | Input low level voltage <sup>(1)</sup>               |                                   |                                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ |      |

| V <sub>IH</sub>         | Input high level voltage <sup>(1)</sup>              |                                   | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                                 |      |

| V <sub>hys</sub>        | Schmitt trigger voltage<br>hysteresis <sup>(2)</sup> |                                   |                                 | 2.5 | 3                               | V    |

| V <sub>OL</sub>         | Output low level voltage <sup>(3)</sup>              | $V_{DD} = 5V, I_{IO} = +2mA$      |                                 | 0.2 | 0.5                             | 1    |

| I <sub>IO</sub>         | Input current on RESET pin                           |                                   |                                 | 2   | 5                               | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor                     |                                   | 20                              | 30  | 120                             | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration                       | Stretch applied on external pulse | 0                               |     | 42 <sup>(4)</sup>               | μs   |

|                         |                                                      | Internal reset sources            | 20                              | 30  | 42 <sup>(4)</sup>               |      |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time <sup>(5)</sup>        | Je.                               | 2.5                             |     |                                 |      |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>(6)</sup>              | NSO.                              |                                 | 200 |                                 | ns   |

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 19.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ . З.

4. Data guaranteed by design, not tested in production.

- To guarantee the reset of the device, a minimum pulse has to be applied to the RESET pin. All short pulses applied on the RESET pin with a duration below to carry can be ignored 5.  $\overline{T}$  pin with a duration below  $t_{h(RSTL)in}$  can be ignored.

- 6. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments. 3050lete