Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I²C, SCI, SPI                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bj9tae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     |       | 16.7.2   | I2C status register 1 (SR1)       | 166 |

|-----|-------|----------|-----------------------------------|-----|

|     |       | 16.7.3   | I2C status register 2 (SR2)       | 168 |

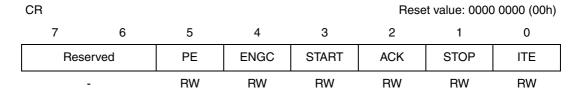

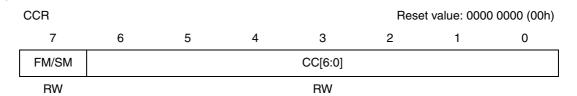

|     |       | 16.7.4   | I2C clock control register (CCR)  |     |

|     |       | 16.7.5   | I2C data register (DR)            |     |

|     |       | 16.7.6   | I2C own address register (OAR1)   |     |

|     |       | 16.7.7   | I2C own address register (OAR2)   |     |

| 17  | 10-bi | t A/D co | onverter (ADC)                    | 173 |

|     | 17.1  | Introdu  | ction                             | 173 |

|     | 17.2  | Main fe  | eatures                           | 173 |

|     | 17.3  | Functio  | onal description                  | 174 |

|     |       | 17.3.1   | A/D converter configuration       | 174 |

|     |       | 17.3.2   | Starting the conversion           | 174 |

|     |       | 17.3.3   | Starting the conversion           | 175 |

|     | 17.4  | Low po   | ower modesotsegisters             | 175 |

|     | 17.5  | Interrup | ots                               | 175 |

|     | 17.6  | ADC re   | egisters                          | 175 |

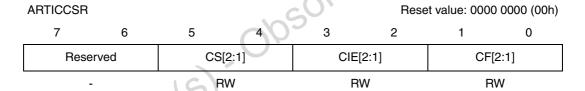

|     |       | 17.6.1   | Control/status register (ADCCSR)  |     |

|     |       | 17.6.2   | Data register (ADCDRH)            | 176 |

|     |       | 17.6.3   | Data register (ADCDRL)            | 177 |

|     |       | 17.6.4   | ADC register map and reset values | 177 |

|     |       |          | 9,0,                              |     |

| 18  | Instr |          | set                               |     |

|     | 18.1  |          | ddressing modes                   |     |

|     | Silv  | 18.1.1   | Inherent                          | 179 |

| psc |       | 18.1.2   | Immediate                         |     |

| 102 |       | 18.1.3   | Direct                            |     |

|     |       | 18.1.4   | Indexed (no offset, short, long)  | 180 |

|     |       | 18.1.5   | Indirect (short, long)            |     |

|     |       | 18.1.6   | Indirect Indexed (Short, Long)    |     |

|     |       | 18.1.7   | Relative (Direct, Indirect)       |     |

|     | 18.2  | Instruct | tion groups                       |     |

|     |       | 18.2.1   | Using a prebyte                   | 183 |

| 19  | Elect | rical ch | aracteristics                     | 186 |

|     | 19.1  | Parame   | eter conditions                   | 186 |

| Table 101. | Instruction groups                                           | 182 |

|------------|--------------------------------------------------------------|-----|

| Table 102. | Instruction set overview                                     | 184 |

| Table 103. | Voltage characteristics                                      | 187 |

| Table 104. | Current characteristics                                      | 188 |

| Table 105. | Thermal characteristics                                      |     |

| Table 106. | General operating conditions                                 | 189 |

| Table 107. | Operating conditions with low voltage detector (LVD)         | 190 |

| Table 108. | Auxiliary voltage detector (AVD) thresholds                  | 190 |

| Table 109. | External voltage detector (EVD) thresholds                   | 191 |

| Table 110. | Current consumption                                          |     |

| Table 111. | Oscillators, PLL and LVD current consumption                 | 193 |

| Table 112. | On-chip peripherals current consumption                      | 194 |

| Table 113. | General timings                                              | 195 |

| Table 114. | External clock source                                        |     |

| Table 115. | Crystal and ceramic resonator oscillators                    | 196 |

| Table 116. | OSCRANGE selection for typical resonators                    | 197 |

| Table 117. | OSCRANGE selection for typical resonators                    | 197 |

| Table 118. | PLL characteristics                                          | 199 |

| Table 119. | RAM supply voltage                                           | 200 |

| Table 120. | Dual voltage HDFlash memory                                  | 200 |

| Table 121. | EMS test results                                             | 202 |

| Table 122. | EMI emissions                                                | 202 |

| Table 123. | EMI emissions                                                | 203 |

| Table 124. | Flectrical sensitivities                                     | 203 |

| Table 125. | I/O port pin general characteristics  Output driving current | 204 |

| Table 126. | Output driving current                                       | 205 |

| Table 127. | Asynchronous RESET pin characteristics                       |     |

| Table 128. | ICCSEL/V <sub>PP</sub> pin characteristics                   |     |

| Table 129. | 8-bit PWM-ART auto-reload timer characteristics              |     |

| Table 130. | 16-bit timer characteristics                                 |     |

| Table 131. | SPI characteristics                                          |     |

| Table 132. | I <sup>2</sup> C control interface characteristics           |     |

| Table 133. | SCL frequency table                                          |     |

| Table 134. | 10-bit ADC characteristics                                   |     |

| Table 135. | ADC accuracy                                                 |     |

| Table 136. | 64-pin (14x14) low profile quad flat package mechanical data |     |

| Table 137. | 64-pin (10x10) low profile quad flat package mechanical data |     |

| Table 138. | 44-pin (10x10) low profile quad flat package mechanical data |     |

| Table 139. | Thermal characteristics                                      |     |

| Table 140. | Flash option bytes                                           |     |

| Table 141. | Option byte 0 bit description                                |     |

| Table 142. | Option byte 1 bit description                                |     |

| Table 143. | Package selection (OPT7)                                     |     |

| Table 144. | STMicroelectronics development tools                         |     |

| Table 145. | STMicroelectronics development tools                         |     |

| Table 146. | Suggested list of socket types                               |     |

| Table 147. | Document revision history                                    | 243 |

| Figure                                                                                                                                                                                                            | 49.                                                                                                                                             | Output compare timing diagram, fTIMER = fCPU/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | Output compare timing diagram, fTIMER = fCPU/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |

| Figure                                                                                                                                                                                                            | 51.                                                                                                                                             | One pulse mode cycle flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 52.                                                                                                                                             | One pulse mode timing example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 53.                                                                                                                                             | Pulse width modulation mode timing example with 2 output compare functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 54.                                                                                                                                             | Pulse width modulation cycle flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112                                                                                                                                       |

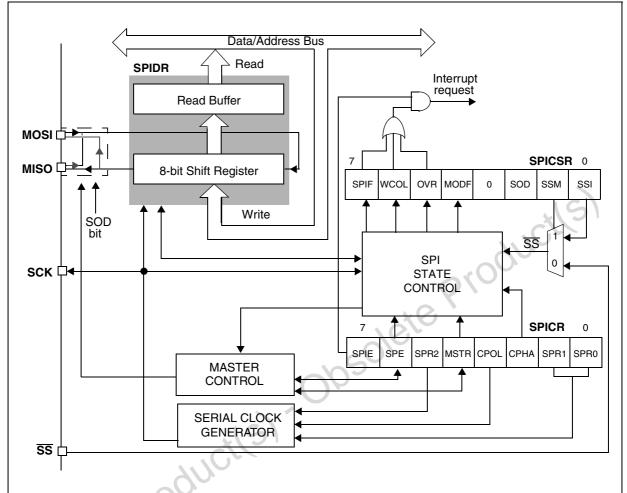

| Figure                                                                                                                                                                                                            | 55.                                                                                                                                             | Serial peripheral interface block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 56.                                                                                                                                             | Single master/single slave application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 57.                                                                                                                                             | Generic SS timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 125                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 58.                                                                                                                                             | Hardware/Software slave select management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 125                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 59.                                                                                                                                             | Data clock timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 128                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 60.                                                                                                                                             | Clearing the WCOL bit (Write Collision Flag) software sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 130                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 61.                                                                                                                                             | Single master / multiple slave configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                           |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | SCI block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                           |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | Word length programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 139                                                                                                                                       |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | SCI baud rate and extended prescaler block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 143                                                                                                                                       |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | Bit sampling in reception mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 147                                                                                                                                       |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | I2C bus protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 157                                                                                                                                       |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | I2C interface block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 158                                                                                                                                       |

| Figure                                                                                                                                                                                                            |                                                                                                                                                 | Transfer sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 163                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 69                                                                                                                                              | Interrupt control logic diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 164                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 70.                                                                                                                                             | ADC block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 173                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 71.                                                                                                                                             | Pin loading conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 186                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 72.                                                                                                                                             | ADC block diagram.  Pin loading conditions.  Pin input voltage.  f <sub>CPU</sub> max versus V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 186                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 73.                                                                                                                                             | f <sub>CPU</sub> max versus V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 189                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 74.                                                                                                                                             | Typical application with an external clock source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 195                                                                                                                                       |

|                                                                                                                                                                                                                   |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                           |

| <b>Figure</b>                                                                                                                                                                                                     | 75.                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                           |

| Figure<br>Figure                                                                                                                                                                                                  |                                                                                                                                                 | Typical application with a crystal or ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196                                                                                                                                       |

| Figure                                                                                                                                                                                                            | 76.                                                                                                                                             | Typical application with a crystal or ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196<br>197                                                                                                                                |

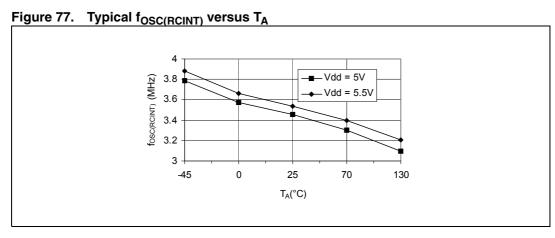

| Figure<br>Figure                                                                                                                                                                                                  | 76.<br>77.                                                                                                                                      | Typical application with a crystal or ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196<br>197<br>197                                                                                                                         |

| Figure<br>Figure<br>Figure                                                                                                                                                                                        | 76.<br>77.<br>78.                                                                                                                               | Typical application with a crystal or ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196<br>197<br>197<br>199                                                                                                                  |

| Figure<br>Figure<br>Figure<br>Figure                                                                                                                                                                              | 76.<br>77.<br>78.<br>79.                                                                                                                        | Typical application with a crystal or ceramic resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196<br>197<br>197<br>199<br>205                                                                                                           |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                                                    | 76.<br>77.<br>78.<br>79.                                                                                                                        | Typical application with a crystal or ceramic resonator.<br>Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .<br>Integrated PLL jitter versus signal frequency(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196<br>197<br>197<br>199<br>205                                                                                                           |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                                          | 76.<br>77.<br>78.<br>79.<br>80.<br>81.                                                                                                          | Typical application with a crystal or ceramic resonator.<br>Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .<br>Integrated PLL jitter versus signal frequency(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196<br>197<br>197<br>199<br>205<br>.205<br>206                                                                                            |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                                                    | 76.<br>77.<br>78.<br>79.<br>80.<br>81.                                                                                                          | Typical application with a crystal or ceramic resonator.<br>Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .<br>Integrated PLL jitter versus signal frequency(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196<br>197<br>197<br>199<br>205<br>.205<br>206<br>206                                                                                     |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                                | 76.<br>77.<br>78.<br>79.<br>80.<br>81.<br>82.                                                                                                   | Typical application with a crystal or ceramic resonator.<br>Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .<br>Integrated PLL jitter versus signal frequency(1).<br>Unused I/O pins configured as input.<br>Typical $I_{PU}$ vs $V_{DD}$ with $V_{IN} = V_{SS}$<br>Typical $V_{OL}$ at $V_{DD} = 5V$ (standard)<br>Typical $V_{OL}$ at $V_{DD} = 5V$ (high-sink)<br>Typical $V_{OH}$ at $V_{DD} = 5V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 196<br>197<br>197<br>199<br>205<br>.205<br>206<br>206<br>206                                                                              |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                      | 76.<br>77.<br>78.<br>79.<br>80.<br>81.<br>82.<br>83.                                                                                            | Typical application with a crystal or ceramic resonator.<br>Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .<br>Integrated PLL jitter versus signal frequency(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196<br>197<br>197<br>199<br>205<br>.205<br>206<br>206<br>206                                                                              |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                            | 76.<br>77.<br>78.<br>79.<br>80.<br>81.<br>82.<br>83.<br>84.                                                                                     | Typical application with a crystal or ceramic resonator.  Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .  Integrated PLL jitter versus signal frequency(1).  Unused I/O pins configured as input.  Typical $I_{PU}$ vs $V_{DD}$ with $V_{IN} = V_{SS}$ .  Typical $V_{OL}$ at $V_{DD} = 5V$ (standard).  Typical $V_{OL}$ at $V_{DD} = 5V$ (high-sink).  Typical $V_{OL}$ versus $V_{DD}$ (standard).  Typical $V_{OL}$ versus $V_{DD}$ (standard).  Typical $V_{OL}$ versus $V_{DD}$ (standard).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 196<br>197<br>197<br>199<br>205<br>.205<br>206<br>206<br>206<br>207<br>207                                                                |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                  | 76.<br>77.<br>78.<br>79.<br>80.<br>81.<br>82.<br>83.<br>84.<br>85.                                                                              | Typical application with a crystal or ceramic resonator. Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ . Integrated PLL jitter versus signal frequency(1). Unused I/O pins configured as input. Typical $I_{PU}$ vs $V_{DD}$ with $V_{IN} = V_{SS}$ Typical $V_{OL}$ at $V_{DD} = 5V$ (standard) Typical $V_{OL}$ at $V_{DD} = 5V$ (high-sink) Typical $V_{OH}$ at $V_{DD} = 5V$ . Typical $V_{OL}$ versus $V_{DD}$ (standard).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196<br>197<br>197<br>199<br>205<br>.205<br>206<br>206<br>207<br>207                                                                       |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                        | 76.<br>77.<br>78.<br>79.<br>80.<br>81.<br>82.<br>83.<br>84.<br>85.<br>86.                                                                       | Typical application with a crystal or ceramic resonator.  Application with a crystal or ceramic resonator for ROM (LQFP64 or any 48/60K ROM) Typical $f_{OSC(RCINT)}$ versus $T_A$ .  Integrated PLL jitter versus signal frequency(1).  Unused I/O pins configured as input.  Typical $I_{PU}$ vs $V_{DD}$ with $V_{IN} = V_{SS}$ Typical $V_{OL}$ at $V_{DD} = 5V$ (standard).  Typical $V_{OL}$ at $V_{DD} = 5V$ (high-sink)  Typical $V_{OL}$ versus $V_{DD}$ (standard).  Typical $V_{OL}$ versus $V_{DD}$ (high-sink)  Typical $V_{OL}$ versus $V_{DD}$ (high-sink)  Typical $V_{OL}$ versus $V_{DD}$ (high-sink)  Typical $V_{DD} - V_{OH}$ versus $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 196<br>197<br>199<br>205<br>.205<br>206<br>206<br>207<br>207<br>207                                                                       |