Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 1.5MB (1.5M x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 192K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Data Converters            | A/D 36x10b, 16x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LFBGA                                                                |

| Supplier Device Package    | 100-MAPBGA (11x11)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5744bk1ammh2r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

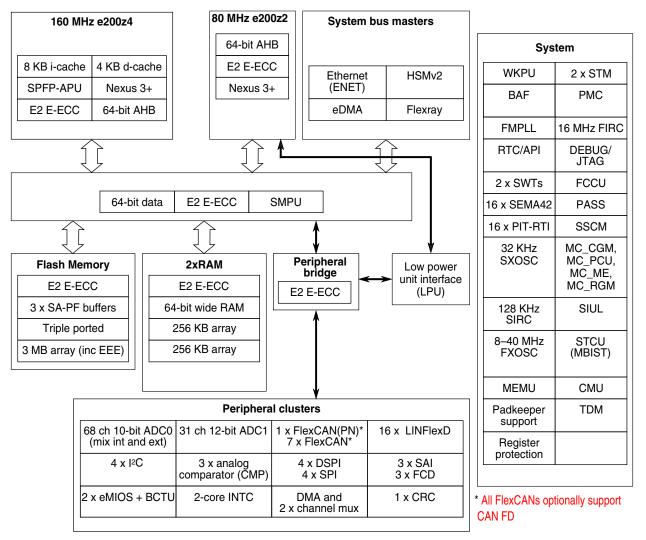

# 1 Block diagram

Figure 1. MPC5746C block diagram

# 2 Family comparison

The following table provides a summary of the different members of the MPC5746C family and their proposed features. This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

# 3.2 Ordering Information

| Example                                                                  | Code                              | PC 57                 | 4      | 6      | С       | Ş      | К0         | М                 | MJ             | 6    | R        |  |

|--------------------------------------------------------------------------|-----------------------------------|-----------------------|--------|--------|---------|--------|------------|-------------------|----------------|------|----------|--|

| ·                                                                        | Qualification Status              |                       |        |        |         |        |            |                   | 1              | 1    | 1        |  |

|                                                                          | Power Architecture                |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Automotive Platform               |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Core Version                      |                       |        |        |         |        |            |                   |                |      |          |  |

| Flas                                                                     | sh Size (core dependent)          |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Product                           |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Optional fields                   |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Fab and mask indicator            |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Temperature spec.                 |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Package Code                      |                       |        |        |         |        |            |                   | ]              |      |          |  |

|                                                                          | CPU Frequency                     |                       |        |        |         |        |            |                   |                |      |          |  |

| R = Ta                                                                   | pe & Reel (blank if Tray)         |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | Due due 6 Manual au               |                       | -      |        |         |        | <b>D</b> - | - 1               | 0              |      |          |  |

| Qualification Status                                                     | Product Version                   | Fab and I<br>K = TSMC |        | versic | on indi | icator |            | -                 | Code<br>6 LQFP | ED   |          |  |

| P = Engineering samples<br>S = Automotive qualified                      | B = Single core<br>C = Dual core  | #(0,1,etc.)           |        | sion o | f the   |        |            |                   | 6 MAPB         |      |          |  |

|                                                                          | C = Dual core                     | maskset,              |        |        |         |        |            |                   | 4 MAPE         |      |          |  |

| PC = Power Architecture                                                  |                                   | maeneeu,              |        |        |         |        | Μ          | H = 10            | OMAPB          | GA   |          |  |

| Automotive Platform                                                      |                                   | Temperat              | ure sp | bec.   |         |        | СР         | U Fre             | quency         |      |          |  |

| 57 = Power Architecture in 55nm                                          | Omtion of tiolds                  | C = -40.C             |        |        |         |        |            |                   |                | unto | 120 MHz  |  |

|                                                                          | Optional fields                   | V = -40.C             |        |        |         |        |            |                   |                | •    | 160 MHz  |  |

| Core Version                                                             | Blank = No optional feature       | M = -40.C             | to +12 | 25.0   | a       |        | 0 -        |                   | sciales        | upto | 100 1012 |  |

| 4 = e200z4 Core Version (highest<br>core version in the case of multiple | S = HSM (Security Module)         |                       |        |        |         |        |            |                   |                |      |          |  |

| cores)                                                                   | F = CAN FD                        |                       |        |        |         |        |            |                   |                |      |          |  |

| ,                                                                        | B = HSM + CAN FD                  |                       |        |        |         |        |            |                   | Metho          |      |          |  |

| Flash Memory Size                                                        | R = 512K RAM                      |                       |        |        |         |        |            | = Tape<br>ink = T | and ree        |      |          |  |

| 4 = 1.5 MB                                                               | T = HSM + 512K RAM                |                       |        |        |         |        | Dia        |                   | lay            |      |          |  |

| 5 = 2 MB                                                                 | G* = CAN FD + 512K RAM            |                       |        |        |         |        |            |                   |                |      |          |  |

| 6 = 3 MB                                                                 | H* = HSM + CAN FD + 512K RAM      |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          | * G and H for 5746 B/C only       |                       |        |        |         |        |            |                   |                |      |          |  |

| Note: Not all part number con                                            | nbinations are available as produ | ction produ           | ıct    |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   | enon prout            |        |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |  |

# 4 General

## 4.1 Absolute maximum ratings

### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

#### General

### Table 6. Recommended operating conditions ( $V_{DD HV x} = 3.3 V$ ) (continued)

| Symbol                      | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Мах | Unit |

|-----------------------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> <sup>8</sup> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ                          | Junction temperature under bias |                               | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. Only applicable when supplying from external source.

- 5. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

- 6. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 7. This supply is shorted VDD\_HV\_A on lower packages.

- 8.  $T_J$ =150°C. Assumes  $T_A$ =125°C

- Assumes maximum  $\theta$ JA of 2s2p board. See Thermal attributes

### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

### Table 7. Recommended operating conditions ( $V_{DD_HV_x} = 5 V$ )

| Symbol                                                  | Parameter                               | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max              | Unit |

|---------------------------------------------------------|-----------------------------------------|-------------------------------|----------------------------------------------------|------------------|------|

| V <sub>DD_HV_A</sub>                                    | HV IO supply voltage                    | —                             | 4.5                                                | 5.5              | V    |

| $V_{DD_HV_B}$                                           |                                         |                               |                                                    |                  |      |

| V <sub>DD_HV_C</sub>                                    |                                         |                               |                                                    |                  |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                     | HV flash supply voltage                 | —                             | 3.15                                               | 3.6              | V    |

| V <sub>DD_HV_ADC1_REF</sub>                             | HV ADC1 high reference voltage          | —                             | 3.15                                               | 5.5              | V    |

| VDD_HV_ADC0     HV ADC supply voltage       VDD_HV_ADC1 |                                         | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5              | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub>      | HV ADC supply ground                    | _                             | -0.1                                               | 0.1              | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                         | Core supply voltage                     |                               | 1.2                                                | 1.32             | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>                | Analog Comparator DAC reference voltage | _                             | 3.15                                               | 5.5 <sup>5</sup> | V    |

| I <sub>INJPAD</sub>                                     |                                         |                               | -3.0                                               | 3.0              | mA   |

| T <sub>A</sub> <sup>7</sup>                             | Ambient temperature under bias          | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125              | °C   |

| TJ                                                      | Junction temperature under bias         | _                             | -40                                                | 150              | °C   |

1. All voltages are referred to  $V_{\text{SS}\ \text{HV}}$  unless otherwise specified

2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash_{reg}}$ .

| Table 8. Voltage regulator electrical specifications (continued) | Table 8. | Voltage regulator | electrical s | specifications ( | (continued) |

|------------------------------------------------------------------|----------|-------------------|--------------|------------------|-------------|

|------------------------------------------------------------------|----------|-------------------|--------------|------------------|-------------|

| Symbol                                       | Parameter                                                                           | Conditions                                                                                                                                                                                                              | Min   | Тур | Max  | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| C <sub>flash_</sub> reg <sup>4</sup>         | External decoupling / stability<br>capacitor for internal Flash<br>regulators       | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1.32  | 2.2 | 3    | μF   |

|                                              | Combined ESR of external<br>capacitor                                               | —                                                                                                                                                                                                                       | 0.001 |     | 0.03 | Ohm  |

| $C_{_{HV\_VDD\_A}}$                          | VDD_HV_A supply capacitor <sup>5, 5</sup>                                           | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| $C_{_{HV\_VDD\_B}}$                          | VDD_HV_B supply capacitor <sup>5</sup>                                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| $C_{_{HV\_VDD\_C}}$                          | VDD_HV_C supply capacitor <sup>5</sup>                                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| C <sub>HV_ADC0</sub><br>C <sub>HV_ADC1</sub> | HV ADC supply decoupling<br>capacitances                                            | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| C <sub>HV_ADR</sub> <sup>6</sup>             | HV ADC SAR reference supply<br>decoupling capacitances                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 0.47  |     | _    | μF   |

| V <sub>DD_HV_BALL</sub>                      | FPREG Ballast collector supply voltage                                              | When collector of NPN ballast is<br>directly supplied by an on board<br>supply source (not shared with<br>VDD_HV_A supply pin) without<br>any series resistance, that is,<br>R <sub>C_BALLAST</sub> less than 0.01 Ohm. | 2.25  | _   | 5.5  | V    |

| R <sub>C_BALLAST</sub>                       | Series resistor on collector of<br>FPREG ballast                                    | When VDD_HV_BALLAST is<br>shorted to VDD_HV_A on the<br>board                                                                                                                                                           | _     | _   | 0.1  | Ohm  |

| t <sub>SU</sub>                              | Start-up time with external<br>ballastafter main supply<br>(VDD_HV_A) stabilization | Cfp_reg = 3 μF                                                                                                                                                                                                          | _     | 74  |      | μs   |

| t <sub>SU_int</sub>                          | Start-up time with internal ballast after main supply (VDD_HV_A) stabilization      | Cfp_reg = 3 μF                                                                                                                                                                                                          | _     | 103 |      | μs   |

| t <sub>ramp</sub>                            | Load current transient                                                              | lload from 15% to 55%<br>$C_{fp_{reg}} = 3 \ \mu F$                                                                                                                                                                     |       | 1.0 |      | μs   |

- Split capacitance on each pair VDD\_LV pin should sum up to a total value of C<sub>fp\_reg</sub>

Typical values will vary over temperature, voltage, tolerance, drift, but total variation must not exceed minimum and maximum values.

- 3. Ceramic X7R or X5R type with capacitance-temperature characteristics +/-15% of -55 degC to +125degC is recommended. The tolerance +/-20% is acceptable.

- 4. It is required to minimize the board parasitic inductance from decoupling capacitor to VDD\_HV\_FLA pin and the routing inductance should be less than 1nH.

#### General

| Symbol                 | Parameter           | State | Conditions | Co       | n                           | Threshold U   |                   |          | Unit   |   |

|------------------------|---------------------|-------|------------|----------|-----------------------------|---------------|-------------------|----------|--------|---|

|                        |                     |       |            | Power Up | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min               | Тур      | Max    | V |

| V <sub>LVD_LV_PD</sub> | LV supply low       | Fall  | Untrimmed  | No       | Yes                         | Function      | Disabled at Start |          |        |   |

| 2_cold                 | voltage monitoring, |       | Trimmed    |          |                             | al            | 1.1400            | 1.1550   | 1.1750 | V |

|                        | detecting at the    | Rise  | Untrimmed  |          |                             |               | Disabled          | at Start |        |   |

|                        | device pin          |       | Trimmed    |          |                             |               | 1.1600            | 1.1750   | 1.1950 | V |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

## 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | _   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

| Symbol                      | Parameter                                  | Conditions <sup>1</sup>                                                          | Min | Тур  | Max | Unit |

|-----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| I <sub>DD_BODY_2</sub><br>6 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | —   | _    | 246 | mA   |

|                             |                                            | $T_a = 125^{\circ}C^5$                                                           |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 160MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105°C                                                           |     | —    | 235 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              | —   | —    | 210 | mA   |

| I <sub>DD_BODY_3</sub><br>7 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 181 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              |     | —    | 171 | mA   |

| IDD_BODY_4 <sup>8</sup>     | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> |     | —    | 264 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           | —   | —    | 171 | mA   |

| I <sub>DD_STOP</sub>        | STOP mode Operating current                | $T_{a} = 125 \ ^{\circ}C^{9}$                                                    | -   | -    | 49  | mA   |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | 10.6 | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           |     | 8.1  | —   |      |

|                             |                                            | $V_{DD_LV} = 1.25 V$                                                             |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 25 °C                                                           |     | 4.6  | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

### Table 10. Current consumption characteristics (continued)

| Symbol                                                        | Parameter                                                            | Va                                 | lue                             | Unit |  |

|---------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------|---------------------------------|------|--|

|                                                               |                                                                      | Min                                | Max                             |      |  |

| Vil (pad_i_hv)                                                | pad_i_hv Input Buffer Low Voltage                                    | VDD_HV_x -<br>0.3                  | 0.45*VDD_HV_<br>x               | V    |  |

| Vhys (pad_i_hv)                                               | pad_i_hv Input Buffer Hysteresis                                     | 0.09*VDD_HV_<br>x                  |                                 | V    |  |

| Vih_hys                                                       | CMOS Input Buffer High Voltage (with hysteresis enabled)             | 0.65*<br>VDD_HV_x                  | VDD_HV_x +<br>0.3               | V    |  |

| Vil_hys                                                       | ys CMOS Input Buffer Low Voltage (with hysteresis VDD_<br>enabled) 0 |                                    | 0.35*VDD_HV_<br>x               | V    |  |

| Vih CMOS Input Buffer High Voltage (with hysteresis disabled) |                                                                      | 0.55 *<br>VDD_HV_x <sup>1, 1</sup> | VDD_HV_x <sup>1</sup> +<br>0.3  | V    |  |

| Vil CMOS Input Buffer Low Voltage (with hysteresis disabled)  |                                                                      | VDD_HV_x -<br>0.3                  | 0.40 *<br>VDD_HV_x <sup>1</sup> | V    |  |

| Vhys                                                          | CMOS Input Buffer Hysteresis                                         | 0.09 *<br>VDD_HV_x <sup>1</sup>    |                                 | V    |  |

| Pull_IIH (pad_i_hv)                                           | Weak Pullup Current <sup>2, 2</sup> Low                              | 23                                 |                                 | μA   |  |

| Pull_IIH (pad_i_hv)                                           | Weak Pullup Current <sup>3, 3</sup> High                             |                                    | 82                              | μA   |  |

| Pull_IIL (pad_i_hv)                                           | Weak Pulldown Current <sup>3</sup> Low                               | 40                                 |                                 | μA   |  |

| Pull_IIL (pad_i_hv)                                           | Weak Pulldown Current <sup>2</sup> High                              |                                    | 130                             | μA   |  |

| Pull_loh                                                      | Weak Pullup Current <sup>4</sup>                                     | 30                                 | 80                              | μA   |  |

| Pull_lol                                                      | Weak Pulldown Current <sup>5</sup>                                   | 30                                 | 80                              | μA   |  |

| linact_d                                                      | Digital Pad Input Leakage Current (weak pull inactive)               | -2.5                               | 2.5                             | μA   |  |

| Voh                                                           | Output High Voltage <sup>6</sup>                                     | 0.8 *<br>VDD_HV_x <sup>1</sup>     | —                               | V    |  |

| Vol                                                           | Output Low Voltage <sup>7</sup>                                      | _                                  | 0.2*VDD_HV_x                    | V    |  |

|                                                               | Output Low Voltage <sup>8</sup>                                      |                                    | 0.1*VDD_HV_x                    |      |  |

| loh_f                                                         | Full drive loh <sup>9, 9</sup> (SIUL2_MSCRn.SRC[1:0] = 11)           | 18                                 | 70                              | mA   |  |

| lol_f                                                         | Full drive lol <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 11)              | 21                                 | 120                             | mA   |  |

| loh_h                                                         | Half drive loh <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 10)              | 9                                  | 35                              | mA   |  |

| lol_h                                                         | Half drive Iol <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 10)              | 10.5                               | 60                              | mA   |  |

### Table 17. DC electrical specifications @ 5 V Range (continued)

- 1.  $VDD_HV_x = VDD_HV_A$ ,  $VDD_HV_B$ ,  $VDD_HV_C$

- 2. Measured when pad=0.69\*VDD\_HV\_x

- 3. Measured when pad=0.49\*VDD\_HV\_x

- 4. Measured when pad = 0 V

- 5. Measured when pad =  $VDD_HV_x$

- 6. Measured when pad is sourcing 2 mA  $\,$

- 7. Measured when pad is sinking 2 mA

- 8. Measured when pad is sinking 1.5 mA

- 9. Ioh/IoI is derived from spice simulations. These values are NOT guaranteed by test.

## 5.5 Reset pad electrical characteristics

The device implements a dedicated bidirectional RESET pin.

# 6.2 Clocks and PLL interfaces modules

## 6.2.1 Main oscillator electrical characteristics

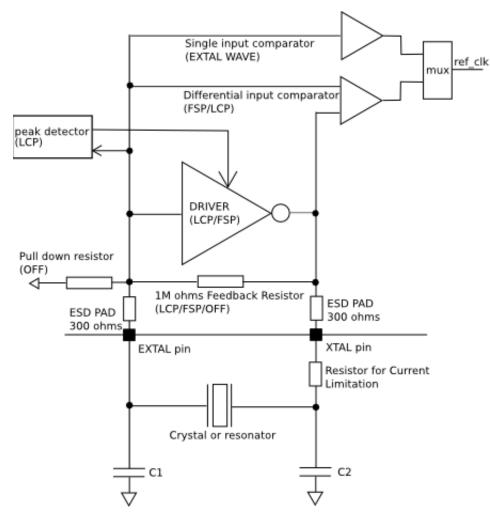

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

Figure 7. Oscillator connections scheme

| Table 23. | Main oscillator electrical characteristics |

|-----------|--------------------------------------------|

|-----------|--------------------------------------------|

| Symbol                      | Parameter               | Mode                       | Conditions | Min | Тур | Max | Unit            |

|-----------------------------|-------------------------|----------------------------|------------|-----|-----|-----|-----------------|

| f <sub>XOSCHS</sub>         | Oscillator<br>frequency | FSP/LCP                    |            | 8   |     | 40  | MHz             |

| <b>g</b> <sub>mXOSCHS</sub> | Driver                  | LCP                        |            |     | 23  |     | mA/V            |

|                             | Transconduct ance       | FSP                        |            |     | 33  | _   |                 |

| V <sub>XOSCHS</sub>         | Oscillation             | LCP <sup>1, 2, 1, 2</sup>  | 8 MHz      |     | 1.0 |     | V <sub>PP</sub> |

|                             | Amplitude               | Amplitude 16 MHz<br>40 MHz | 16 MHz     |     | 1.0 |     |                 |

|                             |                         |                            | 40 MHz     |     | 0.8 |     | -               |

| T <sub>XOSCHSSU</sub>       | Startup time            | FSP/LCP <sup>1</sup>       | 8 MHz      |     | 2   |     | ms              |

|                             |                         |                            | 16 MHz     |     | 1   |     |                 |

|                             |                         |                            | 40 MHz     |     | 0.5 |     |                 |

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|--------------------------------------------------|-------|

| t <sub>drcv</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  | _       | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP | _                                                | _       | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       | _                                                | _       | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods | _       | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

Table 33.

Flash memory AC timing specifications (continued)

## 6.3.6 Flash read wait state and address pipeline control settings

The following table describes the recommended RWSC and APC settings at various operating frequencies based on specified intrinsic flash access times of the flash module controller array at 125 °C.

Table 34.

Flash Read Wait State and Address Pipeline Control Combinations

| Flash frequency             | RWSC setting | APC setting |

|-----------------------------|--------------|-------------|

| 0 MHz < fFlash <= 33 MHz    | 0            | 0           |

| 33 MHz < fFlash <= 100 MHz  | 2            | 1           |

| 100 MHz < fFlash <= 133 MHz | 3            | 1           |

| 133 MHz < fFlash <= 160 MHz | 4            | 1           |

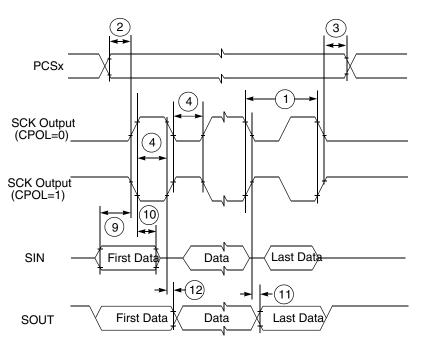

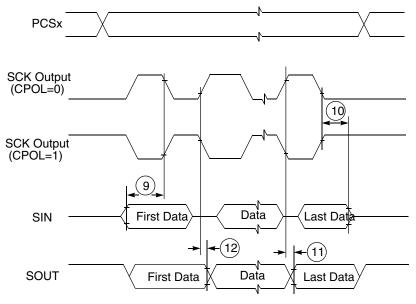

Figure 8. DSPI classic SPI timing — master, CPHA = 0

Figure 9. DSPI classic SPI timing — master, CPHA = 1

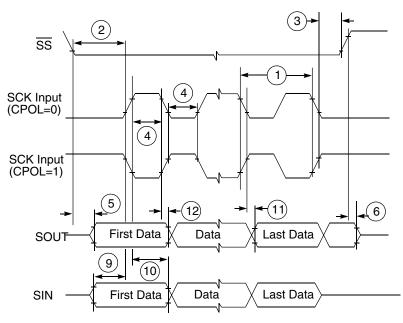

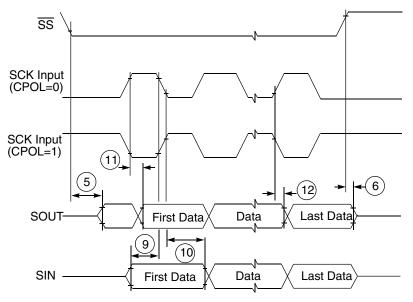

Figure 10. DSPI classic SPI timing — slave, CPHA = 0

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

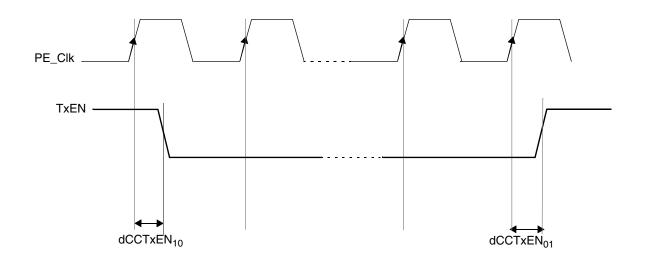

6.4.2.3 TxD

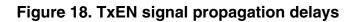

Figure 19. TxD Signal

| Table 39. | TxD output characteristics |

|-----------|----------------------------|

|-----------|----------------------------|

| Name                                                   | Description <sup>1</sup>                                   | Min   | Max            | Unit |

|--------------------------------------------------------|------------------------------------------------------------|-------|----------------|------|

| dCCT <sub>xAsym</sub>                                  | Asymmetry of sending CC @ 25 pF load (=dCCTxD50% - 100 ns) | -2.45 | 2.45           | ns   |

| dCCTxD <sub>RISE25</sub> +dCCTx<br>D <sub>FALL25</sub> | Sum of Rise and Fall time of TxD signal at the output      |       | 9 <sup>2</sup> | ns   |

Table continues on the next page...

#### **Debug specifications**

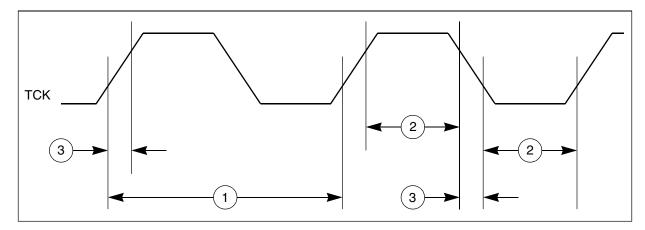

### Table 45. JTAG pin AC electrical characteristics <sup>1</sup> (continued)

| #  | Symbol             | Characteristic                                            | Min | Max | Unit |

|----|--------------------|-----------------------------------------------------------|-----|-----|------|

| 12 | t <sub>BSDVZ</sub> | TCK Falling Edge to Output Valid out of High<br>Impedance | —   | 600 | ns   |

| 13 | t <sub>BSDHZ</sub> | TCK Falling Edge to Output High Impedance                 | —   | 600 | ns   |

| 14 | t <sub>BSDST</sub> | Boundary Scan Input Valid to TCK Rising Edge              | 15  |     | ns   |

| 15 | t <sub>BSDHT</sub> | TCK Rising Edge to Boundary Scan Input Invalid            | 15  | _   | ns   |

- 1. These specifications apply to JTAG boundary scan only.

- 2. This timing applies to TDI, TDO, TMS pins, however, actual frequency is limited by pad type for EXTEST instructions. Refer to pad specification for allowed transition frequency

- 3. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 4. Applies to all pins, limited by pad slew rate. Refer to IO delay and transition specification and add 20 ns for JTAG delay.

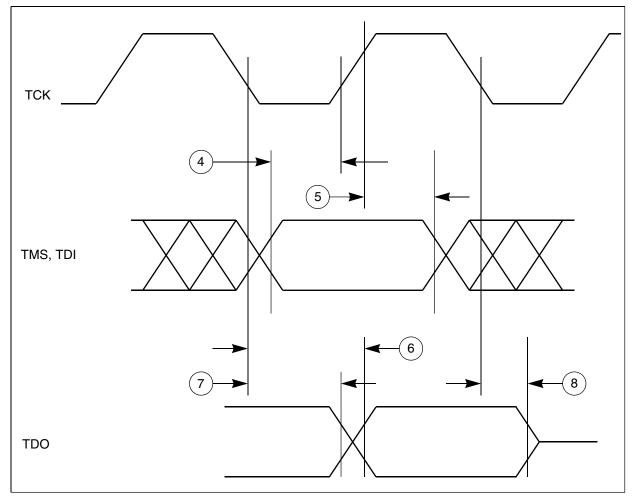

Figure 25. JTAG test clock input timing

### Debug specifications

Figure 26. JTAG test access port timing

| Board type | Symbol           | Description                                                                                                          | 100 MAPBGA | Unit | Notes |

|------------|------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|-------|

| -          | R <sub>θJB</sub> | Thermal<br>resistance, junction<br>to board                                                                          | 10.8       | °C/W | 44    |

| -          | R <sub>θJC</sub> | Thermal<br>resistance, junction<br>to case                                                                           | 8.2        | °C/W | 55    |

|            | Ψ <sub>JT</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection)    | 0.2        | °C/W | 66    |

| _          | Ψ <sub>JB</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) | 7.8        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

# 8 Dimensions

## 8.1 Obtaining package dimensions

Package dimensions are provided in package drawing.

To find a package drawing, go to www.nxp.com and perform a keyword search for the drawing's document number:

| Package    | NXP Document Number |

|------------|---------------------|

| 100 MAPBGA | 98ASA00802D         |

Table continues on the next page...

**Pinouts**

| Package         | NXP Document Number |

|-----------------|---------------------|

| 176-pin LQFP-EP | 98ASA00698D         |

| 256 MAPBGA      | 98ASA00346D         |

| 324 MAPBGA      | 98ASA10582D         |

# 9 Pinouts

## 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

# 10 Reset sequence

## 10.1 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

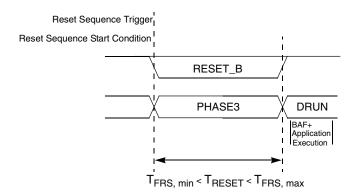

## 10.1.1 Reset sequence duration

Table 49 specifies the reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter                                      | T <sub>Reset</sub> |             | Unit |    |

|-----|-------------------|------------------------------------------------|--------------------|-------------|------|----|

|     |                   |                                                | Min                | Тур<br>1, 1 | Max  |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled       | 6.2                | 7.3         | -    | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled      | 110                | 182         | -    | us |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot    | 6.2                | 7.3         | -    | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot  | 110                | 182         | -    | us |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot | 7                  | 9           | -    | us |

Table 49. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

Figure 36. Functional reset sequence short

The reset sequences shown in Figure 35 and Figure 36 are triggered by functional reset events. RESET\_B is driven low during these two reset sequences only if the corresponding functional reset source (which triggered the reset sequence) was enabled to drive RESET\_B low for the duration of the internal reset sequence. See the RGM\_FBRE register in the device reference manual for more information.

# **11 Revision History**

# 11.1 Revision History

The following table provides a revision history for this document.

| Rev. No. | Date          | Substantial Changes |

|----------|---------------|---------------------|

| Rev 1    | 14 March 2013 | Initial Release     |

| Table 51. | Revision | History ( | (continued) |

|-----------|----------|-----------|-------------|

|-----------|----------|-----------|-------------|

| Rev. No. | Date                | Substantial Changes                                                                                                                                                                                                                                                                                                                           |

|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 4    | 9 March 2016        | <ul> <li>In section, Voltage regulator electrical characteristics</li> <li>In table, Voltage regulator electrical specifications:</li> <li>Updated the footnote on V<sub>DD_HV_BALLAST</sub></li> </ul>                                                                                                                                       |

| Rev 5    | 27 February<br>2017 | <ul> <li>In Family Comparison section:</li> <li>Updated the "MPC5746C Family Comparison" table.</li> <li>added "NVM Memory Map 1", "NVM Memory Map 2", and "RAM Memory Map" tables.</li> </ul>                                                                                                                                                |

|          |                     | <ul> <li>Updated the product version, flash memory size and optional fields information in<br/>Ordering Information section.</li> </ul>                                                                                                                                                                                                       |

|          |                     | In Recommended Operating Conditions section, removed the note related to additional crossover current.                                                                                                                                                                                                                                        |

|          |                     | <ul> <li>VDD_HV_C row added in "Voltage regulator electrical specifications" table in Voltage<br/>regulator electrical characteristics section.</li> </ul>                                                                                                                                                                                    |

|          |                     | <ul> <li>In Voltage Monitor Electrical Characteristics section, updated the "Trimmed" Fall and<br/>Rise specs of VHVD_LV_cold parameter in "Voltage Monitor Electrical Characteristics"<br/>table.</li> </ul>                                                                                                                                 |

|          |                     | <ul> <li>In AC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> </ul>                                                                                                                                                                               |

|          |                     | <ul> <li>In DC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in<br/>the table.</li> </ul>                                                                                                                                      |

|          |                     | <ul> <li>In AC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> <li>In DC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in the table.</li> </ul> |

|          |                     | <ul> <li>In "Flash memory AC timing specifications" table in Flash memory AC timing specifications section:</li> <li>Updated the "t<sub>psus</sub>" typ value from 7 us to 9.4 us.</li> <li>Updated the "t<sub>psus</sub>" max value from 9.1 us to 11.5 us.</li> </ul>                                                                       |

|          |                     | <ul> <li>Added "Continuous SCK Timing" table in DSPI timing section.</li> </ul>                                                                                                                                                                                                                                                               |

|          |                     | <ul> <li>Added "ADC pad leakage" at 105°C TA conditions in "ADC conversion characteristics<br/>(for 12-bit)" table in ADC electrical specifications section.</li> </ul>                                                                                                                                                                       |

|          |                     | <ul> <li>In "STANDBY Current consumption characteristics" table in Supply current characteristics section:</li> <li>Updated the Typ and max values of IDD Standby current.</li> <li>Added IDD Standby3 current spec for FIRC ON.</li> </ul>                                                                                                   |

|          |                     | Removed IVDDHV and IVDDLV specs in 16 MHz RC Oscillator electrical specifications section.                                                                                                                                                                                                                                                    |

|          |                     | Added Reset Sequence section, with Reset Sequence Duration, BAF execution duration section, and Reset Sequence Distribution as its sub-sections.                                                                                                                                                                                              |

#### **Revision History**

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                        |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 5.1  | 22 May 2017 | Removed the Introduction section from Section 4 "General".                                                                                                                                                                 |

|          |             | <ul> <li>In AC Specifications@3.3V section, removed note related to Cz results and added two<br/>notes.</li> </ul>                                                                                                         |

|          |             | <ul> <li>In AC Specifications@5V section, added two notes.</li> </ul>                                                                                                                                                      |

|          |             | <ul> <li>In ADC Electrical Specifications section, added spec value of "ADC Analog Pad" at Max<br/>leakage (standard channel)@ 105 C T<sub>A</sub> in "ADC conversion characteristics (for 10-bit)"<br/>table.</li> </ul>  |

|          |             | <ul> <li>In PLL Electrical Specifications section, updated the first footnote of "Jitter calculation"<br/>table.</li> </ul>                                                                                                |

|          |             | <ul> <li>In Analog Comparator Electrical Specifications section, updated the TDLS (propagation<br/>delay, low power mode) max value in "Comparator and 6-bit DAC electrical<br/>specifications" table to 21 us.</li> </ul> |

|          |             | <ul> <li>In Recommended Operating Conditions section, updated the footnote link to T<sub>A</sub> in<br/>"Recommended operating conditions (V DD_HV_x = 5V)" table.</li> </ul>                                              |

Table 51. Revision History (continued)