Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 2MB (2M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 256K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Data Converters            | A/D 36x10b, 16x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LFBGA                                                                |

| Supplier Device Package    | 100-MAPBGA (11x11)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5745bbk1acmh2 |

# **Table of Contents**

| 1 | Block | k diagran | n4                                            |    |       | 6.3.2       | Flash me      | emory Array Integrity and Margi  | n  |

|---|-------|-----------|-----------------------------------------------|----|-------|-------------|---------------|----------------------------------|----|

| 2 | Fami  | ly compa  | arison4                                       |    |       |             | Read sp       | ecifications                     | 39 |

| 3 | Orde  | ring part | s8                                            |    |       | 6.3.3       | Flash me      | emory module life specifications | 40 |

|   | 3.1   | Determ    | ining valid orderable parts8                  |    |       | 6.3.4       | Data ret      | ention vs program/erase cycles.  | 40 |

|   | 3.2   | Orderin   | ng Information9                               |    |       | 6.3.5       | Flash me      | emory AC timing specifications   | 41 |

| 4 | Gene  | eral      | 9                                             |    |       | 6.3.6       | Flash re      | ad wait state and address pipeli | ne |

|   | 4.1   | Absolut   | te maximum ratings9                           |    |       |             | control s     | settings                         | 42 |

|   | 4.2   | Recom     | mended operating conditions11                 |    | 6.4   | Commu       | ınication ir  | nterfaces                        | 43 |

|   | 4.3   | Voltage   | e regulator electrical characteristics13      |    |       | 6.4.1       | DSPI tim      | ning                             | 43 |

|   | 4.4   | Voltage   | e monitor electrical characteristics17        |    |       | 6.4.2       | FlexRay       | electrical specifications        | 49 |

|   | 4.5   | Supply    | current characteristics                       |    |       |             | 6.4.2.1       | FlexRay timing                   | 49 |

|   | 4.6   | Electro   | static discharge (ESD) characteristics22      |    |       |             | 6.4.2.2       | TxEN                             | 49 |

|   | 4.7   | Electro   | magnetic Compatibility (EMC) specifications23 |    |       |             | 6.4.2.3       | TxD                              | 50 |

| 5 | I/O p | aramete   | rs23                                          |    |       |             | 6.4.2.4       | RxD                              | 51 |

|   | 5.1   | AC spe    | ecifications @ 3.3 V Range23                  |    |       | 6.4.3       | Ethernet      | t switching specifications       | 52 |

|   | 5.2   | DC elec   | ctrical specifications @ 3.3V Range24         |    |       | 6.4.4       | SAI elec      | trical specifications            | 53 |

|   | 5.3   | AC spe    | ecifications @ 5 V Range25                    |    | 6.5   | Debug       | specification | ons                              | 55 |

|   | 5.4   | DC elec   | ctrical specifications @ 5 V Range25          |    |       | 6.5.1       | JTAG in       | terface timing                   | 55 |

|   | 5.5   | Reset p   | pad electrical characteristics26              |    |       | 6.5.2       | Nexus ti      | ming                             | 58 |

|   | 5.6   | PORST     | Telectrical specifications28                  |    |       | 6.5.3       | WKPU/N        | NMI timing                       | 60 |

| 6 | Perip | heral op  | erating requirements and behaviours28         |    |       | 6.5.4       | External      | interrupt timing (IRQ pin)       | 61 |

|   | 6.1   | Analog    | 28                                            | 7  | The   | rmal attrib | outes         |                                  | 61 |

|   |       | 6.1.1     | ADC electrical specifications28               |    | 7.1   | Therma      | l attributes  | S                                | 61 |

|   |       | 6.1.2     | Analog Comparator (CMP) electrical            | 8  | Dim   | ensions     |               |                                  | 65 |

|   |       |           | specifications33                              |    | 8.1   | Obtaini     | ng packag     | e dimensions                     | 65 |

|   | 6.2   | Clocks    | and PLL interfaces modules34                  | 9  | Pino  | outs        |               |                                  | 66 |

|   |       | 6.2.1     | Main oscillator electrical characteristics34  |    | 9.1   | Packag      | e pinouts     | and signal descriptions          | 66 |

|   |       | 6.2.2     | 32 kHz Oscillator electrical specifications36 | 10 | ) Res | et sequer   | ıce           |                                  | 66 |

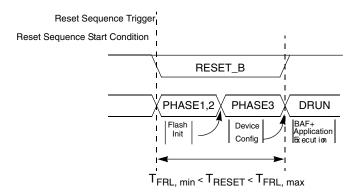

|   |       | 6.2.3     | 16 MHz RC Oscillator electrical               |    | 10.1  | Reset s     | equence       |                                  | 66 |

|   |       |           | specifications36                              |    |       | 10.1.1      | Reset se      | equence duration                 | 66 |

|   |       | 6.2.4     | 128 KHz Internal RC oscillator Electrical     |    |       | 10.1.2      | BAF exe       | ecution duration                 | 66 |

|   |       |           | specifications37                              |    |       | 10.1.3      | Reset se      | equence description              | 67 |

|   |       | 6.2.5     | PLL electrical specifications37               | 11 | 1 Rev | ision Hist  | ory           |                                  | 69 |

|   | 6.3   | Memor     | y interfaces38                                |    | 11.1  | Revisio     | n History     |                                  | 69 |

|   |       | 6.3.1     | Flash memory program and erase                |    |       |             |               |                                  |    |

|   |       |           | specifications38                              |    |       |             |               |                                  |    |

Family comparison

#### Table 1. MPC5746C Family Comparison1 (continued)

| Feature                                                      | MPC5745B                                              | MPC5744B    | MPC5746B            | MPC5744C           | MPC5745C    | MPC5746C                         |  |  |

|--------------------------------------------------------------|-------------------------------------------------------|-------------|---------------------|--------------------|-------------|----------------------------------|--|--|

| I <sup>2</sup> C                                             | 4                                                     | 4           | 4                   |                    | 4           |                                  |  |  |

| SAI/I <sup>2</sup> S                                         | 3                                                     | 3           | 3                   |                    | 3           |                                  |  |  |

| FXOSC                                                        |                                                       |             | 8 - 40              | ) MHz              |             |                                  |  |  |

| SXOSC                                                        |                                                       |             | 32 I                | KHz                |             |                                  |  |  |

| FIRC                                                         |                                                       |             | 16 [                | ИНz                |             |                                  |  |  |

| SIRC                                                         |                                                       |             | 128                 | KHz                |             |                                  |  |  |

| FMPLL                                                        |                                                       |             | -                   | 1                  |             |                                  |  |  |

| Low Power Unit<br>(LPU)                                      |                                                       |             | Y                   | es                 |             |                                  |  |  |

| FlexRay 2.1 (dual channel)                                   | Yes, 128 MB                                           | Yes, 128 MB | Yes, 128 MB         |                    | Yes, 128 MB |                                  |  |  |

| Ethernet (RMII,<br>MII + 1588, Muti<br>queue AVB<br>support) | 1                                                     | 1           | 1                   | 1                  |             |                                  |  |  |

| CRC                                                          |                                                       |             | -                   | 1                  |             |                                  |  |  |

| MEMU                                                         |                                                       | 2           |                     |                    |             |                                  |  |  |

| STCU2                                                        | 1                                                     |             |                     |                    |             |                                  |  |  |

| HSM-v2<br>(security)                                         |                                                       |             | Opti                | onal               |             |                                  |  |  |

| Censorship                                                   |                                                       |             | Y                   | es                 |             |                                  |  |  |

| FCCU                                                         |                                                       |             | -                   | 1                  |             |                                  |  |  |

| Safety level                                                 |                                                       |             | Specific functions  | ASIL-B certifiable |             |                                  |  |  |

| User MBIST                                                   |                                                       |             | Y                   | es                 |             |                                  |  |  |

| I/O Retention in Standby                                     |                                                       |             | Y                   | es                 |             |                                  |  |  |

| GPIO <sup>6</sup>                                            |                                                       |             | Up to 264 GPI an    | d up to 246 GPIO   |             |                                  |  |  |

| Debug                                                        |                                                       |             | JTA                 | GC,                |             |                                  |  |  |

|                                                              |                                                       |             | cJT                 | AG                 |             |                                  |  |  |

| Nexus                                                        |                                                       | Z4 N3+ (C   | Only available on 3 | 24BGA (developm    | ent only))  |                                  |  |  |

|                                                              | Z2 N3+ (Only available on 324BGA (development only) ) |             |                     |                    |             |                                  |  |  |

| Packages                                                     | 176 LQFP-EP                                           | 176 LQFP-EP | 176 LQFP-EP         | 176 LQFP-EP        | 176 LQFP-EP | 176 LQFP-EP                      |  |  |

|                                                              | 256 BGA                                               | 256 BGA     | 256 BGA             | 256 BGA            | 256 BGA     | 256 BGA,                         |  |  |

|                                                              | 100 BGA                                               | 100 BGA     | 100 BGA             | 100 BGA            | 100 BGA     | 324 BGA<br>(development<br>only) |  |  |

|                                                              |                                                       |             |                     |                    |             | 100 BGA                          |  |  |

<sup>1.</sup> Feature set dependent on selected peripheral multiplexing, table shows example. Peripheral availability is package dependent.

<sup>2.</sup> Based on 125°C ambient operating temperature and subject to full device characterization.

<sup>3.</sup> Contact NXP representative for part number

<sup>4.</sup> Additional SWT included when HSM option selected

<sup>5.</sup> See device datasheet and reference manual for information on to timer channel configuration and functions.

<sup>6.</sup> Estimated I/O count for largest proposed packages based on multiplexing with peripherals.

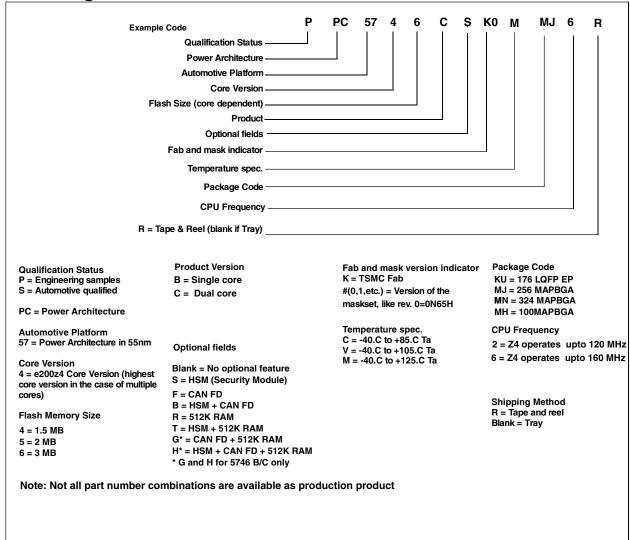

#### **Ordering parts**

Table 4. MPC5746C Family Comparison - RAM Memory Map (continued)

| Start Address | End Address | Allocated size | Description | MPC5744       | MPC5745       | MPC5746   |

|---------------|-------------|----------------|-------------|---------------|---------------|-----------|

| 0x40030000    | 0x4003FFFF  | 64 KB          | SRAM4       | not available | available     | available |

| 0x40040000    | 0x4004FFFF  | 64 KB          | SRAM5       | not available | not available | available |

| 0x40050000    | 0x4005FFFF  | 64 KB          | SRAM6       | not available | not available | available |

| 0x40060000    | 0x4006FFFF  | 64 KB          | SRAM7       | not available | not available | optional  |

| 0x40070000    | 0x4007FFFF  | 64 KB          | SRAM8       | not available | not available | optional  |

# 3 Ordering parts

# 3.1 Determining valid orderable parts

To determine the orderable part numbers for this device, go to www.nxp.com and perform a part number search for the following device number: MPC5746C.

# 3.2 Ordering Information

### 4 General

### 4.1 Absolute maximum ratings

#### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

Table 6. Recommended operating conditions ( $V_{DD\ HV\ x} = 3.3\ V$ ) (continued)

| Symbol           | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Max | Unit |

|------------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> 8 | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| T <sub>J</sub>   | Junction temperature under bias | _                             | -40              | 150 | °C   |

- 1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. Only applicable when supplying from external source.

- 5. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

- 6. VIN1\_CMP\_REF ≤ VDD\_HV\_A

- 7. This supply is shorted VDD\_HV\_A on lower packages.

- 8. T<sub>J</sub>=150°C. Assumes T<sub>A</sub>=125°C

- Assumes maximum θJA of 2s2p board. See Thermal attributes

#### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

Table 7. Recommended operating conditions ( $V_{DD\ HV\ x} = 5\ V$ )

| Symbol                                          | Parameter                                                   | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max              | Unit |

|-------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------|------------------|------|

| $V_{DD\_HV\_A}$                                 | HV IO supply voltage                                        | _                             | 4.5                                                | 5.5              | V    |

| $V_{DD\_HV\_B}$                                 |                                                             |                               |                                                    |                  |      |

| $V_{DD\_HV\_C}$                                 |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>             | HV flash supply voltage                                     | _                             | 3.15                                               | 3.6              | V    |

| V <sub>DD_HV_ADC1_REF</sub>                     | HV ADC1 high reference voltage                              | _                             | 3.15                                               | 5.5              | V    |

| V <sub>DD_HV_ADC0</sub> V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5              | V    |

| V <sub>SS_HV_ADC0</sub> V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                             | -0.1                                               | 0.1              | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                 | Core supply voltage                                         | _                             | 1.2                                                | 1.32             | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>        | Analog Comparator DAC reference voltage                     | _                             | 3.15                                               | 5.5 <sup>5</sup> | V    |

| I <sub>INJPAD</sub>                             | Injected input current on any pin during overload condition | _                             | -3.0                                               | 3.0              | mA   |

| T <sub>A</sub> <sup>7</sup>                     | Ambient temperature under bias                              | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125              | °C   |

| T <sub>J</sub>                                  | Junction temperature under bias                             | _                             | -40                                                | 150              | °C   |

- 1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with Cflash req-

13

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. VIN1\_CMP\_REF ≤ VDD\_HV\_A

- 6. This supply is shorted VDD\_HV\_A on lower packages.

- 7.  $T_J=150$ °C. Assumes  $T_A=125$ °C

- Assumes maximum θJA of 2s2p board. See Thermal attributes

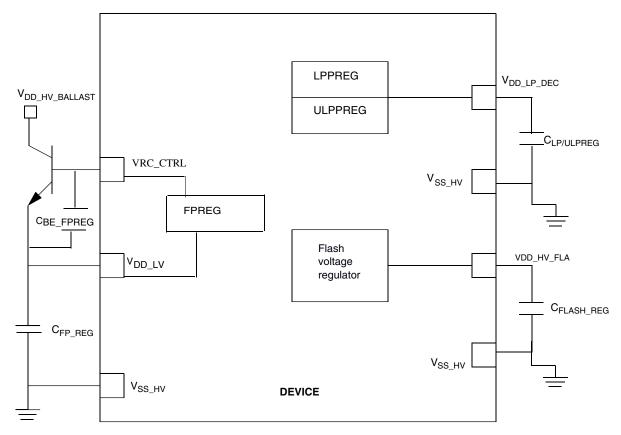

### 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Generating core supply using internal ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- $\bullet$  Low voltage detector low threshold (LVD\_IO\_A\_LO) for  $V_{DD\_HV\_IO\_A\ supply}$

- $\bullet$  Low voltage detector high threshold (LVD\_IO\_A\_Hi) for  $V_{DD\_HV\_IO\_A\ supply}$

- Low voltage detector (LVD\_FLASH) for 3.3 V flash supply (VDD\_HV\_FLA)

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

Figure 2. Voltage regulator capacitance connection

#### **NOTE**

On BGA, VSS\_LV and VSS\_HV have been joined on substrate and renamed as VSS.

Table 8. Voltage regulator electrical specifications

| Symbol                             | Parameter                                                                   | Conditions                                                                                              | Min   | Тур              | Max  | Unit |

|------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------------------|------|------|

| C <sub>fp_reg</sub> <sup>1</sup>   | External decoupling / stability capacitor                                   | Min, max values shall be granted with respect to tolerance, voltage, temperature, and aging variations. | 1.32  | 2.2 <sup>2</sup> | 3    | μF   |

|                                    | Combined ESR of external capacitor                                          | _                                                                                                       | 0.001 | _                | 0.03 | Ohm  |

| C <sub>lp/ulp_reg</sub>            | External decoupling / stability capacitor for internal low power regulators | Min, max values shall be granted with respect to tolerance, voltage, temperature, and aging variations. | 0.8   | 1                | 1.4  | μF   |

|                                    | Combined ESR of external capacitor                                          | _                                                                                                       | 0.001 | _                | 0.1  | Ohm  |

| C <sub>be_fpreg</sub> <sup>3</sup> | Capacitor in parallel to base-                                              | BCP68 and BCP56                                                                                         |       | 3.3              |      | nF   |

|                                    | emitter                                                                     | MJD31                                                                                                   |       | 4.7              |      |      |

Table continues on the next page...

#### General

- 5. 1. For VDD\_HV\_x, 1µf on each side of the chip

- a. 0.1 µf close to each VDD/VSS pin pair.

- b. 10 µf near for each power supply source

- c. For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as specified by CFP\_REG parameter.

- 2. For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as specified by CFP\_REG parameter

- 6. Only applicable to ADC1

- 7. In external ballast configuration the following must be ensured during power-up and power-down (Note: If V<sub>DD\_HV\_BALLAST</sub> is supplied from the same source as VDD\_HV\_A this condition is implicitly met):

- During power-up, V<sub>DD\_HV\_BALLAST</sub> must have met the min spec of 2.25V before VDD\_HV\_A reaches the POR\_HV\_RISE min of 2.75V.

- During power-down, V<sub>DD\_HV\_BALLAST</sub> must not drop below the min spec of 2.25V until VDD\_HV\_A is below POR\_HV\_FALL min of 2.7V.

#### NOTE

For a typical configuration using an external ballast transistor with separate supply for VDD\_HV\_A and the ballast collector, a bulk storage capacitor (as defined in Table 8) is required on VDD\_HV\_A close to the device pins to ensure a stable supply voltage.

Extra care must be taken if the VDD\_HV\_A supply is also being used to power the external ballast transistor or the device is running in internal regulation mode. In these modes, the inrush current on device Power Up or on exit from Low Power Modes is significant and may case the VDD\_HV\_A voltage to drop resulting in an LVD reset event. To avoid this, the board layout should be optimized to reduce common trace resistance or additional capacitance at the ballast transistor collector (or VDD\_HV\_A pins in the case of internal regulation mode) is required. NXP recommends that customers simulate the external voltage supply circuitry.

In all circumstances, the voltage on VDD\_HV\_A must be maintained within the specified operating range (see Recommended operating conditions) to prevent LVD events.

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

# 4.4 Voltage monitor electrical characteristics

Table 9. Voltage monitor electrical characteristics

| Symbol                  | Parameter                     | State | Conditions | Co       | nfiguratio                  | n             |          | Thresho           | ld     | Unit |  |

|-------------------------|-------------------------------|-------|------------|----------|-----------------------------|---------------|----------|-------------------|--------|------|--|

|                         |                               |       |            | Power Up | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min      | Тур               | Max    | V    |  |

| V <sub>POR_LV</sub>     | LV supply power               | Fall  | Untrimmed  | Yes      | No                          | Destructi     | 0.930    | 0.979             | 1.028  | V    |  |

|                         | on reset detector             |       | Trimmed    |          |                             | ve            | -        | -                 | -      | V    |  |

|                         |                               | Rise  | Untrimmed  |          |                             |               | 0.980    | 1.029             | 1.078  | ٧    |  |

|                         |                               |       | Trimmed    |          |                             |               | -        | -                 | -      | ٧    |  |

| V <sub>HVD_LV_col</sub> | LV supply high                | Fall  | Untrimmed  | No       | Yes                         | Function      | Disabled | at Start          | •      | _    |  |

| d                       | voltage monitoring,           |       | Trimmed    |          |                             | al            | 1.325    | 1.345             | 1.375  | V    |  |

|                         | detecting at                  | Rise  | Untrimmed  |          |                             |               | Disabled | at Start          | •      | •    |  |

|                         | device pin                    |       | Trimmed    |          |                             |               | 1.345    | 1.365             | 1.395  | V    |  |

| $V_{LVD\_LV\_PD}$       | LV supply low                 | Fall  | Untrimmed  | Yes      | No                          | Destructi     | 1.0800   | 1.1200            | 1.1600 | V    |  |

| 2_hot                   | voltage monitoring,           |       | Trimmed    |          |                             | ve            | 1.1250   | 1.1425            | 1.1600 | V    |  |

|                         | detecting on the              | Rise  | Untrimmed  |          |                             |               | 1.1000   | 1.1400            | 1.1800 | V    |  |

|                         | PD2 core (hot) area           |       | Trimmed    |          |                             |               | 1.1450   | 1.1625            | 1.1800 | V    |  |

| V <sub>LVD_LV_PD</sub>  | LV supply low                 | Fall  | Untrimmed  | Yes      | No                          | Destructi     | 1.0800   | 1.1200            | 1.1600 | V    |  |

| 1_hot (BGFP)            | voltage monitoring,           |       | Trimmed    |          |                             | ve            | 1.1140   | 1.1370            | 1.1600 | V    |  |

|                         | detecting on the              | Rise  | Untrimmed  |          |                             |               | 1.1000   | 1.140             | 1.1800 | V    |  |

|                         | PD1 core (hot) area           |       | Trimmed    |          |                             |               | 1.1340   | 1.1570            | 1.1800 | V    |  |

| V <sub>LVD_LV_PD</sub>  | LV supply low                 | Fall  | Untrimmed  | Yes I    | No                          | Destructi     | 1.0800   | 1.1200            | 1.1600 | V    |  |

| 0_hot (BGFP)            | voltage monitoring,           |       | Trimmed    |          |                             | ve            | 1.1140   | 1.1370            | 1.1600 | V    |  |

|                         | detecting on the              | Rise  | Untrimmed  |          |                             |               | 1.1000   | 1.1400            | 1.1800 | V    |  |

|                         | PD0 core (hot)<br>area        |       | Trimmed    |          |                             |               | 1.1340   | 1.1570            | 1.1800 | V    |  |

| V <sub>POR_HV</sub>     | HV supply power               | Fall  | Untrimmed  | Yes      | No                          | Destructi     | 2.7000   | 2.8500            | 3.0000 | V    |  |

|                         | on reset detector             |       | Trimmed    |          |                             | ve            | -        | -                 | -      | ٧    |  |

|                         |                               | Rise  | Untrimmed  |          |                             |               | 2.7500   | 2.9000            | 3.0500 | V    |  |

|                         |                               |       | Trimmed    |          |                             |               | -        | -                 | -      | V    |  |

| V <sub>LVD_IO_A_L</sub> | HV IO_A supply                | Fall  | Untrimmed  | Yes      | No                          | Destructi     | 2.7500   | 2.9230            | 3.0950 | V    |  |

| 03, 3                   | low voltage monitoring - low  |       | Trimmed    |          |                             | ve            | 2.9780   | 3.0390            | 3.1000 | ٧    |  |

|                         | range                         | Rise  | Untrimmed  |          |                             |               | 2.7800   | 2.9530            | 3.1250 | ٧    |  |

|                         |                               |       | Trimmed    |          |                             |               | 3.0080   | 3.0690            | 3.1300 | V    |  |

| V <sub>LVD_IO_A_H</sub> | HV IO_A supply                | Fall  | Trimmed    | No       | Yes                         | Destructi     | Disable  | at Start          |        |      |  |

| 13                      | low voltage monitoring - high |       |            |          |                             | ve            | 4.0600   | 4.151             | 4.2400 | V    |  |

|                         | range                         | Rise  | Trimmed    |          |                             |               | Disabled | Disabled at Start |        |      |  |

|                         |                               |       |            |          |                             |               | 4.1150   | 4.2010            | 4.3000 | V    |  |

Table continues on the next page...

- 8. e200Z4 core, 160MHz, cache enabled; e200Z4 core, 80MHz; HSM fully operational (Z0 core @80MHz) FlexRay, 5x CAN, 5x LINFlexD, 2x SPI, 1x ADC used constantly, 1xeMIOS (5 ch), Memory: 3M flash, 384K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- 9. Assuming Ta=Tj, as the device is in Stop mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes.

- 10. Internal structures hold the input voltage less than V<sub>DD\_HV\_ADC\_REF</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

- 11. This value is the total current for two ADCs.Each ADC might consume upto 2mA at max.

- 12. This assumes the default configuration of flash controller register. For more details, refer to Flash memory program and erase specifications

Table 11. Low Power Unit (LPU) Current consumption characteristics

| Symbol   | Parameter     | Conditions <sup>1</sup>                        | Min | Тур  | Max  | Unit |

|----------|---------------|------------------------------------------------|-----|------|------|------|

| LPU_RUN  | with 256K RAM | T <sub>a</sub> = 25 °C                         | _   | 10   | _    | mA   |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = OFF, SPI0 = OFF, LIN0 = OFF, CAN0 = OFF |     |      |      |      |

|          |               | T <sub>a</sub> = 85 °C                         | _   | 10.5 | _    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | T <sub>a</sub> = 105 °C                        | _   | 11   | _    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | $T_a = 125  {}^{\circ}C^{2, 2}$                | _   | _    | 26   |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

| LPU_STOP | with 256K RAM | T <sub>a</sub> = 25 °C                         | _   | 0.18 | _    | mA   |

|          |               | T <sub>a</sub> = 85 °C                         | _   | 0.60 | _    |      |

|          |               | T <sub>a</sub> = 105 °C                        | _   | 1.00 |      |      |

|          |               | T <sub>a</sub> = 125 °C <sup>2</sup>           |     | _    | 10.6 |      |

- 1. The content of the Conditions column identifies the components that draw the specific current.

- Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal

attributes

Table 12. STANDBY Current consumption characteristics

| Symbol   | Parameter    | Conditions <sup>1</sup>                 | Min | Тур | Max  | Unit |

|----------|--------------|-----------------------------------------|-----|-----|------|------|

| STANDBY0 | STANDBY with | T <sub>a</sub> = 25 °C                  | _   | 71  | _    | μΑ   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C                  | _   | 125 | 700  |      |

|          |              | T <sub>a</sub> = 105 °C                 | _   | 195 | 1225 |      |

|          |              | T <sub>a</sub> = 125 °C <sup>2, 2</sup> | _   | 314 | 2100 |      |

| STANDBY1 | STANDBY with | T <sub>a</sub> = 25 °C                  | _   | 72  | _    | μΑ   |

|          | 64K RAM      | T <sub>a</sub> = 85 °C                  | _   | 140 | 715  |      |

|          |              | T <sub>a</sub> = 105 °C                 | _   | 225 | 1275 |      |

|          |              | T <sub>a</sub> = 125 °C <sup>2</sup>    | _   | 358 | 2250 |      |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

### 4.7 Electromagnetic Compatibility (EMC) specifications

EMC measurements to IC-level IEC standards are available from NXP on request.

### 5 I/O parameters

### 5.1 AC specifications @ 3.3 V Range

Table 14. Functional Pad AC Specifications @ 3.3 V Range

| Symbol                 | · ·     | elay (ns) <sup>1</sup><br>I/H>L | Rise/Fall | Edge (ns) | Drive Load<br>(pF)     | SIUL2_MSCRn[SRC 1:0] |

|------------------------|---------|---------------------------------|-----------|-----------|------------------------|----------------------|

|                        | Min     | Max                             | Min       | Max       | 1 [                    | MSB,LSB              |

| pad_sr_hv              |         | 6/6                             |           | 1.9/1.5   | 25                     | 11                   |

| (output)               | 2.5/2.5 | 8.25/7.5                        | 0.8/0.6   | 3.25/3    | 50                     |                      |

| (output)               | 6.4/5   | 19.5/19.5                       | 3.5/2.5   | 12/12     | 200                    |                      |

|                        | 2.2/2.5 | 8/8                             | 0.55/0.5  | 3.9/3.5   | 25                     | 10                   |

|                        | 0.090   | 1.1                             | 0.035     | 1.1       | asymmetry <sup>2</sup> |                      |

|                        | 2.9/3.5 | 12.5/11                         | 1/1       | 7/6       | 50                     |                      |

|                        | 11/8    | 35/31                           | 7.7/5     | 25/21     | 200                    |                      |

|                        | 8.3/9.6 | 45/45                           | 4/3.5     | 25/25     | 50                     | 01 <sup>3</sup>      |

|                        | 13.5/15 | 65/65                           | 6.3/6.2   | 30/30     | 200                    |                      |

|                        | 13/13   | 75/75                           | 6.8/6     | 40/40     | 50                     | 00 <sup>3</sup>      |

|                        | 21/22   | 100/100                         | 11/11     | 51/51     | 200                    |                      |

| pad_i_hv/<br>pad_sr_hv |         | 2/2                             |           | 0.5/0.5   | 0.5                    | NA                   |

| (input) <sup>4</sup>   |         |                                 |           |           |                        |                      |

<sup>1.</sup> As measured from 50% of core side input to Voh/Vol of the output

#### NOTE

The specification given above is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

#### NOTE

The specification given above is measured between 20% / 80%.

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

This row specifies the min and max asymmetry between both the prop delay and the edge rates for a given PVT and 25pF load. Required for the Flexray spec.

<sup>3.</sup> Slew rate control modes

<sup>4.</sup> Input slope = 2ns

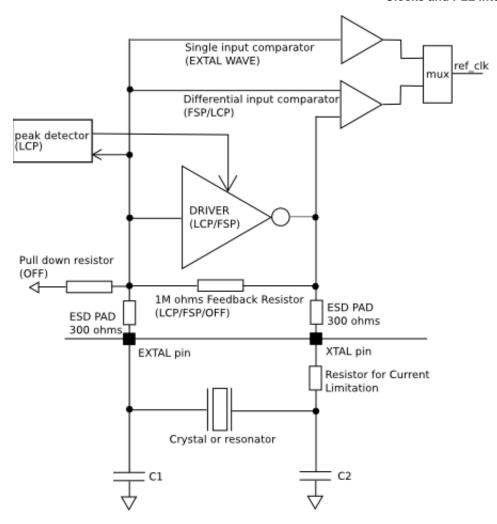

Figure 7. Oscillator connections scheme

Table 23. Main oscillator electrical characteristics

| Symbol                | Parameter                | Mode                 | Conditions                | Min   | Тур | Max | Unit |                 |

|-----------------------|--------------------------|----------------------|---------------------------|-------|-----|-----|------|-----------------|

| f <sub>xoschs</sub>   | Oscillator frequency     | FSP/LCP              |                           | 8     |     | 40  | MHz  |                 |

| 9mxoschs              | Driver                   | LCP                  |                           |       | 23  |     | mA/V |                 |

|                       | Transconduct ance        | FSP                  |                           |       | 33  |     |      |                 |

| V <sub>XOSCHS</sub>   | Oscillation<br>Amplitude | SCHS Oscillation     | LCP <sup>1, 2, 1, 2</sup> | 8 MHz |     | 1.0 |      | V <sub>PP</sub> |

|                       |                          |                      | 16 MHz                    |       | 1.0 |     |      |                 |

|                       |                          |                      | 40 MHz                    | 0.8   |     |     |      |                 |

| T <sub>XOSCHSSU</sub> | Startup time             | FSP/LCP <sup>1</sup> | 8 MHz                     |       | 2   |     | ms   |                 |

|                       |                          |                      | 16 MHz                    | 1     | 1   |     |      |                 |

|                       |                          |                      | 40 MHz                    | 1     | 0.5 |     |      |                 |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

#### Memory interfaces

Table 31. Flash memory Array Integrity and Margin Read specifications (continued)

| Symbol                 | Characteristic                                                | Min    | Typical | Max <sup>1, 1</sup>          | Units 2, 2 |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|------------|

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | _      | _       | 8192 x<br>Tperiod x<br>Nread |            |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | _       | 110.7                        | μs         |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | _       | 192.6                        | μs         |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 | _       | 356.5                        | μs         |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 | _       | 1,339.5                      | μs         |

- 1. Array Integrity times need to be calculated and is dependent on system frequency and number of clocks per read. The equation presented require Tperiod (which is the unit accurate period, thus for 200 MHz, Tperiod would equal 5e-9) and Nread (which is the number of clocks required for read, including pipeline contribution. Thus for a read setup that requires 6 clocks to read with no pipeline, Nread would equal 6. For a read setup that requires 6 clocks to read, and has the address pipeline set to 2, Nread would equal 4 (or 6 2).)

- 2. The units for Array Integrity are determined by the period of the system clock. If unit accurate period is used in the equation, the results of the equation are also unit accurate.

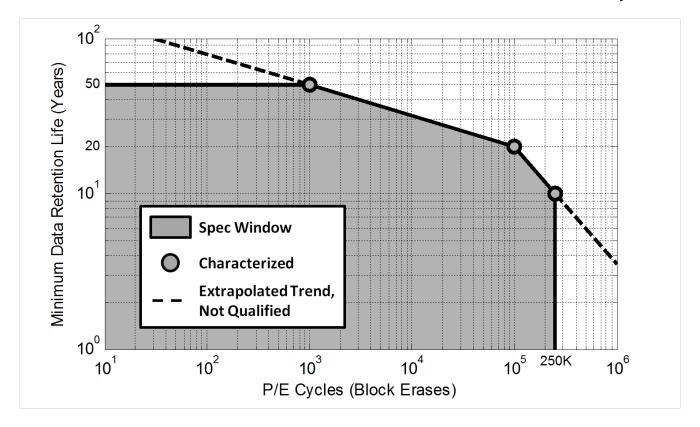

#### 6.3.3 Flash memory module life specifications

Table 32. Flash memory module life specifications

| Symbol           | Characteristic                                                                              | Conditions                        | Min     | Typical | Units         |

|------------------|---------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|---------------|

| Array P/E cycles | Number of program/erase cycles per block for 16 KB, 32 KB and 64 KB blocks. <sup>1, 1</sup> | _                                 | 250,000 | _       | P/E<br>cycles |

|                  | Number of program/erase cycles per block for 256 KB blocks. <sup>2, 2</sup>                 | _                                 | 1,000   | 250,000 | P/E<br>cycles |

| Data retention   | Minimum data retention.                                                                     | Blocks with 0 - 1,000 P/E cycles. | 50      | _       | Years         |

|                  |                                                                                             | Blocks with 100,000 P/E cycles.   | 20      | _       | Years         |

|                  |                                                                                             | Blocks with 250,000 P/E cycles.   | 10      | _       | Years         |

- 1. Program and erase supported across standard temperature specs.

- 2. Program and erase supported across standard temperature specs.

## 6.3.4 Data retention vs program/erase cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits.

# 6.3.5 Flash memory AC timing specifications

Table 33. Flash memory AC timing specifications

| Symbol             | Characteristic                                                                                                | Min | Typical                                        | Max                                             | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub>  | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.                                          | _   | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>esus</sub>  | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.                                          | _   | 16<br>plus four<br>system<br>clock<br>periods  | 20.8 plus four system clock periods             | μѕ    |

| t <sub>res</sub>   | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low.                                 | _   | _                                              | 100                                             | ns    |

| t <sub>done</sub>  | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.  | _   | _                                              | 5                                               | ns    |

| t <sub>dones</sub> | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1. | _   | 16<br>plus four<br>system<br>clock<br>periods  | 20.8 plus four system clock periods             | μs    |

Table continues on the next page...

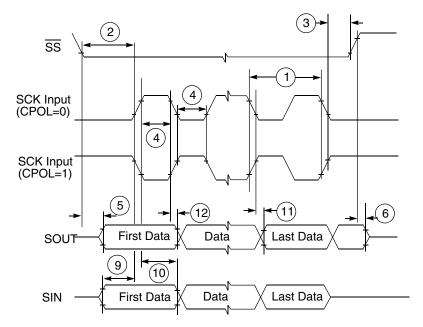

Figure 10. DSPI classic SPI timing — slave, CPHA = 0

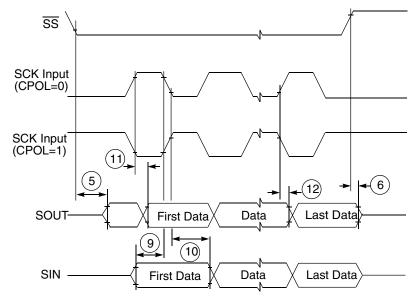

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

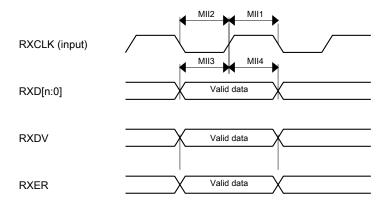

Figure 22. RMII/MII receive signal timing diagram

#### 6.4.3.2 RMII signal switching specifications

The following timing specs meet the requirements for RMII style interfaces for a range of transceiver devices.

| Num   | Description                                 | Min. | Max. | Unit            |

|-------|---------------------------------------------|------|------|-----------------|

| _     | EXTAL frequency (RMII input clock RMII_CLK) | _    | 50   | MHz             |

| RMII1 | RMII_CLK pulse width high                   | 35%  | 65%  | RMII_CLK period |

| RMII2 | RMII_CLK pulse width low                    | 35%  | 65%  | RMII_CLK period |

| RMII3 | RXD[1:0], CRS_DV, RXER to RMII_CLK setup    | 4    | _    | ns              |

| RMII4 | RMII_CLK to RXD[1:0], CRS_DV, RXER hold     | 2    | _    | ns              |

| RMII7 | RMII_CLK to TXD[1:0], TXEN invalid          | 4    | _    | ns              |

| RMII8 | RMII_CLK to TXD[1:0], TXEN valid            | _    | 15   | ns              |

Table 42. RMII signal switching specifications

### 6.4.4 SAI electrical specifications

All timing requirements are specified relative to the clock period or to the minimum allowed clock period of a device

Table 43. Master mode SAI Timing

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

#### **Debug specifications**

#### Table 45. JTAG pin AC electrical characteristics <sup>1</sup> (continued)

| #  | Symbol             | Characteristic                                         | Min | Max | Unit |

|----|--------------------|--------------------------------------------------------|-----|-----|------|

| 12 | t <sub>BSDVZ</sub> | TCK Falling Edge to Output Valid out of High Impedance | _   | 600 | ns   |

| 13 | t <sub>BSDHZ</sub> | TCK Falling Edge to Output High Impedance              | _   | 600 | ns   |

| 14 | t <sub>BSDST</sub> | Boundary Scan Input Valid to TCK Rising Edge           | 15  | _   | ns   |

| 15 | t <sub>BSDHT</sub> | TCK Rising Edge to Boundary Scan Input Invalid         | 15  | _   | ns   |

- 1. These specifications apply to JTAG boundary scan only.

- 2. This timing applies to TDI, TDO, TMS pins, however, actual frequency is limited by pad type for EXTEST instructions. Refer to pad specification for allowed transition frequency

- 3. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 4. Applies to all pins, limited by pad slew rate. Refer to IO delay and transition specification and add 20 ns for JTAG delay.

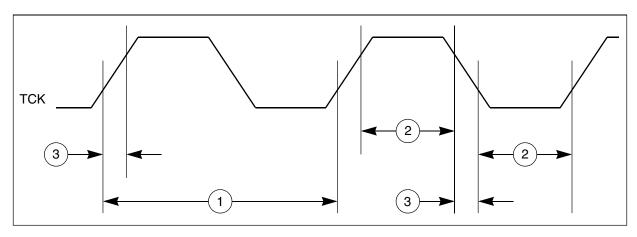

Figure 25. JTAG test clock input timing

#### Thermal attributes

| Board type        | Symbol            | Description                                                       | 176LQFP | Unit | Notes |

|-------------------|-------------------|-------------------------------------------------------------------|---------|------|-------|

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 17.8    | °C/W | 1, 3  |

| _                 | $R_{\theta JB}$   | Thermal resistance, junction to board                             | 10.9    | °C/W | 44    |

| _                 | R <sub>0JC</sub>  | Thermal resistance, junction to case                              | 8.4     | °C/W | 55    |

| _                 | $\Psi_{ m JT}$    | Thermal resistance, junction to package top                       | 0.5     | °C/W | 66    |

| _                 | Ψ <sub>ЈВ</sub>   | Thermal characterization parameter, junction to package bottom    | 0.3     | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                       | 324 MAPBGA | Unit | Notes  |

|-------------------|-------------------|-------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | $R_{\theta JA}$   | Thermal resistance, junction to ambient (natural convection)      | 31.0       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal resistance, junction to ambient (natural convection)      | 24.3       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>eJMA</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 23.5       | °C/W | 1, 3   |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)  | 20.1       | °C/W | 1,3    |

Table continues on the next page...

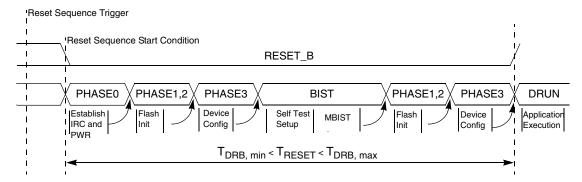

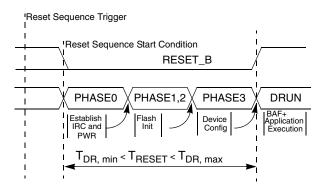

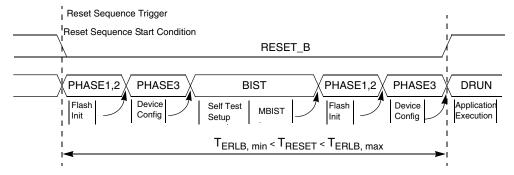

#### Reset sequence

68

Figure 32. Destructive reset sequence, BIST enabled

Figure 33. Destructive reset sequence, BIST disabled

Figure 34. External reset sequence long, BIST enabled

Figure 35. Functional reset sequence long

**Table 51. Revision History (continued)**

| Rev. No. Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. No. Date | Substantial Changes  In section: Reset pad electrical characteristics Revised table, Reset electrical characteristics Deleted note, There are some specific ports that supports TTL functionality. These ports are, PB[4], PB[5], PB[6], PB[7], PB[8], PB[9], PD[0], PD[1], PD[2], PD[3], PD[4], PD[5], PD[6], PD[7], PD[8], PD[9], PD[10], and PD[11].  In section: PORST electrical specifications In table: PORST electrical specifications Updated 'Min' value for W <sub>NFPORST</sub> In section: Peripheral operating requirements and behaviours Changed section title from Input impedance and ADC accuracy to Input equivalent circuit and ADC conversion characteristics. Revised table: ADC conversion characteristics (for 12-bit) and ADC conversion characteristics (for 10-bit) Removed table, ADC supply configurations.  In section: Analogue Comparator (CMP) electrical specifications Updated 'Max' value of IpoLS Updated 'Min' and 'Max' for V <sub>AIO</sub> and DNL Updated 'Descripton' 'Min' 'Max' od V <sub>H</sub> Updated 'Descripton' 'Min' 'Max' od V <sub>H</sub> Updated 'Descripton' 'Min' 'Max' od V <sub>H</sub> Updated 'Descripton' 'Min' 'Max' of V <sub>H</sub> Removed row for I <sub>DLS</sub> Removed row for V <sub>CMPOh</sub> and V <sub>CMPOl</sub> In section: Clocks and PLL interfaces modules In table: Main oscillator electrical characteristics V <sub>XOSCHS</sub> : Removed values for 4 MHz. T <sub>XOSCHSSU</sub> : Updated range to 8-40 MHz. In table: 18 MHz RC Oscillator electrical specifications Posc: Updated 'Max' for T <sub>Startup</sub> and T <sub>L,J,IT</sub> Removed F <sub>Untrimmed</sub> row In table: 128 KHz Internal RC oscillator electrical specifications Fosc: Updated 'Temperature dependence' and 'Supply dependence' Max values In table: 128 LHz Internal RC oscillator electrical specifications Removed Tupt (Dosch Low Level, Input Clock High Level, Power consumption, Regulator Maximum Output Current, Analog Supply, Digital Supply (V <sub>DD, LV</sub> ), Modulation Depth (Down Spread), PLL reset assertion time, and Power Consumption Removed 'Min' value for Duty Cycle at plicikout Removed 'Min' value for Lock Time in calibration mode. |

|               | <ul> <li>Added 1 Sigma Random Jitter and Total Period Jitter values for Long Term         Jitter (Interger and Fractional Mode) rows.</li> <li>In section Flash read wait state and address pipeline control settings</li> <li>In Flash Read Wait State and Address Pipeline Control: Updated APC for 40 MHz.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | Removed section: On-chip peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.