Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4                                                           |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 80MHz, 160MHz                                                            |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Number of I/O              | 178                                                                      |

| Program Memory Size        | 2MB (2M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 256K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Data Converters            | A/D 36x10b, 16x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 256-LBGA                                                                 |

| Supplier Device Package    | 256-MAPPBGA (17x17)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5745cbk1ammj6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### NOTE

All optional features (Flash memory, RAM, Peripherals) start with lowest number or address (e.g., FlexCAN0) and end at highest available number or address (e.g., MPC574xB/C have 6 CAN, ending with FlexCAN5).

| Feature                                        | MPC5745B        | MPC5744B                                                     | MPC5746B                                      | MPC5744C                  | MPC5745C                                                     | MPC5746C                                   |  |  |

|------------------------------------------------|-----------------|--------------------------------------------------------------|-----------------------------------------------|---------------------------|--------------------------------------------------------------|--------------------------------------------|--|--|

| CPUs                                           | e200z4          | e200z4                                                       | e200z4                                        | e200z4                    | e200z4                                                       | e200z4                                     |  |  |

|                                                |                 |                                                              |                                               | e200z2                    | e200z2                                                       | e200z2                                     |  |  |

| FPU                                            | e200z4          | e200z4                                                       | e200z4                                        | e200z4                    | e200z4                                                       | e200z4                                     |  |  |

| Maximum<br>Operating<br>Frequency <sup>2</sup> | 160MHz (Z4)     | 160MHz (Z4)                                                  | 160MHz (Z4)                                   | 160MHz (Z4)<br>80MHz (Z2) | 160MHz (Z4)<br>80MHz (Z2)                                    | 160MHz (Z4<br>80MHz (Z2)                   |  |  |

| Flash memory                                   | 2 MB            | 1.5 MB                                                       | 3 MB                                          | 1.5 MB                    | 2 MB                                                         | 3 MB                                       |  |  |

| EEPROM<br>support                              | E               | Emulated up to 64                                            | K                                             | E                         | Emulated up to 64                                            | <                                          |  |  |

| RAM                                            | 256 KB          | 192 KB                                                       | 384 KB<br>(Optional<br>512KB) <sup>3, 3</sup> | 192 KB                    | 256 KB                                                       | 384 KB<br>(Optional<br>512KB) <sup>3</sup> |  |  |

| ECC                                            |                 |                                                              | End t                                         | o End                     |                                                              |                                            |  |  |

| SMPU                                           |                 |                                                              | 16 e                                          | entry                     |                                                              |                                            |  |  |

| DMA                                            |                 |                                                              | 32 ch                                         | annels                    |                                                              |                                            |  |  |

| 10-bit ADC                                     |                 |                                                              | 36 Standar                                    | d channels                |                                                              |                                            |  |  |

|                                                |                 |                                                              | 32 Externa                                    | al channels               |                                                              |                                            |  |  |

| 12-bit ADC                                     |                 |                                                              | 15 Precisio                                   | n channels                |                                                              |                                            |  |  |

|                                                |                 |                                                              | 16 Standar                                    | d channels                |                                                              |                                            |  |  |

| Analog<br>Comparator                           |                 |                                                              | :                                             | 3                         |                                                              |                                            |  |  |

| BCTU                                           |                 |                                                              | -                                             | 1                         |                                                              |                                            |  |  |

| SWT                                            |                 | 1, SWT[0] <sup>4</sup>                                       |                                               |                           | 2 <sup>4</sup>                                               |                                            |  |  |

| STM                                            |                 | 1, STM[0]                                                    |                                               |                           | 2                                                            |                                            |  |  |

| PIT-RTI                                        |                 |                                                              | 16 chan                                       | nels PIT                  |                                                              |                                            |  |  |

|                                                |                 |                                                              | 1 chanr                                       | nels RTI                  |                                                              |                                            |  |  |

| RTC/API                                        |                 |                                                              |                                               | 1                         |                                                              |                                            |  |  |

| Total Timer I/O <sup>5</sup>                   |                 |                                                              | 64 ch                                         | annels                    |                                                              |                                            |  |  |

|                                                |                 |                                                              | 16-                                           | bits                      |                                                              |                                            |  |  |

| LINFlexD                                       |                 | 1                                                            |                                               |                           | 1                                                            |                                            |  |  |

|                                                | Master and      | Master and Slave (LINFlexD[0], 11 Master<br>(LINFlexD[1:11]) |                                               |                           | Master and Slave (LINFlexD[0], 15 Master<br>(LINFlexD[1:15]) |                                            |  |  |

| FlexCAN                                        | 6 with optional | CAN FD support                                               | (FlexCAN[0:5])                                | 8 with optional           | CAN FD support                                               | (FlexCAN[0:7])                             |  |  |

| DSPI/SPI                                       |                 |                                                              | 4 x [                                         | DSPI                      |                                                              |                                            |  |  |

|                                                |                 |                                                              | 4 x                                           | SPI                       |                                                              |                                            |  |  |

Table 1. MPC5746C Family Comparison1

Table continues on the next page...

# 3.2 Ordering Information

| Example                                                                  | Code                              | PC 57                 | 4      | 6      | С       | Ş      | К0         | М                 | MJ             | 6    | R        |

|--------------------------------------------------------------------------|-----------------------------------|-----------------------|--------|--------|---------|--------|------------|-------------------|----------------|------|----------|

| ·                                                                        | Qualification Status              |                       |        |        |         |        |            |                   | 1              | 1    | 1        |

|                                                                          | Power Architecture                |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Automotive Platform               |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Core Version                      |                       |        |        |         |        |            |                   |                |      |          |

| Flas                                                                     | sh Size (core dependent)          |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Product                           |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Optional fields                   |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Fab and mask indicator            |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Temperature spec.                 |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Package Code                      |                       |        |        |         |        |            |                   | ]              |      |          |

|                                                                          | CPU Frequency                     |                       |        |        |         |        |            |                   |                |      |          |

| R = Ta                                                                   | pe & Reel (blank if Tray)         |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | Due due 6 Manual au               |                       | -      |        |         |        | <b>D</b> - | - 1               | 0              |      |          |

| Qualification Status                                                     | Product Version                   | Fab and I<br>K = TSMC |        | versic | on indi | icator |            | -                 | Code<br>6 LQFP | ED   |          |

| P = Engineering samples<br>S = Automotive qualified                      | B = Single core<br>C = Dual core  | #(0,1,etc.)           |        | sion o | f the   |        |            |                   | 6 MAPB         |      |          |

|                                                                          | C = Dual core                     | maskset,              |        |        |         |        |            |                   | 4 MAPE         |      |          |

| PC = Power Architecture                                                  |                                   | maeneeu,              |        |        |         |        | Μ          | H = 10            | OMAPB          | GA   |          |

| Automotive Platform                                                      |                                   | Temperat              | ure sp | bec.   |         |        | СР         | U Fre             | quency         |      |          |

| 57 = Power Architecture in 55nm                                          | Omtion of tiolds                  | C = -40.C             |        |        |         |        |            |                   |                | unto | 120 MHz  |

|                                                                          | Optional fields                   | V = -40.C             |        |        |         |        |            |                   |                | •    | 160 MHz  |

| Core Version                                                             | Blank = No optional feature       | M = -40.C             | to +12 | 25.0   | a       |        | 0 -        |                   | sciales        | upto | 100 1012 |

| 4 = e200z4 Core Version (highest<br>core version in the case of multiple | S = HSM (Security Module)         |                       |        |        |         |        |            |                   |                |      |          |

| cores)                                                                   | F = CAN FD                        |                       |        |        |         |        |            |                   |                |      |          |

| ,                                                                        | B = HSM + CAN FD                  |                       |        |        |         |        |            |                   | Metho          |      |          |

| Flash Memory Size                                                        | R = 512K RAM                      |                       |        |        |         |        |            | = Tape<br>ink = T | and ree        |      |          |

| 4 = 1.5 MB                                                               | T = HSM + 512K RAM                |                       |        |        |         |        | Dia        |                   | lay            |      |          |

| 5 = 2 MB                                                                 | G* = CAN FD + 512K RAM            |                       |        |        |         |        |            |                   |                |      |          |

| 6 = 3 MB                                                                 | H* = HSM + CAN FD + 512K RAM      |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          | * G and H for 5746 B/C only       |                       |        |        |         |        |            |                   |                |      |          |

| Note: Not all part number con                                            | nbinations are available as produ | ction produ           | ıct    |        |         |        |            |                   |                |      |          |

|                                                                          |                                   | enon prout            |        |        |         |        |            |                   |                |      |          |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |

|                                                                          |                                   |                       |        |        |         |        |            |                   |                |      |          |

# 4 General

### 4.1 Absolute maximum ratings

#### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 6. This supply is shorted VDD\_HV\_A on lower packages.

- 7.  $T_J=150^{\circ}C$ . Assumes  $T_A=125^{\circ}C$

- Assumes maximum θJA of 2s2p board. See Thermal attributes

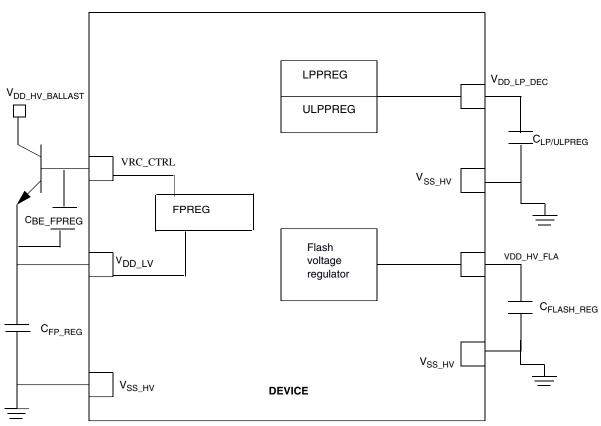

### 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Generating core supply using internal ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Low voltage detector (LVD\_FLASH) for 3.3 V flash supply (VDD\_HV\_FLA)

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

Figure 2. Voltage regulator capacitance connection

### NOTE

On BGA, VSS\_LV and VSS\_HV have been joined on substrate and renamed as VSS.

| Table 8. | Voltage regulator electrical specifications |

|----------|---------------------------------------------|

|----------|---------------------------------------------|

| Symbol                             | Parameter                                                                         | Conditions                                                                                                       | Min   | Тур              | Max  | Unit |

|------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------------------|------|------|

| C <sub>fp_reg</sub> 1              | External decoupling / stability capacitor                                         | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 1.32  | 2.2 <sup>2</sup> | 3    | μF   |

|                                    | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.03 | Ohm  |

| C <sub>lp/ulp_reg</sub>            | External decoupling / stability<br>capacitor for internal low power<br>regulators | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 0.8   | 1                | 1.4  | μF   |

|                                    | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.1  | Ohm  |

| C <sub>be_fpreg</sub> <sup>3</sup> | Capacitor in parallel to base-                                                    | BCP68 and BCP56                                                                                                  |       | 3.3              |      | nF   |

|                                    | emitter                                                                           | MJD31                                                                                                            | ]     | 4.7              |      |      |

Table continues on the next page ...

#### General

| Symbol                 | Parameter     | State | Conditions | Co             | nfiguratio                  | n             | Threshold     |                |        | Unit |

|------------------------|---------------|-------|------------|----------------|-----------------------------|---------------|---------------|----------------|--------|------|

|                        |               |       |            | Power Up       | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min           | Тур            | Max    | V    |

| V <sub>LVD_LV_PD</sub> | LV supply low | Fall  | Untrimmed  | No             | Yes                         | Function      | Disabled      | abled at Start |        |      |

| 2_cold                 |               |       | Trimmed    |                |                             | al            | 1.1400 1.1550 | 1.1550         | 1.1750 | V    |

|                        |               |       | Disabled   | abled at Start |                             |               |               |                |        |      |

|                        | device pin    |       | Trimmed    |                |                             |               | 1.1600        | 1.1750         | 1.1950 | V    |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

# 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | _   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

Table continues on the next page ...

| Symbol                      | Parameter                                  | Conditions <sup>1</sup>                                                          | Min      | Тур  | Max | Unit |

|-----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|----------|------|-----|------|

| I <sub>DD_BODY_2</sub><br>6 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | —        | _    | 246 | mA   |

|                             |                                            | $T_a = 125^{\circ}C^5$                                                           |          |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |          |      |     |      |

|                             |                                            | SYS_CLK = 160MHz                                                                 |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 105°C                                                           |          | —    | 235 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              | —        | —    | 210 | mA   |

| I <sub>DD_BODY_3</sub><br>7 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _        | _    | 181 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |          |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |          |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —        | —    | 176 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              |          | —    | 171 | mA   |

| IDD_BODY_4 <sup>8</sup>     | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> |          | —    | 264 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |          |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |          |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —        | —    | 176 | mA   |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           | —        | —    | 171 | mA   |

| I <sub>DD_STOP</sub>        | STOP mode Operating current                | $T_{a} = 125 \ ^{\circ}C^{9}$                                                    | -        | -    | 49  | mA   |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | <u> </u> | 10.6 | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           |          | 8.1  | —   |      |

|                             |                                            | $V_{DD_LV} = 1.25 V$                                                             |          |      |     |      |

|                             |                                            | T <sub>a</sub> = 25 °C                                                           |          | 4.6  | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |          |      |     |      |

### Table 10. Current consumption characteristics (continued)

Table continues on the next page...

General

| Symbol   | Parameter    | Conditions <sup>1</sup>   | Min | Тур | Max  | Unit |

|----------|--------------|---------------------------|-----|-----|------|------|

| STANDBY2 | STANDBY with | T <sub>a</sub> = 25 °C    | —   | 75  | _    | μA   |

|          | 128K RAM     | T <sub>a</sub> = 85 °C    | —   | 155 | 730  |      |

|          |              | $T_a = 105 \ ^{\circ}C$   | —   | 255 | 1350 |      |

|          |              | $T_a = 125 \ ^{\circ}C^2$ | —   | 396 | 2600 |      |

| STANDBY3 | STANDBY with | $T_a = 25 \text{ °C}$     | —   | 80  | _    | μA   |

|          | 256K RAM     | T <sub>a</sub> = 85 °C    | —   | 180 | 800  |      |

|          |              | $T_a = 105 \ ^{\circ}C$   | —   | 290 | 1425 | ]    |

|          |              | $T_a = 125 \ ^{\circ}C^2$ | —   | 465 | 2900 | 1    |

| STANDBY3 | FIRC ON      | $T_a = 25 \text{ °C}$     | _   | 500 | —    | μA   |

# Table 12. STANDBY Current consumption characteristics (continued)

1. The content of the Conditions column identifies the components that draw the specific current.

Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes

# 4.6 Electrostatic discharge (ESD) characteristics

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

### NOTE

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Symbol                | Parameter               | Conditions <sup>1</sup>        | Class | Max value <sup>2</sup> | Unit |

|-----------------------|-------------------------|--------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C         | H1C   | 2000                   | V    |

|                       | (Human Body Model)      | conforming to AEC-<br>Q100-002 |       |                        |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C         | C3A   | 500                    | V    |

|                       | (Charged Device Model)  | conforming to AEC-<br>Q100-011 |       | 750 (corners)          |      |

Table 13. ESD ratings

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. Data based on characterization results, not tested in production.

#### Peripheral operating requirements and behaviours

| Symbol              | Parameter                                      | Conditions                                                                                       |      | Value       |     |    |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-------------|-----|----|--|

|                     |                                                |                                                                                                  | Min  | Min Typ Max |     |    |  |

| V <sub>HYS</sub>    | CMOS Input Buffer hysterisis                   | —                                                                                                | 300  | —           | _   | mV |  |

| V <sub>DD_POR</sub> | Minimum supply for strong pull-down activation | -                                                                                                | —    | _           | 1.2 | V  |  |

| I <sub>OL_R</sub>   | Strong pull-down current <sup>1, 1</sup>       | $\label{eq:Device under power-on reset} $V_{DD_HV_A} = V_{DD_POR}$$V_{OL} = 0.35^*V_{DD_HV_A}$$$ | 0.2  | _           | _   | mA |  |

|                     |                                                | Device under power-on reset<br>$V_{DD_{HV}A} = V_{DD_{POR}}$<br>$V_{OL} = 0.35^*V_{DD_{HV}IO}$   | 11   | _           |     | mA |  |

| W <sub>FRST</sub>   | RESET input filtered pulse                     | —                                                                                                | _    | _           | 500 | ns |  |

| W <sub>NFRST</sub>  | RESET input not filtered pulse                 | -                                                                                                | 2000 | —           | _   | ns |  |

| ll <sub>WPU</sub> l | Weak pull-up current absolute value            | RESET pin V <sub>IN</sub> = V <sub>DD</sub>                                                      | 23   | —           | 82  | μA |  |

Table 18.

Functional reset pad electrical specifications (continued)

1. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for RESET.

# 5.6 PORST electrical specifications

#### Table 19. PORST electrical specifications

| Symbol              | Parameter                      |                                | Value |                                |    |  |  |

|---------------------|--------------------------------|--------------------------------|-------|--------------------------------|----|--|--|

|                     |                                | Min                            | Тур   | Max                            |    |  |  |

| W <sub>FPORST</sub> | PORST input filtered pulse     |                                | —     | 200                            | ns |  |  |

| WNFPORST            | PORST input not filtered pulse | 1000                           | —     | _                              | ns |  |  |

| V <sub>IH</sub>     | Input high level               | 0.65 x<br>V <sub>DD_HV_A</sub> | _     | _                              | V  |  |  |

| V <sub>IL</sub>     | Input low level                | -                              | _     | 0.35 x<br>V <sub>DD_HV_A</sub> | V  |  |  |

# 6 Peripheral operating requirements and behaviours

# 6.1 Analog

### 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

### 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                             | Min.     | Тур. | Max.                    | Unit             |

|--------------------|-------------------------------------------------------------------------|----------|------|-------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                         |          | _    | 250                     | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                          | _        | 5    | 11                      | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                    | $V_{SS}$ | -    | V <sub>IN1_CMP_RE</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1, 1</sup>                             | -47      | _    | 47                      | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2, 2</sup>                            | _        | 1    | 25                      | mV               |

|                    | • CR0[HYSTCTR] = 00                                                     | _        | 20   | 50                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>                                   | _        | 40   | 70                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 10</li> </ul>                                   | _        | 60   | 105                     | mV               |

|                    | • CR0[HYSTCTR] = 11                                                     |          |      |                         |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1,</sup><br>3, 3   | _        | -    | 250                     | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>          | _        | 5    | 21                      | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4, 4</sup> | —        | 4    |                         | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>     | —        | 100  |                         | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                                  |          |      | - <b>I</b>              |                  |

|                    | 3.3V Reference Voltage                                                  | _        | 6    | 9                       | μA               |

|                    | 5V Reference Voltage                                                    | _        | 10   | 16                      | μA               |

| INL                | 6-bit DAC integral non-linearity                                        | -0.5     | —    | 0.5                     | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                    | -0.8     | _    | 0.8                     | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_{-HV_{-}A}}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

| Symbol               | Characteristic <sup>1</sup>        | Typ <sup>2</sup> |                               | tory<br>nming <sup>3, 4</sup>   | Field Update                           |                           | te                  | Unit |

|----------------------|------------------------------------|------------------|-------------------------------|---------------------------------|----------------------------------------|---------------------------|---------------------|------|

|                      |                                    |                  | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifetime Max <sup>6</sup> |                     |      |

|                      |                                    |                  | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles         | ≤ 250,000<br>cycles |      |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time  | 43               | 100                           | 150                             | 55                                     | 500                       |                     | μs   |

| t <sub>ppgm</sub>    | Page (256 bits) program time       | 73               | 200                           | 300                             | 108                                    | 500                       |                     | μs   |

| t <sub>qppgm</sub>   | Quad-page (1024 bits) program time | 268              | 800                           | 1,200                           | 396                                    | 2,000                     |                     | μs   |

| t <sub>16kers</sub>  | 16 KB Block erase time             | 168              | 290                           | 320                             | 250                                    | 1,000                     |                     | ms   |

| t <sub>16kpgm</sub>  | 16 KB Block program time           | 34               | 45                            | 50                              | 40                                     | 1,000                     |                     | ms   |

| t <sub>32kers</sub>  | 32 KB Block erase time             | 217              | 360                           | 390                             | 310                                    | 1,200                     |                     | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time           | 69               | 100                           | 110                             | 90                                     | 1,200                     |                     | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time             | 315              | 490                           | 590                             | 420                                    | 1,600                     |                     | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time           | 138              | 180                           | 210                             | 170                                    | 1,600                     |                     | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time            | 884              | 1,520                         | 2,030                           | 1,080                                  | 4,000                     | —                   | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time          | 552              | 720                           | 880                             | 650                                    | 4,000                     | —                   | ms   |

#### Table 30. Flash memory program and erase specifications

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

### 6.3.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                | Characteristic                                               | Min | Typical | Max <sup>1, 1</sup>          | Units<br>2, 2 |

|-----------------------|--------------------------------------------------------------|-----|---------|------------------------------|---------------|

| t <sub>ai16kseq</sub> | Array Integrity time for sequential sequence on 16 KB block. | -   | _       | 512 x<br>Tperiod x<br>Nread  | _             |

| t <sub>ai32kseq</sub> | Array Integrity time for sequential sequence on 32 KB block. | _   | _       | 1024 x<br>Tperiod x<br>Nread | _             |

| t <sub>ai64kseq</sub> | Array Integrity time for sequential sequence on 64 KB block. | -   | _       | 2048 x<br>Tperiod x<br>Nread | _             |

Table continues on the next page ...

### 6.3.5 Flash memory AC timing specifications Table 33. Flash memory AC timing specifications

| Symbol             | Characteristic                                                                                                | Min | Typical                                        | Max                                             | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub>  | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.                                          | _   | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>esus</sub>  | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.                                          | _   | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>res</sub>   | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low.                                 |     | _                                              | 100                                             | ns    |

| t <sub>done</sub>  | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.  | —   | _                                              | 5                                               | ns    |

| t <sub>dones</sub> | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1. |     | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

Table continues on the next page...

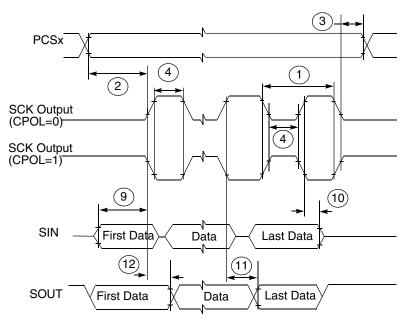

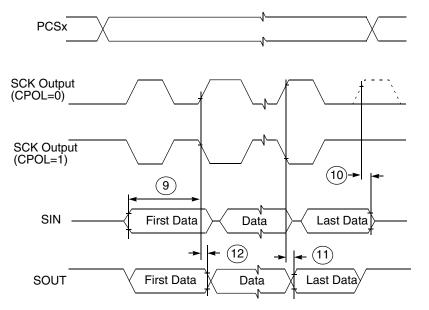

Figure 12. DSPI modified transfer format timing — master, CPHA = 0

Figure 13. DSPI modified transfer format timing — master, CPHA = 1

| Name                 | Description <sup>1</sup>                                                               | Min | Max | Unit |

|----------------------|----------------------------------------------------------------------------------------|-----|-----|------|

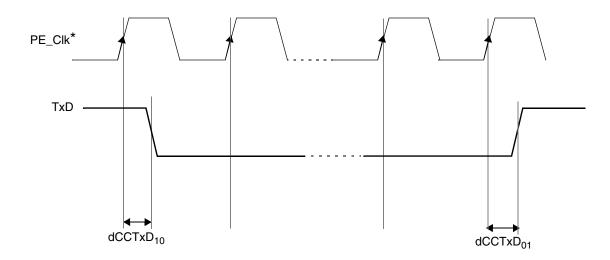

| dCCTxD <sub>01</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | _   | 25  | ns   |

| dCCTxD <sub>10</sub> | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge | —   | 25  | ns   |

#### Table 39. TxD output characteristics (continued)

1. All parameters specified for  $V_{DD_HV_IOx}$  = 3.3 V -5%, +±10%, TJ = -40 °C / 150 °C, TxD pin load maximum 25 pF.

2. For  $3.3 \text{ V} \pm 10\%$  operation, this specification is 10 ns.

\*FlexRay Protocol Engine Clock

#### Figure 20. TxD Signal propagation delays

### 6.4.2.4 RxD

| Name                 | Description <sup>1</sup>                                                             | Min     | Max | Unit |

|----------------------|--------------------------------------------------------------------------------------|---------|-----|------|

| C_CCRxD              | D Input capacitance on —<br>RxD pin                                                  |         | 7   | pF   |

| uCCLogic_1           | Threshold for detecting<br>logic high                                                | g 35 70 |     | %    |

| uCCLogic_0           | Threshold for detecting logic low                                                    | 30      | 65  | %    |

| dCCRxD <sub>01</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>rising edge  | _       | 10  | ns   |

| dCCRxD <sub>10</sub> | Sum of delay from<br>actual input to the D<br>input of the first FF,<br>falling edge | _       | 10  | ns   |

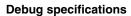

Figure 27. JTAG boundary scan timing

# 6.5.2 Nexus timing

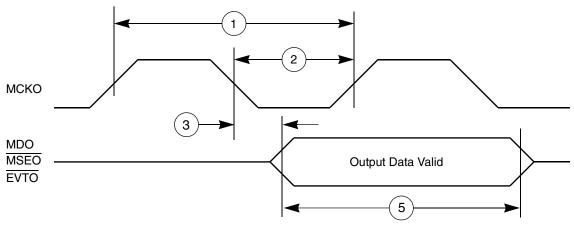

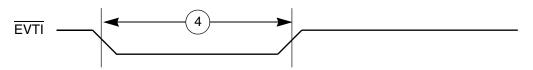

### Table 46. Nexus debug port timing 1

| No. | Symbol                                     | Parameter                                           | Condition<br>s | Min  | Max  | Unit  |

|-----|--------------------------------------------|-----------------------------------------------------|----------------|------|------|-------|

| 1   | t <sub>MCYC</sub>                          | MCKO Cycle Time                                     | —              | 15.6 | _    | ns    |

| 2   | t <sub>MDC</sub>                           | MCKO Duty Cycle                                     | —              | 40   | 60   | %     |

| 3   | t <sub>MDOV</sub>                          | MCKO Low to MDO, MSEO, EVTO Data Valid <sup>2</sup> | —              | -0.1 | 0.25 | tMCYC |

| 4   | t <sub>EVTIPW</sub>                        | EVTI Pulse Width                                    | —              | 4    | _    | tTCYC |

| 5   | t <sub>EVTOPW</sub>                        | EVTO Pulse Width                                    | —              | 1    | —    | tMCYC |

| 6   | t <sub>TCYC</sub>                          | TCK Cycle Time <sup>3</sup>                         | —              | 62.5 | _    | ns    |

| 7   | t <sub>TDC</sub>                           | TCK Duty Cycle                                      | —              | 40   | 60   | %     |

| 8   | t <sub>NTDIS</sub> ,<br>t <sub>NTMSS</sub> | TDI, TMS Data Setup Time                            | —              | 8    | _    | ns    |

Table continues on the next page...

### Table 46. Nexus debug port timing <sup>1</sup> (continued)

| No. | Symbol                                     | Parameter                     | Condition<br>s | Min | Мах | Unit |

|-----|--------------------------------------------|-------------------------------|----------------|-----|-----|------|

| 9   | t <sub>NTDIH</sub> ,<br>t <sub>NTMSH</sub> | TDI, TMS Data Hold Time       | _              | 5   | _   | ns   |

| 10  | t <sub>JOV</sub>                           | TCK Low to TDO/RDY Data Valid |                | 0   | 25  | ns   |

1. JTAG specifications in this table apply when used for debug functionality. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

- 2. For all Nexus modes except DDR mode, MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. The system clock frequency needs to be four times faster than the TCK frequency.

Figure 28. Nexus output timing

Figure 29. Nexus EVTI Input Pulse Width

#### **Thermal attributes**

| Board type | Symbol           | Description                                                                                   | 324 MAPBGA | Unit | Notes |

|------------|------------------|-----------------------------------------------------------------------------------------------|------------|------|-------|

| _          | R <sub>θJB</sub> | Thermal<br>resistance, junction<br>to board                                                   | 16.8       | °C/W | 44    |

| _          | R <sub>θJC</sub> | Thermal<br>resistance, junction<br>to case                                                    | 7.4        | °C/W | 55    |

| _          | Ψ <sub>JT</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package top<br>natural convection    | 0.2        | °C/W | 66    |

|            | Ψ <sub>JB</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>natural convection | 7.3        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 256 MAPBGA | Unit | Notes  |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 42.6       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>eJA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 26.0       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 31.0       | °C/W | 1,3    |

| Four-layer (2s2p) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 21.3       | °C/W | 1,3    |

|                   | R <sub>0JB</sub>  | Thermal<br>resistance, junction<br>to board                                | 12.8       | °C/W | 44     |

Table continues on the next page...

| Board type | Symbol           | Description                                                                                                          | 100 MAPBGA | Unit | Notes |

|------------|------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|-------|

| -          | R <sub>θJB</sub> | Thermal<br>resistance, junction<br>to board                                                                          | 10.8       | °C/W | 44    |

| -          | R <sub>θJC</sub> | Thermal<br>resistance, junction<br>to case                                                                           | 8.2        | °C/W | 55    |

|            | Ψ <sub>JT</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection)    | 0.2        | °C/W | 66    |

| _          | Ψ <sub>JB</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) | 7.8        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

# 8 Dimensions

## 8.1 Obtaining package dimensions

Package dimensions are provided in package drawing.

To find a package drawing, go to www.nxp.com and perform a keyword search for the drawing's document number:

| Package    | NXP Document Number |

|------------|---------------------|

| 100 MAPBGA | 98ASA00802D         |

Table continues on the next page...

**Pinouts**

| Package         | NXP Document Number |

|-----------------|---------------------|

| 176-pin LQFP-EP | 98ASA00698D         |

| 256 MAPBGA      | 98ASA00346D         |

| 324 MAPBGA      | 98ASA10582D         |

# 9 Pinouts

# 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

# 10 Reset sequence

# 10.1 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

# 10.1.1 Reset sequence duration

Table 49 specifies the reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter T <sub>Reset</sub>                        |     |             | Unit |    |

|-----|-------------------|-----------------------------------------------------|-----|-------------|------|----|

|     |                   |                                                     | Min | Тур<br>1, 1 | Max  |    |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled            | 6.2 | 7.3         | -    | ms |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled 110 182 - |     | us          |      |    |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot         | 6.2 | 7.3         | -    | ms |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot       | 110 | 182         | -    | us |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot      | 7   | 9           | -    | us |

Table 49. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

## 10.1.2 BAF execution duration

Following table specifies the typical BAF execution time in case BAF boot header is present at first location (Typical) and last location (worst case). Total Boot time is the sum of reset sequence duration and BAF execution time.

| BAF execution<br>duration                                | Min | Тур | Мах | Unit |

|----------------------------------------------------------|-----|-----|-----|------|

| BAF execution time<br>(boot header at first<br>location) | _   | 200 | _   | μs   |

| BAF execution time<br>(boot header at last<br>location)  | _   | _   | 320 | μs   |

Table 50. BAF execution duration

## 10.1.3 Reset sequence description

The figures in this section show the internal states of the device during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in .

With the beginning of DRUN mode, the first instruction is fetched and executed. At this point, application execution starts and the internal reset sequence is finished.

The following figures show the internal states of the device during the execution of the reset sequence and the possible states of the RESET\_B signal pin.

### NOTE

RESET\_B is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the device internal reset circuitry. A high level on this pin can only be generated by an external pullup resistor which is strong enough to overdrive the weak internal pulldown resistor. The rising edge on RESET\_B in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET\_B asserted low beyond the last Phase3.

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |      | <ul> <li>In section: Voltage monitor electrical characteristics         <ul> <li>Updated description for Low Voltage detector block.</li> <li>Added note, BCP56, MCP68 and MJD31 are guaranteed ballasts.</li> <li>In table: Voltage regulator electrical specifications                 <ul></ul></li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|          |      | <ul> <li>In section: Supply current characteristics <ul> <li>In table: Current consumption characteristics</li> <li>I<sub>DD_BODY_4</sub>: Updated SYS_CLK to 120 MHz.</li> <li>I<sub>DD_BODY_4</sub>: Updated Max for T<sub>a</sub>= 105 °C fand 85 °C )</li> <li>I<sub>dd_STOP</sub>: Added condition for T<sub>a</sub>= 105 °C and removed Max value for T<sub>a</sub>= 85 °C.</li> <li>I<sub>DD_HV_ADC_REF</sub>: Added condition for T<sub>a</sub>= 105 °C and 85 °C and removed Max value for T<sub>a</sub>= 25 °C.</li> <li>I<sub>DD_HV_FLASH</sub>: Added condition for T<sub>a</sub>= 105 °C and 85 °C</li> </ul> </li> <li>In table: Low Power Unit (LPU) Current consumption characteristics <ul> <li>LPU_RUN and LPU_STOP: Added condition for T<sub>a</sub>= 105 °C and 85 °C</li> <li>In table: STANDBY Current consumption characteristics</li> <li>Added condition for T<sub>a</sub>= 105 °C for all entries.</li> </ul> </li> </ul> |  |  |

|          |      | <ul> <li>In section: I/O parameters <ul> <li>In table: Functional Pad AC Specifications @ 3.3 V Range</li> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table: DC electrical specifications @ 3.3V Range <ul> <li>Updateded Min and Max values for Vih and Vil respectively.</li> </ul> </li> <li>In table: Functional Pad AC Specifications @ 5 V Range <ul> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table DC electrical specifications @ 5 V Range <ul> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table DC electrical specifications @ 5 V Range <ul> <li>Updated Min value for Vhys</li> </ul> </li> </ul>                                                                                                                                                                                                                                                           |  |  |

Table 51. Revision History (continued)

Table continues on the next page...