Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4                                                           |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 80MHz, 160MHz                                                            |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Number of I/O              | 129                                                                      |

| Program Memory Size        | 2MB (2M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 256K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Data Converters            | A/D 36x10b, 16x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5745cfk1amku6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 6. This supply is shorted VDD\_HV\_A on lower packages.

- 7.  $T_J=150^{\circ}C$ . Assumes  $T_A=125^{\circ}C$

- Assumes maximum θJA of 2s2p board. See Thermal attributes

### 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Generating core supply using internal ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Low voltage detector (LVD\_FLASH) for 3.3 V flash supply (VDD\_HV\_FLA)

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

#### General

- 5. 1. For VDD\_HV\_x, 1µf on each side of the chip

- a. 0.1  $\mu f$  close to each VDD/VSS pin pair.

- b. 10  $\mu f$  near for each power supply source

- c. For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as specified by CFP\_REG parameter.

- For VDD\_LV, 0.1uf close to each VDD/VSS pin pair is required. Depending on the the selected regulation mode, this

amount of capacitance will need to be subtracted from the total capacitance required by the regulator for e.g., as

specified by CFP\_REG parameter

- 6. Only applicable to ADC1

- 7. In external ballast configuration the following must be ensured during power-up and power-down (Note: If V<sub>DD\_HV\_BALLAST</sub> is supplied from the same source as VDD\_HV\_A this condition is implicitly met):

- During power-up, V<sub>DD\_HV\_BALLAST</sub> must have met the min spec of 2.25V before VDD\_HV\_A reaches the POR\_HV\_RISE min of 2.75V.

- During power-down,  $V_{DD_HV_BALLAST}$  must not drop below the min spec of 2.25V until VDD\_HV\_A is below POR\_HV\_FALL min of 2.7V.

### NOTE

For a typical configuration using an external ballast transistor with separate supply for VDD\_HV\_A and the ballast collector, a bulk storage capacitor (as defined in Table 8) is required on VDD\_HV\_A close to the device pins to ensure a stable supply voltage.

Extra care must be taken if the VDD\_HV\_A supply is also being used to power the external ballast transistor or the device is running in internal regulation mode. In these modes, the inrush current on device Power Up or on exit from Low Power Modes is significant and may case the VDD\_HV\_A voltage to drop resulting in an LVD reset event. To avoid this, the board layout should be optimized to reduce common trace resistance or additional capacitance at the ballast transistor collector (or VDD\_HV\_A pins in the case of internal regulation mode) is required. NXP recommends that customers simulate the external voltage supply circuitry.

In all circumstances, the voltage on VDD\_HV\_A must be maintained within the specified operating range (see Recommended operating conditions) to prevent LVD events.

#### General

| Symbol                 | Parameter           | State    | Conditions | Configuration |                             |               |                   | Unit     |        |   |

|------------------------|---------------------|----------|------------|---------------|-----------------------------|---------------|-------------------|----------|--------|---|

|                        |                     |          |            | Power Up      | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min               | Тур      | Max    | V |

| V <sub>LVD_LV_PD</sub> | LV supply low       | Fall     | Untrimmed  | No            | Yes                         | Function      | Disabled          | at Start |        |   |

| 2_cold                 | voltage monitoring, |          | Trimmed    | trimmed       |                             | al            | 1.1400            | 1.1550   | 1.1750 | V |

|                        | detecting at the    | the Rise | Untrimmed  |               |                             |               | Disabled at Start |          |        |   |

|                        | device pin          |          | Trimmed    |               |                             |               | 1.1600            | 1.1750   | 1.1950 | V |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

## 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | —   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

Table continues on the next page ...

General

| Symbol   | Parameter    | Conditions <sup>1</sup>   | Min | Тур | Max  | Unit |

|----------|--------------|---------------------------|-----|-----|------|------|

| STANDBY2 | STANDBY with | T <sub>a</sub> = 25 °C    | —   | 75  | _    | μA   |

|          | 128K RAM     | T <sub>a</sub> = 85 °C    | —   | 155 | 730  |      |

|          |              | $T_a = 105 \ ^{\circ}C$   | —   | 255 | 1350 |      |

|          |              | $T_a = 125 \ ^{\circ}C^2$ | —   | 396 | 2600 |      |

| STANDBY3 | STANDBY with | $T_a = 25 \text{ °C}$     | —   | 80  | _    | μA   |

|          | 256K RAM     | T <sub>a</sub> = 85 °C    | —   | 180 | 800  |      |

|          |              | $T_a = 105 \ ^{\circ}C$   | —   | 290 | 1425 | ]    |

|          |              | $T_a = 125 \ ^{\circ}C^2$ | —   | 465 | 2900 | 1    |

| STANDBY3 | FIRC ON      | $T_a = 25 \text{ °C}$     | _   | 500 | —    | μA   |

# Table 12. STANDBY Current consumption characteristics (continued)

1. The content of the Conditions column identifies the components that draw the specific current.

Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes

## 4.6 Electrostatic discharge (ESD) characteristics

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

### NOTE

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Symbol                | Parameter               | Conditions <sup>1</sup>        | Class | Max value <sup>2</sup> | Unit |

|-----------------------|-------------------------|--------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C         | H1C   | 2000                   | V    |

|                       | (Human Body Model)      | conforming to AEC-<br>Q100-002 |       |                        |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C         | C3A   | 500                    | V    |

|                       | (Charged Device Model)  | conforming to AEC-<br>Q100-011 |       | 750 (corners)          |      |

Table 13. ESD ratings

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. Data based on characterization results, not tested in production.

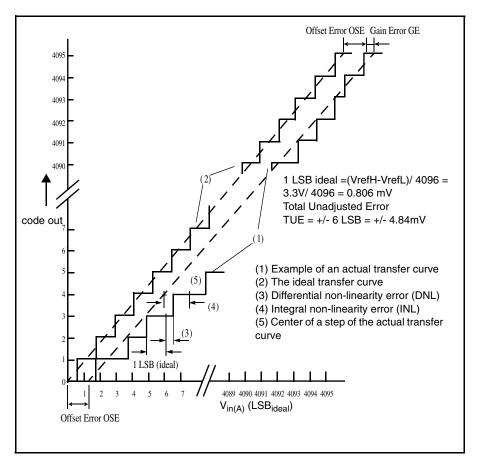

Figure 5. ADC characteristics and error definitions

### 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                             | Min.     | Тур. | Max.                    | Unit             |

|--------------------|-------------------------------------------------------------------------|----------|------|-------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                         |          | _    | 250                     | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                          | _        | 5    | 11                      | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                    | $V_{SS}$ | -    | V <sub>IN1_CMP_RE</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1, 1</sup>                             | -47      | _    | 47                      | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2, 2</sup>                            | _        | 1    | 25                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 00</li> </ul>                                   | _        | 20   | 50                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>                                   | _        | 40   | 70                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 10</li> </ul>                                   | _        | 60   | 105                     | mV               |

|                    | • CR0[HYSTCTR] = 11                                                     |          |      |                         |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1,</sup><br>3, 3   | _        | -    | 250                     | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>          | _        | 5    | 21                      | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4, 4</sup> | —        | 4    |                         | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>     | —        | 100  |                         | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                                  |          |      |                         |                  |

|                    | 3.3V Reference Voltage                                                  | _        | 6    | 9                       | μA               |

|                    | 5V Reference Voltage                                                    | _        | 10   | 16                      | μA               |

| INL                | 6-bit DAC integral non-linearity                                        | -0.5     | —    | 0.5                     | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                    | -0.8     | _    | 0.8                     | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_{-HV_{-}A}}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

#### **Clocks and PLL interfaces modules**

| Symbol          | Parameter                                   | Mode     | Conditions               | Min  | Тур | Max  | Unit |

|-----------------|---------------------------------------------|----------|--------------------------|------|-----|------|------|

|                 | Oscillator                                  | FSP      | 8 MHz                    |      | 2.2 |      | mA   |

|                 | Analog Circuit<br>supply current            |          | 16 MHz                   |      | 2.2 |      |      |

|                 |                                             |          | 40 MHz                   |      | 3.2 |      |      |

|                 |                                             | LCP      | 8 MHz                    |      | 141 |      | uA   |

|                 |                                             |          | 16 MHz                   |      | 252 |      |      |

|                 |                                             |          | 40 MHz                   |      | 518 |      |      |

| V <sub>IH</sub> | Input High<br>level CMOS<br>Schmitt trigger | EXT Wave | Oscillator<br>supply=3.3 | 1.95 |     |      | V    |

| V <sub>IL</sub> | Input low level<br>CMOS<br>Schmitt trigger  |          | Oscillator<br>supply=3.3 |      |     | 1.25 | V    |

Table 23.

Main oscillator electrical characteristics (continued)

1. Values are very dependent on crystal or resonator used and parasitic capacitance observed in the board.

2. Typ value for oscillator supply 3.3 V@27 °C

## 6.2.2 32 kHz Oscillator electrical specifications

#### Table 24. 32 kHz oscillator electrical specifications

| Symbol              | Parameter                                       | Condition | Min | Тур | Мах | Unit |

|---------------------|-------------------------------------------------|-----------|-----|-----|-----|------|

| f <sub>osc_lo</sub> | Oscillator crystal<br>or resonator<br>frequency |           | 32  |     | 40  | KHz  |

| t <sub>cst</sub>    | Crystal Start-up<br>Time <sup>1, 2</sup>        |           |     |     | 2   | S    |

1. This parameter is characterized before qualification rather than 100% tested.

2. Proper PC board layout procedures must be followed to achieve specifications.

### 6.2.3 16 MHz RC Oscillator electrical specifications Table 25. 16 MHz RC Oscillator electrical specifications

| Symbol               | Parameter                              | Conditions | Value |     | Unit |     |

|----------------------|----------------------------------------|------------|-------|-----|------|-----|

|                      |                                        |            | Min   | Тур | Max  | 1   |

| F <sub>Target</sub>  | IRC target frequency                   | —          | —     | 16  | —    | MHz |

| PTA                  | IRC frequency variation after trimming | —          | -5    | —   | 5    | %   |

| T <sub>startup</sub> | Startup time                           | —          |       | _   | 1.5  | us  |

| T <sub>STJIT</sub>   | Cycle to cycle jitter                  |            | —     | —   | 1.5  | %   |

| T <sub>LTJIT</sub>   | Long term jitter                       |            | —     | —   | 0.2  | %   |

| Symbol               | Characteristic <sup>1</sup>        | Typ <sup>2</sup> |                               | tory<br>nming <sup>3, 4</sup>   | F                                      | Field Update      |                           | Unit |

|----------------------|------------------------------------|------------------|-------------------------------|---------------------------------|----------------------------------------|-------------------|---------------------------|------|

|                      |                                    |                  | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifeti            | Lifetime Max <sup>6</sup> |      |

|                      |                                    |                  | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles | ≤ 250,000<br>cycles       |      |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time  | 43               | 100                           | 150                             | 55                                     | 500               |                           | μs   |

| t <sub>ppgm</sub>    | Page (256 bits) program time       | 73               | 200                           | 300                             | 108                                    | 500               |                           | μs   |

| t <sub>qppgm</sub>   | Quad-page (1024 bits) program time | 268              | 800                           | 1,200                           | 396                                    | 2,000             |                           | μs   |

| t <sub>16kers</sub>  | 16 KB Block erase time             | 168              | 290                           | 320                             | 250                                    | 1,000             |                           | ms   |

| t <sub>16kpgm</sub>  | 16 KB Block program time           | 34               | 45                            | 50                              | 40                                     | 1,000             |                           | ms   |

| t <sub>32kers</sub>  | 32 KB Block erase time             | 217              | 360                           | 390                             | 310                                    | 1,200             |                           | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time           | 69               | 100                           | 110                             | 90                                     | 1,200             |                           | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time             | 315              | 490                           | 590                             | 420                                    | 1,600             |                           | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time           | 138              | 180                           | 210                             | 170                                    | 1,600             |                           | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time            | 884              | 1,520                         | 2,030                           | 1,080                                  | 4,000             | —                         | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time          | 552              | 720                           | 880                             | 650                                    | 4,000             | —                         | ms   |

#### Table 30. Flash memory program and erase specifications

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

### 6.3.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                | Characteristic                                               | Min | Typical | Max <sup>1, 1</sup>          | Units<br>2, 2 |

|-----------------------|--------------------------------------------------------------|-----|---------|------------------------------|---------------|

| t <sub>ai16kseq</sub> | Array Integrity time for sequential sequence on 16 KB block. | -   | _       | 512 x<br>Tperiod x<br>Nread  | _             |

| t <sub>ai32kseq</sub> | Array Integrity time for sequential sequence on 32 KB block. | _   | _       | 1024 x<br>Tperiod x<br>Nread | _             |

| t <sub>ai64kseq</sub> | Array Integrity time for sequential sequence on 64 KB block. | -   | _       | 2048 x<br>Tperiod x<br>Nread | _             |

Table continues on the next page ...

## 6.4 Communication interfaces

## 6.4.1 DSPI timing

Table 35. DSPI electrical specifications

| No | Symbol            | Parameter               | Conditions                                          | High Spo                 | eed Mode                 | low Spe           | ed mode         | Unit |

|----|-------------------|-------------------------|-----------------------------------------------------|--------------------------|--------------------------|-------------------|-----------------|------|

|    |                   |                         |                                                     | Min                      | Max                      | Min               | Max             | 7    |

| 1  | t <sub>scк</sub>  | DSPI cycle              | Master (MTFE = 0)                                   | 25                       | _                        | 50                | _               | ns   |

|    |                   | time                    | Slave (MTFE = 0)                                    | 40                       | —                        | 60                | _               |      |

| 2  | tcsc              | PCS to SCK delay        |                                                     | 16                       | —                        | _                 | -               | ns   |

| 3  | t <sub>ASC</sub>  | After SCK<br>delay      | _                                                   | 16                       | —                        | —                 | -               | ns   |

| 4  | t <sub>SDC</sub>  | SCK duty<br>cycle       | _                                                   | t <sub>SCK</sub> /2 - 10 | t <sub>SCK</sub> /2 + 10 | —                 | -               | ns   |

| 5  | t <sub>A</sub>    | Slave access time       | SS active to SOUT valid                             | _                        | 40                       | _                 | _               | ns   |

| 6  | t <sub>DIS</sub>  | Slave SOUT disable time | <sub>SS</sub> inactive to SOUT<br>High-Z or invalid | _                        | 10                       | —                 | _               | ns   |

| 7  | t <sub>PCSC</sub> | PCSx to<br>PCSS time    | _                                                   | 13                       | —                        | —                 | _               | ns   |

| 8  | t <sub>PASC</sub> | PCSS to<br>PCSx time    |                                                     | 13                       | —                        | _                 | _               | ns   |

| 9  | t <sub>SUI</sub>  | Data setup              | Master (MTFE = 0)                                   | NA                       | —                        | 20                | _               | ns   |

|    |                   | time for<br>inputs      | Slave                                               | 2                        | —                        | 2                 | _               |      |

|    |                   | inputs                  | Master (MTFE = 1,<br>CPHA = 0)                      | 15                       | —                        | 8 <sup>1, 1</sup> | _               |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      | 15                       | —                        | 20                | —               |      |

| 10 | t <sub>HI</sub>   | Data hold               | Master (MTFE = 0)                                   | NA                       | —                        | -5                |                 | ns   |

|    |                   | time for<br>inputs      | Slave                                               | 4                        | —                        | 4                 | _               |      |

|    |                   | inputs                  | Master (MTFE = 1,<br>CPHA = 0)                      | 0                        | —                        | 11 <sup>1</sup>   | _               |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      | 0                        | —                        | -5                | -               |      |

| 11 | t <sub>SUO</sub>  | Data valid              | Master (MTFE = 0)                                   | _                        | NA                       | —                 | 4               | ns   |

|    |                   | (after SCK<br>edge)     | Slave                                               | _                        | 15                       | _                 | 23              |      |

|    |                   | euge)                   | Master (MTFE = 1,<br>CPHA = 0)                      | —                        | 4                        | —                 | 16 <sup>1</sup> |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      |                          | 4                        | _                 | 4               | 1    |

Table continues on the next page...

## 6.4.2 FlexRay electrical specifications

### 6.4.2.1 FlexRay timing

This section provides the FlexRay Interface timing characteristics for the input and output signals. It should be noted that these are recommended numbers as per the FlexRay EPL v3.0 specification, and subject to change per the final timing analysis of the device.

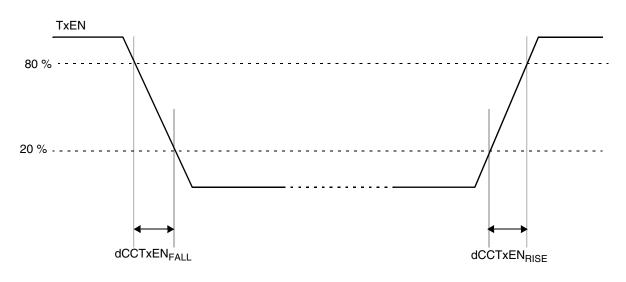

### 6.4.2.2 TxEN

#### Figure 17. TxEN signal

| Table 38. | TxEN output | characteristics <sup>1</sup> |

|-----------|-------------|------------------------------|

|-----------|-------------|------------------------------|

| Name                      | Description                                                                            | Min | Max | Unit |

|---------------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| dCCTxEN <sub>RISE25</sub> | Rise time of TxEN signal at CC                                                         | —   | 9   | ns   |

| dCCTxEN <sub>FALL25</sub> | Fall time of TxEN signal at CC                                                         | —   | 9   | ns   |

| dCCTxEN <sub>01</sub>     | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | _   | 25  | ns   |

| dCCTxEN <sub>10</sub>     | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge |     | 25  | ns   |

1. All parameters specified for  $V_{DD_HV_IOx}$  = 3.3 V -5%, +±10%, TJ = -40 °C / 150 °C, TxEN pin load maximum 25 pF

1. All parameters specified for VDD\_HV\_IOx = 3.3 V -5%, +±10%, TJ = -40 oC / 150 oC.

### 6.4.3 Ethernet switching specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

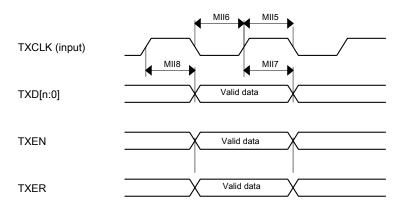

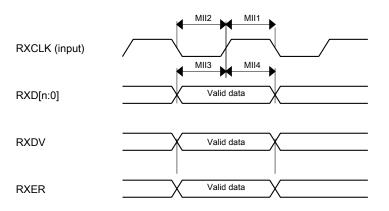

### 6.4.3.1 MII signal switching specifications

The following timing specs meet the requirements for MII style interfaces for a range of transceiver devices.

| Symbol | Description                           | Min. | Max. | Unit   |

|--------|---------------------------------------|------|------|--------|

| —      | RXCLK frequency                       | —    | 25   | MHz    |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    |      | ns     |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    |      | ns     |

| _      | TXCLK frequency                       | —    | 25   | MHz    |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | —    | ns     |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   |      | 25   | ns     |

Table 41. MII signal switching specifications

#### Figure 21. RMII/MII transmit signal timing diagram

### Figure 22. RMII/MII receive signal timing diagram

### 6.4.3.2 RMII signal switching specifications

The following timing specs meet the requirements for RMII style interfaces for a range of transceiver devices.

| Num   | Description                                 | Min. | Max. | Unit               |

|-------|---------------------------------------------|------|------|--------------------|

| —     | EXTAL frequency (RMII input clock RMII_CLK) | —    | 50   | MHz                |

| RMII1 | RMII_CLK pulse width high                   | 35%  | 65%  | RMII_CLK<br>period |

| RMII2 | RMII_CLK pulse width low                    | 35%  | 65%  | RMII_CLK<br>period |

| RMII3 | RXD[1:0], CRS_DV, RXER to RMII_CLK setup    | 4    | _    | ns                 |

| RMII4 | RMII_CLK to RXD[1:0], CRS_DV, RXER hold     | 2    | _    | ns                 |

| RMII7 | RMII_CLK to TXD[1:0], TXEN invalid          | 4    | —    | ns                 |

| RMII8 | RMII_CLK to TXD[1:0], TXEN valid            | _    | 15   | ns                 |

Table 42. RMII signal switching specifications

## 6.4.4 SAI electrical specifications

All timing requirements are specified relative to the clock period or to the minimum allowed clock period of a device

| no | Parameter           | Va  | lue | Unit |

|----|---------------------|-----|-----|------|

|    |                     | Min | Мах |      |

|    | Operating Voltage   | 2.7 | 3.6 | V    |

| S1 | SAI_MCLK cycle time | 40  | -   | ns   |

Table 43. Master mode SAI Timing

Table continues on the next page...

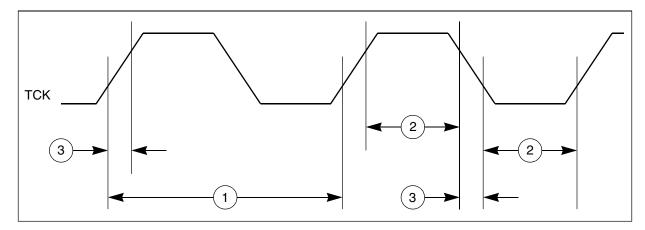

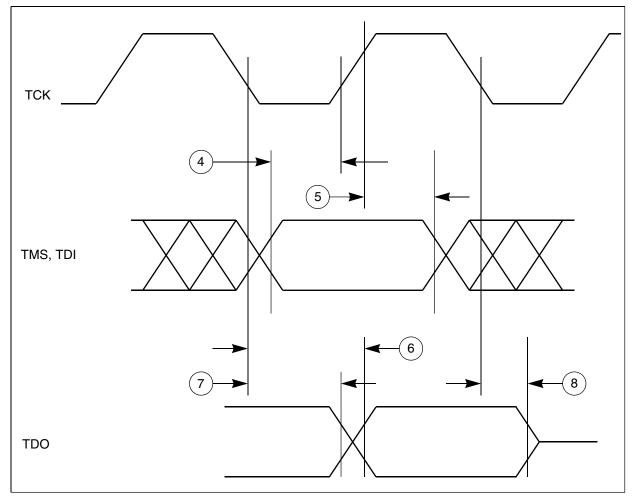

#### **Debug specifications**

### Table 45. JTAG pin AC electrical characteristics <sup>1</sup> (continued)

| #  | Symbol             | Characteristic                                            | Min | Max | Unit |

|----|--------------------|-----------------------------------------------------------|-----|-----|------|

| 12 | t <sub>BSDVZ</sub> | TCK Falling Edge to Output Valid out of High<br>Impedance | —   | 600 | ns   |

| 13 | t <sub>BSDHZ</sub> | TCK Falling Edge to Output High Impedance                 | —   | 600 | ns   |

| 14 | t <sub>BSDST</sub> | Boundary Scan Input Valid to TCK Rising Edge              | 15  |     | ns   |

| 15 | t <sub>BSDHT</sub> | TCK Rising Edge to Boundary Scan Input Invalid            | 15  | _   | ns   |

- 1. These specifications apply to JTAG boundary scan only.

- 2. This timing applies to TDI, TDO, TMS pins, however, actual frequency is limited by pad type for EXTEST instructions. Refer to pad specification for allowed transition frequency

- 3. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 4. Applies to all pins, limited by pad slew rate. Refer to IO delay and transition specification and add 20 ns for JTAG delay.

Figure 25. JTAG test clock input timing

#### Debug specifications

Figure 26. JTAG test access port timing

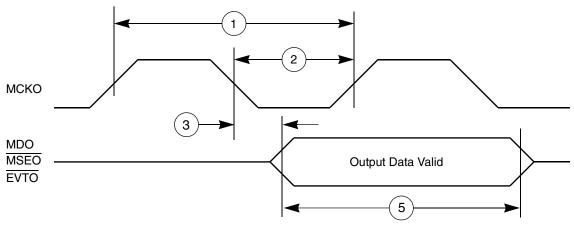

### Table 46. Nexus debug port timing <sup>1</sup> (continued)

| No. | Symbol                                     | Parameter                     | Condition<br>s | Min | Мах | Unit |

|-----|--------------------------------------------|-------------------------------|----------------|-----|-----|------|

| 9   | t <sub>NTDIH</sub> ,<br>t <sub>NTMSH</sub> | TDI, TMS Data Hold Time       | _              | 5   | _   | ns   |

| 10  | t <sub>JOV</sub>                           | TCK Low to TDO/RDY Data Valid |                | 0   | 25  | ns   |

1. JTAG specifications in this table apply when used for debug functionality. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

- 2. For all Nexus modes except DDR mode, MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. The system clock frequency needs to be four times faster than the TCK frequency.

Figure 28. Nexus output timing

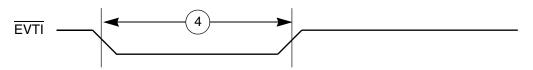

Figure 29. Nexus EVTI Input Pulse Width

#### Thermal attributes

| Board type | Symbol               | Description                                                                                                          | 256 MAPBGA | Unit | Notes |

|------------|----------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|-------|

| -          | R <sub>θJC</sub>     | Thermal<br>resistance, junction<br>to case                                                                           | 7.9        | °C/W | 55    |

|            | Ψ <sub>JT</sub>      | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection)    | 0.2        | °C/W | 66    |

| _          | R <sub>0JB_CSB</sub> | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) | 9.0        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 100 MAPBGA | Unit | Notes   |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|---------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 50.9       | °C/W | 1, 21,2 |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 27.0       | °C/W | 1,2,33  |

| Single-layer (1s) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 38.0       | °C/W | 1,3     |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 22.2       | °C/W | 1,3     |

Table continues on the next page ...

**Pinouts**

| Package         | NXP Document Number |

|-----------------|---------------------|

| 176-pin LQFP-EP | 98ASA00698D         |

| 256 MAPBGA      | 98ASA00346D         |

| 324 MAPBGA      | 98ASA10582D         |

## 9 Pinouts

## 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

## 10 Reset sequence

## 10.1 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

## 10.1.1 Reset sequence duration

Table 49 specifies the reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol            | Parameter                                      |     | T <sub>Reset</sub> |     | Unit |

|-----|-------------------|------------------------------------------------|-----|--------------------|-----|------|

|     |                   |                                                | Min | Тур<br>1, 1        | Max |      |

| 1   | T <sub>DRB</sub>  | Destructive Reset Sequence, BIST enabled       | 6.2 | 7.3                | -   | ms   |

| 2   | T <sub>DR</sub>   | Destructive Reset Sequence, BIST disabled      | 110 | 182                | -   | us   |

| 3   | T <sub>ERLB</sub> | External Reset Sequence Long, Unsecure Boot    | 6.2 | 7.3                | -   | ms   |

| 4   | T <sub>FRL</sub>  | Functional Reset Sequence Long, Unsecure Boot  | 110 | 182                | -   | us   |

| 5   | T <sub>FRS</sub>  | Functional Reset Sequence Short, Unsecure Boot | 7   | 9                  | -   | us   |

Table 49. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>In section: Reset pad electrical characteristics         <ul> <li>Revised table, Reset electrical characteristics</li> <li>Deleted note, There are some specific ports that supports TTL functionality. These ports are, PB[4], PB[5], PB[6], PB[7], PB[8], PB[9], PD[0], PD[1], PD[2], PD[3], PD[4], PD[5], PD[6], PD[7], PD[8], PD[9], PD[10], and PD[11].</li> </ul> </li> <li>In section: PORST electrical specifications         <ul> <li>In table: PORST electrical specifications</li> <li>Updated 'Min' value for W<sub>NFPORST</sub></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |      | <ul> <li>In section: Peripheral operating requirements and behaviours         <ul> <li>Changed section title from Input impedance and ADC accuracy to Input equivalent circuit and ADC conversion characteristics.</li> <li>Revised table: ADC conversion characteristics (for 12-bit) and ADC conversion characteristics (for 10-bit)</li> <li>Removed table, ADC supply configurations.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |      | <ul> <li>In section: Analogue Comparator (CMP) electrical specifications         <ul> <li>In table: Comparator and 6-bit DAC electrical specifications</li> <li>Updated 'Max' value of I<sub>DDLS</sub></li> <li>Updated 'Min' and 'Max' for V<sub>AIO</sub> and DNL</li> <li>Updated 'Descripton' 'Min' 'Max' od V<sub>H</sub></li> <li>Updated row for t<sub>DHS</sub></li> <li>Added row for t<sub>DLS</sub></li> <li>Removed row for V<sub>CMPOh</sub> and V<sub>CMPOI</sub></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |      | <ul> <li>In section: Clocks and PLL interfaces modules <ul> <li>In table: Main oscillator electrical characteristics</li> <li>V<sub>XOSCHS</sub>: Removed values for 4 MHz.</li> <li>T<sub>XOSCHSSU</sub>: Updated range to 8-40 MHz.</li> </ul> </li> <li>In table: 16 MHz RC Oscillator electrical specifications <ul> <li>Updated 'Max' for T<sub>startup</sub> and T<sub>LTJIT</sub></li> <li>Removed F<sub>Untrimmed</sub> row</li> </ul> </li> <li>In table: 128 KHz Internal RC oscillator electrical specifications <ul> <li>Fosc: Removed Uncaliberated 'Condition' and updated 'Min', 'Typ', and 'Max' for Caliberated condition</li> <li>Fosc: Updated 'Temperature dependence' and 'Supply dependence' Max values</li> </ul> </li> <li>In table: PLL electrical specifications <ul> <li>Removed entries for Input Clock Low Level, Input Clock High Level, Power consumption, Regulator Maximum Output Current, Analog Supply, Digital Supply (V<sub>DD_LV</sub>), Modulation Depth (Down Spread), PLL reset assertion time, and Power Consumption</li> <li>Removed 'Typ' value for Duty Cycle at pllclkout</li> <li>Removed 'Typ' value for Duty Cycle at pllclkout</li> <li>Removed 'Min' value for Lock Time in calibration mode.</li> </ul> </li> </ul> |

|          |      | Jitter (Interger and Fractional Mode) rows.           • In section Flash read wait state and address pipeline control settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | In Flash Read Wait State and Address Pipeline Control: Updated APC for 40 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | Removed section: On-chip peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 51. Revision History (continued)

Table continues on the next page ...

| Rev. No. | Date         | Substantial Changes                                                                                                                                                         |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 3    | 2 March 2016 | In section, Recommended operating conditions                                                                                                                                |

|          |              | Added a new Note                                                                                                                                                            |

|          |              | In section, Voltage regulator electrical characteristics                                                                                                                    |

|          |              | <ul> <li>In table, Voltage regulator electrical specifications:</li> </ul>                                                                                                  |

|          |              | <ul> <li>Added a new row for C<sub>HV_VDD_B</sub></li> <li>Added a fastrate an V</li> </ul>                                                                                 |

|          |              | <ul> <li>Added a footnote on V<sub>DD_HV_BALLAST</sub></li> <li>Added a new Note at the end of this section</li> </ul>                                                      |

|          |              |                                                                                                                                                                             |

|          |              | In section, Voltage monitor electrical characteristics                                                                                                                      |

|          |              | <ul> <li>In table, Voltage monitor electrical characteristics:</li> <li>Removed "V<sub>LVD FLASH</sub>" and "V<sub>LVD FLASH</sub> during low power mode using</li> </ul>   |

|          |              | LPBG as reference" rows                                                                                                                                                     |

|          |              | <ul> <li>Updated Fall and Rise trimmed Minimum values for V<sub>HVD_LV_cold</sub></li> </ul>                                                                                |

|          |              | In section, Supply current characteristics                                                                                                                                  |

|          |              | In table, Current consumption characteristics:                                                                                                                              |

|          |              | <ul> <li>Updated the footnote mentioned in the Condition column of I<sub>DD_STOP</sub> row</li> </ul>                                                                       |

|          |              | Updated all TBD values     In table Law Power Unit (LBL) Current consumption above staristics:                                                                              |

|          |              | <ul> <li>In table, Low Power Unit (LPU) Current consumption characteristics:</li> <li>Updated the typical value of LPU_STOP to 0.18 mA</li> </ul>                           |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | <ul> <li>In table, STANDBY Current consumption characteristics:</li> </ul>                                                                                                  |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | In section, AC specifications @ 3.3 V Range                                                                                                                                 |

|          |              | In table, Functional Pad AC Specifications @ 3.3 V Range:                                                                                                                   |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | In section, DC electrical specifications @ 3.3V Range                                                                                                                       |

|          |              | In table, DC electrical specifications @ 3.3V Range:                                                                                                                        |

|          |              | <ul> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                                                                                             |

|          |              | In section, AC specifications @ 5 V Range                                                                                                                                   |

|          |              | In table, Functional Pad AC Specifications @ 5 V Range:                                                                                                                     |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | <ul> <li>In section, DC electrical specifications @ 5 V Range</li> </ul>                                                                                                    |

|          |              | In table, DC electrical specifications @ 5 V Range:                                                                                                                         |

|          |              | <ul> <li>Updated Min and Max values for Pull_Ioh and Pull_Iol rows</li> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                          |

|          |              |                                                                                                                                                                             |

|          |              | In section, Reset pad electrical characteristics                                                                                                                            |

|          |              | <ul> <li>In table, Functional reset pad electrical specifications:</li> <li>Updated parameter column for V<sub>IH</sub>, V<sub>IL</sub> and V<sub>HYS</sub> rows</li> </ul> |

|          |              | • Updated Min and Max values for $V_{IH}$ and $V_{IL}$ rows                                                                                                                 |

|          |              |                                                                                                                                                                             |

|          |              | <ul> <li>In section, PORST electrical specifications</li> <li>In table, PORST electrical specifications:</li> </ul>                                                         |

|          |              | <ul> <li>Updated Unit and Min/Max values for V<sub>IH</sub> and V<sub>IL</sub> rows</li> </ul>                                                                              |

|          |              | <ul> <li>In section, input equivalent size it and ADC conversion sharestaristics</li> </ul>                                                                                 |

|          |              | <ul> <li>In section, Input equivalent circuit and ADC conversion characteristics</li> <li>In table, ADC conversion characteristics (for 12-bit):</li> </ul>                 |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | In table, ADC conversion characteristics (for 10-bit):                                                                                                                      |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | In section, Analog Comparator (CMP) electrical specifications                                                                                                               |

|          |              | <ul> <li>In table, Comparator and 6-bit DAC electrical specifications:</li> </ul>                                                                                           |

|          | MPC57        | • Updated Min and Max values for Valo to ±47 mV<br>46C Microcontroller Datasneet Data Sheet, Rev. 5.1, 05/2017.                                                             |

| 74       |              | NXP Semiconductors                                                                                                                                                          |

|          |              | In section, Main oscillator electrical characteristics                                                                                                                      |

#### **Revision History**

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                        |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 5.1  | 22 May 2017 | Removed the Introduction section from Section 4 "General".                                                                                                                                                                 |

|          |             | <ul> <li>In AC Specifications@3.3V section, removed note related to Cz results and added two<br/>notes.</li> </ul>                                                                                                         |

|          |             | <ul> <li>In AC Specifications@5V section, added two notes.</li> </ul>                                                                                                                                                      |

|          |             | <ul> <li>In ADC Electrical Specifications section, added spec value of "ADC Analog Pad" at Max<br/>leakage (standard channel)@ 105 C T<sub>A</sub> in "ADC conversion characteristics (for 10-bit)"<br/>table.</li> </ul>  |

|          |             | <ul> <li>In PLL Electrical Specifications section, updated the first footnote of "Jitter calculation"<br/>table.</li> </ul>                                                                                                |

|          |             | <ul> <li>In Analog Comparator Electrical Specifications section, updated the TDLS (propagation<br/>delay, low power mode) max value in "Comparator and 6-bit DAC electrical<br/>specifications" table to 21 us.</li> </ul> |

|          |             | <ul> <li>In Recommended Operating Conditions section, updated the footnote link to T<sub>A</sub> in<br/>"Recommended operating conditions (V DD_HV_x = 5V)" table.</li> </ul>                                              |

Table 51. Revision History (continued)