Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processore20024Core Size32-Bit Single-CoreSped120MHzConnectivityCANbus, Ethernet, FlexRay, I°C, LINbus, SPIProjenarisDMA, I°S, POR, WDTNumber of I/O129Program Memory SizeMB (SM x 8)PROM Size64K x 8RAM Size04K x 8Voltage - Supply (Vcc/Vdb)315V ~ 5.5VData ConvertersAND 36x10b, 16x12bOperating Temperature-40°C ~ 105°C (TA)Mounting Type1.9°C ~ 105°C (TA)Prokage / Case316-QIP Exposed PadSupplier Device Package76-LQF Package / CaseProchase URL1.6°LP Exposed PadPurchase URLhttps://www.exfl.com/product-detail/nzp-semiconductors/spC5746bftAutvu2 |                            |                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPIPeripheralsDMA, I²S, POR, WDTNumber of I/O129Program Memory Size3MB (3M x 8)Program Memory TypeFLASHEEPROM Size64K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature4.0°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadNon to the Det Met Met Met Met Met Met Met Met Met M                                                                                                                | Product Status             | Active                                                                   |

| Speed120MHzConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPIPeripheralsDMA, I²S, POR, WDTNumber of I/O129Program Memory Size3MB (3M x 8)Program Memory TypeFLASHEEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator Type-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed Pad                                                                                                                                                                                                            | Core Processor             | e200z4                                                                   |

| ConnectivityCANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPIPeripheralsDMA, I <sup>2</sup> S, POR, WDTNumber of I/O129Program Memory Size3MB (3M x 8)Program Memory TypeFLASHEEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                         | Core Size                  | 32-Bit Single-Core                                                       |

| PeripheralsDMA, I²S, POR, WDTNumber of I/O129Program Memory Size3MB (3M x 8)Program Memory TypeFLASHEEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed Pad                                                                                                                                                                                                                                                 | Speed                      | 120MHz                                                                   |

| Number of I/O129Program Memory Size3MB (3M × 8)Program Memory TypeFLASHEEPROM Size64K × 8RAM Size384K × 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed Pad                                                                                                                                                                                                                                                                               | Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Program Memory Size3MB (3M x 8)Program Memory TypeFLASHEEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                       | Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Program Memory TypeFLASHEEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed Pad                                                                                                                                                                                                                                                                                                                             | Number of I/O              | 129                                                                      |

| EEPROM Size64K x 8RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                              | Program Memory Size        | 3MB (3M × 8)                                                             |

| RAM Size384K x 8Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)3.15V ~ 5.5VData ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                | EEPROM Size                | 64K x 8                                                                  |

| Data ConvertersA/D 36x10b, 16x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                      | RAM Size                   | 384K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Operating Temperature     -40°C ~ 105°C (TA)       Mounting Type     Surface Mount       Package / Case     176-LQFP Exposed Pad       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | A/D 36x10b, 16x12b                                                       |

| Mounting TypeSurface MountPackage / Case176-LQFP Exposed PadSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Oscillator Type            | Internal                                                                 |

| Package / Case     176-LQFP Exposed Pad       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Supplier Device Package 176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Package / Case             | 176-LQFP Exposed Pad                                                     |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746bfk1avku2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | 176-LQFP (24x24)                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746bfk1avku2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Family comparison

### Table 1. MPC5746C Family Comparison1 (continued)

| Feature                                                      | MPC5745B    | MPC5744B    | MPC5746B            | MPC5744C           | MPC5745C    | MPC5746C                         |  |  |  |

|--------------------------------------------------------------|-------------|-------------|---------------------|--------------------|-------------|----------------------------------|--|--|--|

| l <sup>2</sup> C                                             | 4           | 4           | 4                   |                    | 4           |                                  |  |  |  |

| SAI/I <sup>2</sup> S                                         | 3           | 3           | 3                   |                    | 3           |                                  |  |  |  |

| FXOSC                                                        |             |             | 8 - 40              | ) MHz              |             |                                  |  |  |  |

| SXOSC                                                        |             |             | 32                  | KHz                |             |                                  |  |  |  |

| FIRC                                                         |             |             | 16                  | MHz                |             |                                  |  |  |  |

| SIRC                                                         |             |             | 128                 | KHz                |             |                                  |  |  |  |

| FMPLL                                                        |             |             |                     | 1                  |             |                                  |  |  |  |

| Low Power Unit<br>(LPU)                                      |             |             | Y                   | es                 |             |                                  |  |  |  |

| FlexRay 2.1<br>(dual channel)                                | Yes, 128 MB | Yes, 128 MB | Yes, 128 MB         |                    | Yes, 128 MB |                                  |  |  |  |

| Ethernet (RMII,<br>MII + 1588, Muti<br>queue AVB<br>support) | 1           | 1           | 1                   | 1                  |             |                                  |  |  |  |

| CRC                                                          |             | 1           |                     |                    |             |                                  |  |  |  |

| MEMU                                                         |             |             | 2                   | 2                  |             |                                  |  |  |  |

| STCU2                                                        |             |             |                     | 1                  |             |                                  |  |  |  |

| HSM-v2<br>(security)                                         |             |             | Opti                | onal               |             |                                  |  |  |  |

| Censorship                                                   |             |             | Y                   | es                 |             |                                  |  |  |  |

| FCCU                                                         |             |             |                     | 1                  |             |                                  |  |  |  |

| Safety level                                                 |             |             | Specific functions  | ASIL-B certifiable |             |                                  |  |  |  |

| User MBIST                                                   |             |             | Y                   | es                 |             |                                  |  |  |  |

| I/O Retention in<br>Standby                                  |             |             | Y                   | es                 |             |                                  |  |  |  |

| GPIO <sup>6</sup>                                            |             |             | Up to 264 GPI an    | d up to 246 GPIO   |             |                                  |  |  |  |

| Debug                                                        |             |             | JTA                 | GC,                |             |                                  |  |  |  |

|                                                              |             |             | cJT                 | AG                 |             |                                  |  |  |  |

| Nexus                                                        |             | Z4 N3+ (C   | Only available on 3 | 24BGA (developm    | ent only))  |                                  |  |  |  |

|                                                              |             | Z2 N3+ (C   | Only available on 3 | 24BGA (developm    | ent only))  |                                  |  |  |  |

| Packages                                                     | 176 LQFP-EP | 176 LQFP-EP | 176 LQFP-EP         | 176 LQFP-EP        | 176 LQFP-EP | 176 LQFP-EP                      |  |  |  |

|                                                              | 256 BGA     | 256 BGA     | 256 BGA             | 256 BGA            | 256 BGA     | 256 BGA,                         |  |  |  |

|                                                              | 100 BGA     | 100 BGA     | 100 BGA             | 100 BGA            | 100 BGA     | 324 BGA<br>(development<br>only) |  |  |  |

|                                                              |             |             |                     |                    |             | 100 BGA                          |  |  |  |

1. Feature set dependent on selected peripheral multiplexing, table shows example. Peripheral availability is package dependent.

- 2. Based on 125°C ambient operating temperature and subject to full device characterization.

- 3. Contact NXP representative for part number

- 4. Additional SWT included when HSM option selected

- 5. See device datasheet and reference manual for information on to timer channel configuration and functions.

- 6. Estimated I/O count for largest proposed packages based on multiplexing with peripherals.

# 3.2 Ordering Information

| Example                                                                  | Code                              | PC 57                                                                   | 4      | 6      | С       | Ş      | К0         | М                 | MJ      | 6    | R        |

|--------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------|--------|--------|---------|--------|------------|-------------------|---------|------|----------|

| ·                                                                        | Qualification Status              |                                                                         |        |        |         |        |            |                   | 1       | 1    | 1        |

|                                                                          | Power Architecture                |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          |                                   |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Automotive Platform               |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Core Version                      |                                                                         |        |        |         |        |            |                   |         |      |          |

| Flas                                                                     | sh Size (core dependent)          |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Product                           |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Optional fields                   |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Fab and mask indicator            |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Temperature spec.                 |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Package Code                      |                                                                         |        |        |         |        |            |                   | ]       |      |          |

|                                                                          | CPU Frequency                     |                                                                         |        |        |         |        |            |                   |         |      |          |

| R = Ta                                                                   | pe & Reel (blank if Tray)         |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | Due due 6 Manual au               |                                                                         | -      |        |         |        | <b>D</b> - | - 1               | 0       |      |          |

| Qualification Status                                                     | Product Version                   | Fab and I<br>K = TSMC                                                   |        | versic | on indi | icator |            | -                 | Code    | ED   |          |

| P = Engineering samples<br>S = Automotive qualified                      | B = Single core<br>C = Dual core  | K = TSMC FabKU = 176 LQFP EP#(0,1,etc.) = Version of theMJ = 256 MAPBGA |        |        |         |        |            |                   |         |      |          |

|                                                                          | C = Dual core                     | maskset,                                                                |        |        |         |        |            |                   | 4 MAPE  |      |          |

| PC = Power Architecture                                                  |                                   | maeneeu,                                                                |        |        |         |        | Μ          | H = 10            | OMAPB   | GA   |          |

| Automotive Platform                                                      |                                   | Temperat                                                                | ure sp | bec.   |         |        | СР         | U Fre             | quency  |      |          |

| 57 = Power Architecture in 55nm                                          | Omtion of tiolds                  | C = -40.C                                                               |        |        |         |        |            |                   |         | unto | 120 MHz  |

|                                                                          | Optional fields                   | V = -40.C                                                               |        |        |         |        |            |                   |         | •    | 160 MHz  |

| Core Version                                                             | Blank = No optional feature       | M = -40.C                                                               | to +12 | 25.0   | a       |        | 0 -        |                   | sciales | upto | 100 1012 |

| 4 = e200z4 Core Version (highest<br>core version in the case of multiple | S = HSM (Security Module)         |                                                                         |        |        |         |        |            |                   |         |      |          |

| cores)                                                                   | F = CAN FD                        |                                                                         |        |        |         |        |            |                   |         |      |          |

| ,                                                                        | B = HSM + CAN FD                  |                                                                         |        |        |         |        |            |                   | Metho   |      |          |

| Flash Memory Size                                                        | R = 512K RAM                      |                                                                         |        |        |         |        |            | = Tape<br>ink = T | and ree |      |          |

| 4 = 1.5 MB                                                               | T = HSM + 512K RAM                |                                                                         |        |        |         |        | Dia        |                   | lay     |      |          |

| 5 = 2 MB                                                                 | G* = CAN FD + 512K RAM            |                                                                         |        |        |         |        |            |                   |         |      |          |

| 6 = 3 MB                                                                 | H* = HSM + CAN FD + 512K RAM      |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          | * G and H for 5746 B/C only       |                                                                         |        |        |         |        |            |                   |         |      |          |

| Note: Not all part number con                                            | nbinations are available as produ | ction produ                                                             | ıct    |        |         |        |            |                   |         |      |          |

|                                                                          |                                   | enon prout                                                              |        |        |         |        |            |                   |         |      |          |

|                                                                          |                                   |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          |                                   |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          |                                   |                                                                         |        |        |         |        |            |                   |         |      |          |

|                                                                          |                                   |                                                                         |        |        |         |        |            |                   |         |      |          |

# 4 General

## 4.1 Absolute maximum ratings

### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

| Symbol                                                                                   | Parameter                                                                          | Conditions <sup>1</sup>                                                                 | Min         | Max                                                                                            | Unit |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------|------|

| $\begin{array}{c} V_{DD\_HV\_A},  V_{DD\_HV\_B}, \\ V_{DD\_HV\_C}{}^{2,  3} \end{array}$ | 3.3 V - 5. 5V input/output supply voltage                                          |                                                                                         | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_FLA</sub> <sup>4, 5</sup>                                                   | 3.3 V flash supply voltage (when supplying from an external source in bypass mode) |                                                                                         | -0.3        | 3.63                                                                                           | V    |

| V <sub>DD_LP_DEC</sub> <sup>6</sup>                                                      | Decoupling pin for low power regulators <sup>7</sup>                               | _                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>DD_HV_ADC1_REF</sub> <sup>8</sup>                                                 | 3.3 V / 5.0 V ADC1 high reference voltage                                          | —                                                                                       | -0.3        | 6                                                                                              | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub>                                       | 3.3 V to 5.5V ADC supply voltage                                                   | _                                                                                       | -0.3        | 6.0                                                                                            | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub>                                       | 3.3V to 5.5V ADC supply ground                                                     | _                                                                                       | -0.1        | 0.1                                                                                            | V    |

| V <sub>DD_LV</sub> <sup>9, 10, 10, 11, 11, 12</sup>                                      | Core logic supply voltage                                                          | _                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>INA</sub>                                                                         | Voltage on analog pin with respect to ground (V <sub>SS_HV</sub> )                 | _                                                                                       | -0.3        | Min (V <sub>DD_HV_x</sub> ,<br>V <sub>DD_HV_ADCx</sub> ,<br>V <sub>DD_ADCx_REF</sub> )<br>+0.3 | V    |

| V <sub>IN</sub>                                                                          | Voltage on any digital pin with respect to ground ( $V_{SS_HV}$ )                  | Relative to<br>V <sub>DD_HV_A</sub> ,<br>V <sub>DD_HV_B</sub> ,<br>V <sub>DD_HV_C</sub> | -0.3        | V <sub>DD_HV_x</sub> + 0.3                                                                     | V    |

| I <sub>INJPAD</sub>                                                                      | Injected input current on any pin during overload condition                        | Always                                                                                  | -5          | 5                                                                                              | mA   |

| I <sub>INJSUM</sub>                                                                      | Absolute sum of all injected input currents during overload condition              | _                                                                                       | -50         | 50                                                                                             | mA   |

| T <sub>ramp</sub>                                                                        | Supply ramp rate                                                                   | _                                                                                       | 0.5 V / min | 100V/ms                                                                                        | —    |

| T <sub>A</sub> <sup>13</sup>                                                             | Ambient temperature                                                                | —                                                                                       | -40         | 125                                                                                            | °C   |

| T <sub>STG</sub>                                                                         | Storage temperature                                                                | _                                                                                       | -55         | 165                                                                                            | °C   |

| Table 5. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

- 1. All voltages are referred to VSS\_HV unless otherwise specified

- 2. VDD\_HV\_B and VDD\_HV\_C are common together on the 176 LQFP-EP package.

- Allowed V<sub>DD\_HV\_x</sub> = 5.5–6.0 V for 60 seconds cumulative time with no restrictions, for 10 hours cumulative time device in reset, T<sub>J</sub>= 150 °C, remaining time at or below 5.5 V.

- 4. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 5. VDD\_HV\_FLA must be disconnected from ANY power sources when VDD\_HV\_A = 5V

- 6. This pin should be decoupled with low ESR 1  $\mu$ F capacitor.

- 7. Not available for input voltage, only for decoupling internal regulators

- 8. 10-bit ADC does not have dedicated reference and its reference is bonded to 10-bit ADC supply(VDD\_HV\_ADC0) inside the package.

- Allowed 1.45 1.5 V for 60 seconds cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time as defined in footnotes 10 and 11.

- 10. Allowed 1.38 1.45 V- for 10 hours cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time as defined in footnote 11.

- 11. 1.32 1.38 V range allowed periodically for supply with sinusoidal shape and average supply value below 1.326 V at maximum T<sub>J</sub> = 150 °C.

- 12. If HVD on core supply (V<sub>HVD LV x</sub>) is enabled, it will generate a reset when supply goes above threshold.

- 13.  $T_J=150^{\circ}C$ . Assumes  $T_A=125^{\circ}C$

- Assumes maximum θJA for 2s2p board. See Thermal attributes

#### General

| Symbol                 | Parameter                  | State | Conditions | Configuration |                             |               | Threshold U |                  |        | Unit |  |

|------------------------|----------------------------|-------|------------|---------------|-----------------------------|---------------|-------------|------------------|--------|------|--|

|                        |                            |       |            | Power Up      | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min         | Тур              | Max    | V    |  |

| V <sub>LVD_LV_PD</sub> | LV supply low              | Fall  | Untrimmed  | No            | Yes                         | Function      | Disabled    | isabled at Start |        |      |  |

| 2_cold                 | 2_cold voltage monitoring, |       | Trimmed    |               |                             | al            | 1.1400      | 1.1550           | 1.1750 | V    |  |

|                        |                            | Rise  | Untrimmed  |               |                             |               | Disabled    | at Start         |        |      |  |

|                        | device pin                 |       | Trimmed    |               |                             |               | 1.1600      | 1.1750           | 1.1950 | V    |  |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

## 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | _   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

Table continues on the next page ...

- e200Z4 core, 160MHz, cache enabled; e200Z4 core, 80MHz; HSM fully operational (Z0 core @80MHz) FlexRay, 5x CAN, 5x LINFlexD, 2x SPI, 1x ADC used constantly, 1xeMIOS (5 ch), Memory: 3M flash, 384K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- 9. Assuming Ta=Tj, as the device is in Stop mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes.

- 10. Internal structures hold the input voltage less than V<sub>DD\_HV\_ADC\_REF</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

- 11. This value is the total current for two ADCs.Each ADC might consume upto 2mA at max.

- 12. This assumes the default configuration of flash controller register. For more details, refer to Flash memory program and erase specifications

Table 11. Low Power Unit (LPU) Current consumption characteristics

| Symbol   | Parameter     | Conditions <sup>1</sup>                        | Min | Тур  | Мах  | Unit |

|----------|---------------|------------------------------------------------|-----|------|------|------|

| LPU_RUN  | with 256K RAM | $T_a = 25 \text{ °C}$                          | -   | 10   | —    | mA   |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = OFF, SPI0 = OFF, LIN0 = OFF, CAN0 = OFF |     |      |      |      |

|          |               | T <sub>a</sub> = 85 °C                         | —   | 10.5 | —    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | T <sub>a</sub> = 105 °C                        | —   | 11   | —    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | $T_a = 125 \ ^{\circ}C^{2, 2}$                 | —   | —    | 26   |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

| LPU_STOP | with 256K RAM | $T_a = 25 \text{ °C}$                          | —   | 0.18 | —    | mA   |

|          |               | T <sub>a</sub> = 85 °C                         | —   | 0.60 | —    |      |

|          |               | T <sub>a</sub> = 105 °C                        | —   | 1.00 |      |      |

|          |               | $T_{a} = 125 \ ^{\circ}C^{2}$                  | —   | _    | 10.6 |      |

- 1. The content of the Conditions column identifies the components that draw the specific current.

- Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes

Table 12. STANDBY Current consumption characteristics

| Symbol   | Parameter    | Conditions <sup>1</sup>       | Min | Тур | Max  | Unit |

|----------|--------------|-------------------------------|-----|-----|------|------|

| STANDBY0 | STANDBY with | T <sub>a</sub> = 25 °C        | —   | 71  | —    | μA   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C        | —   | 125 | 700  |      |

|          |              | T <sub>a</sub> = 105 °C       | —   | 195 | 1225 |      |

|          |              | $T_a = 125 \text{ °C}^{2, 2}$ | —   | 314 | 2100 |      |

| STANDBY1 | STANDBY with | $T_a = 25 \text{ °C}$         | —   | 72  |      | μA   |

|          | 64K RAM      | T <sub>a</sub> = 85 °C        | —   | 140 | 715  |      |

|          |              | T <sub>a</sub> = 105 °C       | —   | 225 | 1275 |      |

|          |              | $T_a = 125 \ ^{\circ}C^2$     | —   | 358 | 2250 | 1    |

Table continues on the next page...

#### Peripheral operating requirements and behaviours

| Symbol              | Parameter                                      | Conditions                                                                                       |      | Value |     |    |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-------|-----|----|--|

|                     |                                                |                                                                                                  | Min  | Тур   | Max |    |  |

| V <sub>HYS</sub>    | CMOS Input Buffer hysterisis                   | —                                                                                                | 300  | —     | _   | mV |  |

| V <sub>DD_POR</sub> | Minimum supply for strong pull-down activation | -                                                                                                | —    | _     | 1.2 | V  |  |

| I <sub>OL_R</sub>   | Strong pull-down current <sup>1, 1</sup>       | $\label{eq:Device under power-on reset} $V_{DD_HV_A} = V_{DD_POR}$$V_{OL} = 0.35^*V_{DD_HV_A}$$$ | 0.2  | _     |     | mA |  |

|                     |                                                | Device under power-on reset<br>$V_{DD_{HV}A} = V_{DD_{POR}}$<br>$V_{OL} = 0.35^*V_{DD_{HV}IO}$   | 11   | _     |     | mA |  |

| W <sub>FRST</sub>   | RESET input filtered pulse                     | —                                                                                                | _    | _     | 500 | ns |  |

| W <sub>NFRST</sub>  | RESET input not filtered pulse                 | -                                                                                                | 2000 | —     | _   | ns |  |

| ll <sub>WPU</sub> l | Weak pull-up current absolute value            | RESET pin V <sub>IN</sub> = V <sub>DD</sub>                                                      | 23   | —     | 82  | μA |  |

Table 18.

Functional reset pad electrical specifications (continued)

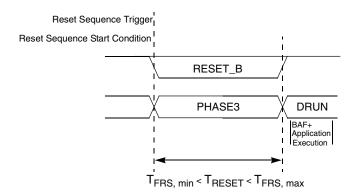

1. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for RESET.

# 5.6 PORST electrical specifications

### Table 19. PORST electrical specifications

| Symbol              | Parameter                      |                                | Value |                                |    |  |

|---------------------|--------------------------------|--------------------------------|-------|--------------------------------|----|--|

|                     |                                | Min                            | Тур   | Max                            |    |  |

| W <sub>FPORST</sub> | PORST input filtered pulse     |                                | —     | 200                            | ns |  |

| WNFPORST            | PORST input not filtered pulse | 1000                           | —     | _                              | ns |  |

| V <sub>IH</sub>     | Input high level               | 0.65 x<br>V <sub>DD_HV_A</sub> | _     | _                              | V  |  |

| V <sub>IL</sub>     | Input low level                | -                              | _     | 0.35 x<br>V <sub>DD_HV_A</sub> | V  |  |

# 6 Peripheral operating requirements and behaviours

## 6.1 Analog

## 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Analog

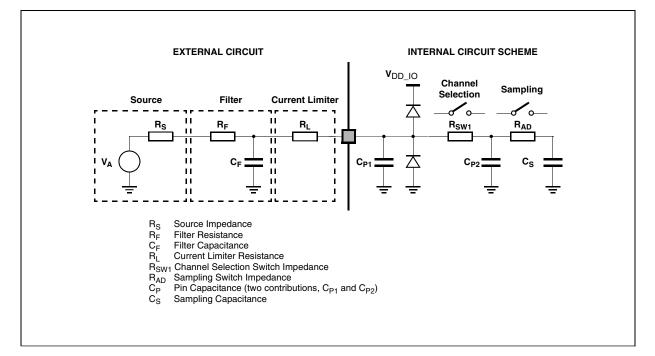

## 6.1.1.1 Input equivalent circuit and ADC conversion characteristics

### Figure 6. Input equivalent circuit

## NOTE

The ADC performance specifications are not guaranteed if two ADCs simultaneously sample the same shared channel.

Table 20. ADC conversion characteristics (for 12-bit)

| Symbol                         | Parameter                                                                                                         | Conditions                             | Min              | Typ <sup>1</sup> | Max  | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------|------|

| f <sub>CK</sub>                | ADC Clock frequency (depends on<br>ADC configuration) (The duty cycle<br>depends on AD_CK <sup>2</sup> frequency) | _                                      | 15.2             | 80               | 80   | MHz  |

| f <sub>s</sub>                 | Sampling frequency                                                                                                | 80 MHz                                 | —                |                  | 1.00 | MHz  |

| t <sub>sample</sub>            | Sample time <sup>3</sup>                                                                                          | 80 MHz@ 100 ohm source impedance       | 250              | —                | _    | ns   |

| t <sub>conv</sub>              | Conversion time <sup>4</sup>                                                                                      | 80 MHz                                 | 700              | _                | —    | ns   |

| t <sub>total_conv</sub>        | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard and extended channels)                | 80 MHz                                 | 1.5 <sup>5</sup> | _                | _    | μs   |

|                                | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for precision channels)                            |                                        | 1                | _                |      |      |

| C <sub>S</sub> <sup>6, 6</sup> | ADC input sampling capacitance                                                                                    | —                                      | —                | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>6</sup>   | ADC input pin capacitance 1                                                                                       | —                                      | —                | _                | 5    | pF   |

| C <sub>P2</sub> <sup>6</sup>   | ADC input pin capacitance 2                                                                                       | —                                      | _                | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>6</sup>  | Internal resistance of analog                                                                                     | $V_{REF}$ range = 4.5 to 5.5 V         | —                | _                | 0.3  | kΩ   |

|                                | source                                                                                                            | V <sub>REF</sub> range = 3.15 to 3.6 V | —                | _                | 875  | Ω    |

Table continues on the next page...

| Symbol                           | Parameter                                                        | Conditions                          | Min | Typ <sup>1</sup> | Max  | Unit |

|----------------------------------|------------------------------------------------------------------|-------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                     | 80 MHz                              | 550 |                  | —    | ns   |

| t <sub>total_conv</sub>          | Total Conversion time tsample + tconv (for standard channels)    | 80 MHz                              | 1   | _                |      | μs   |

|                                  | Total Conversion time tsample +<br>tconv (for extended channels) |                                     | 1.5 | _                | _    |      |

| C <sub>S</sub> <sup>5</sup>      | ADC input sampling capacitance                                   | —                                   | —   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                      | —                                   | _   | —                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                      | —                                   | _   | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                    | $V_{REF}$ range = 4.5 to 5.5 V      | _   | _                | 0.3  | kΩ   |

|                                  | source                                                           | $V_{REF}$ range = 3.15 to 3.6 V     | _   | _                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                             | —                                   | —   | _                | 825  | Ω    |

| INL                              | Integral non-linearity                                           | —                                   | -2  | _                | 2    | LSB  |

| DNL                              | Differential non-linearity                                       | —                                   | -1  |                  | 1    | LSB  |

| OFS                              | Offset error                                                     | —                                   | -4  |                  | 4    | LSB  |

| GNE                              | Gain error                                                       | —                                   | -4  | —                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                   | 150 °C                              | _   | _                | 2500 | nA   |

| (pad going to one<br>ADC)        | Max positive/negative injection                                  |                                     | -5  | _                | 5    | mA   |

| ADO)                             | Max leakage (standard channel)                                   | 105 °C <sub>TA</sub>                | _   | 5                | 250  | nA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                              | Without current injection           | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                         | With current injection <sup>6</sup> |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                              |                                     |     |                  | < 1  | μs   |

Table 21. ADC conversion characteristics (for 10-bit) (continued)

- Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.</li>

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 65

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: Absolute maximum ratings) must be honored to meet TUE spec quoted here

## 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol                                                      | Description                                                             | Min.     | Тур. | Max.                    | Unit             |

|-------------------------------------------------------------|-------------------------------------------------------------------------|----------|------|-------------------------|------------------|

| I <sub>DDHS</sub>                                           | Supply current, High-speed mode (EN=1, PMODE=1)                         |          | _    | 250                     | μA               |

| I <sub>DDLS</sub>                                           | Supply current, low-speed mode (EN=1, PMODE=0)                          | _        | 5    | 11                      | μA               |

| V <sub>AIN</sub>                                            | Analog input voltage                                                    | $V_{SS}$ | -    | V <sub>IN1_CMP_RE</sub> | V                |

| V <sub>AIO</sub>                                            | Analog input offset voltage <sup>1, 1</sup>                             | -47      | _    | 47                      | mV               |

| V <sub>H</sub> Analog comparator hysteresis <sup>2, 2</sup> |                                                                         | _        | 1    | 25                      | mV               |

|                                                             | • CR0[HYSTCTR] = 00                                                     | _        | 20   | 50                      | mV               |

|                                                             | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>                                   | _        | 40   | 70                      | mV               |

|                                                             | <ul> <li>CR0[HYSTCTR] = 10</li> </ul>                                   | _        | 60   | 105                     | mV               |

|                                                             | • CR0[HYSTCTR] = 11                                                     |          |      |                         |                  |

| t <sub>DHS</sub>                                            | Propagation Delay, High Speed Mode (Full Swing) <sup>1,</sup><br>3, 3   | _        | -    | 250                     | ns               |

| t <sub>DLS</sub>                                            | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>          | _        | 5    | 21                      | μs               |

|                                                             | Analog comparator initialization delay, High speed mode <sup>4, 4</sup> | —        | 4    |                         | μs               |

|                                                             | Analog comparator initialization delay, Low speed mode <sup>4</sup>     | —        | 100  |                         | μs               |

| I <sub>DAC6b</sub>                                          | 6-bit DAC current adder (when enabled)                                  |          |      | - <b>I</b>              |                  |

|                                                             | 3.3V Reference Voltage                                                  | _        | 6    | 9                       | μA               |

|                                                             | 5V Reference Voltage                                                    | _        | 10   | 16                      | μA               |

| INL                                                         | 6-bit DAC integral non-linearity                                        | -0.5     | —    | 0.5                     | LSB <sup>5</sup> |

| DNL                                                         | 6-bit DAC differential non-linearity                                    | -0.8     | _    | 0.8                     | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_{-HV_{-}A}}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

#### **Clocks and PLL interfaces modules**

| Symbol          | Parameter                                   | Mode     | Conditions               | Min  | Тур | Max  | Unit |

|-----------------|---------------------------------------------|----------|--------------------------|------|-----|------|------|

|                 | Oscillator                                  | FSP      | 8 MHz                    |      | 2.2 |      | mA   |

|                 | Analog Circuit<br>supply current            |          | 16 MHz                   |      | 2.2 |      |      |

|                 |                                             |          | 40 MHz                   |      | 3.2 |      |      |

|                 |                                             | LCP      | 8 MHz                    |      | 141 |      | uA   |

|                 |                                             |          | 16 MHz                   |      | 252 |      |      |

|                 |                                             |          | 40 MHz                   |      | 518 |      |      |

| V <sub>IH</sub> | Input High<br>level CMOS<br>Schmitt trigger | EXT Wave | Oscillator<br>supply=3.3 | 1.95 |     |      | V    |

| V <sub>IL</sub> | Input low level<br>CMOS<br>Schmitt trigger  |          | Oscillator<br>supply=3.3 |      |     | 1.25 | V    |

Table 23.

Main oscillator electrical characteristics (continued)

1. Values are very dependent on crystal or resonator used and parasitic capacitance observed in the board.

2. Typ value for oscillator supply 3.3 V@27 °C

## 6.2.2 32 kHz Oscillator electrical specifications

### Table 24. 32 kHz oscillator electrical specifications

| Symbol              | Parameter                                       | Condition | Min | Тур | Мах | Unit |

|---------------------|-------------------------------------------------|-----------|-----|-----|-----|------|

| f <sub>osc_lo</sub> | Oscillator crystal<br>or resonator<br>frequency |           | 32  |     | 40  | KHz  |

| t <sub>cst</sub>    | Crystal Start-up<br>Time <sup>1, 2</sup>        |           |     |     | 2   | S    |

1. This parameter is characterized before qualification rather than 100% tested.

2. Proper PC board layout procedures must be followed to achieve specifications.

### 6.2.3 16 MHz RC Oscillator electrical specifications Table 25. 16 MHz RC Oscillator electrical specifications

| Symbol               | Parameter                              | Conditions | Value |     |     | Unit |

|----------------------|----------------------------------------|------------|-------|-----|-----|------|

|                      |                                        |            | Min   | Тур | Max | 1    |

| F <sub>Target</sub>  | IRC target frequency                   | —          | —     | 16  | —   | MHz  |

| PTA                  | IRC frequency variation after trimming | —          | -5    | —   | 5   | %    |

| T <sub>startup</sub> | Startup time                           | —          |       | _   | 1.5 | us   |

| T <sub>STJIT</sub>   | Cycle to cycle jitter                  |            | —     | —   | 1.5 | %    |

| T <sub>LTJIT</sub>   | Long term jitter                       |            | —     | —   | 0.2 | %    |

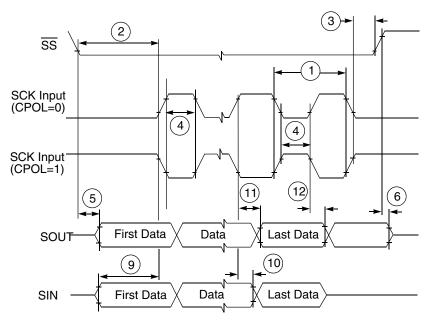

Figure 14. DSPI modified transfer format timing – slave, CPHA = 0

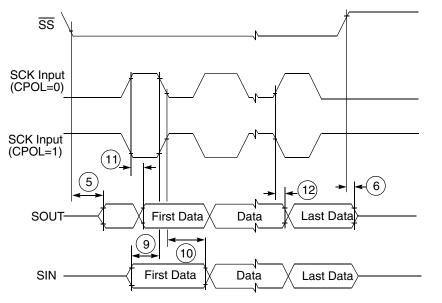

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

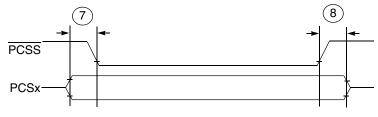

Figure 16. DSPI PCS strobe (PCSS) timing

| No  | Parameter                                 | Value   |    | Unit |

|-----|-------------------------------------------|---------|----|------|

|     |                                           | Min Max |    |      |

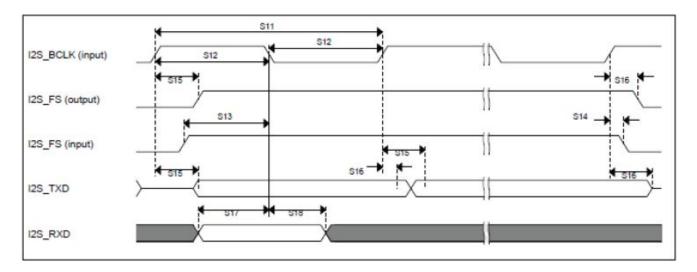

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | -       | 28 | ns   |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0       | -  | ns   |

| S17 | SAI_RXD setup before SAI_BCLK             | 10      | -  | ns   |

| S18 | SAI_RXD hold after SAI_BCLK               | 2       | -  | ns   |

Table 44. Slave mode SAI Timing (continued)

Figure 24. Slave mode SAI Timing

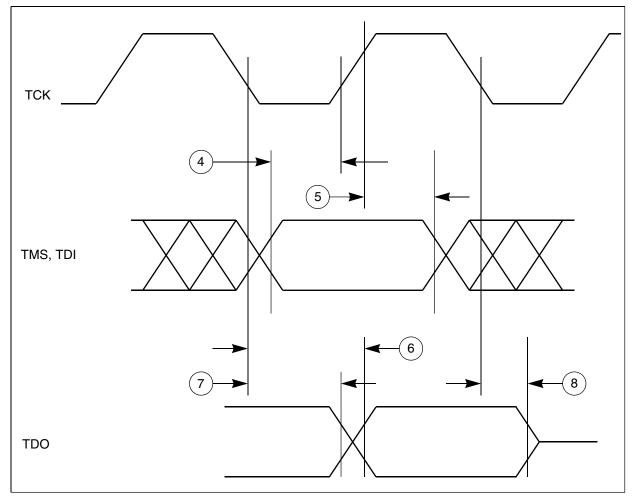

## 6.5 Debug specifications

## 6.5.1 JTAG interface timing

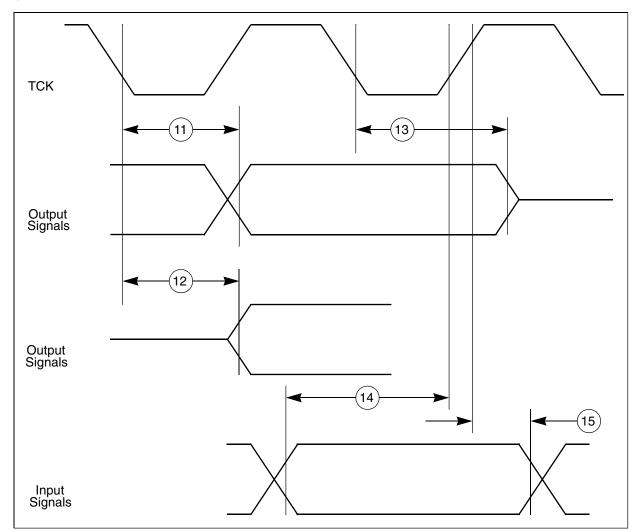

Table 45. JTAG pin AC electrical characteristics <sup>1</sup>

| #  | Symbol                                | Characteristic                      | Min  | Мах                 | Unit |

|----|---------------------------------------|-------------------------------------|------|---------------------|------|

| 1  | t <sub>JCYC</sub>                     | TCK Cycle Time <sup>2, 2</sup>      | 62.5 | —                   | ns   |

| 2  | t <sub>JDC</sub>                      | TCK Clock Pulse Width               | 40   | 60                  | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK Rise and Fall Times (40% - 70%) |      | 3                   | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI Data Setup Time            | 5    | _                   | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI Data Hold Time             | 5    |                     | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK Low to TDO Data Valid           | —    | 20 <sup>3, 3</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK Low to TDO Data Invalid         | 0    | _                   | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK Low to TDO High Impedance       |      | 15                  | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK Falling Edge to Output Valid    | —    | 600 <sup>4, 4</sup> | ns   |

Table continues on the next page ...

### Debug specifications

Figure 26. JTAG test access port timing

Figure 27. JTAG boundary scan timing

# 6.5.2 Nexus timing

### Table 46. Nexus debug port timing 1

| No. | Symbol                                     | Parameter                                           | Condition<br>s | Min  | Max  | Unit  |

|-----|--------------------------------------------|-----------------------------------------------------|----------------|------|------|-------|

| 1   | t <sub>MCYC</sub>                          | MCKO Cycle Time                                     | —              | 15.6 | _    | ns    |

| 2   | t <sub>MDC</sub>                           | MCKO Duty Cycle                                     | —              | 40   | 60   | %     |

| 3   | t <sub>MDOV</sub>                          | MCKO Low to MDO, MSEO, EVTO Data Valid <sup>2</sup> | —              | -0.1 | 0.25 | tMCYC |

| 4   | t <sub>EVTIPW</sub>                        | EVTI Pulse Width                                    | —              | 4    | _    | tTCYC |

| 5   | t <sub>EVTOPW</sub>                        | EVTO Pulse Width                                    | —              | 1    | —    | tMCYC |

| 6   | t <sub>TCYC</sub>                          | TCK Cycle Time <sup>3</sup>                         | —              | 62.5 | _    | ns    |

| 7   | t <sub>TDC</sub>                           | TCK Duty Cycle                                      | —              | 40   | 60   | %     |

| 8   | t <sub>NTDIS</sub> ,<br>t <sub>NTMSS</sub> | TDI, TMS Data Setup Time                            | —              | 8    | _    | ns    |

Table continues on the next page...

#### **Thermal attributes**

| Board type | Symbol           | Description                                                                                   | 324 MAPBGA | Unit | Notes |

|------------|------------------|-----------------------------------------------------------------------------------------------|------------|------|-------|

| _          | R <sub>θJB</sub> | Thermal<br>resistance, junction<br>to board                                                   | 16.8       | °C/W | 44    |

| _          | R <sub>θJC</sub> | Thermal<br>resistance, junction<br>to case                                                    | 7.4        | °C/W | 55    |

| _          | Ψ <sub>JT</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package top<br>natural convection    | 0.2        | °C/W | 66    |

|            | Ψ <sub>JB</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>natural convection | 7.3        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 256 MAPBGA | Unit | Notes  |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 42.6       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>eJA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 26.0       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 31.0       | °C/W | 1,3    |

| Four-layer (2s2p) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 21.3       | °C/W | 1,3    |

|                   | R <sub>0JB</sub>  | Thermal<br>resistance, junction<br>to board                                | 12.8       | °C/W | 44     |

Table continues on the next page...

#### Thermal attributes

| Board type | Symbol               | Description                                                                                                          | 256 MAPBGA | Unit | Notes |

|------------|----------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|-------|

| -          | R <sub>θJC</sub>     | Thermal<br>resistance, junction<br>to case                                                                           | 7.9        | °C/W | 55    |

|            | Ψ <sub>JT</sub>      | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection)    | 0.2        | °C/W | 66    |

| _          | R <sub>0JB_CSB</sub> | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) | 9.0        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).