Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 160MHz                                                                 |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                        |

| Number of I/O              | 178                                                                    |

| Program Memory Size        | 3MB (3M × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 384K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                           |

| Data Converters            | A/D 36x10b, 16x12b                                                     |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 256-LBGA                                                               |

| Supplier Device Package    | 256-MAPPBGA (17x17)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746bk1mmj6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

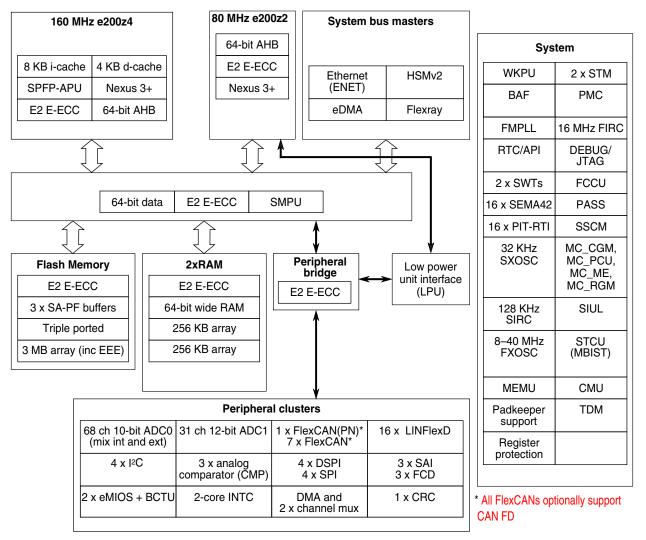

# 1 Block diagram

Figure 1. MPC5746C block diagram

# 2 Family comparison

The following table provides a summary of the different members of the MPC5746C family and their proposed features. This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

# 3.2 Ordering Information

| Example                                                                  | Code                                                                     | PC 57                                                             | 4      | 6      | С               | Ş | К0                                  | М                 | MJ      | 6    | R        |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|--------|--------|-----------------|---|-------------------------------------|-------------------|---------|------|----------|

| ·                                                                        | Qualification Status                                                     |                                                                   |        |        |                 |   |                                     |                   | 1       | 1    | 1        |

|                                                                          | Power Architecture                                                       |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Automotive Platform                                                      |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Core Version                                                             |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| Flas                                                                     | sh Size (core dependent)                                                 |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Product                                                                  |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Optional fields                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Fab and mask indicator                                                   |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Temperature spec.                                                        |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Package Code                                                             |                                                                   |        |        |                 |   |                                     |                   | ]       |      |          |

|                                                                          | CPU Frequency                                                            |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| R = Ta                                                                   | pe & Reel (blank if Tray)                                                |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | Due due 6 Manual au                                                      |                                                                   | -      |        |                 |   | <b>D</b> -                          | - 1               | 0       |      |          |

| Qualification Status                                                     | Product Version                                                          | Fab and mask version indicator Package (<br>K = TSMC Fab KU = 176 |        |        |                 |   |                                     | ED                |         |      |          |

| P = Engineering samples<br>S = Automotive qualified                      | B = Single core                                                          |                                                                   |        | sion o | f the           |   | KU = 176 LQFP EP<br>MJ = 256 MAPBGA |                   |         |      |          |

|                                                                          | C = Dual core #(0,1,etc.) = Version of the<br>maskset, like rev. 0=0N65H |                                                                   |        |        | MN = 324 MAPBGA |   |                                     |                   |         |      |          |

| PC = Power Architecture                                                  |                                                                          | maeneeu,                                                          |        |        |                 |   | Μ                                   | H = 10            | OMAPB   | GA   |          |

| Automotive Platform                                                      |                                                                          | Temperat                                                          | ure sp | bec.   |                 |   | СР                                  | U Fre             | quency  |      |          |

| 57 = Power Architecture in 55nm                                          | Omtion of tiolds                                                         | C = -40.C                                                         |        |        |                 |   |                                     |                   |         | unto | 120 MHz  |

|                                                                          | Optional fields                                                          | V = -40.C                                                         |        |        |                 |   |                                     |                   |         | •    | 160 MHz  |

| Core Version                                                             | Blank = No optional feature                                              | M = -40.C                                                         | to +12 | 25.0   | a               |   | 0 -                                 |                   | sciales | upto | 100 1012 |

| 4 = e200z4 Core Version (highest<br>core version in the case of multiple | S = HSM (Security Module)                                                |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| cores)                                                                   | F = CAN FD                                                               |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| ,                                                                        | B = HSM + CAN FD                                                         |                                                                   |        |        |                 |   |                                     |                   | Metho   |      |          |

| Flash Memory Size                                                        | R = 512K RAM                                                             |                                                                   |        |        |                 |   |                                     | = Tape<br>ink = T | and ree |      |          |

| 4 = 1.5 MB                                                               | T = HSM + 512K RAM                                                       |                                                                   |        |        |                 |   | Dia                                 |                   | lay     |      |          |

| 5 = 2 MB                                                                 | G* = CAN FD + 512K RAM                                                   |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| 6 = 3 MB                                                                 | H* = HSM + CAN FD + 512K RAM                                             |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          | * G and H for 5746 B/C only                                              |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

| Note: Not all part number con                                            | nbinations are available as produ                                        | ction produ                                                       | ıct    |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          | enon prout                                                        |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

|                                                                          |                                                                          |                                                                   |        |        |                 |   |                                     |                   |         |      |          |

# 4 General

## 4.1 Absolute maximum ratings

### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

#### General

### Table 6. Recommended operating conditions ( $V_{DD HV x} = 3.3 V$ ) (continued)

| Symbol                      | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Мах | Unit |

|-----------------------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> <sup>8</sup> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ                          | Junction temperature under bias |                               | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. Only applicable when supplying from external source.

- 5. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

- 6. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 7. This supply is shorted VDD\_HV\_A on lower packages.

- 8.  $T_J$ =150°C. Assumes  $T_A$ =125°C

- Assumes maximum  $\theta$ JA of 2s2p board. See Thermal attributes

### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

### Table 7. Recommended operating conditions ( $V_{DD_HV_x} = 5 V$ )

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max              | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------|------------------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | —                             | 4.5                                                | 5.5              | V    |

| $V_{DD_HV_B}$                                      |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_C</sub>                               |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | —                             | 3.15                                               | 3.6              | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              | —                             | 3.15                                               | 5.5              | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5              | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                             | -0.1                                               | 0.1              | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                                         |                               | 1.2                                                | 1.32             | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>           | Analog Comparator DAC reference voltage                     | _                             | 3.15                                               | 5.5 <sup>5</sup> | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | _                             | -3.0                                               | 3.0              | mA   |

| T <sub>A</sub> <sup>7</sup>                        | Ambient temperature under bias                              | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125              | °C   |

| TJ                                                 | Junction temperature under bias                             | _                             | -40                                                | 150              | °C   |

1. All voltages are referred to  $V_{\text{SS}\ \text{HV}}$  unless otherwise specified

2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash_{reg}}$ .

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 6. This supply is shorted VDD\_HV\_A on lower packages.

- 7.  $T_J=150^{\circ}C$ . Assumes  $T_A=125^{\circ}C$

- Assumes maximum θJA of 2s2p board. See Thermal attributes

## 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Generating core supply using internal ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- Low voltage detector low threshold (LVD\_IO\_A\_LO) for V<sub>DD\_HV\_IO\_A supply</sub>

- Low voltage detector high threshold (LVD\_IO\_A\_Hi) for V<sub>DD\_HV\_IO\_A</sub> supply

- Low voltage detector (LVD\_FLASH) for 3.3 V flash supply (VDD\_HV\_FLA)

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

# 4.4 Voltage monitor electrical characteristics

| Table 9. | Voltage monitor electrical characteristics |

|----------|--------------------------------------------|

|----------|--------------------------------------------|

| Symbol                  | Parameter                        | State   | Conditions                | Co       | nfiguratio                  | n             |          | Thresho        | ld     | Unit   |        |        |   |

|-------------------------|----------------------------------|---------|---------------------------|----------|-----------------------------|---------------|----------|----------------|--------|--------|--------|--------|---|

|                         |                                  |         |                           | Power Up | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min      | Тур            | Max    | V      |        |        |   |

| V <sub>POR_LV</sub>     | LV supply power                  | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 0.930    | 0.979          | 1.028  | V      |        |        |   |

|                         | on reset detector                |         | Trimmed                   |          |                             | ve            | -        | -              | -      | V      |        |        |   |

|                         |                                  | Rise    | Untrimmed                 |          |                             |               | 0.980    | 1.029          | 1.078  | V      |        |        |   |

|                         |                                  |         | Trimmed                   |          |                             |               | -        | -              | -      | V      |        |        |   |

| V <sub>HVD_LV_col</sub> |                                  |         | Untrimmed No Yes Function |          |                             | Disabled      | at Start | 1              |        |        |        |        |   |

| d                       | voltage monitoring,              |         | Trimmed                   | -        |                             | al            | 1.325    | 1.345          | 1.375  | V      |        |        |   |

|                         | detecting at                     | Rise    | Untrimmed                 |          |                             |               | Disabled | at Start       |        |        |        |        |   |

|                         | device pin                       |         | Trimmed                   |          |                             |               | 1.345    | 1.365          | 1.395  | V      |        |        |   |

| V <sub>LVD_LV_PD</sub>  | LV supply low                    | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 1.0800   | 1.1200         | 1.1600 | V      |        |        |   |

| 2_hot                   | voltage Trimmo<br>monitoring,    | Trimmed |                           | ve       | 1.1250                      | 1.1425        | 1.1600   | V              |        |        |        |        |   |

|                         | detecting on the                 | Rise    | Untrimmed                 |          |                             |               | 1.1000   | 1.1400         | 1.1800 | V      |        |        |   |

|                         | PD2 core (hot)<br>area           | . ,     |                           | Trimmed  |                             |               | 1.1450   | 1.1625         | 1.1800 | V      |        |        |   |

| V <sub>LVD_LV_PD</sub>  | LV supply low                    | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 1.0800   | 1.1200         | 1.1600 | V      |        |        |   |

| 1_hot (BGFP)            | voltage<br>monitoring,           |         | Trimmed                   |          |                             | ve            | 1.1140   | 1.1370         | 1.1600 | V      |        |        |   |

|                         | detecting on the                 | Rise    | Untrimmed                 |          |                             |               | 1.1000   | 1.140          | 1.1800 | V      |        |        |   |

|                         | PD1 core (hot)<br>area           |         | Trimmed                   |          |                             |               | 1.1340   | 1.1570         | 1.1800 | V      |        |        |   |

| V <sub>LVD_LV_PD</sub>  | LV supply low                    | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 1.0800   | 1.1200         | 1.1600 | V      |        |        |   |

| 0_hot (BGFP)            | voltage monitoring,              |         | Trimmed                   |          |                             | ve            | 1.1140   | 1.1370         | 1.1600 | V      |        |        |   |

|                         | detecting on the                 | Rise    | Untrimmed                 | 1        |                             |               | 1.1000   | 1.1400         | 1.1800 | V      |        |        |   |

|                         | PD0 core (hot)<br>area           |         | Trimmed                   |          |                             |               | 1.1340   | 1.1570         | 1.1800 | V      |        |        |   |

| V <sub>POR_HV</sub>     | HV supply power                  | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 2.7000   | 2.8500         | 3.0000 | V      |        |        |   |

|                         | on reset detector                |         | Trimmed                   | -        |                             | ve            | -        | -              | -      | V      |        |        |   |

|                         |                                  | Rise    | Untrimmed                 | -        |                             |               | 2.7500   | 2.9000         | 3.0500 | V      |        |        |   |

|                         |                                  |         | Trimmed                   | -        |                             |               | -        | -              | -      | V      |        |        |   |

| V <sub>LVD_IO_A_L</sub> | HV IO_A supply                   | Fall    | Untrimmed                 | Yes      | No                          | Destructi     | 2.7500   | 2.9230         | 3.0950 | V      |        |        |   |

| 0 <sup>3, 3</sup>       | low voltage<br>monitoring - low  |         | Trimmed                   |          |                             | ve            | 2.9780   | 3.0390         | 3.1000 | V      |        |        |   |

|                         | range                            | Rise    | Untrimmed                 |          |                             |               | 2.7800   | 2.9530         | 3.1250 | V      |        |        |   |

|                         |                                  |         | Trimmed                   | 1        |                             | 3.0080        | 3.0690   | 3.1300         | V      |        |        |        |   |

| V <sub>LVD_IO_A_H</sub> | HV IO_A supply                   | Fall    | Trimmed                   | No       | Yes                         | Destructi     | Disabled | at Start       |        |        |        |        |   |

| l <sup>3</sup>          | low voltage<br>monitoring - high |         |                           |          |                             | ve            | 4.0600   | 4.151          | 4.2400 | V      |        |        |   |

|                         | range                            | Rise    | Trimmed                   | ]        |                             |               | Disabled | abled at Start |        |        |        |        |   |

|                         |                                  | range   | lange                     |          |                             |               |          |                |        | 4.1150 | 4.2010 | 4.3000 | V |

Table continues on the next page ...

| Symbol                      | Parameter                                  | Conditions <sup>1</sup>                                                          | Min | Тур  | Max | Unit |

|-----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| I <sub>DD_BODY_2</sub><br>6 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | —   | _    | 246 | mA   |

|                             |                                            | $T_a = 125^{\circ}C^5$                                                           |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 160MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105°C                                                           |     | —    | 235 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              | —   | —    | 210 | mA   |

| I <sub>DD_BODY_3</sub><br>7 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 181 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              |     | —    | 171 | mA   |

| IDD_BODY_4 <sup>8</sup>     | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> |     | —    | 264 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           | —   | —    | 171 | mA   |

| I <sub>DD_STOP</sub>        | STOP mode Operating current                | $T_{a} = 125 \ ^{\circ}C^{9}$                                                    | -   | -    | 49  | mA   |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | 10.6 | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           |     | 8.1  | —   |      |

|                             |                                            | $V_{DD_LV} = 1.25 V$                                                             |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 25 °C                                                           |     | 4.6  | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

## Table 10. Current consumption characteristics (continued)

Table continues on the next page...

# 4.7 Electromagnetic Compatibility (EMC) specifications

EMC measurements to IC-level IEC standards are available from NXP on request.

# 5 I/O parameters

# 5.1 AC specifications @ 3.3 V Range

| Symbol                 |         | Prop. Delay (ns) <sup>1</sup><br>L>H/H>L |          | Rise/Fall Edge (ns) |                        | SIUL2_MSCRn[SRC 1:0] |  |  |

|------------------------|---------|------------------------------------------|----------|---------------------|------------------------|----------------------|--|--|

|                        | Min     | Max                                      | Min      | Max                 | 1                      | MSB,LSB              |  |  |

| pad_sr_hv              |         | 6/6                                      |          | 1.9/1.5             | 25                     | 11                   |  |  |

| (output)               | 2.5/2.5 | 8.25/7.5                                 | 0.8/0.6  | 3.25/3              | 50                     |                      |  |  |

| (output)               | 6.4/5   | 19.5/19.5                                | 3.5/2.5  | 12/12               | 200                    |                      |  |  |

|                        | 2.2/2.5 | 8/8                                      | 0.55/0.5 | 3.9/3.5             | 25                     | 10                   |  |  |

|                        | 0.090   | 1.1                                      | 0.035    | 1.1                 | asymmetry <sup>2</sup> |                      |  |  |

|                        | 2.9/3.5 | 12.5/11                                  | 1/1      | 7/6                 | 50                     |                      |  |  |

|                        | 11/8    | 35/31                                    | 7.7/5    | 25/21               | 200                    |                      |  |  |

|                        | 8.3/9.6 | 45/45                                    | 4/3.5    | 25/25               | 50                     | 01 <sup>3</sup>      |  |  |

|                        | 13.5/15 | 65/65                                    | 6.3/6.2  | 30/30               | 200                    |                      |  |  |

|                        | 13/13   | 75/75                                    | 6.8/6    | 40/40               | 50                     | 00 <sup>3</sup>      |  |  |

|                        | 21/22   | 100/100                                  | 11/11    | 51/51               | 200                    |                      |  |  |

| pad_i_hv/<br>pad_sr_hv |         | 2/2                                      |          | 0.5/0.5             | 0.5                    | NA                   |  |  |

| (input) <sup>4</sup>   |         |                                          |          |                     |                        |                      |  |  |

### Table 14. Functional Pad AC Specifications @ 3.3 V Range

1. As measured from 50% of core side input to Voh/Vol of the output

- This row specifies the min and max asymmetry between both the prop delay and the edge rates for a given PVT and 25pF load. Required for the Flexray spec.

- 3. Slew rate control modes

- 4. Input slope = 2ns

## NOTE

The specification given above is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

### NOTE

The specification given above is measured between 20% / 80%.

#### Peripheral operating requirements and behaviours

| Symbol              | Parameter                                      | Conditions                                                                                       |      | Value   |     |    |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|---------|-----|----|--|

|                     |                                                |                                                                                                  | Min  | Min Typ |     |    |  |

| V <sub>HYS</sub>    | CMOS Input Buffer hysterisis                   | —                                                                                                | 300  | —       | _   | mV |  |

| V <sub>DD_POR</sub> | Minimum supply for strong pull-down activation | -                                                                                                | —    | _       | 1.2 | V  |  |

| I <sub>OL_R</sub>   | Strong pull-down current <sup>1, 1</sup>       | $\label{eq:Device under power-on reset} $V_{DD_HV_A} = V_{DD_POR}$$V_{OL} = 0.35^*V_{DD_HV_A}$$$ | 0.2  | _       | _   | mA |  |

|                     |                                                | Device under power-on reset<br>$V_{DD_{HV}A} = V_{DD_{POR}}$<br>$V_{OL} = 0.35^*V_{DD_{HV}IO}$   | 11   | _       |     | mA |  |

| W <sub>FRST</sub>   | RESET input filtered pulse                     | —                                                                                                | —    | _       | 500 | ns |  |

| W <sub>NFRST</sub>  | RESET input not filtered pulse                 | -                                                                                                | 2000 | —       | _   | ns |  |

| ll <sub>WPU</sub> l | Weak pull-up current absolute value            | RESET pin V <sub>IN</sub> = V <sub>DD</sub>                                                      | 23   | —       | 82  | μA |  |

Table 18.

Functional reset pad electrical specifications (continued)

1. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for RESET.

# 5.6 PORST electrical specifications

### Table 19. PORST electrical specifications

| Symbol              | Parameter                      |                                | Value |                                |    |  |  |

|---------------------|--------------------------------|--------------------------------|-------|--------------------------------|----|--|--|

|                     |                                | Min                            | Тур   | Max                            |    |  |  |

| W <sub>FPORST</sub> | PORST input filtered pulse     |                                | —     | 200                            | ns |  |  |

| WNFPORST            | PORST input not filtered pulse | 1000                           | —     | _                              | ns |  |  |

| V <sub>IH</sub>     | Input high level               | 0.65 x<br>V <sub>DD_HV_A</sub> | _     | _                              | V  |  |  |

| V <sub>IL</sub>     | Input low level                | —                              | _     | 0.35 x<br>V <sub>DD_HV_A</sub> | V  |  |  |

# 6 Peripheral operating requirements and behaviours

## 6.1 Analog

## 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Analog

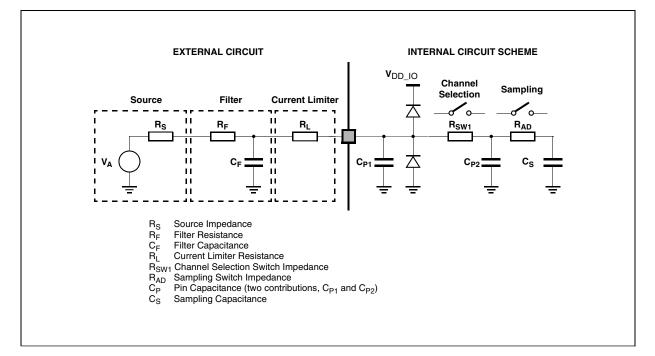

## 6.1.1.1 Input equivalent circuit and ADC conversion characteristics

### Figure 6. Input equivalent circuit

## NOTE

The ADC performance specifications are not guaranteed if two ADCs simultaneously sample the same shared channel.

Table 20. ADC conversion characteristics (for 12-bit)

| Symbol                         | Parameter                                                                                                         | Conditions                             | Min              | Typ <sup>1</sup> | Max  | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------|------|

| f <sub>CK</sub>                | ADC Clock frequency (depends on<br>ADC configuration) (The duty cycle<br>depends on AD_CK <sup>2</sup> frequency) | _                                      | 15.2             | 80               | 80   | MHz  |

| f <sub>s</sub>                 | Sampling frequency                                                                                                | 80 MHz                                 | —                |                  | 1.00 | MHz  |

| t <sub>sample</sub>            | Sample time <sup>3</sup>                                                                                          | 80 MHz@ 100 ohm source impedance       | 250              | _                | _    | ns   |

| t <sub>conv</sub>              | Conversion time <sup>4</sup>                                                                                      | 80 MHz                                 | 700              | _                | —    | ns   |

| t <sub>total_conv</sub>        | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard and extended channels)                | 80 MHz                                 | 1.5 <sup>5</sup> | _                | _    | μs   |

|                                | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for precision channels)                            |                                        | 1                | _                |      |      |

| C <sub>S</sub> <sup>6, 6</sup> | ADC input sampling capacitance                                                                                    | —                                      | —                | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>6</sup>   | ADC input pin capacitance 1                                                                                       | —                                      | —                | _                | 5    | pF   |

| C <sub>P2</sub> <sup>6</sup>   | ADC input pin capacitance 2                                                                                       | —                                      | _                | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>6</sup>  | Internal resistance of analog                                                                                     | $V_{REF}$ range = 4.5 to 5.5 V         | —                | _                | 0.3  | kΩ   |

|                                | source                                                                                                            | V <sub>REF</sub> range = 3.15 to 3.6 V | —                | _                | 875  | Ω    |

Table continues on the next page...

| Symbol                                  | Parameter                                 | Conditions                             | Min | Typ <sup>1</sup> | Max                                                      | Unit |

|-----------------------------------------|-------------------------------------------|----------------------------------------|-----|------------------|----------------------------------------------------------|------|

| R <sub>AD</sub> <sup>6</sup>            | Internal resistance of analog source      | —                                      | -   | _                | 825                                                      | Ω    |

| INL                                     | Integral non-linearity (precise channel)  | —                                      | -2  | _                | 2                                                        | LSB  |

| INL                                     | Integral non-linearity (standard channel) | —                                      | -3  | _                | 3                                                        | LSB  |

| DNL                                     | Differential non-linearity                | —                                      | -1  |                  | 1                                                        | LSB  |

| OFS                                     | Offset error                              | —                                      | -6  | _                | 6                                                        | LSB  |

| GNE                                     | Gain error                                | —                                      | -4  | _                | 4                                                        | LSB  |

| ADC Analog Pad                          | Max leakage (precision channel)           | 150 °C                                 | —   | _                | 250                                                      | nA   |

| (pad going to one ADC)                  | Max leakage (standard channel)            | 150 °C                                 | _   | _                | 2500                                                     | nA   |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Max leakage (standard channel)            | 105 °C <sub>TA</sub>                   | _   | 5                | 250                                                      | nA   |

|                                         | Max positive/negative injection           |                                        | -5  | _                | 5                                                        | mA   |

| TUEprecision channels                   | Total unadjusted error for precision      | Without current injection              | -6  | +/-4             | 6                                                        | LSB  |

|                                         | channels                                  | With current injection <sup>7, 7</sup> |     | +/-5             | 2<br>3<br>1<br>6<br>4<br>250<br>2500<br>2500<br>250<br>5 | LSB  |

| TUE <sub>standard/extended</sub>        | Total unadjusted error for standard/      | Without current injection              | -8  | +/-6             | 8                                                        | LSB  |

| channels                                | extended channels                         | With current injection <sup>7</sup>    |     | +/-8             |                                                          | LSB  |

| t <sub>recovery</sub>                   | STOP mode to Run mode recovery time       |                                        |     |                  | < 1                                                      | μs   |

#### Table 20. ADC conversion characteristics (for 12-bit) (continued)

- Active ADC input, VinA < [min(ADC\_VrefH, ADC\_ADV, VDD\_HV\_IOx)]. VDD\_HV\_IOx refers to I/O segment supply voltage. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions (VDD\_HV\_x = 3.3 V)' for required relation between IO\_supply\_A,B,C and ADC\_Supply.</li>

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. Apart from tsample and tconv, few cycles are used up in ADC digital interface and hence the overall throughput from the ADC is lower.

- 6. See Figure 6.

- 7. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: Absolute maximum ratings) must be honored to meet TUE spec quoted here

### Table 21. ADC conversion characteristics (for 10-bit)

| Symbol              | Parameter                                                                                                    | Conditions                          | Min  | Typ <sup>1</sup> | Max  | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------|------|------------------|------|------|

| f <sub>CK</sub>     | ADC Clock frequency (depends on ADC configuration) (The duty cycle depends on AD_CK <sup>2</sup> frequency.) | _                                   | 15.2 | 80               | 80   | MHz  |

| f <sub>s</sub>      | Sampling frequency                                                                                           | —                                   |      | _                | 1.00 | MHz  |

| t <sub>sample</sub> | Sample time <sup>3</sup>                                                                                     | 80 MHz@ 100 ohm source<br>impedance | 275  | _                | _    | ns   |

Table continues on the next page...

# 6.2 Clocks and PLL interfaces modules

## 6.2.1 Main oscillator electrical characteristics

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

#### **Clocks and PLL interfaces modules**

| Symbol          | Parameter                                   | Mode     | Conditions               | Min  | Тур | Мах  | Unit |

|-----------------|---------------------------------------------|----------|--------------------------|------|-----|------|------|

|                 | Oscillator                                  | FSP      | 8 MHz                    |      | 2.2 |      | mA   |

|                 | Analog Circuit<br>supply current            |          | 16 MHz                   |      | 2.2 |      |      |

|                 |                                             |          | 40 MHz                   |      | 3.2 |      |      |

|                 |                                             | LCP      | 8 MHz                    |      | 141 |      | uA   |

|                 |                                             |          | 16 MHz                   |      | 252 |      |      |

|                 |                                             |          | 40 MHz                   |      | 518 |      |      |

| V <sub>IH</sub> | Input High<br>level CMOS<br>Schmitt trigger | EXT Wave | Oscillator<br>supply=3.3 | 1.95 |     |      | V    |

| V <sub>IL</sub> | Input low level<br>CMOS<br>Schmitt trigger  | EXT Wave | Oscillator<br>supply=3.3 |      |     | 1.25 | V    |

Table 23.

Main oscillator electrical characteristics (continued)

1. Values are very dependent on crystal or resonator used and parasitic capacitance observed in the board.

2. Typ value for oscillator supply 3.3 V@27 °C

## 6.2.2 32 kHz Oscillator electrical specifications

#### Table 24. 32 kHz oscillator electrical specifications

| Symbol              | Parameter                                       | Condition | Min | Тур | Мах | Unit |

|---------------------|-------------------------------------------------|-----------|-----|-----|-----|------|

| f <sub>osc_lo</sub> | Oscillator crystal<br>or resonator<br>frequency |           | 32  |     | 40  | KHz  |

| t <sub>cst</sub>    | Crystal Start-up<br>Time <sup>1, 2</sup>        |           |     |     | 2   | S    |

1. This parameter is characterized before qualification rather than 100% tested.

2. Proper PC board layout procedures must be followed to achieve specifications.

## 6.2.3 16 MHz RC Oscillator electrical specifications Table 25. 16 MHz RC Oscillator electrical specifications

| Symbol               | Parameter                              | Conditions | Value |     | Unit |     |

|----------------------|----------------------------------------|------------|-------|-----|------|-----|

|                      |                                        |            | Min   | Тур | Мах  | 1   |

| F <sub>Target</sub>  | IRC target frequency                   | —          | —     | 16  | —    | MHz |

| PTA                  | IRC frequency variation after trimming | —          | -5    |     | 5    | %   |

| T <sub>startup</sub> | Startup time                           | —          |       |     | 1.5  | us  |

| T <sub>STJIT</sub>   | Cycle to cycle jitter                  |            | —     |     | 1.5  | %   |

| T <sub>LTJIT</sub>   | Long term jitter                       |            | _     | _   | 0.2  | %   |

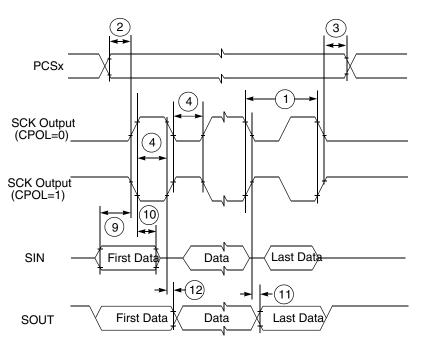

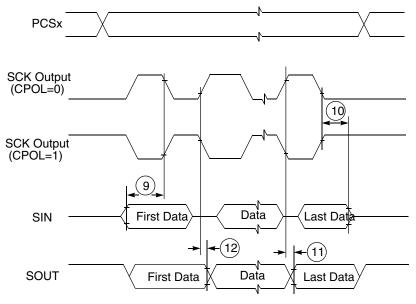

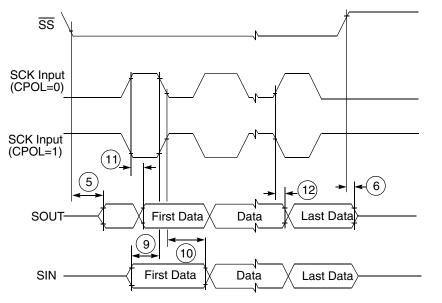

Figure 8. DSPI classic SPI timing — master, CPHA = 0

Figure 9. DSPI classic SPI timing — master, CPHA = 1

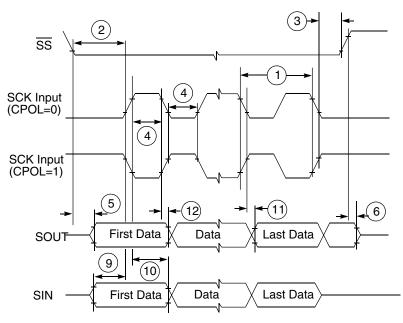

Figure 10. DSPI classic SPI timing — slave, CPHA = 0

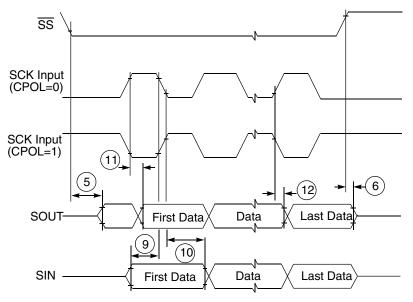

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

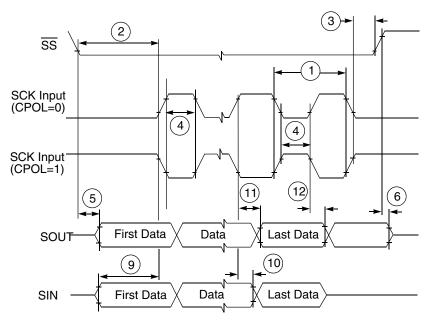

Figure 14. DSPI modified transfer format timing – slave, CPHA = 0

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

Figure 16. DSPI PCS strobe (PCSS) timing

1. All parameters specified for VDD\_HV\_IOx = 3.3 V -5%, +±10%, TJ = -40 oC / 150 oC.

## 6.4.3 Ethernet switching specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

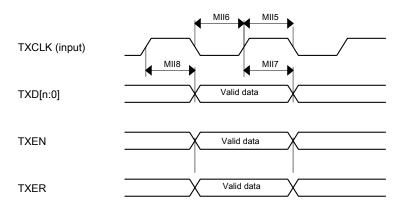

### 6.4.3.1 MII signal switching specifications

The following timing specs meet the requirements for MII style interfaces for a range of transceiver devices.

| Symbol | Description                           | Min. | Max. | Unit   |

|--------|---------------------------------------|------|------|--------|

| —      | RXCLK frequency                       | _    | 25   | MHz    |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK  |

|        |                                       |      |      | period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    |      | ns     |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    |      | ns     |

| —      | TXCLK frequency                       | _    | 25   | MHz    |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK  |

|        |                                       |      |      | period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | —    | ns     |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   | _    | 25   | ns     |

Table 41. MII signal switching specifications

### Figure 21. RMII/MII transmit signal timing diagram

#### **Debug specifications**

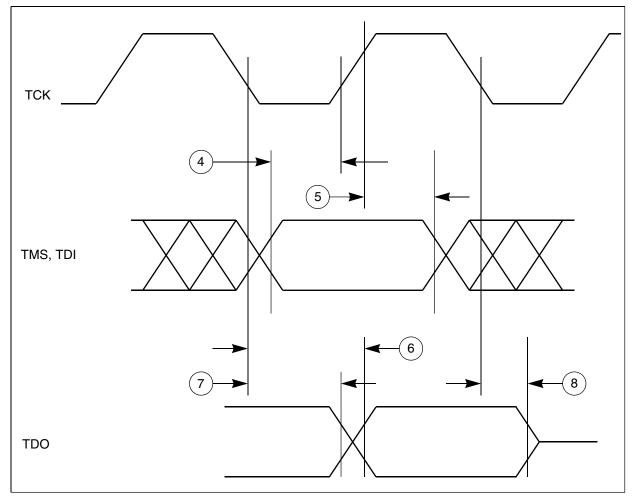

### Table 45. JTAG pin AC electrical characteristics <sup>1</sup> (continued)

| #  | Symbol             | Characteristic                                            | Min | Max | Unit |

|----|--------------------|-----------------------------------------------------------|-----|-----|------|

| 12 | t <sub>BSDVZ</sub> | TCK Falling Edge to Output Valid out of High<br>Impedance | —   | 600 | ns   |

| 13 | t <sub>BSDHZ</sub> | TCK Falling Edge to Output High Impedance                 | —   | 600 | ns   |

| 14 | t <sub>BSDST</sub> | Boundary Scan Input Valid to TCK Rising Edge              | 15  |     | ns   |

| 15 | t <sub>BSDHT</sub> | TCK Rising Edge to Boundary Scan Input Invalid            | 15  | _   | ns   |

- 1. These specifications apply to JTAG boundary scan only.

- 2. This timing applies to TDI, TDO, TMS pins, however, actual frequency is limited by pad type for EXTEST instructions. Refer to pad specification for allowed transition frequency

- 3. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 4. Applies to all pins, limited by pad slew rate. Refer to IO delay and transition specification and add 20 ns for JTAG delay.

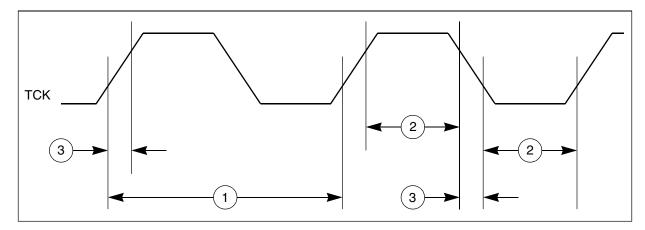

Figure 25. JTAG test clock input timing

#### Debug specifications

Figure 26. JTAG test access port timing

| Rev. No. | Date | Substantial Changes                                                                                         |

|----------|------|-------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>In section, Thermal attributes</li> <li>Added table for 100 MAPBGA</li> </ul>                      |

|          |      | <ul> <li>In section Obtaining package dimensions</li> <li>Updated package details for 100 MAPBGA</li> </ul> |

|          |      | Editoral updates throughtout including correction of various module names.                                  |

## Table 51. Revision History (continued)

Table continues on the next page...

| Table 51. | Revision | History ( | (continued) |

|-----------|----------|-----------|-------------|

|-----------|----------|-----------|-------------|

| Rev. No. | Date                | Substantial Changes                                                                                                                                                                                                                                                                                                                           |

|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 4    | 9 March 2016        | <ul> <li>In section, Voltage regulator electrical characteristics</li> <li>In table, Voltage regulator electrical specifications:</li> <li>Updated the footnote on V<sub>DD_HV_BALLAST</sub></li> </ul>                                                                                                                                       |

| Rev 5    | 27 February<br>2017 | <ul> <li>In Family Comparison section:</li> <li>Updated the "MPC5746C Family Comparison" table.</li> <li>added "NVM Memory Map 1", "NVM Memory Map 2", and "RAM Memory Map" tables.</li> </ul>                                                                                                                                                |

|          |                     | <ul> <li>Updated the product version, flash memory size and optional fields information in<br/>Ordering Information section.</li> </ul>                                                                                                                                                                                                       |

|          |                     | <ul> <li>In Recommended Operating Conditions section, removed the note related to additional<br/>crossover current.</li> </ul>                                                                                                                                                                                                                |

|          |                     | <ul> <li>VDD_HV_C row added in "Voltage regulator electrical specifications" table in Voltage<br/>regulator electrical characteristics section.</li> </ul>                                                                                                                                                                                    |

|          |                     | <ul> <li>In Voltage Monitor Electrical Characteristics section, updated the "Trimmed" Fall and<br/>Rise specs of VHVD_LV_cold parameter in "Voltage Monitor Electrical Characteristics"<br/>table.</li> </ul>                                                                                                                                 |

|          |                     | <ul> <li>In AC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> </ul>                                                                                                                                                                               |

|          |                     | <ul> <li>In DC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in<br/>the table.</li> </ul>                                                                                                                                      |

|          |                     | <ul> <li>In AC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> <li>In DC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in the table.</li> </ul> |

|          |                     | <ul> <li>In "Flash memory AC timing specifications" table in Flash memory AC timing specifications section:</li> <li>Updated the "t<sub>psus</sub>" typ value from 7 us to 9.4 us.</li> <li>Updated the "t<sub>psus</sub>" max value from 9.1 us to 11.5 us.</li> </ul>                                                                       |

|          |                     | <ul> <li>Added "Continuous SCK Timing" table in DSPI timing section.</li> </ul>                                                                                                                                                                                                                                                               |

|          |                     | <ul> <li>Added "ADC pad leakage" at 105°C TA conditions in "ADC conversion characteristics<br/>(for 12-bit)" table in ADC electrical specifications section.</li> </ul>                                                                                                                                                                       |

|          |                     | <ul> <li>In "STANDBY Current consumption characteristics" table in Supply current characteristics section:</li> <li>Updated the Typ and max values of IDD Standby current.</li> <li>Added IDD Standby3 current spec for FIRC ON.</li> </ul>                                                                                                   |

|          |                     | <ul> <li>Removed IVDDHV and IVDDLV specs in 16 MHz RC Oscillator electrical specifications<br/>section.</li> </ul>                                                                                                                                                                                                                            |

|          |                     | <ul> <li>Added Reset Sequence section, with Reset Sequence Duration, BAF execution duration<br/>section, and Reset Sequence Distribution as its sub-sections.</li> </ul>                                                                                                                                                                      |

Table continues on the next page ...