Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, WDT                                          |

| Number of I/O              | 129                                                                      |

| Program Memory Size        | 3MB (3M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K × 8                                                                  |

| RAM Size                   | 384K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 5.5V                                                             |

| Data Converters            | A/D 36x10b, 16x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746bsk1mku2r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Start Address | End Address | Flash block                  | RWW partition | MPC5744       | MPC5745       | MPC5746       |

|---------------|-------------|------------------------------|---------------|---------------|---------------|---------------|

| 0x01000000    | 0x0103FFFF  | 256 KB code<br>Flash block 0 | 6             | available     | available     | available     |

| 0x01040000    | 0x0107FFFF  | 256 KB code<br>Flash block 1 | 6             | available     | available     | available     |

| 0x01080000    | 0x010BFFFF  | 256 KB code<br>Flash block 2 | 6             | available     | available     | available     |

| 0x010C0000    | 0x010FFFFF  | 256 KB code<br>Flash block3  | 6             | available     | available     | available     |

| 0x01100000    | 0x0113FFFF  | 256 KB code<br>Flash block 4 | 6             | not available | available     | available     |

| 0x01140000    | 0x0117FFFF  | 256 KB code<br>Flash block 5 | 7             | not available | available     | available     |

| 0x01180000    | 0x011BFFFF  | 256 KB code<br>Flash block 6 | 7             | not available | not available | available     |

| 0x011C0000    | 0x011FFFFF  | 256 KB code<br>Flash block 7 | 7             | not available | not available | available     |

| 0x01200000    | 0x0123FFFF  | 256 KB code<br>Flash block 8 | 7             | not available | not available | available     |

| 0x01240000    | 0x0127FFFF  | 256 KB code<br>Flash block 9 | 7             | not available | not available | not available |

Table 2. MPC5746C Family Comparison - NVM Memory Map 1

## Table 3. MPC5746C Family Comparison - NVM Memory Map 2

| Start Address | End Address | Flash block      | <b>RWW</b> partition | MPC5744B      | MPC5744C  |

|---------------|-------------|------------------|----------------------|---------------|-----------|

|               |             |                  |                      | MPC5745B      | MPC5745C  |

|               |             |                  |                      | MPC5746B      | MPC5746C  |

| 0x00F90000    | 0x00F93FFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F94000    | 0x00F97FFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F98000    | 0x00F9BFFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F9C000    | 0x00F9FFFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00FA0000    | 0x00FA3FFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FA4000    | 0x00FA7FFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FA8000    | 0x00FABFFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FAC000    | 0x00FAFFFF  | 16 KB data Flash | 3                    | not available | available |

### Table 4. MPC5746C Family Comparison - RAM Memory Map

| Start Address | End Address | Allocated size | Description | MPC5744   | MPC5745   | MPC5746   |

|---------------|-------------|----------------|-------------|-----------|-----------|-----------|

| 0x4000000     | 0x40001FFF  | 8 KB           | SRAM0       | available | available | available |

| 0x40002000    | 0x4000FFFF  | 56 KB          | SRAM1       | available | available | available |

| 0x40010000    | 0x4001FFFF  | 64 KB          | SRAM2       | available | available | available |

| 0x40020000    | 0x4002FFFF  | 64 KB          | SRAM3       | available | available | available |

Table continues on the next page...

# 3.2 Ordering Information

| Example                                                                  | Code                              | PC 57                 | 4      | 6      | С       | Ş      | К0              | М                                   | MJ      | 6    | R        |  |

|--------------------------------------------------------------------------|-----------------------------------|-----------------------|--------|--------|---------|--------|-----------------|-------------------------------------|---------|------|----------|--|

| ·                                                                        | Qualification Status              |                       |        |        |         |        |                 |                                     | 1       | 1    | 1        |  |

|                                                                          | Power Architecture                |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Automotive Platform               |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Core Version                      |                       |        |        |         |        |                 |                                     |         |      |          |  |

| Flas                                                                     | sh Size (core dependent)          |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Product                           |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Optional fields                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Fab and mask indicator            |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Temperature spec.                 |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Package Code                      |                       |        |        |         |        |                 |                                     | ]       |      |          |  |

|                                                                          | CPU Frequency                     |                       |        |        |         |        |                 |                                     |         |      |          |  |

| R = Ta                                                                   | pe & Reel (blank if Tray)         |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | Due due 6 Manual au               |                       | -      |        |         |        | <b>D</b> -      | - 1                                 | 0       |      |          |  |

| Qualification Status                                                     | Product Version                   | Fab and I<br>K = TSMC |        | versic | on indi | icator |                 | -                                   | Code    | ED   |          |  |

| P = Engineering samples<br>S = Automotive qualified                      | B = Single core<br>C = Dual core  |                       |        | sion o | f the   |        |                 | KU = 176 LQFP EP<br>MJ = 256 MAPBGA |         |      |          |  |

|                                                                          | C = Dual core                     |                       | ,      |        |         |        | MN = 324 MAPBGA |                                     |         |      |          |  |

| PC = Power Architecture                                                  |                                   | maeneeu,              |        |        |         |        | Μ               | H = 10                              | OMAPB   | GA   |          |  |

| Automotive Platform                                                      |                                   | Temperat              | ure sp | bec.   |         |        | СР              | U Fre                               | quency  |      |          |  |

| 57 = Power Architecture in 55nm                                          | Omtion of tiolds                  | C = -40.C             |        |        |         |        |                 |                                     |         | unto | 120 MHz  |  |

|                                                                          | Optional fields                   | V = -40.C             |        |        |         |        |                 |                                     |         | •    | 160 MHz  |  |

| Core Version                                                             | Blank = No optional feature       | M = -40.C             | to +12 | 25.0   | a       |        | 0 -             |                                     | sciales | upto | 100 1012 |  |

| 4 = e200z4 Core Version (highest<br>core version in the case of multiple | S = HSM (Security Module)         |                       |        |        |         |        |                 |                                     |         |      |          |  |

| cores)                                                                   | F = CAN FD                        |                       |        |        |         |        |                 |                                     |         |      |          |  |

| ,                                                                        | B = HSM + CAN FD                  |                       |        |        |         |        |                 |                                     | Metho   |      |          |  |

| Flash Memory Size                                                        | R = 512K RAM                      |                       |        |        |         |        |                 | = Tape<br>ink = T                   | and ree |      |          |  |

| 4 = 1.5 MB                                                               | T = HSM + 512K RAM                |                       |        |        |         |        | Dia             |                                     | lay     |      |          |  |

| 5 = 2 MB                                                                 | G* = CAN FD + 512K RAM            |                       |        |        |         |        |                 |                                     |         |      |          |  |

| 6 = 3 MB                                                                 | H* = HSM + CAN FD + 512K RAM      |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          | * G and H for 5746 B/C only       |                       |        |        |         |        |                 |                                     |         |      |          |  |

| Note: Not all part number con                                            | nbinations are available as produ | ction produ           | ıct    |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   | enon prout            |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

|                                                                          |                                   |                       |        |        |         |        |                 |                                     |         |      |          |  |

# 4 General

## 4.1 Absolute maximum ratings

## NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in Table 5 for specific conditions

#### General

## Table 6. Recommended operating conditions ( $V_{DD HV x} = 3.3 V$ ) (continued)

| Symbol                      | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Мах | Unit |

|-----------------------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> <sup>8</sup> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ                          | Junction temperature under bias |                               | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. Only applicable when supplying from external source.

- 5. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

- 6. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 7. This supply is shorted VDD\_HV\_A on lower packages.

- 8.  $T_J$ =150°C. Assumes  $T_A$ =125°C

- Assumes maximum  $\theta$ JA of 2s2p board. See Thermal attributes

## NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

### Table 7. Recommended operating conditions ( $V_{DD_HV_x} = 5 V$ )

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max              | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------|------------------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | —                             | 4.5                                                | 5.5              | V    |

| $V_{DD_HV_B}$                                      |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_C</sub>                               |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | —                             | 3.15                                               | 3.6              | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              | —                             | 3.15                                               | 5.5              | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5              | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                             | -0.1                                               | 0.1              | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                                         |                               | 1.2                                                | 1.32             | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>           | Analog Comparator DAC reference voltage                     | _                             | 3.15                                               | 5.5 <sup>5</sup> | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | _                             | -3.0                                               | 3.0              | mA   |

| T <sub>A</sub> <sup>7</sup>                        | Ambient temperature under bias                              | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125              | °C   |

| TJ                                                 | Junction temperature under bias                             | _                             | -40                                                | 150              | °C   |

1. All voltages are referred to  $V_{\text{SS}\ \text{HV}}$  unless otherwise specified

2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash_{reg}}$ .

#### General

| Symbol                 | Parameter     | State | Conditions | Co       | nfiguratio                  | n             | Threshold U       |               |        |   |  |

|------------------------|---------------|-------|------------|----------|-----------------------------|---------------|-------------------|---------------|--------|---|--|

|                        |               |       |            | Power Up | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min               | Тур           | Max    | V |  |

| V <sub>LVD_LV_PD</sub> | LV supply low | Fall  | Untrimmed  | No       | Yes                         | Function      | Disabled          | bled at Start |        |   |  |

| 2_cold                 |               | U U   | Trimmed    |          |                             | al            | 1.1400            | 1.1550        | 1.1750 | V |  |

|                        |               | Rise  | Untrimmed  |          |                             |               | Disabled at Start |               |        |   |  |

|                        | device pin    |       | Trimmed    |          |                             |               | 1.1600            | 1.1750        | 1.1950 | V |  |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

# 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

## NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | _   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

Table continues on the next page...

#### General

| Symbol                                 | Parameter                           | Conditions <sup>1</sup>              | Min | Тур | Max   | Unit |

|----------------------------------------|-------------------------------------|--------------------------------------|-----|-----|-------|------|

| DD_HV_ADC_REF <sup>10,</sup><br>11, 11 | ADC REF Operating current           | T <sub>a</sub> = 125 °C <sup>5</sup> | —   | 200 | 400   | μA   |

| 11, 11                                 |                                     | 2 ADCs operating at 80 MHz           |     |     |       |      |

|                                        |                                     | $V_{DD_{HV}ADC_{REF}} = 5.5 V$       |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 105 °C              | _   | 200 | _     |      |

|                                        |                                     | 2 ADCs operating at 80 MHz           |     |     |       |      |

|                                        |                                     | $V_{DD_{HV}ADC_{REF}} = 5.5 V$       |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 85 °C               | _   | 200 | _     |      |

|                                        |                                     | 2 ADCs operating at 80 MHz           |     |     |       |      |

|                                        |                                     | $V_{DD_{HV}ADC_{REF}} = 5.5 V$       |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 25 °C               | _   | 200 | _     |      |

|                                        |                                     | 2 ADCs operating at 80 MHz           |     |     |       |      |

|                                        |                                     | $V_{DD_{HV}ADC_{REF}} = 3.6 V$       |     |     |       |      |

| I <sub>DD_HV_ADCx</sub> <sup>11</sup>  | ADC HV Operating current            | T <sub>a</sub> = 125 °C <sup>5</sup> | _   | 1.2 | 1.2 2 | m/   |

|                                        |                                     | ADC operating at 80 MHz              |     |     |       |      |

|                                        |                                     | $V_{DD_HV_ADC} = 5.5 V$              |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 25 °C               | _   | 1   | 2     |      |

|                                        |                                     | ADC operating at 80 MHz              |     |     |       |      |

|                                        |                                     | $V_{DD_HV_ADC} = 3.6 V$              |     |     |       |      |

| I <sub>DD_HV_FLASH</sub> 12            | Flash Operating current during read | T <sub>a</sub> = 125 °C <sup>5</sup> |     | 40  | 45    | mA   |

|                                        | access                              | 3.3 V supplies                       |     |     |       |      |

|                                        |                                     | 160 MHz frequency                    |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 105 °C              | _   | 40  | 45    |      |

|                                        |                                     | 3.3 V supplies                       |     |     |       |      |

|                                        |                                     | 160 MHz frequency                    |     |     |       |      |

|                                        |                                     | T <sub>a</sub> = 85 °C               | —   | 40  | 45    | 1    |

|                                        |                                     | 3.3 V supplies                       |     |     |       |      |

|                                        |                                     | 160 MHz frequency                    |     |     |       |      |

|                                        | 1                                   |                                      |     | -   |       | I    |

### Table 10. Current consumption characteristics (continued)

- 1. The content of the Conditions column identifies the components that draw the specific current.

- Single e200Z4 core cache disabled @80 MHz, no FlexRay, no ENET, 2 x CAN, 8 LINFlexD, 2 SPI, ADC0 and 1 used constantly, no HSM, Memory: 2M flash, 128K RAM RUN mode, Clocks: FIRC on, XOSC, PLL on, SIRC on for TOD, no 32KHz crystal (TOD runs off SIRC).

- 3. Recommended Transistors:MJD31 @ 85°C, 105°C and 125°C. In case of internal ballast mode, it is expected that the external ballast is not mounted and BAL\_SELECT\_INT pin is tied to VDD\_HV\_A supply on board. Internal ballast can be used for all use cases with current consumption upto 150mA

- 4. The power consumption does not consider the dynamic current of I/Os

- 5. Tj=150°C. Assumes Ta=125°C

- Assumes maximum θJA of 2s2p board. SeeThermal attributes

- e200Z4 core, 160MHz, cache enabled; e200Z2 core, 80MHz, no FlexRay, no ENET, 7 CAN, 16 LINFlexD, 4 SPI, 1x ADC used constantly, includes HSM at start-up / periodic use, Memory: 3M flash, 256K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- e200Z4 core, 120MHz, cache enabled; e200Z2 core, 60MHz; no FlexRay, no ENET, 7 CAN, 16 LINFlexD, 4 SPI, 1x ADC used constantly, includes HSM at start-up / periodic use, Memory: 3M flash, 128K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- e200Z4 core, 160MHz, cache enabled; e200Z4 core, 80MHz; HSM fully operational (Z0 core @80MHz) FlexRay, 5x CAN, 5x LINFlexD, 2x SPI, 1x ADC used constantly, 1xeMIOS (5 ch), Memory: 3M flash, 384K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- 9. Assuming Ta=Tj, as the device is in Stop mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes.

- 10. Internal structures hold the input voltage less than V<sub>DD\_HV\_ADC\_REF</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

- 11. This value is the total current for two ADCs.Each ADC might consume upto 2mA at max.

- 12. This assumes the default configuration of flash controller register. For more details, refer to Flash memory program and erase specifications

Table 11. Low Power Unit (LPU) Current consumption characteristics

| Symbol   | Parameter     | Conditions <sup>1</sup>                        | Min | Тур  | Мах  | Unit |

|----------|---------------|------------------------------------------------|-----|------|------|------|

| LPU_RUN  | with 256K RAM | $T_a = 25 \text{ °C}$                          | -   | 10   | —    | mA   |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = OFF, SPI0 = OFF, LIN0 = OFF, CAN0 = OFF |     |      |      |      |

|          |               | T <sub>a</sub> = 85 °C                         | —   | 10.5 | —    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | T <sub>a</sub> = 105 °C                        | —   | 11   | —    |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

|          |               | $T_a = 125 \ ^{\circ}C^{2, 2}$                 | —   | —    | 26   |      |

|          |               | SYS_CLK = 16MHz                                |     |      |      |      |

|          |               | ADC0 = ON, SPI0 = ON, LIN0 = ON, CAN0 = ON     |     |      |      |      |

| LPU_STOP | with 256K RAM | $T_a = 25 \text{ °C}$                          | —   | 0.18 | —    | mA   |

|          |               | T <sub>a</sub> = 85 °C                         | —   | 0.60 | —    |      |

|          |               | T <sub>a</sub> = 105 °C                        | —   | 1.00 |      |      |

|          |               | $T_{a} = 125 \ ^{\circ}C^{2}$                  | —   | _    | 10.6 |      |

- 1. The content of the Conditions column identifies the components that draw the specific current.

- Assuming Ta=Tj, as the device is in static (fully clock gated) mode. Assumes maximum θJA of 2s2p board. SeeThermal attributes

Table 12. STANDBY Current consumption characteristics

| Symbol   | Parameter    | Conditions <sup>1</sup>       | Min | Тур | Max  | Unit |

|----------|--------------|-------------------------------|-----|-----|------|------|

| STANDBY0 | STANDBY with | T <sub>a</sub> = 25 °C        | —   | 71  | —    | μA   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C        | —   | 125 | 700  |      |

|          |              | T <sub>a</sub> = 105 °C       | —   | 195 | 1225 |      |

|          |              | $T_a = 125 \text{ °C}^{2, 2}$ | —   | 314 | 2100 |      |

| STANDBY1 | STANDBY with | $T_a = 25 \text{ °C}$         | —   | 72  |      | μA   |

|          | 64K RAM      | T <sub>a</sub> = 85 °C        | —   | 140 | 715  |      |

|          |              | T <sub>a</sub> = 105 °C       | —   | 225 | 1275 |      |

|          |              | $T_a = 125 \ ^{\circ}C^2$     | —   | 358 | 2250 | 1    |

Table continues on the next page...

# 5.2 DC electrical specifications @ 3.3V Range

### Table 15. DC electrical specifications @ 3.3V Range

| Symbol              | Parameter                                                  | Va                                 | Value                          |    |  |  |

|---------------------|------------------------------------------------------------|------------------------------------|--------------------------------|----|--|--|

|                     |                                                            | Min                                | Max                            |    |  |  |

| Vih (pad_i_hv)      | Pad_I_HV Input Buffer High Voltage                         | 0.72*VDD_HV_<br>x                  | VDD_HV_x +<br>0.3              | V  |  |  |

| Vil (pad_i_hv)      | Pad_I_HV Input Buffer Low Voltage                          | VDD_HV_x -<br>0.3                  | 0.45*VDD_HV_<br>x              | V  |  |  |

| Vhys (pad_i_hv)     | Pad_I_HV Input Buffer Hysteresis                           | 0.11*VDD_HV_<br>x                  |                                | V  |  |  |

| Vih_hys             | CMOS Input Buffer High Voltage (with hysteresis enabled)   | 0.67*VDD_HV_<br>x                  | VDD_HV_x +<br>0.3              | V  |  |  |

| Vil_hys             | CMOS Input Buffer Low Voltage (with hysteresis enabled)    | VDD_HV_x -<br>0.3                  | 0.35*VDD_HV_<br>x              | V  |  |  |

| Vih                 | CMOS Input Buffer High Voltage (with hysteresis disabled)  | 0.57 *<br>VDD_HV_x <sup>1, 1</sup> | VDD_HV_x <sup>1</sup> + 0.3    | V  |  |  |

| Vil                 | CMOS Input Buffer Low Voltage (with hysteresis disabled)   | VDD_HV_x -<br>0.3                  | 0.4 *<br>VDD_HV_x <sup>1</sup> | V  |  |  |

| Vhys                | CMOS Input Buffer Hysteresis                               | 0.09 *<br>VDD_HV_x <sup>1</sup>    |                                | V  |  |  |

| Pull_IIH (pad_i_hv) | Weak Pullup Current <sup>2, 2</sup> Low                    | 15                                 |                                | μA |  |  |

| Pull_IIH (pad_i_hv) | Weak Pullup Current <sup>3, 3</sup> High                   |                                    | 55                             | μA |  |  |

| Pull_IIL (pad_i_hv) | Weak Pulldown Current <sup>3</sup> Low                     | 28                                 |                                | μA |  |  |

| Pull_IIL (pad_i_hv) | Weak Pulldown Current <sup>2</sup> High                    |                                    | 85                             | μA |  |  |

| Pull_loh            | Weak Pullup Current <sup>4</sup>                           | 15                                 | 50                             | μA |  |  |

| Pull_lol            | Weak Pulldown Current <sup>5</sup>                         | 15                                 | 50                             | μA |  |  |

| linact_d            | Digital Pad Input Leakage Current (weak pull inactive)     | -2.5                               | 2.5                            | μA |  |  |

| Voh                 | Output High Voltage <sup>6</sup>                           | 0.8<br>*VDD_HV_x <sup>1</sup>      | —                              | V  |  |  |

| Vol                 | Output Low Voltage <sup>7</sup>                            | _                                  | 0.2<br>*VDD_HV_x <sup>1</sup>  | V  |  |  |

|                     | Output Low Voltage <sup>8</sup>                            |                                    | 0.1 *VDD_HV_x                  |    |  |  |

| loh_f               | Full drive loh <sup>9, 9</sup> (SIUL2_MSCRn.SRC[1:0] = 11) | 18                                 | 70                             | mA |  |  |

| lol_f               | Full drive Iol <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 11)    | 21                                 | 120                            | mA |  |  |

| loh_h               | Half drive loh <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 10)    | 9                                  | 35                             | mA |  |  |

| lol_h               | Half drive Iol <sup>9</sup> (SIUL2_MSCRn.SRC[1:0] = 10)    | 10.5                               | 60                             | mA |  |  |

- 1. VDD\_HV\_x = VDD\_HV\_A, VDD\_HV\_B, VDD\_HV\_C

- 2. Measured when pad=0.69\*VDD\_HV\_x

- 3. Measured when pad=0.49\*VDD\_HV\_x

- 4. Measured when pad = 0 V

- 5. Measured when pad =  $VDD_HV_x$

- 6. Measured when pad is sourcing 2 mA

- 7. Measured when pad is sinking 2 mA

- 8. Measured when pad is sinking 1.5 mA

- 9. Ioh/IoI is derived from spice simulations. These values are NOT guaranteed by test.

#### I/O parameters

| Table 18. | Functional res | et pad electrical | specifications |

|-----------|----------------|-------------------|----------------|

|-----------|----------------|-------------------|----------------|

| Symbol          | Parameter                      | Conditions |                     | Value |                         | Unit |

|-----------------|--------------------------------|------------|---------------------|-------|-------------------------|------|

|                 |                                |            | Min                 | Тур   | Max                     | 1    |

| V <sub>IH</sub> | CMOS Input Buffer High Voltage | —          | 0.65*V <sub>D</sub> | _     | V <sub>DD_HV_x</sub>    | V    |

|                 |                                |            | D_HV_x              |       | +0.3                    |      |

| VIL             | CMOS Input Buffer Low Voltage  | —          | V <sub>DD_HV</sub>  |       | 0.35*V <sub>DD_HV</sub> | V    |

|                 |                                |            | <sub>x</sub> -0.3   |       | _x                      |      |

Table continues on the next page...

Analog

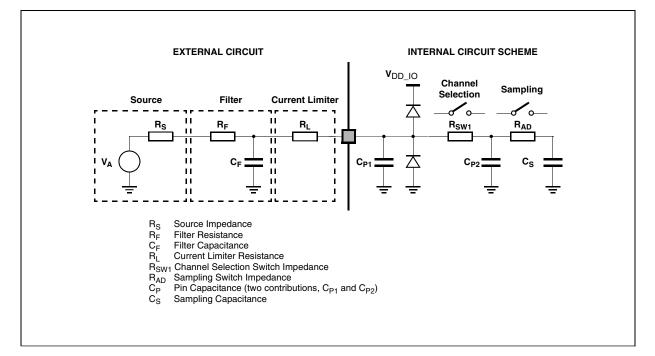

## 6.1.1.1 Input equivalent circuit and ADC conversion characteristics

### Figure 6. Input equivalent circuit

## NOTE

The ADC performance specifications are not guaranteed if two ADCs simultaneously sample the same shared channel.

Table 20. ADC conversion characteristics (for 12-bit)

| Symbol                         | Parameter                                                                                                         | Conditions                             | Min              | Typ <sup>1</sup> | Max  | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------|------|

| f <sub>CK</sub>                | ADC Clock frequency (depends on<br>ADC configuration) (The duty cycle<br>depends on AD_CK <sup>2</sup> frequency) | —                                      | 15.2             | 80               | 80   | MHz  |

| f <sub>s</sub>                 | Sampling frequency                                                                                                | 80 MHz                                 | —                |                  | 1.00 | MHz  |

| t <sub>sample</sub>            | Sample time <sup>3</sup>                                                                                          | 80 MHz@ 100 ohm source impedance       | 250              | —                | _    | ns   |

| t <sub>conv</sub>              | Conversion time <sup>4</sup>                                                                                      | 80 MHz                                 | 700              | _                | —    | ns   |

| t <sub>total_conv</sub>        | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for standard and extended channels)                | 80 MHz                                 | 1.5 <sup>5</sup> | _                | _    | μs   |

|                                | Total Conversion time t <sub>sample</sub> + t <sub>conv</sub> (for precision channels)                            |                                        | 1                | _                |      |      |

| C <sub>S</sub> <sup>6, 6</sup> | ADC input sampling capacitance                                                                                    | —                                      | —                | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>6</sup>   | ADC input pin capacitance 1                                                                                       | —                                      | —                | _                | 5    | pF   |

| C <sub>P2</sub> <sup>6</sup>   | ADC input pin capacitance 2                                                                                       | —                                      | _                | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>6</sup>  | Internal resistance of analog                                                                                     | $V_{REF}$ range = 4.5 to 5.5 V         | —                | _                | 0.3  | kΩ   |

|                                | source                                                                                                            | V <sub>REF</sub> range = 3.15 to 3.6 V | —                | _                | 875  | Ω    |

Table continues on the next page...

## 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                             | Min.     | Тур. | Max.                    | Unit             |

|--------------------|-------------------------------------------------------------------------|----------|------|-------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                         |          | _    | 250                     | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                          | _        | 5    | 11                      | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                                    | $V_{SS}$ | -    | V <sub>IN1_CMP_RE</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage <sup>1, 1</sup>                             | -47      | _    | 47                      | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2, 2</sup>                            | _        | 1    | 25                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 00</li> </ul>                                   | _        | 20   | 50                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>                                   | _        | 40   | 70                      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 10</li> </ul>                                   | _        | 60   | 105                     | mV               |

|                    | • CR0[HYSTCTR] = 11                                                     |          |      |                         |                  |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1,</sup><br>3, 3   | _        | -    | 250                     | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) <sup>1, 3</sup>          | _        | 5    | 21                      | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4, 4</sup> | —        | 4    |                         | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>     | —        | 100  |                         | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                                  |          |      |                         |                  |

|                    | 3.3V Reference Voltage                                                  | _        | 6    | 9                       | μA               |

|                    | 5V Reference Voltage                                                    | _        | 10   | 16                      | μA               |

| INL                | 6-bit DAC integral non-linearity                                        | -0.5     | —    | 0.5                     | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                    | -0.8     | _    | 0.8                     | LSB              |

1. Measured with hysteresis mode of 00

2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD_{-HV_{-}A}}$ -0.6V

3. Full swing = VIH, VIL

4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

5. 1 LSB =  $V_{reference}/64$

## NOTE

The above start up time of 1 us is equivalent to 16 cycles of 16 MHz.

## 6.2.4 128 KHz Internal RC oscillator Electrical specifications Table 26. 128 KHz Internal RC oscillator electrical specifications

| Symbol                         | Parameter               | Condition     | Min | Тур | Мах   | Unit  |

|--------------------------------|-------------------------|---------------|-----|-----|-------|-------|

| F <sub>oscu</sub> <sup>1</sup> | Oscillator<br>frequency | Calibrated    | 119 | 128 | 136.5 | KHz   |

|                                | Temperature dependence  |               |     |     | 600   | ppm/C |

|                                | Supply dependence       |               |     |     | 18    | %/V   |

|                                | Supply current          | Clock running |     |     | 2.75  | μA    |

|                                |                         | Clock stopped |     |     | 200   | nA    |

1. Vdd=1.2 V, 1.32V, T<sub>a</sub>=-40 C, 125 C

# 6.2.5 PLL electrical specifications

### Table 27. PLL electrical specifications

| Parameter                        | Min       | Тур | Max          | Unit | Comments                                                    |

|----------------------------------|-----------|-----|--------------|------|-------------------------------------------------------------|

| Input Frequency                  | 8         |     | 40           | MHz  |                                                             |

| VCO Frequency Range              | 600       |     | 1280         | MHz  |                                                             |

| Duty Cycle at pllclkout          | 48%       |     | 52%          |      | This specification is guaranteed at PLL IP boundary         |

| Period Jitter                    |           |     | See Table 28 | ps   | NON SSCG mode                                               |

| TIE                              |           |     | See Table 28 |      | at 960 M Integrated over 1MHz offset not valid in SSCG mode |

| Modulation Depth (Center Spread) | +/- 0.25% |     | +/- 3.0%     |      |                                                             |

| Modulation Frequency             |           |     | 32           | KHz  |                                                             |

| Lock Time                        |           |     | 60           | μs   | Calibration mode                                            |

### Table 28. Jitter calculation

| Type of jitter | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)                                        |

|----------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|

| Period Jitter  | 60 ps                                                                 | 3% of pllclkout1,2                                                     | Modulation depth                                                        |                                                                  | +/-( $J_{SN}$ + $J_{SDM}$ + $J_{SSCG}$ + $N^{[4]}$ × $J_{RJ}$ ) |

Table continues on the next page...

| Type of jitter                        | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)  |

|---------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------|

| Long Term Jitter<br>(Integer Mode)    |                                                                       |                                                                        |                                                                         | 40                                                               | +/-(N x J <sub>RJ</sub> ) |

| Long Term jitter<br>(Fractional Mode) |                                                                       |                                                                        |                                                                         | 100                                                              | +/-(N x J <sub>RJ</sub> ) |

Table 28. Jitter calculation (continued)

1. This jitter component is due to self noise generated due to bond wire inductances on different PLL supplies. The jitter value is valid for inductor value of 5nH or less each on VDD\_LV and VSS\_LV.

2. This jitter component is added when the PLL is working in the fractional mode.

3. This jitter component is added when the PLL is working in the Spread Spectrum Mode. Else it is 0.

4. The value of N is dependent on the accuracy requirement of the application. See Table 29

### Table 29. Percentage of sample exceeding specified value of jitter

| N | Percentage of samples exceeding specified value of jitter<br>(%) |

|---|------------------------------------------------------------------|

| 1 | 31.73                                                            |

| 2 | 4.55                                                             |

| 3 | 0.27                                                             |

| 4 | 6.30 × 1e-03                                                     |

| 5 | 5.63 × 1e-05                                                     |

| 6 | 2.00 × 1e-07                                                     |

| 7 | 2.82 × 1e-10                                                     |

# 6.3 Memory interfaces

# 6.3.1 Flash memory program and erase specifications

### NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 30 shows the estimated Program/Erase times.

| Symbol               | Characteristic                                                                                                                                                                                                                        | Min                                              | Typical | Max                                              | Units |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|--------------------------------------------------|-------|

| t <sub>drcv</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                          | 16<br>plus seven<br>system<br>clock<br>periods.  | _       | 45<br>plus seven<br>system<br>clock<br>periods   | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read<br>or Array Integrity until the UT0-AID bit is cleared. This time also<br>applies to the resuming from a suspend or breakpoint by<br>clearing AISUS or clearing NAIBP | _                                                | _       | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array<br>Integrity abort until the UT0-AID bit is set. This time also applies<br>to the UT0-AISUS to UT0-AID setting in the event of a Array<br>Integrity suspend request.       | _                                                | _       | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read<br>abort until the UT0-AID bit is set. This time also applies to the<br>UT0-AISUS to UT0-AID setting in the event of a Margin Read<br>suspend request.                | 10.36<br>plus four<br>system<br>clock<br>periods | _       | 20.42<br>plus four<br>system<br>clock<br>periods | μs    |

Table 33.

Flash memory AC timing specifications (continued)

# 6.3.6 Flash read wait state and address pipeline control settings

The following table describes the recommended RWSC and APC settings at various operating frequencies based on specified intrinsic flash access times of the flash module controller array at 125 °C.

Table 34.

Flash Read Wait State and Address Pipeline Control Combinations

| Flash frequency             | RWSC setting | APC setting |

|-----------------------------|--------------|-------------|

| 0 MHz < fFlash <= 33 MHz    | 0            | 0           |

| 33 MHz < fFlash <= 100 MHz  | 2            | 1           |

| 100 MHz < fFlash <= 133 MHz | 3            | 1           |

| 133 MHz < fFlash <= 160 MHz | 4            | 1           |

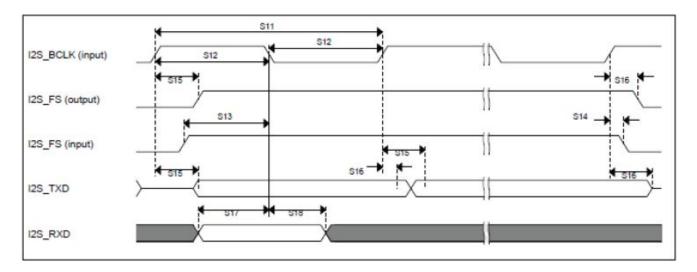

| No  | Parameter                                 | Value |     | Unit |

|-----|-------------------------------------------|-------|-----|------|

|     |                                           | Min   | Мах |      |

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | -     | 28  | ns   |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0     | -   | ns   |

| S17 | SAI_RXD setup before SAI_BCLK             | 10    | -   | ns   |

| S18 | SAI_RXD hold after SAI_BCLK               | 2     | -   | ns   |

Table 44. Slave mode SAI Timing (continued)

Figure 24. Slave mode SAI Timing

# 6.5 Debug specifications

## 6.5.1 JTAG interface timing

Table 45. JTAG pin AC electrical characteristics <sup>1</sup>

| #  | Symbol                                | Characteristic                      | Min  | Мах                 | Unit |

|----|---------------------------------------|-------------------------------------|------|---------------------|------|

| 1  | t <sub>JCYC</sub>                     | TCK Cycle Time <sup>2, 2</sup>      | 62.5 | —                   | ns   |

| 2  | t <sub>JDC</sub>                      | TCK Clock Pulse Width               | 40   | 60                  | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK Rise and Fall Times (40% - 70%) |      | 3                   | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI Data Setup Time            | 5    | _                   | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI Data Hold Time             | 5    |                     | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK Low to TDO Data Valid           | —    | 20 <sup>3, 3</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK Low to TDO Data Invalid         | 0    | —                   | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK Low to TDO High Impedance       |      | 15                  | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK Falling Edge to Output Valid    | —    | 600 <sup>4, 4</sup> | ns   |

Table continues on the next page ...

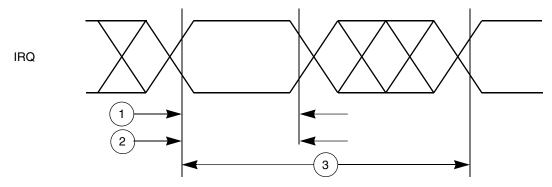

## 6.5.4 External interrupt timing (IRQ pin) Table 48. External interrupt timing specifications

| No. | Symbol            | Parameter             | Conditions | Min | Max | Unit             |

|-----|-------------------|-----------------------|------------|-----|-----|------------------|

| 1   | t <sub>IPWL</sub> | IRQ pulse width low   | —          | 3   | —   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | IRQ pulse width high  | —          | 3   | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | IRQ edge to edge time |            | 6   |     | t <sub>CYC</sub> |

These values applies when IRQ pins are configured for rising edge or falling edge events, but not both.

Figure 31. External interrupt timing

# 7 Thermal attributes

# 7.1 Thermal attributes

| Board type        | Symbol            | Description                                                                | 176LQFP | Unit | Notes    |

|-------------------|-------------------|----------------------------------------------------------------------------|---------|------|----------|

| Single-layer (1s) | R <sub>θJA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 50.7    | °C/W | 11, 22   |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 24.2    | °C/W | 1, 2, 33 |

| Single-layer (1s) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 38.1    | °C/W | 1, 3     |

Table continues on the next page ...

#### **Thermal attributes**

| Board type | Symbol           | Description                                                                                   | 324 MAPBGA | Unit | Notes |

|------------|------------------|-----------------------------------------------------------------------------------------------|------------|------|-------|

| _          | R <sub>θJB</sub> | Thermal<br>resistance, junction<br>to board                                                   | 16.8       | °C/W | 44    |

| _          | R <sub>θJC</sub> | Thermal<br>resistance, junction<br>to case                                                    | 7.4        | °C/W | 55    |

| _          | Ψ <sub>JT</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package top<br>natural convection    | 0.2        | °C/W | 66    |

|            | Ψ <sub>JB</sub>  | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>natural convection | 7.3        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 256 MAPBGA | Unit | Notes  |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 42.6       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>eJA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 26.0       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 31.0       | °C/W | 1,3    |

| Four-layer (2s2p) | R <sub>ejma</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 21.3       | °C/W | 1,3    |

|                   | R <sub>0JB</sub>  | Thermal<br>resistance, junction<br>to board                                | 12.8       | °C/W | 44     |

Table continues on the next page...

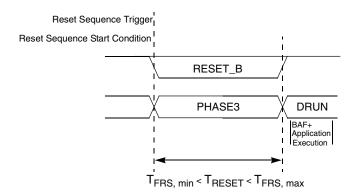

# 10.1.2 BAF execution duration

Following table specifies the typical BAF execution time in case BAF boot header is present at first location (Typical) and last location (worst case). Total Boot time is the sum of reset sequence duration and BAF execution time.

| BAF execution<br>duration                                | Min | Тур | Мах | Unit |

|----------------------------------------------------------|-----|-----|-----|------|

| BAF execution time<br>(boot header at first<br>location) | _   | 200 | _   | μs   |

| BAF execution time<br>(boot header at last<br>location)  | _   | _   | 320 | μs   |

Table 50. BAF execution duration

# 10.1.3 Reset sequence description

The figures in this section show the internal states of the device during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in .

With the beginning of DRUN mode, the first instruction is fetched and executed. At this point, application execution starts and the internal reset sequence is finished.

The following figures show the internal states of the device during the execution of the reset sequence and the possible states of the RESET\_B signal pin.

## NOTE

RESET\_B is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the device internal reset circuitry. A high level on this pin can only be generated by an external pullup resistor which is strong enough to overdrive the weak internal pulldown resistor. The rising edge on RESET\_B in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET\_B asserted low beyond the last Phase3.

Figure 36. Functional reset sequence short

The reset sequences shown in Figure 35 and Figure 36 are triggered by functional reset events. RESET\_B is driven low during these two reset sequences only if the corresponding functional reset source (which triggered the reset sequence) was enabled to drive RESET\_B low for the duration of the internal reset sequence. See the RGM\_FBRE register in the device reference manual for more information.

# **11 Revision History**

# 11.1 Revision History

The following table provides a revision history for this document.

| Rev. No. | Date          | Substantial Changes |

|----------|---------------|---------------------|

| Rev 1    | 14 March 2013 | Initial Release     |

Table continues on the next page...

| Rev. No. | Date         | Substantial Changes                                                                                                                                                         |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 3    | 2 March 2016 | In section, Recommended operating conditions                                                                                                                                |

|          |              | Added a new Note                                                                                                                                                            |

|          |              | In section, Voltage regulator electrical characteristics                                                                                                                    |

|          |              | <ul> <li>In table, Voltage regulator electrical specifications:</li> </ul>                                                                                                  |

|          |              | <ul> <li>Added a new row for C<sub>HV_VDD_B</sub></li> <li>Added a fastrate an V</li> </ul>                                                                                 |

|          |              | <ul> <li>Added a footnote on V<sub>DD_HV_BALLAST</sub></li> <li>Added a new Note at the end of this section</li> </ul>                                                      |

|          |              |                                                                                                                                                                             |

|          |              | In section, Voltage monitor electrical characteristics                                                                                                                      |

|          |              | <ul> <li>In table, Voltage monitor electrical characteristics:</li> <li>Removed "V<sub>LVD FLASH</sub>" and "V<sub>LVD FLASH</sub> during low power mode using</li> </ul>   |

|          |              | LPBG as reference" rows                                                                                                                                                     |

|          |              | <ul> <li>Updated Fall and Rise trimmed Minimum values for V<sub>HVD_LV_cold</sub></li> </ul>                                                                                |

|          |              | In section, Supply current characteristics                                                                                                                                  |

|          |              | In table, Current consumption characteristics:                                                                                                                              |

|          |              | <ul> <li>Updated the footnote mentioned in the Condition column of I<sub>DD_STOP</sub> row</li> </ul>                                                                       |

|          |              | Updated all TBD values     In table Law Power Unit (LBL) Current consumption above staristics:                                                                              |

|          |              | <ul> <li>In table, Low Power Unit (LPU) Current consumption characteristics:</li> <li>Updated the typical value of LPU_STOP to 0.18 mA</li> </ul>                           |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | <ul> <li>In table, STANDBY Current consumption characteristics:</li> </ul>                                                                                                  |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | In section, AC specifications @ 3.3 V Range                                                                                                                                 |

|          |              | In table, Functional Pad AC Specifications @ 3.3 V Range:                                                                                                                   |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | In section, DC electrical specifications @ 3.3V Range                                                                                                                       |

|          |              | In table, DC electrical specifications @ 3.3V Range:                                                                                                                        |

|          |              | <ul> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                                                                                             |

|          |              | In section, AC specifications @ 5 V Range                                                                                                                                   |

|          |              | In table, Functional Pad AC Specifications @ 5 V Range:                                                                                                                     |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | <ul> <li>In section, DC electrical specifications @ 5 V Range</li> </ul>                                                                                                    |

|          |              | In table, DC electrical specifications @ 5 V Range:                                                                                                                         |

|          |              | <ul> <li>Updated Min and Max values for Pull_Ioh and Pull_Iol rows</li> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                          |

|          |              |                                                                                                                                                                             |

|          |              | In section, Reset pad electrical characteristics                                                                                                                            |

|          |              | <ul> <li>In table, Functional reset pad electrical specifications:</li> <li>Updated parameter column for V<sub>IH</sub>, V<sub>IL</sub> and V<sub>HYS</sub> rows</li> </ul> |

|          |              | • Updated Min and Max values for $V_{IH}$ and $V_{IL}$ rows                                                                                                                 |

|          |              |                                                                                                                                                                             |

|          |              | <ul> <li>In section, PORST electrical specifications</li> <li>In table, PORST electrical specifications:</li> </ul>                                                         |

|          |              | <ul> <li>Updated Unit and Min/Max values for V<sub>IH</sub> and V<sub>IL</sub> rows</li> </ul>                                                                              |

|          |              | . In contrast, land a subscience discuit and ADO companying share staristics                                                                                                |

|          |              | <ul> <li>In section, Input equivalent circuit and ADC conversion characteristics</li> <li>In table, ADC conversion characteristics (for 12-bit):</li> </ul>                 |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |