Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Package / Case Supplier Device Package | 176-LQFP Exposed Pad 176-LQFP (24x24)                              |

|----------------------------------------|--------------------------------------------------------------------|

| Mounting Type                          | Surface Mount                                                      |

| Operating Temperature                  | -40°C ~ 105°C (TA)                                                 |

| Oscillator Type                        | Internal                                                           |

| Data Converters                        | A/D 80x10b, 64x12b                                                 |

| Voltage - Supply (Vcc/Vdd)             | 3V ~ 5.5V                                                          |

| RAM Size                               | 512K x 8                                                           |

| EEPROM Size                            | -                                                                  |

| Program Memory Type                    | FLASH                                                              |

| Program Memory Size                    | 3MB (3M x 8)                                                       |

| Number of I/O                          | 129                                                                |

| Peripherals                            | DMA, LVD, POR, WDT                                                 |

| Connectivity                           | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG |

| Speed                                  | 80MHz/160MHz                                                       |

| Core Size                              | 32-Bit Dual-Core                                                   |

| Core Processor                         | e200z2, e200z4                                                     |

| Product Status                         | Active                                                             |

- Debug functionality

- e200z2 core:NDI per IEEE-ISTO 5001-2008 Class3+

- e200z4 core: NDI per IEEE-ISTO 5001-2008 Class 3+

- Timer

- 16 Periodic Interrupt Timers (PITs)

- Two System Timer Modules (STM)

- Three Software Watchdog Timers (SWT)

- 64 Configurable Enhanced Modular Input Output Subsystem (eMIOS) channels

- Device/board boundary Scan testing supported with Joint Test Action Group (JTAG) of IEEE 1149.1 and IEEE 1149.7 (CJTAG)

- Security

- Hardware Security Module (HSMv2)

- Password and Device Security (PASS) supporting advanced censorship and life-cycle management

- One Fault Collection and Control Unit (FCCU) to collect faults and issue interrupts

- · Functional Safety

- ISO26262 ASIL-B compliance

- Multiple operating modes

- Includes enhanced low power operation

**Family comparison**

### Table 1. MPC5746C Family Comparison1 (continued)

| Feature                                                      | MPC5745B    | MPC5744B    | MPC5746B            | MPC5744C                            | MPC5745C    | MPC5746C                         |  |  |

|--------------------------------------------------------------|-------------|-------------|---------------------|-------------------------------------|-------------|----------------------------------|--|--|

| I <sup>2</sup> C                                             | 4           | 4           | 4                   | 4                                   |             |                                  |  |  |

| SAI/I <sup>2</sup> S                                         | 3           | 3           | 3                   | 3                                   |             |                                  |  |  |

| FXOSC                                                        |             |             | 8 - 40              | ) MHz                               |             |                                  |  |  |

| SXOSC                                                        |             |             | 32 I                | KHz                                 |             |                                  |  |  |

| FIRC                                                         |             |             | 16 [                | ИНz                                 |             |                                  |  |  |

| SIRC                                                         |             |             | 128                 | KHz                                 |             |                                  |  |  |

| FMPLL                                                        |             |             | -                   | 1                                   |             |                                  |  |  |

| Low Power Unit<br>(LPU)                                      |             |             | Y                   | es                                  |             |                                  |  |  |

| FlexRay 2.1 (dual channel)                                   | Yes, 128 MB | Yes, 128 MB | Yes, 128 MB         |                                     | Yes, 128 MB |                                  |  |  |

| Ethernet (RMII,<br>MII + 1588, Muti<br>queue AVB<br>support) | 1           | 1           | 1                   | 1                                   |             |                                  |  |  |

| CRC                                                          |             |             | -                   | 1                                   |             |                                  |  |  |

| MEMU                                                         |             |             | 2                   | 2                                   |             |                                  |  |  |

| STCU2                                                        |             |             | -                   | 1                                   |             |                                  |  |  |

| HSM-v2<br>(security)                                         |             |             | Opti                | onal                                |             |                                  |  |  |

| Censorship                                                   |             |             | Y                   | es                                  |             |                                  |  |  |

| FCCU                                                         |             |             | -                   | 1                                   |             |                                  |  |  |

| Safety level                                                 |             |             | Specific functions  | ASIL-B certifiable                  |             |                                  |  |  |

| User MBIST                                                   |             |             | Y                   | es                                  |             |                                  |  |  |

| I/O Retention in Standby                                     |             |             | Y                   | es                                  |             |                                  |  |  |

| GPIO <sup>6</sup>                                            |             |             | Up to 264 GPI an    | d up to 246 GPIO                    |             |                                  |  |  |

| Debug                                                        |             |             | JTA                 | GC,                                 |             |                                  |  |  |

|                                                              |             |             | cJT                 | AG                                  |             |                                  |  |  |

| Nexus                                                        |             | Z4 N3+ (C   | Only available on 3 | 24BGA (developm                     | ent only))  |                                  |  |  |

|                                                              |             | Z2 N3+ (C   | only available on 3 | 24BGA (developm                     | ent only))  |                                  |  |  |

| Packages                                                     | 176 LQFP-EP | 176 LQFP-EP | 176 LQFP-EP         | 176 LQFP-EP 176 LQFP-EP 176 LQFP-EP |             |                                  |  |  |

|                                                              | 256 BGA     | 256 BGA     | 256 BGA             | 256 BGA 256 BGA 256 BGA,            |             |                                  |  |  |

|                                                              | 100 BGA     | 100 BGA     | 100 BGA             | 100 BGA                             | 100 BGA     | 324 BGA<br>(development<br>only) |  |  |

|                                                              |             |             |                     |                                     |             | 100 BGA                          |  |  |

<sup>1.</sup> Feature set dependent on selected peripheral multiplexing, table shows example. Peripheral availability is package dependent.

<sup>2.</sup> Based on 125°C ambient operating temperature and subject to full device characterization.

<sup>3.</sup> Contact NXP representative for part number

<sup>4.</sup> Additional SWT included when HSM option selected

<sup>5.</sup> See device datasheet and reference manual for information on to timer channel configuration and functions.

<sup>6.</sup> Estimated I/O count for largest proposed packages based on multiplexing with peripherals.

13

- 4. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating

- 5. VIN1\_CMP\_REF ≤ VDD\_HV\_A

- 6. This supply is shorted VDD\_HV\_A on lower packages.

- 7.  $T_J=150$ °C. Assumes  $T_A=125$ °C

- Assumes maximum θJA of 2s2p board. See Thermal attributes

### 4.3 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- Choice of generating supply voltage for the core area.

- Control of external NPN ballast transistor

- Generating core supply using internal ballast transistor

- Connecting an external 1.25 V (nominal) supply directly without the NPN ballast

- Internal generation of the 3.3 V flash supply when device connected in 5V applications

- External bypass of the 3.3 V flash regulator when device connected in 3.3V applications

- $\bullet$  Low voltage detector low threshold (LVD\_IO\_A\_LO) for  $V_{DD\_HV\_IO\_A\ supply}$

- $\bullet$  Low voltage detector high threshold (LVD\_IO\_A\_Hi) for  $V_{DD\_HV\_IO\_A\ supply}$

- Low voltage detector (LVD\_FLASH) for 3.3 V flash supply (VDD\_HV\_FLA)

- Various low voltage detectors (LVD\_LV\_x)

- High voltage detector (HVD\_LV\_cold) for 1.2 V digital core supply (VDD\_LV)

- Power on Reset (POR\_LV) for 1.25 V digital core supply (VDD\_LV)

- Power on Reset (POR\_HV) for 3.3 V to 5 V supply (VDD\_HV\_A)

The following bipolar transistors<sup>1</sup> are supported, depending on the device performance requirements. As a minimum the following must be considered when determining the most appropriate solution to maintain the device under its maximum power dissipation capability: current, ambient temperature, mounting pad area, duty cycle and frequency for Idd, collector voltage, etc

<sup>1.</sup> BCP56, MCP68 and MJD31are guaranteed ballasts.

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

Figure 2. Voltage regulator capacitance connection

#### **NOTE**

On BGA, VSS\_LV and VSS\_HV have been joined on substrate and renamed as VSS.

Table 8. Voltage regulator electrical specifications

| Symbol                             | Parameter                                                                   | Conditions                                                                                              | Min   | Тур              | Max  | Unit |

|------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------------------|------|------|

| C <sub>fp_reg</sub> <sup>1</sup>   | External decoupling / stability capacitor                                   | Min, max values shall be granted with respect to tolerance, voltage, temperature, and aging variations. | 1.32  | 2.2 <sup>2</sup> | 3    | μF   |

|                                    | Combined ESR of external capacitor                                          | _                                                                                                       | 0.001 | _                | 0.03 | Ohm  |

| C <sub>lp/ulp_reg</sub>            | External decoupling / stability capacitor for internal low power regulators | Min, max values shall be granted with respect to tolerance, voltage, temperature, and aging variations. | 0.8   | 1                | 1.4  | μF   |

|                                    | Combined ESR of external capacitor                                          | _                                                                                                       | 0.001 | _                | 0.1  | Ohm  |

| C <sub>be_fpreg</sub> <sup>3</sup> | Capacitor in parallel to base-                                              | BCP68 and BCP56                                                                                         |       | 3.3              |      | nF   |

|                                    | emitter                                                                     | MJD31                                                                                                   |       | 4.7              |      |      |

Table continues on the next page...

Table 10. Current consumption characteristics (continued)

| Symbol                              | Parameter                               | Conditions <sup>1</sup>                                                          | Min | Тур  | Max | Unit |

|-------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| I <sub>DD_BODY_2</sub>              | RUN Body Mode Profile Operating current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 246 | mA   |

|                                     |                                         | $T_a = 125^{\circ}C^5$                                                           |     |      |     |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                                     |                                         | SYS_CLK = 160MHz                                                                 |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 105°C                                                           | _   | _    | 235 | mA   |

|                                     |                                         | $T_a = 85^{\circ}C$                                                              | _   | _    | 210 | mA   |

| I <sub>DD_BODY_3</sub> 7            | RUN Body Mode Profile Operating current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 181 | mA   |

|                                     |                                         | $T_a = 125  ^{\circ}C^{5}$                                                       |     |      |     |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                                     |                                         | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 105 °C                                                          | _   | _    | 176 | mA   |

|                                     |                                         | $T_a = 85^{\circ}C$                                                              | _   | _    | 171 | mA   |

| I <sub>DD_BODY_4</sub> <sup>8</sup> | RUN Body Mode Profile Operating current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 264 | mA   |

|                                     |                                         | $T_a = 125  ^{\circ}C^{5}$                                                       |     |      |     |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                                     |                                         | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 105 °C                                                          | _   | _    | 176 | mA   |

|                                     |                                         | T <sub>a</sub> = 85 °C                                                           | _   | _    | 171 | mA   |

| I <sub>DD_STOP</sub>                | STOP mode Operating current             | $T_a = 125  {}^{\circ}C^9$                                                       | —   | -    | 49  | mA   |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 105 °C                                                          | -   | 10.6 | _   |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 85 °C                                                           | -   | 8.1  | _   |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                                     |                                         | T <sub>a</sub> = 25 °C                                                           | -   | 4.6  | _   |      |

|                                     |                                         | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

Table continues on the next page...

Table 10. Current consumption characteristics (continued)

| Symbol                                   | Parameter                           | Conditions <sup>1</sup>                | Min | Тур | Max | Unit |

|------------------------------------------|-------------------------------------|----------------------------------------|-----|-----|-----|------|

| I <sub>DD_HV_ADC_REF</sub> 10,<br>11, 11 | ADC REF Operating current           | $T_a = 125  ^{\circ}C^5$               |     | 200 | 400 | μΑ   |

| 11, 11                                   |                                     | 2 ADCs operating at 80 MHz             |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC\_REF} = 5.5 \text{ V}$ |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 105 °C                | _   | 200 | _   |      |

|                                          |                                     | 2 ADCs operating at 80 MHz             |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC\_REF} = 5.5 \text{ V}$ |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 85 °C                 | _   | 200 | _   |      |

|                                          |                                     | 2 ADCs operating at 80 MHz             |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC\_REF} = 5.5 \text{ V}$ |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 25 °C                 | _   | 200 | _   |      |

|                                          |                                     | 2 ADCs operating at 80 MHz             |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC\_REF} = 3.6 \text{ V}$ |     |     |     |      |

| I <sub>DD_HV_ADCx</sub> 11               | ADC HV Operating current            | $T_a = 125  ^{\circ}C^5$               | _   | 1.2 | 2   | mA   |

|                                          |                                     | ADC operating at 80 MHz                |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC} = 5.5 \text{ V}$      |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 25 °C                 | _   | 1   | 2   |      |

|                                          |                                     | ADC operating at 80 MHz                |     |     |     |      |

|                                          |                                     | $V_{DD\_HV\_ADC} = 3.6 \text{ V}$      |     |     |     |      |

| I <sub>DD_HV_FLASH</sub> 12              | Flash Operating current during read | $T_a = 125  ^{\circ}C^5$               | _   | 40  | 45  | mA   |

|                                          | access                              | 3.3 V supplies                         |     |     |     |      |

|                                          |                                     | 160 MHz frequency                      |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 105 °C                | _   | 40  | 45  |      |

|                                          |                                     | 3.3 V supplies                         |     |     |     |      |

|                                          |                                     | 160 MHz frequency                      |     |     |     |      |

|                                          |                                     | T <sub>a</sub> = 85 °C                 | _   | 40  | 45  |      |

|                                          |                                     | 3.3 V supplies                         |     |     |     |      |

|                                          |                                     | 160 MHz frequency                      |     |     |     |      |

- 1. The content of the Conditions column identifies the components that draw the specific current.

- 2. Single e200Z4 core cache disabled @80 MHz, no FlexRay, no ENET, 2 x CAN, 8 LINFlexD, 2 SPI, ADC0 and 1 used constantly, no HSM, Memory: 2M flash, 128K RAM RUN mode, Clocks: FIRC on, XOSC, PLL on, SIRC on for TOD, no 32KHz crystal (TOD runs off SIRC).

- 3. Recommended Transistors:MJD31 @ 85°C, 105°C and 125°C. In case of internal ballast mode, it is expected that the external ballast is not mounted and BAL\_SELECT\_INT pin is tied to VDD\_HV\_A supply on board. Internal ballast can be used for all use cases with current consumption upto 150mA

- 4. The power consumption does not consider the dynamic current of I/Os

- 5. Tj=150°C. Assumes Ta=125°C

- Assumes maximum θJA of 2s2p board. SeeThermal attributes

- e200Z4 core, 160MHz, cache enabled; e200Z2 core, 80MHz, no FlexRay, no ENET, 7 CAN, 16 LINFlexD, 4 SPI, 1x ADC used constantly, includes HSM at start-up / periodic use, Memory: 3M flash, 256K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

- e200Z4 core, 120MHz, cache enabled; e200Z2 core, 60MHz; no FlexRay, no ENET, 7 CAN, 16 LINFlexD, 4 SPI, 1x ADC used constantly, includes HSM at start-up / periodic use, Memory: 3M flash, 128K RAM, Clocks: FIRC on, XOSC on, PLL on, SIRC on, no 32KHz crystal

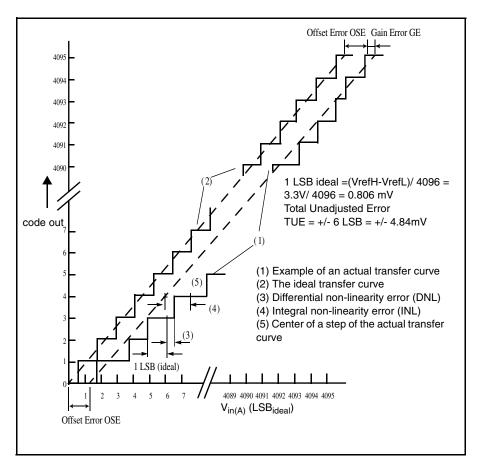

Figure 5. ADC characteristics and error definitions

Table 21. ADC conversion characteristics (for 10-bit) (continued)

| Symbol                           | Parameter                                                     | Conditions                             | Min | Typ <sup>1</sup> | Max  | Unit |

|----------------------------------|---------------------------------------------------------------|----------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                  | 80 MHz                                 | 550 | _                | _    | ns   |

| t <sub>total_conv</sub>          | Total Conversion time tsample + tconv (for standard channels) | 80 MHz                                 | 1   | _                | _    | μs   |

|                                  | Total Conversion time tsample + tconv (for extended channels) |                                        | 1.5 | _                | _    |      |

| C <sub>S</sub> <sup>5</sup>      | ADC input sampling capacitance                                | _                                      | _   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                   | _                                      | _   | _                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                   | _                                      | _   | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                 | V <sub>REF</sub> range = 4.5 to 5.5 V  | _   | _                | 0.3  | kΩ   |

|                                  | source                                                        | V <sub>REF</sub> range = 3.15 to 3.6 V | _   | _                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                          | _                                      | _   | _                | 825  | Ω    |

| INL                              | Integral non-linearity                                        | _                                      | -2  | _                | 2    | LSB  |

| DNL                              | Differential non-linearity                                    | _                                      | -1  | _                | 1    | LSB  |

| OFS                              | Offset error                                                  | _                                      | -4  | _                | 4    | LSB  |

| GNE                              | Gain error                                                    | _                                      | -4  | _                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                | 150 °C                                 | _   | _                | 2500 | nA   |

| (pad going to one<br>ADC)        | Max positive/negative injection                               |                                        | -5  | _                | 5    | mA   |

| ADO)                             | Max leakage (standard channel)                                | 105 °C <sub>TA</sub>                   | _   | 5                | 250  | nA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                           | Without current injection              | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                      | With current injection <sup>6</sup>    |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                           |                                        |     |                  | < 1  | μs   |

- 1. Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- 3. During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>sample</sub> depend on programming.

- 4. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 65

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: Absolute maximum ratings) must be honored to meet TUE spec quoted here

# 6.1.2 Analog Comparator (CMP) electrical specifications Table 22. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                                             | Min.     | Тур. | Max.                    | Unit             |

|--------------------|-------------------------------------------------------------------------|----------|------|-------------------------|------------------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)                         | _        | _    | 250                     | μΑ               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)                          | _        | 5    | 11                      | μΑ               |

| $V_{AIN}$          | Analog input voltage                                                    | $V_{SS}$ | _    | V <sub>IN1_CMP_RE</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage 1, 1                                        | -47      | _    | 47                      | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>2, 2</sup>                            | _        | 1    | 25                      | mV               |

|                    | • CR0[HYSTCTR] = 00                                                     | _        | 20   | 50                      | mV               |

|                    | • CR0[HYSTCTR] = 01                                                     | _        | 40   | 70                      | mV               |

|                    | CR0[HYSTCTR] = 10                                                       | _        | 60   | 105                     | mV               |

|                    | • CR0[HYSTCTR] = 11                                                     |          |      | 105                     | 111 V            |

| t <sub>DHS</sub>   | Propagation Delay, High Speed Mode (Full Swing) <sup>1,</sup> 3, 3      | _        | _    | 250                     | ns               |

| t <sub>DLS</sub>   | Propagation Delay, Low power Mode (Full Swing) 1, 3                     | _        | 5    | 21                      | μs               |

|                    | Analog comparator initialization delay, High speed mode <sup>4, 4</sup> | _        | 4    |                         | μs               |

|                    | Analog comparator initialization delay, Low speed mode <sup>4</sup>     | _        | 100  |                         | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (when enabled)                                  |          |      |                         |                  |

|                    | 3.3V Reference Voltage                                                  | _        | 6    | 9                       | μA               |

|                    | 5V Reference Voltage                                                    | _        | 10   | 16                      | μA               |

| INL                | 6-bit DAC integral non-linearity                                        | -0.5     | _    | 0.5                     | LSB <sup>5</sup> |

| DNL                | 6-bit DAC differential non-linearity                                    | -0.8     | _    | 0.8                     | LSB              |

- 1. Measured with hysteresis mode of 00

- 2. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD\ HV\ A}$ -0.6V

- 3. Full swing = VIH, VIL

- 4. Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

- 5.  $1 LSB = V_{reference}/64$

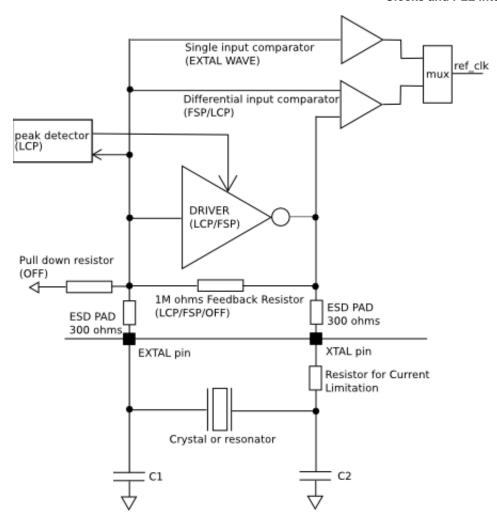

### 6.2 Clocks and PLL interfaces modules

#### 6.2.1 Main oscillator electrical characteristics

This device provides a driver for oscillator in pierce configuration with amplitude control. Controlling the amplitude allows a more sinusoidal oscillation, reducing in this way the EMI. Other benefits arises by reducing the power consumption. This Loop Controlled Pierce (LCP mode) requires good practices to reduce the stray capacitance of traces between crystal and MCU.

An operation in Full Swing Pierce (FSP mode), implemented by an inverter is also available in case of parasitic capacitances and cannot be reduced by using crystal with high equivalent series resistance. For this mode, a special care needs to be taken regarding the serial resistance used to avoid the crystal overdrive.

Other two modes called External (EXT Wave) and disable (OFF mode) are provided. For EXT Wave, the drive is disabled and an external source of clock within CMOS level based in analog oscillator supply can be used. When OFF, EXTAL is pulled down by 240 Kohms resistor and the feedback resistor remains active connecting XTAL through EXTAL by 1M resistor.

Figure 7. Oscillator connections scheme

Table 23. Main oscillator electrical characteristics

| Symbol                | Parameter            | Mode                      | Conditions | Min    | Тур | Max | Unit            |  |

|-----------------------|----------------------|---------------------------|------------|--------|-----|-----|-----------------|--|

| f <sub>xoschs</sub>   | Oscillator frequency | FSP/LCP                   |            | 8      |     | 40  | MHz             |  |

| 9 <sub>m</sub> XOSCHS | Driver               | LCP                       |            |        | 23  |     | mA/V            |  |

|                       | Transconduct ance    | FSP                       |            |        | 33  |     |                 |  |

| V <sub>XOSCHS</sub>   | Oscillation          | LCP <sup>1, 2, 1, 2</sup> | 8 MHz      |        | 1.0 |     | V <sub>PP</sub> |  |

|                       | Amplitude            | Amplitude                 |            | 16 MHz |     | 1.0 |                 |  |

|                       |                      |                           | 40 MHz     |        | 0.8 |     |                 |  |

| T <sub>XOSCHSSU</sub> | Startup time         | FSP/LCP <sup>1</sup>      | 8 MHz      |        | 2   |     | ms              |  |

|                       |                      |                           | 16 MHz     | 1      | 1   |     |                 |  |

|                       |                      |                           | 40 MHz     | 1      | 0.5 |     |                 |  |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

37

### **NOTE**

The above start up time of 1 us is equivalent to 16 cycles of 16 MHz.

# 6.2.4 128 KHz Internal RC oscillator Electrical specifications

Table 26. 128 KHz Internal RC oscillator electrical specifications

| Symbol                         | Parameter              | Condition     | Min | Тур | Max   | Unit  |

|--------------------------------|------------------------|---------------|-----|-----|-------|-------|

| F <sub>oscu</sub> <sup>1</sup> | Oscillator frequency   | Calibrated    | 119 | 128 | 136.5 | KHz   |

|                                | Temperature dependence |               |     |     | 600   | ppm/C |

|                                | Supply dependence      |               |     |     | 18    | %/V   |

|                                | Supply current         | Clock running |     |     | 2.75  | μΑ    |

|                                |                        | Clock stopped |     |     | 200   | nA    |

1. Vdd=1.2 V, 1.32V, T<sub>a</sub>=-40 C, 125 C

# 6.2.5 PLL electrical specifications

Table 27. PLL electrical specifications

| Parameter                        | Min       | Тур | Max          | Unit | Comments                                                    |

|----------------------------------|-----------|-----|--------------|------|-------------------------------------------------------------|

| Input Frequency                  | 8         |     | 40           | MHz  |                                                             |

| VCO Frequency Range              | 600       |     | 1280         | MHz  |                                                             |

| Duty Cycle at pllclkout          | 48%       |     | 52%          |      | This specification is guaranteed at PLL IP boundary         |

| Period Jitter                    |           |     | See Table 28 | ps   | NON SSCG mode                                               |

| TIE                              |           |     | See Table 28 |      | at 960 M Integrated over 1MHz offset not valid in SSCG mode |

| Modulation Depth (Center Spread) | +/- 0.25% |     | +/- 3.0%     |      |                                                             |

| Modulation Frequency             |           |     | 32           | KHz  |                                                             |

| Lock Time                        |           |     | 60           | μs   | Calibration mode                                            |

Table 28. Jitter calculation

| Type of jitter | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)                                                 |

|----------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|

| Period Jitter  | 60 ps                                                                 | 3% of pllclkout1,2                                                     | Modulation depth                                                        | 0.1% of pliclkout1,2                                             | +/-( $J_{SN}$ + $J_{SDM}$ + $J_{SSCG}$ + $N$ <sup>[4]</sup> × $J_{RJ}$ ) |

Table continues on the next page...

#### **Memory interfaces**

Table 33. Flash memory AC timing specifications (continued)

| Symbol               | Characteristic                                                                                                                                                                                                               | Min                                  | Typical | Max                                              | Units |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|--------------------------------------------------|-------|

| t <sub>drcv</sub>    | Time to recover once exiting low power mode.                                                                                                                                                                                 | 16 plus seven system clock periods.  | _       | 45 plus seven system clock periods               | μs    |

| t <sub>aistart</sub> | Time from 0 to 1 transition of UT0-AIE initiating a Margin Read or Array Integrity until the UT0-AID bit is cleared. This time also applies to the resuming from a suspend or breakpoint by clearing AISUS or clearing NAIBP | _                                    | _       | 5                                                | ns    |

| t <sub>aistop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating an Array Integrity abort until the UT0-AID bit is set. This time also applies to the UT0-AISUS to UT0-AID setting in the event of a Array Integrity suspend request.       | _                                    | _       | 80<br>plus fifteen<br>system<br>clock<br>periods | ns    |

| t <sub>mrstop</sub>  | Time from 1 to 0 transition of UT0-AIE initiating a Margin Read abort until the UT0-AID bit is set. This time also applies to the UT0-AISUS to UT0-AID setting in the event of a Margin Read suspend request.                | 10.36 plus four system clock periods | _       | 20.42<br>plus four<br>system<br>clock<br>periods | μѕ    |

# 6.3.6 Flash read wait state and address pipeline control settings

The following table describes the recommended RWSC and APC settings at various operating frequencies based on specified intrinsic flash access times of the flash module controller array at 125 °C.

Table 34. Flash Read Wait State and Address Pipeline Control Combinations

| Flash frequency             | RWSC setting | APC setting |

|-----------------------------|--------------|-------------|

| 0 MHz < fFlash <= 33 MHz    | 0            | 0           |

| 33 MHz < fFlash <= 100 MHz  | 2            | 1           |

| 100 MHz < fFlash <= 133 MHz | 3            | 1           |

| 133 MHz < fFlash <= 160 MHz | 4            | 1           |

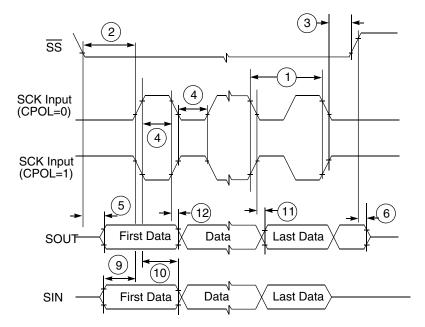

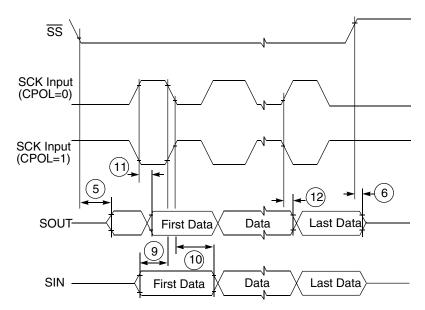

Figure 10. DSPI classic SPI timing — slave, CPHA = 0

Figure 11. DSPI classic SPI timing — slave, CPHA = 1

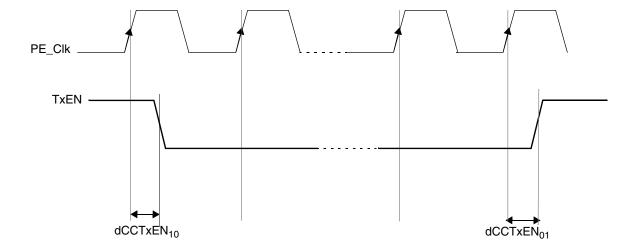

Figure 18. TxEN signal propagation delays

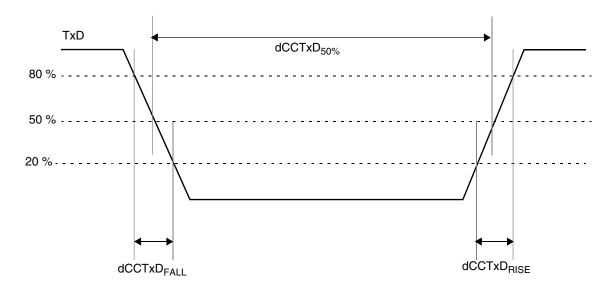

### 6.4.2.3 TxD

Figure 19. TxD Signal

Table 39. TxD output characteristics

| Name                                                   | Description <sup>1</sup>                                   | Min   | Max            | Unit |

|--------------------------------------------------------|------------------------------------------------------------|-------|----------------|------|

| dCCT <sub>xAsym</sub>                                  | Asymmetry of sending CC @ 25 pF load (=dCCTxD50% - 100 ns) | -2.45 | 2.45           | ns   |

| dCCTxD <sub>RISE25</sub> +dCCTx<br>D <sub>FALL25</sub> | Sum of Rise and Fall time of TxD signal at the output      | _     | 9 <sup>2</sup> | ns   |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

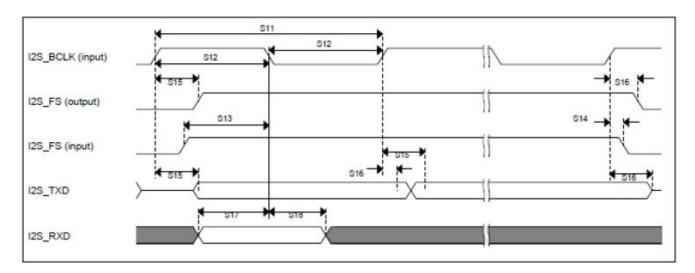

Table 44. Slave mode SAI Timing (continued)

| No  | Parameter                                 | Parameter Value |     | Unit |

|-----|-------------------------------------------|-----------------|-----|------|

|     |                                           | Min             | Max |      |

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | -               | 28  | ns   |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0               | -   | ns   |

| S17 | SAI_RXD setup before SAI_BCLK             | 10              | -   | ns   |

| S18 | SAI_RXD hold after SAI_BCLK               | 2               | -   | ns   |

Figure 24. Slave mode SAI Timing

# 6.5 Debug specifications

# 6.5.1 JTAG interface timing

Table 45. JTAG pin AC electrical characteristics <sup>1</sup>

| #  | Symbol                                | Characteristic                                   | Min  | Max                 | Unit |

|----|---------------------------------------|--------------------------------------------------|------|---------------------|------|

| 1  | t <sub>JCYC</sub>                     | TCK Cycle Time <sup>2, 2</sup>                   | 62.5 | _                   | ns   |

| 2  | t <sub>JDC</sub>                      | TCK Clock Pulse Width                            | 40   | 60                  | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK Rise and Fall Times (40% - 70%)              | _    | 3                   | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI Data Setup Time                         | 5    | _                   | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI Data Hold Time                          | 5    | _                   | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK Low to TDO Data Valid                        | _    | 20 <sup>3, 3</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK Low to TDO Data Invalid                      |      | _                   | ns   |

| 8  | t <sub>TDOHZ</sub>                    | t <sub>TDOHZ</sub> TCK Low to TDO High Impedance |      | 15                  | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK Falling Edge to Output Valid                 | _    | 600 <sup>4, 4</sup> | ns   |

Table continues on the next page...

MPC5746C Microcontroller Datasheet Data Sheet, Rev. 5.1, 05/2017.

#### Thermal attributes

| Board type        | Symbol            | Description                                                       | 176LQFP | Unit | Notes |

|-------------------|-------------------|-------------------------------------------------------------------|---------|------|-------|

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 17.8    | °C/W | 1, 3  |

| _                 | $R_{\theta JB}$   | Thermal resistance, junction to board                             | 10.9    | °C/W | 44    |

| _                 | R <sub>0JC</sub>  | Thermal resistance, junction to case                              | 8.4     | °C/W | 55    |

| _                 | $\Psi_{ m JT}$    | Thermal resistance, junction to package top                       | 0.5     | °C/W | 66    |

| _                 | Ψ <sub>ЈВ</sub>   | Thermal characterization parameter, junction to package bottom    | 0.3     | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                       | 324 MAPBGA | Unit | Notes  |

|-------------------|-------------------|-------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | $R_{\theta JA}$   | Thermal resistance, junction to ambient (natural convection)      | 31.0       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal resistance, junction to ambient (natural convection)      | 24.3       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>eJMA</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 23.5       | °C/W | 1, 3   |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)  | 20.1       | °C/W | 1,3    |

Table continues on the next page...

#### Thermal attributes

| Board type | Symbol               | Description                                                                                        | 256 MAPBGA | Unit | Notes |

|------------|----------------------|----------------------------------------------------------------------------------------------------|------------|------|-------|

| _          | R <sub>eJC</sub>     | Thermal resistance, junction to case                                                               | 7.9        | °C/W | 55    |

| _          | $\Psi_{ m JT}$       | Thermal characterization parameter, junction to package top outside center (natural convection)    | 0.2        | °C/W | 66    |

| _          | R <sub>0JB_CSB</sub> | Thermal characterization parameter, junction to package bottom outside center (natural convection) | 9.0        | °C/W | 77    |

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                       | 100 MAPBGA | Unit | Notes   |

|-------------------|-------------------|-------------------------------------------------------------------|------------|------|---------|

| Single-layer (1s) | $R_{\theta JA}$   | Thermal resistance, junction to ambient (natural convection)      | 50.9       | °C/W | 1, 21,2 |

| Four-layer (2s2p) | $R_{\theta JA}$   | Thermal resistance, junction to ambient (natural convection)      | 27.0       | °C/W | 1,2,33  |

| Single-layer (1s) | R <sub>ӨЈМА</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 38.0       | °C/W | 1,3     |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./ min. air speed) | 22.2       | °C/W | 1,3     |

Table continues on the next page...

75

# Table 51. Revision History (continued)

| Rev. No. | Date                | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 4    | 9 March 2016        | In section, Voltage regulator electrical characteristics     In table, Voltage regulator electrical specifications:         Updated the footnote on V <sub>DD_HV_BALLAST</sub>                                                                                                                                                                                                                                                                     |

| Rev 5    | 27 February<br>2017 | <ul> <li>In Family Comparison section:         <ul> <li>Updated the "MPC5746C Family Comparison" table.</li> <li>added "NVM Memory Map 1", "NVM Memory Map 2", and "RAM Memory Map" tables.</li> </ul> </li> </ul>                                                                                                                                                                                                                                 |

|          |                     | <ul> <li>Updated the product version, flash memory size and optional fields information in<br/>Ordering Information section.</li> </ul>                                                                                                                                                                                                                                                                                                            |

|          |                     | <ul> <li>In Recommended Operating Conditions section, removed the note related to additional<br/>crossover current.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

|          |                     | VDD_HV_C row added in "Voltage regulator electrical specifications" table in Voltage regulator electrical characteristics section.                                                                                                                                                                                                                                                                                                                 |

|          |                     | <ul> <li>In Voltage Monitor Electrical Characteristics section, updated the "Trimmed" Fall and<br/>Rise specs of VHVD_LV_cold parameter in "Voltage Monitor Electrical Characteristics"<br/>table.</li> </ul>                                                                                                                                                                                                                                      |

|          |                     | <ul> <li>In AC Electrical Specifications: 3.3 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> <li>In DC Electrical Specifications: 3.3 V Range section, changed the occurrences of</li> </ul>                                                                                                                                                                                              |

|          |                     | <ul> <li>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in the table.</li> <li>In AC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> <li>In DC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in the table.</li> </ul> |

|          |                     | <ul> <li>In "Flash memory AC timing specifications" table in Flash memory AC timing specifications section:</li> <li>Updated the "t<sub>psus</sub>" typ value from 7 us to 9.4 us.</li> <li>Updated the "t<sub>psus</sub>" max value from 9.1 us to 11.5 us.</li> </ul>                                                                                                                                                                            |

|          |                     | Added "Continuous SCK Timing" table in DSPI timing section.                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                     | <ul> <li>Added "ADC pad leakage" at 105°C TA conditions in "ADC conversion characteristics<br/>(for 12-bit)" table in ADC electrical specifications section.</li> </ul>                                                                                                                                                                                                                                                                            |

|          |                     | <ul> <li>In "STANDBY Current consumption characteristics" table in Supply current characteristics section:</li> <li>Updated the Typ and max values of IDD Standby current.</li> <li>Added IDD Standby3 current spec for FIRC ON.</li> </ul>                                                                                                                                                                                                        |

|          |                     | Removed IVDDHV and IVDDLV specs in 16 MHz RC Oscillator electrical specifications section.                                                                                                                                                                                                                                                                                                                                                         |

|          |                     | <ul> <li>Added Reset Sequence section, with Reset Sequence Duration, BAF execution duration<br/>section, and Reset Sequence Distribution as its sub-sections.</li> </ul>                                                                                                                                                                                                                                                                           |

Table continues on the next page...

#### **Revision History**

# Table 51. Revision History (continued)

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                       |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 5.1  | 22 May 2017 | Removed the Introduction section from Section 4 "General".                                                                                                                                                                |

|          |             | In AC Specifications@3.3V section, removed note related to Cz results and added two notes.                                                                                                                                |

|          |             | In AC Specifications@5V section, added two notes.                                                                                                                                                                         |

|          |             | <ul> <li>In ADC Electrical Specifications section, added spec value of "ADC Analog Pad" at Max<br/>leakage (standard channel)@ 105 C T<sub>A</sub> in "ADC conversion characteristics (for 10-bit)"<br/>table.</li> </ul> |

|          |             | In PLL Electrical Specifications section, updated the first footnote of "Jitter calculation" table.                                                                                                                       |

|          |             | In Analog Comparator Electrical Specifications section, updated the TDLS (propagation delay, low power mode) max value in "Comparator and 6-bit DAC electrical specifications" table to 21 us.                            |

|          |             | <ul> <li>In Recommended Operating Conditions section, updated the footnote link to T<sub>A</sub> in<br/>"Recommended operating conditions (V DD_HV_x = 5V)" table.</li> </ul>                                             |