Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4                                                          |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Speed                      | 80MHz/160MHz                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG      |

| Peripherals                | DMA, LVD, POR, WDT                                                      |

| Number of I/O              | 178                                                                     |

| Program Memory Size        | 3MB (3M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 80x10b, 64x12b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 256-LBGA                                                                |

| Supplier Device Package    | 256-MAPPBGA (17x17)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746ck1ammj6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

| Symbol                                                                                   | Parameter                                                                                                     | Conditions <sup>1</sup>                                                                 | Min         | Max                                                                                            | Unit |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------|------|

| $\begin{array}{c} V_{DD\_HV\_A},  V_{DD\_HV\_B}, \\ V_{DD\_HV\_C}{}^{2,  3} \end{array}$ | <sup>2</sup> _A, V <sub>DD_HV_B</sub> , 3.3 V - 5. 5V input/output supply voltage —<br>D_HV_c <sup>2, 3</sup> |                                                                                         | -0.3        | 6.0                                                                                            | V    |

| V <sub>DD_HV_FLA</sub> <sup>4, 5</sup>                                                   | 3.3 V flash supply voltage (when supplying from an external source in bypass mode)                            |                                                                                         | -0.3        | 3.63                                                                                           | V    |

| V <sub>DD_LP_DEC</sub> <sup>6</sup>                                                      | Decoupling pin for low power regulators <sup>7</sup>                                                          | _                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>DD_HV_ADC1_REF</sub> <sup>8</sup>                                                 | 3.3 V / 5.0 V ADC1 high reference voltage                                                                     | —                                                                                       | -0.3        | 6                                                                                              | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub>                                       | 3.3 V to 5.5V ADC supply voltage                                                                              | _                                                                                       | -0.3        | 6.0                                                                                            | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub>                                       | 3.3V to 5.5V ADC supply ground                                                                                | _                                                                                       | -0.1        | 0.1                                                                                            | V    |

| V <sub>DD_LV</sub> <sup>9, 10, 10, 11, 11, 12</sup>                                      | Core logic supply voltage                                                                                     | —                                                                                       | -0.3        | 1.32                                                                                           | V    |

| V <sub>INA</sub>                                                                         | Voltage on analog pin with respect to ground (V <sub>SS_HV</sub> )                                            | _                                                                                       | -0.3        | Min (V <sub>DD_HV_x</sub> ,<br>V <sub>DD_HV_ADCx</sub> ,<br>V <sub>DD_ADCx_REF</sub> )<br>+0.3 | V    |

| V <sub>IN</sub>                                                                          | Voltage on any digital pin with respect to ground ( $V_{SS_HV}$ )                                             | Relative to<br>V <sub>DD_HV_A</sub> ,<br>V <sub>DD_HV_B</sub> ,<br>V <sub>DD_HV_C</sub> | -0.3        | V <sub>DD_HV_x</sub> + 0.3                                                                     | V    |

| I <sub>INJPAD</sub>                                                                      | Injected input current on any pin during overload condition                                                   | Always                                                                                  | -5          | 5                                                                                              | mA   |

| I <sub>INJSUM</sub>                                                                      | Absolute sum of all injected input currents during overload condition                                         | _                                                                                       | -50         | 50                                                                                             | mA   |

| T <sub>ramp</sub>                                                                        | Supply ramp rate                                                                                              | _                                                                                       | 0.5 V / min | 100V/ms                                                                                        | —    |

| T <sub>A</sub> <sup>13</sup>                                                             | Ambient temperature                                                                                           | —                                                                                       | -40         | 125                                                                                            | °C   |

| T <sub>STG</sub>                                                                         | Storage temperature                                                                                           | _                                                                                       | -55         | 165                                                                                            | °C   |

| Table 5. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

- 1. All voltages are referred to VSS\_HV unless otherwise specified

- 2. VDD\_HV\_B and VDD\_HV\_C are common together on the 176 LQFP-EP package.

- Allowed V<sub>DD\_HV\_x</sub> = 5.5–6.0 V for 60 seconds cumulative time with no restrictions, for 10 hours cumulative time device in reset, T<sub>J</sub>= 150 °C, remaining time at or below 5.5 V.

- 4. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 5. VDD\_HV\_FLA must be disconnected from ANY power sources when VDD\_HV\_A = 5V

- 6. This pin should be decoupled with low ESR 1  $\mu$ F capacitor.

- 7. Not available for input voltage, only for decoupling internal regulators

- 8. 10-bit ADC does not have dedicated reference and its reference is bonded to 10-bit ADC supply(VDD\_HV\_ADC0) inside the package.

- Allowed 1.45 1.5 V for 60 seconds cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time as defined in footnotes 10 and 11.

- 10. Allowed 1.38 1.45 V- for 10 hours cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time as defined in footnote 11.

- 11. 1.32 1.38 V range allowed periodically for supply with sinusoidal shape and average supply value below 1.326 V at maximum T<sub>J</sub> = 150 °C.

- 12. If HVD on core supply (V<sub>HVD LV x</sub>) is enabled, it will generate a reset when supply goes above threshold.

- 13.  $T_J=150^{\circ}C$ . Assumes  $T_A=125^{\circ}C$

- Assumes maximum θJA for 2s2p board. See Thermal attributes

#### General

### Table 6. Recommended operating conditions ( $V_{DD HV x} = 3.3 V$ ) (continued)

| Symbol                      | Parameter                       | Conditions <sup>1</sup>       | Min <sup>2</sup> | Мах | Unit |

|-----------------------------|---------------------------------|-------------------------------|------------------|-----|------|

| T <sub>A</sub> <sup>8</sup> | Ambient temperature under bias  | f <sub>CPU</sub> ≤ 160<br>MHz | -40              | 125 | °C   |

| TJ                          | Junction temperature under bias |                               | -40              | 150 | °C   |

1. All voltages are referred to  $V_{SS\ HV}$  unless otherwise specified

- 2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

- 3. VDD\_HV\_FLA must be connected to VDD\_HV\_A when VDD\_HV\_A = 3.3V

- 4. Only applicable when supplying from external source.

- 5. VDD\_LV supply pins should never be grounded (through a small impedance). If these are not driven, they should only be left floating.

- 6. VIN1\_CMP\_REF  $\leq$  VDD\_HV\_A

- 7. This supply is shorted VDD\_HV\_A on lower packages.

- 8.  $T_J$ =150°C. Assumes  $T_A$ =125°C

- Assumes maximum  $\theta$ JA of 2s2p board. See Thermal attributes

### NOTE

If VDD\_HV\_A is in 5V range, it is necessary to use internal Flash supply 3.3V regulator. VDD\_HV\_FLA should not be supplied externally and should only have decoupling capacitor.

### Table 7. Recommended operating conditions ( $V_{DD_HV_x} = 5 V$ )

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup>       | Min <sup>2</sup>                                   | Max              | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------|------------------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | —                             | 4.5                                                | 5.5              | V    |

| $V_{DD_HV_B}$                                      |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_C</sub>                               |                                                             |                               |                                                    |                  |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | —                             | 3.15                                               | 3.6              | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              | —                             | 3.15                                               | 5.5              | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                             | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 5.5              | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                             | -0.1                                               | 0.1              | V    |

| V <sub>DD_LV</sub> <sup>4</sup>                    | Core supply voltage                                         |                               | 1.2                                                | 1.32             | V    |

| V <sub>IN1_CMP_REF</sub> <sup>5, 6</sup>           | Analog Comparator DAC reference voltage                     | _                             | 3.15                                               | 5.5 <sup>5</sup> | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | _                             | -3.0                                               | 3.0              | mA   |

| T <sub>A</sub> <sup>7</sup>                        | Ambient temperature under bias                              | f <sub>CPU</sub> ≤ 160<br>MHz | -40                                                | 125              | °C   |

| TJ                                                 | Junction temperature under bias                             | _                             | -40                                                | 150              | °C   |

1. All voltages are referred to  $V_{\text{SS}\ \text{HV}}$  unless otherwise specified

2. Device will be functional down (and electrical specifications as per various datasheet parameters will be guaranteed) to the point where one of the LVD/HVD resets the device. When voltage drops outside range for an LVD/HVD, device is reset.

3. When VDD\_HV is in 5 V range, VDD\_HV\_FLA cannot be supplied externally. This pin is decoupled with  $C_{flash_{reg}}$ .

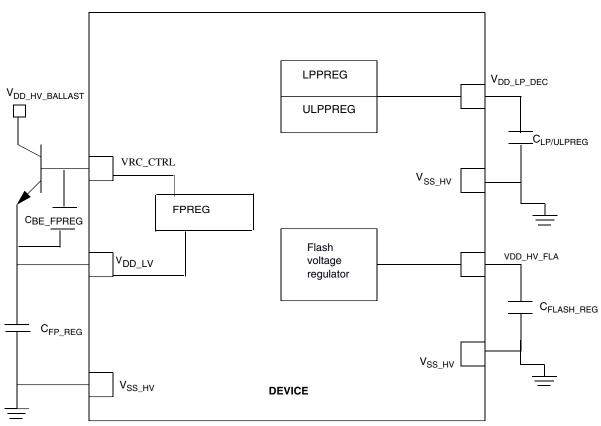

Figure 2. Voltage regulator capacitance connection

## NOTE

On BGA, VSS\_LV and VSS\_HV have been joined on substrate and renamed as VSS.

| Table 8. | Voltage regulator electrical specifications |

|----------|---------------------------------------------|

|----------|---------------------------------------------|

| Symbol                             | Parameter                                                                         | Conditions                                                                                                       | Min   | Тур              | Max  | Unit |

|------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------------------|------|------|

| C <sub>fp_reg</sub> 1              | External decoupling / stability capacitor                                         | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 1.32  | 2.2 <sup>2</sup> | 3    | μF   |

|                                    | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.03 | Ohm  |

| C <sub>lp/ulp_reg</sub>            | External decoupling / stability<br>capacitor for internal low power<br>regulators | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations. | 0.8   | 1                | 1.4  | μF   |

|                                    | Combined ESR of external capacitor                                                | —                                                                                                                | 0.001 | _                | 0.1  | Ohm  |

| C <sub>be_fpreg</sub> <sup>3</sup> | Capacitor in parallel to base-                                                    | BCP68 and BCP56                                                                                                  |       | 3.3              |      | nF   |

|                                    | emitter                                                                           | MJD31                                                                                                            | ]     | 4.7              |      |      |

Table continues on the next page ...

| Table 8. Voltage regulator electrical specifications (continued) | Table 8. | Voltage regulator | electrical s | specifications ( | (continued) |

|------------------------------------------------------------------|----------|-------------------|--------------|------------------|-------------|

|------------------------------------------------------------------|----------|-------------------|--------------|------------------|-------------|

| Symbol                                       | Parameter                                                                           | Conditions                                                                                                                                                                                                              | Min   | Тур | Max  | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| C <sub>flash_reg</sub> <sup>4</sup>          | External decoupling / stability<br>capacitor for internal Flash<br>regulators       | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1.32  | 2.2 | 3    | μF   |

|                                              | Combined ESR of external<br>capacitor                                               | —                                                                                                                                                                                                                       | 0.001 |     | 0.03 | Ohm  |

| $C_{_{HV\_VDD\_A}}$                          | VDD_HV_A supply capacitor <sup>5, 5</sup>                                           | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| $C_{_{HV\_VDD\_B}}$                          | VDD_HV_B supply capacitor <sup>5</sup>                                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| $C_{_{HV\_VDD\_C}}$                          | VDD_HV_C supply capacitor <sup>5</sup>                                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| C <sub>HV_ADC0</sub><br>C <sub>HV_ADC1</sub> | HV ADC supply decoupling<br>capacitances                                            | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 1     |     | _    | μF   |

| C <sub>HV_ADR</sub> <sup>6</sup>             | HV ADC SAR reference supply<br>decoupling capacitances                              | Min, max values shall be granted<br>with respect to tolerance, voltage,<br>temperature, and aging<br>variations.                                                                                                        | 0.47  |     | _    | μF   |

| V <sub>DD_HV_BALL</sub>                      | FPREG Ballast collector supply voltage                                              | When collector of NPN ballast is<br>directly supplied by an on board<br>supply source (not shared with<br>VDD_HV_A supply pin) without<br>any series resistance, that is,<br>R <sub>C_BALLAST</sub> less than 0.01 Ohm. | 2.25  | _   | 5.5  | V    |

| R <sub>C_BALLAST</sub>                       | Series resistor on collector of<br>FPREG ballast                                    | When VDD_HV_BALLAST is<br>shorted to VDD_HV_A on the<br>board                                                                                                                                                           | _     | _   | 0.1  | Ohm  |

| t <sub>SU</sub>                              | Start-up time with external<br>ballastafter main supply<br>(VDD_HV_A) stabilization | Cfp_reg = 3 μF                                                                                                                                                                                                          | _     | 74  |      | μs   |

| t <sub>SU_int</sub>                          | Start-up time with internal ballast after main supply (VDD_HV_A) stabilization      | Cfp_reg = 3 μF                                                                                                                                                                                                          | _     | 103 |      | μs   |

| t <sub>ramp</sub>                            | Load current transient                                                              | lload from 15% to 55%<br>$C_{fp_{reg}} = 3 \ \mu F$                                                                                                                                                                     |       | 1.0 |      | μs   |

- Split capacitance on each pair VDD\_LV pin should sum up to a total value of C<sub>fp\_reg</sub>

Typical values will vary over temperature, voltage, tolerance, drift, but total variation must not exceed minimum and maximum values.

- 3. Ceramic X7R or X5R type with capacitance-temperature characteristics +/-15% of -55 degC to +125degC is recommended. The tolerance +/-20% is acceptable.

- 4. It is required to minimize the board parasitic inductance from decoupling capacitor to VDD\_HV\_FLA pin and the routing inductance should be less than 1nH.

#### General

| Symbol                 | Parameter     | State                                               | Conditions | Configuration |                             |               | Threshold I |        |        | Unit   |        |        |   |  |

|------------------------|---------------|-----------------------------------------------------|------------|---------------|-----------------------------|---------------|-------------|--------|--------|--------|--------|--------|---|--|

|                        |               |                                                     |            | Power Up      | Mask<br>Opt <sup>2, 2</sup> | Reset<br>Type | Min         | Тур    | Max    | V      |        |        |   |  |

| V <sub>LVD_LV_PD</sub> | LV supply low | ow Fall Untrimmed No Yes Function Disabled at Start |            |               |                             |               |             |        |        |        |        |        |   |  |

| 2_cold                 |               |                                                     | Trimmed    | _             |                             |               |             |        | al     | 1.1400 | 1.1550 | 1.1750 | V |  |

| 1                      |               | Rise                                                | Untrimmed  |               |                             |               |             |        |        |        |        |        |   |  |

|                        |               |                                                     | Trimmed    |               |                             |               | 1.1600      | 1.1750 | 1.1950 | V      |        |        |   |  |

Table 9. Voltage monitor electrical characteristics (continued)

1. All monitors that are active at power-up will gate the power up recovery and prevent exit from POWERUP phase until the minimum level is crossed. These monitors can in some cases be masked during normal device operation, but when active will always generate a destructive reset.

2. Voltage monitors marked as non maskable are essential for device operation and hence cannot be masked.

3. There is no voltage monitoring on the V<sub>DD\_HV\_ADC0</sub>, V<sub>DD\_HV\_ADC1</sub>, V<sub>DD\_HV\_B</sub> and V<sub>DD\_HV\_C</sub> I/O segments. For applications requiring monitoring of these segments, either connect these to V<sub>DD\_HV\_A</sub> at the PCB level or monitor externally.

# 4.5 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

### NOTE

The ballast must be chosen in accordance with the ballast transistor supplier operating conditions and recommendations.

| Symbol                         | Parameter                                  | Conditions <sup>1</sup>                      | Min | Тур | Max | Unit |

|--------------------------------|--------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>DD_BODY_1</sub><br>2, 3 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + | -   | _   | 147 | mA   |

| 2, 0                           |                                            | 2 x HV ADC supplies <sup>4, 4</sup>          |     |     |     |      |

|                                |                                            | $T_{a} = 125^{\circ}C^{5, 5}$                |     |     |     |      |

|                                |                                            | V <sub>DD_LV</sub> = 1.25 V                  |     |     |     |      |

|                                |                                            | VDD_HV_A = 5.5V                              |     |     |     |      |

|                                |                                            | SYS_CLK = 80MHz                              |     |     |     |      |

|                                |                                            | $T_a = 105^{\circ}C$                         | —   | —   | 142 | mA   |

|                                |                                            | T <sub>a</sub> = 85 °C                       | —   |     | 137 | mA   |

Table 10.

Current consumption characteristics

Table continues on the next page ...

| Symbol                      | Parameter                                  | Conditions <sup>1</sup>                                                          | Min | Тур  | Max | Unit |

|-----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| I <sub>DD_BODY_2</sub><br>6 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | —   | _    | 246 | mA   |

|                             |                                            | $T_a = 125^{\circ}C^5$                                                           |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 160MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105°C                                                           |     | —    | 235 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              | —   | —    | 210 | mA   |

| I <sub>DD_BODY_3</sub><br>7 | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> | _   | _    | 181 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | $T_a = 85^{\circ}C$                                                              |     | —    | 171 | mA   |

| IDD_BODY_4 <sup>8</sup>     | RUN Body Mode Profile Operating<br>current | LV supply + HV supply + HV<br>Flash supply + 2 x HV ADC<br>supplies <sup>4</sup> |     | —    | 264 | mA   |

|                             |                                            | T <sub>a</sub> = 125 °C <sup>5</sup>                                             |     |      |     |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | VDD_HV_A = 5.5V                                                                  |     |      |     |      |

|                             |                                            | SYS_CLK = 120MHz                                                                 |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | —    | 176 | mA   |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           | —   | —    | 171 | mA   |

| I <sub>DD_STOP</sub>        | STOP mode Operating current                | $T_{a} = 125 \ ^{\circ}C^{9}$                                                    | -   | -    | 49  | mA   |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 105 °C                                                          | —   | 10.6 | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 85 °C                                                           |     | 8.1  | —   |      |

|                             |                                            | $V_{DD_LV} = 1.25 V$                                                             |     |      |     |      |

|                             |                                            | T <sub>a</sub> = 25 °C                                                           |     | 4.6  | —   |      |

|                             |                                            | V <sub>DD_LV</sub> = 1.25 V                                                      |     |      |     |      |

## Table 10. Current consumption characteristics (continued)

Table continues on the next page...

## 5.3 AC specifications @ 5 V Range

### Table 16. Functional Pad AC Specifications @ 5 V Range

| Symbol                 | Prop. D | elay (ns) <sup>1</sup> | Rise/Fal | l Edge (ns) | Drive Load (pF) | SIUL2_MSCRn[SRC 1:0] |

|------------------------|---------|------------------------|----------|-------------|-----------------|----------------------|

|                        | L>H/H>L |                        | L>H/H>L  |             |                 |                      |

|                        | Min     | Max                    | Min      | Мах         | ] [             | MSB,LSB              |

| pad_sr_hv              |         | 4.5/4.5                |          | 1.3/1.2     | 25              | 11                   |

| (output)               |         | 6/6                    |          | 2.5/2       | 50              |                      |

| (output)               |         | 13/13                  |          | 9/9         | 200             |                      |

|                        |         | 5.25/5.25              |          | 3/2         | 25              | 10                   |

|                        |         | 9/8                    |          | 5/4         | 50              |                      |

|                        |         | 22/22                  |          | 18/16       | 200             |                      |

|                        |         | 27/27                  |          | 13/13       | 50              | 01 <sup>2, 2</sup>   |

|                        |         | 40/40                  |          | 24/24       | 200             |                      |

|                        |         | 40/40                  |          | 24/24       | 50              | 00 <sup>2</sup>      |

|                        |         | 65/65                  |          | 40/40       | 200             |                      |

| pad_i_hv/<br>pad_sr_hv |         | 1.5/1.5                |          | 0.5/0.5     | 0.5             | NA                   |

| (input)                |         |                        |          |             |                 |                      |

1. As measured from 50% of core side input to Voh/Vol of the output

2. Slew rate control modes

### NOTE

The above specification is based on simulation data into an ideal lumped capacitor. Customer should use IBIS models for their specific board/loading conditions to simulate the expected signal integrity and edge rates of their system.

### NOTE

The above specification is measured between 20% / 80%.

# 5.4 DC electrical specifications @ 5 V Range

### Table 17. DC electrical specifications @ 5 V Range

| Symbol         | Parameter                          | Value        |                   | Unit |

|----------------|------------------------------------|--------------|-------------------|------|

|                |                                    | Min          | Мах               |      |

| Vih (pad_i_hv) | pad_i_hv Input Buffer High Voltage | 0.7*VDD_HV_x | VDD_HV_x +<br>0.3 | V    |

Table continues on the next page...

| Type of jitter                        | Jitter due to<br>Supply<br>Noise (ps)<br>J <sub>SN</sub> <sup>1</sup> | Jitter due to<br>Fractional Mode<br>(ps) J <sub>SDM</sub> <sup>2</sup> | Jitter due to<br>Fractional Mode<br>J <sub>SSCG</sub> (ps) <sup>3</sup> | 1 Sigma<br>Random<br>Jitter J <sub>RJ</sub><br>(ps) <sup>4</sup> | Total Period Jitter (ps)  |

|---------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------|

| Long Term Jitter<br>(Integer Mode)    |                                                                       |                                                                        |                                                                         | 40                                                               | +/-(N x J <sub>RJ</sub> ) |

| Long Term jitter<br>(Fractional Mode) |                                                                       |                                                                        |                                                                         | 100                                                              | +/-(N x J <sub>RJ</sub> ) |

Table 28. Jitter calculation (continued)

1. This jitter component is due to self noise generated due to bond wire inductances on different PLL supplies. The jitter value is valid for inductor value of 5nH or less each on VDD\_LV and VSS\_LV.

2. This jitter component is added when the PLL is working in the fractional mode.

3. This jitter component is added when the PLL is working in the Spread Spectrum Mode. Else it is 0.

4. The value of N is dependent on the accuracy requirement of the application. See Table 29

### Table 29. Percentage of sample exceeding specified value of jitter

| N | Percentage of samples exceeding specified value of jitter<br>(%) |

|---|------------------------------------------------------------------|

| 1 | 31.73                                                            |

| 2 | 4.55                                                             |

| 3 | 0.27                                                             |

| 4 | 6.30 × 1e-03                                                     |

| 5 | 5.63 × 1e-05                                                     |

| 6 | 2.00 × 1e-07                                                     |

| 7 | 2.82 × 1e-10                                                     |

## 6.3 Memory interfaces

# 6.3.1 Flash memory program and erase specifications

### NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 30 shows the estimated Program/Erase times.

| Symbol               | Characteristic <sup>1</sup>        | Typ <sup>2</sup> |                               | tory<br>nming <sup>3, 4</sup>   | F                                      | Field Update              |                     |    |

|----------------------|------------------------------------|------------------|-------------------------------|---------------------------------|----------------------------------------|---------------------------|---------------------|----|

|                      |                                    |                  | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifetime Max <sup>6</sup> |                     |    |

|                      |                                    |                  | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles         | ≤ 250,000<br>cycles |    |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time  | 43               | 100                           | 150                             | 55                                     | 500                       |                     | μs |

| t <sub>ppgm</sub>    | Page (256 bits) program time       | 73               | 200                           | 300                             | 108                                    | 500                       |                     | μs |

| t <sub>qppgm</sub>   | Quad-page (1024 bits) program time | 268              | 800                           | 1,200                           | 396                                    | 2,000                     |                     | μs |

| t <sub>16kers</sub>  | 16 KB Block erase time             | 168              | 290                           | 320                             | 250                                    | 1,000                     |                     | ms |

| t <sub>16kpgm</sub>  | 16 KB Block program time           | 34               | 45                            | 50                              | 40                                     | 1,000                     |                     | ms |

| t <sub>32kers</sub>  | 32 KB Block erase time             | 217              | 360                           | 390                             | 310                                    | 1,200                     |                     | ms |

| t <sub>32kpgm</sub>  | 32 KB Block program time           | 69               | 100                           | 110                             | 90                                     | 1,200                     |                     | ms |

| t <sub>64kers</sub>  | 64 KB Block erase time             | 315              | 490                           | 590                             | 420                                    | 1,600                     |                     | ms |

| t <sub>64kpgm</sub>  | 64 KB Block program time           | 138              | 180                           | 210                             | 170                                    | 1,600                     |                     | ms |

| t <sub>256kers</sub> | 256 KB Block erase time            | 884              | 1,520                         | 2,030                           | 1,080                                  | 4,000                     | —                   | ms |

| t <sub>256kpgm</sub> | 256 KB Block program time          | 552              | 720                           | 880                             | 650                                    | 4,000                     | —                   | ms |

#### Table 30. Flash memory program and erase specifications

1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

3. Conditions:  $\leq$  150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}C \le T_J \le 150^{\circ}C$ , full spec voltage.

### 6.3.2 Flash memory Array Integrity and Margin Read specifications Table 31. Flash memory Array Integrity and Margin Read specifications

| Symbol                | Characteristic                                               | Min | Typical | Max <sup>1, 1</sup>          | Units<br>2, 2 |

|-----------------------|--------------------------------------------------------------|-----|---------|------------------------------|---------------|

| t <sub>ai16kseq</sub> | Array Integrity time for sequential sequence on 16 KB block. | -   | _       | 512 x<br>Tperiod x<br>Nread  | _             |

| t <sub>ai32kseq</sub> | Array Integrity time for sequential sequence on 32 KB block. | _   | _       | 1024 x<br>Tperiod x<br>Nread | _             |

| t <sub>ai64kseq</sub> | Array Integrity time for sequential sequence on 64 KB block. | -   | _       | 2048 x<br>Tperiod x<br>Nread | _             |

Table continues on the next page ...

# 6.4 Communication interfaces

# 6.4.1 DSPI timing

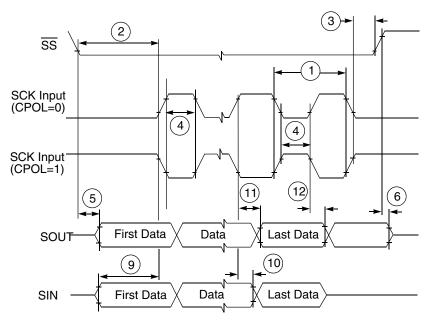

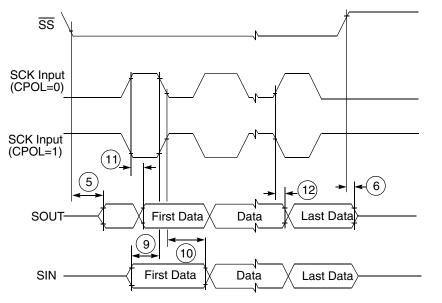

Table 35. DSPI electrical specifications

| No | Symbol            | Parameter               | Conditions                                          | High Spo                 | eed Mode                 | low Spe           | ed mode         | Unit |

|----|-------------------|-------------------------|-----------------------------------------------------|--------------------------|--------------------------|-------------------|-----------------|------|

|    |                   |                         |                                                     | Min                      | Max                      | Min               | Max             | 7    |

| 1  | t <sub>scк</sub>  | DSPI cycle              | Master (MTFE = 0)                                   | 25                       | _                        | 50                | _               | ns   |

|    |                   | time                    | Slave (MTFE = 0)                                    | 40                       | —                        | 60                | _               |      |

| 2  | tcsc              | PCS to SCK delay        |                                                     | 16                       | —                        | _                 | -               | ns   |

| 3  | t <sub>ASC</sub>  | After SCK<br>delay      | _                                                   | 16                       | —                        | —                 | -               | ns   |

| 4  | t <sub>SDC</sub>  | SCK duty<br>cycle       | _                                                   | t <sub>SCK</sub> /2 - 10 | t <sub>SCK</sub> /2 + 10 | —                 | -               | ns   |

| 5  | t <sub>A</sub>    | Slave access<br>time    | SS active to SOUT valid                             | _                        | 40                       | _                 | _               | ns   |

| 6  | t <sub>DIS</sub>  | Slave SOUT disable time | <sub>SS</sub> inactive to SOUT<br>High-Z or invalid | _                        | 10                       | —                 | _               | ns   |

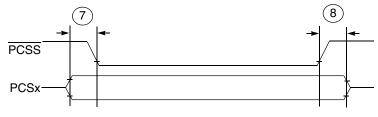

| 7  | t <sub>PCSC</sub> | PCSx to<br>PCSS time    | _                                                   | 13                       | —                        | —                 | _               | ns   |

| 8  | t <sub>PASC</sub> | PCSS to<br>PCSx time    |                                                     | 13                       | —                        | _                 | _               | ns   |

| 9  | t <sub>SUI</sub>  | Data setup              | Master (MTFE = 0)                                   | NA                       | —                        | 20                | _               | ns   |

|    |                   | time for<br>inputs      | Slave                                               | 2                        | —                        | 2                 | _               |      |

|    |                   | inputs                  | Master (MTFE = 1,<br>CPHA = 0)                      | 15                       |                          | 8 <sup>1, 1</sup> | _               |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      | 15                       | —                        | 20                | —               |      |

| 10 | t <sub>HI</sub>   | Data hold               | Master (MTFE = 0)                                   | NA                       | —                        | -5                |                 | ns   |

|    |                   | time for<br>inputs      | Slave                                               | 4                        | —                        | 4                 | _               |      |

|    |                   | inputs                  | Master (MTFE = 1,<br>CPHA = 0)                      | 0                        | —                        | 11 <sup>1</sup>   | _               |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      | 0                        | —                        | -5                | -               |      |

| 11 | t <sub>suo</sub>  | Data valid              | Master (MTFE = 0)                                   | _                        | NA                       | —                 | 4               | ns   |

|    |                   | (after SCK<br>edge)     | Slave                                               | _                        | 15                       | _                 | 23              |      |

|    |                   | euge)                   | Master (MTFE = 1,<br>CPHA = 0)                      | —                        | 4                        | —                 | 16 <sup>1</sup> |      |

|    |                   |                         | Master (MTFE = 1,<br>CPHA = 1)                      |                          | 4                        | _                 | 4               | 1    |

Table continues on the next page...

Figure 14. DSPI modified transfer format timing – slave, CPHA = 0

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

Figure 16. DSPI PCS strobe (PCSS) timing

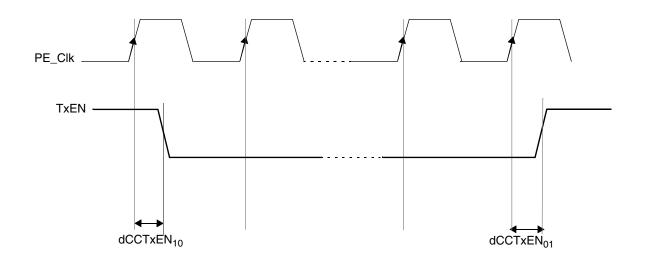

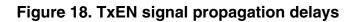

6.4.2.3 TxD

Figure 19. TxD Signal

| Table 39. | TxD output characteristics |

|-----------|----------------------------|

|-----------|----------------------------|

| Name                                                   | Description <sup>1</sup>                                   | Min   | Max            | Unit |

|--------------------------------------------------------|------------------------------------------------------------|-------|----------------|------|

| dCCT <sub>xAsym</sub>                                  | Asymmetry of sending CC @ 25 pF load (=dCCTxD50% - 100 ns) | -2.45 | 2.45           | ns   |

| dCCTxD <sub>RISE25</sub> +dCCTx<br>D <sub>FALL25</sub> | Sum of Rise and Fall time of TxD signal at the output      |       | 9 <sup>2</sup> | ns   |

Table continues on the next page...

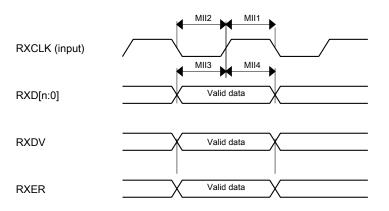

### Figure 22. RMII/MII receive signal timing diagram

## 6.4.3.2 RMII signal switching specifications

The following timing specs meet the requirements for RMII style interfaces for a range of transceiver devices.

| Num   | Description                                 | Min. | Max. | Unit               |

|-------|---------------------------------------------|------|------|--------------------|

| —     | EXTAL frequency (RMII input clock RMII_CLK) | _    | 50   | MHz                |

| RMII1 | RMII_CLK pulse width high                   | 35%  | 65%  | RMII_CLK<br>period |

| RMII2 | RMII_CLK pulse width low                    | 35%  | 65%  | RMII_CLK<br>period |

| RMII3 | RXD[1:0], CRS_DV, RXER to RMII_CLK setup    | 4    | _    | ns                 |

| RMII4 | RMII_CLK to RXD[1:0], CRS_DV, RXER hold     | 2    | _    | ns                 |

| RMII7 | RMII_CLK to TXD[1:0], TXEN invalid          | 4    | —    | ns                 |

| RMII8 | RMII_CLK to TXD[1:0], TXEN valid            | _    | 15   | ns                 |

Table 42. RMII signal switching specifications

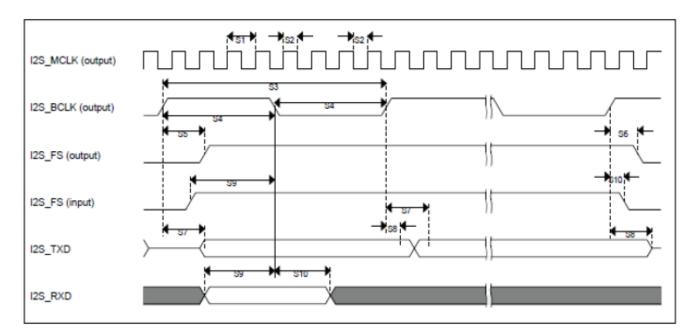

# 6.4.4 SAI electrical specifications

All timing requirements are specified relative to the clock period or to the minimum allowed clock period of a device

| no | Parameter           | Va  | Unit |    |

|----|---------------------|-----|------|----|

|    |                     | Min | Мах  |    |

|    | Operating Voltage   | 2.7 | 3.6  | V  |

| S1 | SAI_MCLK cycle time | 40  | -    | ns |

Table 43. Master mode SAI Timing

Table continues on the next page...

#### FlexRay electrical specifications

| no  | Parameter                                  | Va  | Unit |                |

|-----|--------------------------------------------|-----|------|----------------|

|     |                                            | Min | Max  |                |

| S2  | SAI_MCLK pulse width high/low              | 45% | 55%  | MCLK<br>period |

| S3  | SAI_BCLK cycle time                        | 80  | -    | BCLK<br>period |

| S4  | SAI_BCLK pulse width high/low              | 45% | 55%  | ns             |

| S5  | SAI_BCLK to SAI_FS output valid            | -   | 15   | ns             |

| S6  | SAI_BCLK to SAI_FS output invalid          | 0   | -    | ns             |

| S7  | SAI_BCLK to SAI_TXD valid                  | -   | 15   | ns             |

| S8  | SAI_BCLK to SAI_TXD invalid                | 0   | -    | ns             |

| S9  | SAI_RXD/SAI_FS input setup before SAI_BCLK | 28  | -    | ns             |

| S10 | SAI_RXD/SAI_FS input hold after SAI_BCLK   | 0   | -    | ns             |

Table 43. Master mode SAI Timing (continued)

| Table 44. | Slave | mode | SAI | Timing |

|-----------|-------|------|-----|--------|

|-----------|-------|------|-----|--------|

| No  | Parameter                             | Value |     | Unit        |

|-----|---------------------------------------|-------|-----|-------------|

|     |                                       | Min   | Мах |             |

|     | Operating Voltage                     | 2.7   | 3.6 | V           |

| S11 | SAI_BCLK cycle time (input)           | 80    | -   | ns          |

| S12 | SAI_BCLK pulse width high/low (input) | 45%   | 55% | BCLK period |

| S13 | SAI_FS input setup before SAI_BCLK    | 10    | -   | ns          |

| S14 | SAI_FS input hold after SAI_BCLK      | 2     | -   | ns          |

Table continues on the next page...

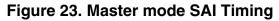

### Debug specifications

Figure 26. JTAG test access port timing

#### Thermal attributes

| Board type        | Symbol            | Description                                                                | 176LQFP | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------|---------|------|-------|

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 17.8    | °C/W | 1, 3  |

| _                 | R <sub>θJB</sub>  | Thermal<br>resistance, junction<br>to board                                | 10.9    | °C/W | 44    |

| _                 | R <sub>θJC</sub>  | Thermal<br>resistance, junction<br>to case                                 | 8.4     | °C/W | 55    |

| _                 | Ψ <sub>JT</sub>   | Thermal<br>resistance, junction<br>to package top                          | 0.5     | °C/W | 66    |

| _                 | Ψ <sub>JB</sub>   | Thermal<br>characterization<br>parameter, junction<br>to package bottom    | 0.3     | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 324 MAPBGA | Unit | Notes  |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|--------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 31.0       | °C/W | 11, 22 |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 24.3       | °C/W | 1,2,33 |

| Single-layer (1s) | R <sub>eJMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 23.5       | °C/W | 1, 3   |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 20.1       | °C/W | 1,3    |

Table continues on the next page...

**Pinouts**

| Package         | NXP Document Number |  |  |

|-----------------|---------------------|--|--|

| 176-pin LQFP-EP | 98ASA00698D         |  |  |

| 256 MAPBGA      | 98ASA00346D         |  |  |

| 324 MAPBGA      | 98ASA10582D         |  |  |

# 9 Pinouts

# 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

# 10 Reset sequence

# 10.1 Reset sequence

This section describes different reset sequences and details the duration for which the device remains in reset condition in each of those conditions.

# 10.1.1 Reset sequence duration

Table 49 specifies the reset sequence duration for the five different reset sequences described in Reset sequence description.

| No. | Symbol                                                      | Parameter T <sub>Reset</sub>                   |     |             | Unit |    |

|-----|-------------------------------------------------------------|------------------------------------------------|-----|-------------|------|----|

|     |                                                             |                                                | Min | Тур<br>1, 1 | Max  |    |

| 1   | 1 T <sub>DRB</sub> Destructive Reset Sequence, BIST enabled |                                                | 6.2 | 7.3         | -    | ms |

| 2   | T <sub>DR</sub>                                             | Destructive Reset Sequence, BIST disabled      |     | 182         | -    | us |

| 3   | T <sub>ERLB</sub>                                           | LB External Reset Sequence Long, Unsecure Boot |     | 7.3         | -    | ms |

| 4   | T <sub>FRL</sub>                                            | Functional Reset Sequence Long, Unsecure Boot  |     | 182         | -    | us |

| 5   | T <sub>FRS</sub>                                            | Functional Reset Sequence Short, Unsecure Boot |     | 9           | -    | us |

Table 49. RESET sequences

1. The Typ value is applicable only if the reset sequence duration is not prolonged by an extended assertion of RESET\_B by an external reset generator.

| Rev. No. | Date         | Substantial Changes                                                                                                                                                         |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 3    | 2 March 2016 | In section, Recommended operating conditions                                                                                                                                |

|          |              | Added a new Note                                                                                                                                                            |

|          |              | In section, Voltage regulator electrical characteristics                                                                                                                    |

|          |              | <ul> <li>In table, Voltage regulator electrical specifications:</li> </ul>                                                                                                  |

|          |              | <ul> <li>Added a new row for C<sub>HV_VDD_B</sub></li> <li>Added a fastrate an V</li> </ul>                                                                                 |

|          |              | <ul> <li>Added a footnote on V<sub>DD_HV_BALLAST</sub></li> <li>Added a new Note at the end of this section</li> </ul>                                                      |

|          |              |                                                                                                                                                                             |

|          |              | In section, Voltage monitor electrical characteristics                                                                                                                      |

|          |              | <ul> <li>In table, Voltage monitor electrical characteristics:</li> <li>Removed "V<sub>LVD FLASH</sub>" and "V<sub>LVD FLASH</sub> during low power mode using</li> </ul>   |

|          |              | LPBG as reference" rows                                                                                                                                                     |

|          |              | <ul> <li>Updated Fall and Rise trimmed Minimum values for V<sub>HVD_LV_cold</sub></li> </ul>                                                                                |

|          |              | In section, Supply current characteristics                                                                                                                                  |

|          |              | In table, Current consumption characteristics:                                                                                                                              |

|          |              | <ul> <li>Updated the footnote mentioned in the Condition column of I<sub>DD_STOP</sub> row</li> </ul>                                                                       |

|          |              | Updated all TBD values     In table Law Power Unit (LBL) Current consumption above staristics:                                                                              |

|          |              | <ul> <li>In table, Low Power Unit (LPU) Current consumption characteristics:</li> <li>Updated the typical value of LPU_STOP to 0.18 mA</li> </ul>                           |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | <ul> <li>In table, STANDBY Current consumption characteristics:</li> </ul>                                                                                                  |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | In section, AC specifications @ 3.3 V Range                                                                                                                                 |

|          |              | In table, Functional Pad AC Specifications @ 3.3 V Range:                                                                                                                   |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | In section, DC electrical specifications @ 3.3V Range                                                                                                                       |

|          |              | In table, DC electrical specifications @ 3.3V Range:                                                                                                                        |

|          |              | <ul> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                                                                                             |

|          |              | In section, AC specifications @ 5 V Range                                                                                                                                   |

|          |              | In table, Functional Pad AC Specifications @ 5 V Range:                                                                                                                     |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | <ul> <li>In section, DC electrical specifications @ 5 V Range</li> </ul>                                                                                                    |

|          |              | In table, DC electrical specifications @ 5 V Range:                                                                                                                         |

|          |              | <ul> <li>Updated Min and Max values for Pull_Ioh and Pull_Iol rows</li> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                          |

|          |              |                                                                                                                                                                             |

|          |              | In section, Reset pad electrical characteristics                                                                                                                            |

|          |              | <ul> <li>In table, Functional reset pad electrical specifications:</li> <li>Updated parameter column for V<sub>IH</sub>, V<sub>IL</sub> and V<sub>HYS</sub> rows</li> </ul> |

|          |              | • Updated Min and Max values for $V_{IH}$ and $V_{IL}$ rows                                                                                                                 |

|          |              |                                                                                                                                                                             |

|          |              | <ul> <li>In section, PORST electrical specifications</li> <li>In table, PORST electrical specifications:</li> </ul>                                                         |

|          |              | <ul> <li>Updated Unit and Min/Max values for V<sub>IH</sub> and V<sub>IL</sub> rows</li> </ul>                                                                              |

|          |              | . In contrast, land a subscience discuit and ADO companying share staristics                                                                                                |

|          |              | <ul> <li>In section, Input equivalent circuit and ADC conversion characteristics</li> <li>In table, ADC conversion characteristics (for 12-bit):</li> </ul>                 |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | <ul> <li>In table, ADC conversion characteristics (for 10-bit):</li> </ul>                                                                                                  |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | In section, Analog Comparator (CMP) electrical specifications                                                                                                               |

|          |              | In table, Comparator and 6-bit DAC electrical specifications:                                                                                                               |

|          | MPC57        | • Updated Min and Max values for Valo to ±47 mV<br>46C Microcontroller Datasneet Data Sheet, Rev. 5.1, 05/2017.                                                             |

| 74       |              | NXP Semiconductors                                                                                                                                                          |

|          |              | In section, Main oscillator electrical characteristics                                                                                                                      |

| Table 51. | Revision | History ( | (continued) |

|-----------|----------|-----------|-------------|

|-----------|----------|-----------|-------------|

| Rev. No.                  | Date         | Substantial Changes                                                                                                                                                                                                                                                                                                                           |

|---------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 4                     | 9 March 2016 | <ul> <li>In section, Voltage regulator electrical characteristics</li> <li>In table, Voltage regulator electrical specifications:</li> <li>Updated the footnote on V<sub>DD_HV_BALLAST</sub></li> </ul>                                                                                                                                       |

| Rev 5 27 February<br>2017 |              | <ul> <li>In Family Comparison section:</li> <li>Updated the "MPC5746C Family Comparison" table.</li> <li>added "NVM Memory Map 1", "NVM Memory Map 2", and "RAM Memory Map" tables.</li> </ul>                                                                                                                                                |

|                           |              | <ul> <li>Updated the product version, flash memory size and optional fields information in<br/>Ordering Information section.</li> </ul>                                                                                                                                                                                                       |

|                           |              | <ul> <li>In Recommended Operating Conditions section, removed the note related to additional<br/>crossover current.</li> </ul>                                                                                                                                                                                                                |

|                           |              | <ul> <li>VDD_HV_C row added in "Voltage regulator electrical specifications" table in Voltage<br/>regulator electrical characteristics section.</li> </ul>                                                                                                                                                                                    |

|                           |              | <ul> <li>In Voltage Monitor Electrical Characteristics section, updated the "Trimmed" Fall and<br/>Rise specs of VHVD_LV_cold parameter in "Voltage Monitor Electrical Characteristics"<br/>table.</li> </ul>                                                                                                                                 |

|                           |              | <ul> <li>In AC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> </ul>                                                                                                                                                                               |

|                           |              | <ul> <li>In DC Electrical Specifications: 3.3 V Range section, changed the occurrences of<br/>"ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in<br/>the table.</li> </ul>                                                                                                                                      |

|                           |              | <ul> <li>In AC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" in the table.</li> <li>In DC Electrical Specifications: 5 V Range section, changed the occurrences of "ipp_sre[1:0]" to "SIUL2_MSCRn.SRC[1:0]" and updated "Vol min and max" values in the table.</li> </ul> |

|                           |              | <ul> <li>In "Flash memory AC timing specifications" table in Flash memory AC timing specifications section:</li> <li>Updated the "t<sub>psus</sub>" typ value from 7 us to 9.4 us.</li> <li>Updated the "t<sub>psus</sub>" max value from 9.1 us to 11.5 us.</li> </ul>                                                                       |

|                           |              | <ul> <li>Added "Continuous SCK Timing" table in DSPI timing section.</li> </ul>                                                                                                                                                                                                                                                               |