# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4                                                           |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 80MHz/160MHz                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SAI, SPI, USB, USB OTG       |

| Peripherals                | DMA, LVD, POR, WDT                                                       |

| Number of I/O              | 129                                                                      |

| Program Memory Size        | 3MB (3M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 80x10b, 64x12b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5746csk1mku6r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Debug functionality

- e200z2 core:NDI per IEEE-ISTO 5001-2008 Class3+

- e200z4 core: NDI per IEEE-ISTO 5001-2008 Class 3+

- Timer

- 16 Periodic Interrupt Timers (PITs)

- Two System Timer Modules (STM)

- Three Software Watchdog Timers (SWT)

- 64 Configurable Enhanced Modular Input Output Subsystem (eMIOS) channels

- Device/board boundary Scan testing supported with Joint Test Action Group (JTAG) of IEEE 1149.1 and IEEE 1149.7 (CJTAG)

- Security

- Hardware Security Module (HSMv2)

- Password and Device Security (PASS) supporting advanced censorship and life-cycle management

- One Fault Collection and Control Unit (FCCU) to collect faults and issue interrupts

- Functional Safety

- ISO26262 ASIL-B compliance

- Multiple operating modes

- Includes enhanced low power operation

### NOTE

All optional features (Flash memory, RAM, Peripherals) start with lowest number or address (e.g., FlexCAN0) and end at highest available number or address (e.g., MPC574xB/C have 6 CAN, ending with FlexCAN5).

| Feature                                        | MPC5745B        | MPC5744B                              | MPC5746B                                      | MPC5744C                                                     | MPC5745C                  | MPC5746C                                   |  |

|------------------------------------------------|-----------------|---------------------------------------|-----------------------------------------------|--------------------------------------------------------------|---------------------------|--------------------------------------------|--|

| CPUs                                           | e200z4          | e200z4                                | e200z4                                        | e200z4                                                       | e200z4                    | e200z4                                     |  |

|                                                |                 |                                       |                                               | e200z2                                                       | e200z2                    | e200z2                                     |  |

| FPU                                            | e200z4          | e200z4                                | e200z4                                        | e200z4                                                       | e200z4                    | e200z4                                     |  |

| Maximum<br>Operating<br>Frequency <sup>2</sup> | 160MHz (Z4)     | 160MHz (Z4)                           | 160MHz (Z4)                                   | 160MHz (Z4)<br>80MHz (Z2)                                    | 160MHz (Z4)<br>80MHz (Z2) | 160MHz (Z4<br>80MHz (Z2)                   |  |

| Flash memory                                   | 2 MB            | 1.5 MB                                | 3 MB                                          | 1.5 MB                                                       | 2 MB                      | 3 MB                                       |  |

| EEPROM<br>support                              | E               | Emulated up to 64                     | K                                             | E                                                            | Emulated up to 64         | <                                          |  |

| RAM                                            | 256 KB          | 192 KB                                | 384 KB<br>(Optional<br>512KB) <sup>3, 3</sup> | 192 KB                                                       | 256 KB                    | 384 KB<br>(Optional<br>512KB) <sup>3</sup> |  |

| ECC                                            |                 |                                       | End t                                         | o End                                                        |                           |                                            |  |

| SMPU                                           |                 |                                       | 16 e                                          | entry                                                        |                           |                                            |  |

| DMA                                            |                 |                                       | 32 ch                                         | annels                                                       |                           |                                            |  |

| 10-bit ADC                                     |                 |                                       | 36 Standar                                    | d channels                                                   |                           |                                            |  |

|                                                |                 |                                       | 32 Externa                                    | al channels                                                  |                           |                                            |  |

| 12-bit ADC                                     |                 |                                       | 15 Precisio                                   | n channels                                                   |                           |                                            |  |

|                                                |                 | 16 Standar                            |                                               |                                                              |                           |                                            |  |

| Analog<br>Comparator                           |                 |                                       | :                                             | 3                                                            |                           |                                            |  |

| BCTU                                           |                 |                                       | -                                             | 1                                                            |                           |                                            |  |

| SWT                                            |                 | 1, SWT[0] <sup>4</sup>                |                                               |                                                              | 2 <sup>4</sup>            |                                            |  |

| STM                                            |                 | 1, STM[0]                             |                                               |                                                              | 2                         |                                            |  |

| PIT-RTI                                        |                 |                                       | 16 chan                                       | nels PIT                                                     |                           |                                            |  |

|                                                |                 |                                       | 1 chanr                                       | nels RTI                                                     |                           |                                            |  |

| RTC/API                                        |                 |                                       |                                               | 1                                                            |                           |                                            |  |

| Total Timer I/O <sup>5</sup>                   |                 |                                       | 64 ch                                         | annels                                                       |                           |                                            |  |

|                                                |                 |                                       | 16-                                           | bits                                                         |                           |                                            |  |

| LINFlexD                                       |                 | 1                                     |                                               |                                                              | 1                         |                                            |  |

|                                                | Master and      | Slave (LINFlexD[0<br>(LINFlexD[1:11]) | )], 11 Master                                 | Master and Slave (LINFlexD[0], 15 Master<br>(LINFlexD[1:15]) |                           |                                            |  |

| FlexCAN                                        | 6 with optional | CAN FD support                        | (FlexCAN[0:5])                                | 8 with optional                                              | CAN FD support            | (FlexCAN[0:7])                             |  |

| DSPI/SPI                                       |                 |                                       | 4 x [                                         | DSPI                                                         |                           |                                            |  |

|                                                |                 |                                       | 4 x                                           | SPI                                                          |                           |                                            |  |

Table 1. MPC5746C Family Comparison1

Table continues on the next page...

| Start Address | End Address | Flash block                  | RWW partition | MPC5744       | MPC5745       | MPC5746       |

|---------------|-------------|------------------------------|---------------|---------------|---------------|---------------|

| 0x01000000    | 0x0103FFFF  | 256 KB code<br>Flash block 0 | 6             | available     | available     | available     |

| 0x01040000    | 0x0107FFFF  | 256 KB code<br>Flash block 1 | 6             | available     | available     | available     |

| 0x01080000    | 0x010BFFFF  | 256 KB code<br>Flash block 2 | 6             | available     | available     | available     |

| 0x010C0000    | 0x010FFFFF  | 256 KB code<br>Flash block3  | 6             | available     | available     | available     |

| 0x01100000    | 0x0113FFFF  | 256 KB code<br>Flash block 4 | 6             | not available | available     | available     |

| 0x01140000    | 0x0117FFFF  | 256 KB code<br>Flash block 5 | 7             | not available | available     | available     |

| 0x01180000    | 0x011BFFFF  | 256 KB code<br>Flash block 6 | 7             | not available | not available | available     |

| 0x011C0000    | 0x011FFFFF  | 256 KB code<br>Flash block 7 | 7             | not available | not available | available     |

| 0x01200000    | 0x0123FFFF  | 256 KB code<br>Flash block 8 | 7             | not available | not available | available     |

| 0x01240000    | 0x0127FFFF  | 256 KB code<br>Flash block 9 | 7             | not available | not available | not available |

Table 2. MPC5746C Family Comparison - NVM Memory Map 1

### Table 3. MPC5746C Family Comparison - NVM Memory Map 2

| Start Address | End Address | Flash block      | <b>RWW</b> partition | MPC5744B      | MPC5744C  |

|---------------|-------------|------------------|----------------------|---------------|-----------|

|               |             |                  |                      | MPC5745B      | MPC5745C  |

|               |             |                  |                      | MPC5746B      | MPC5746C  |

| 0x00F90000    | 0x00F93FFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F94000    | 0x00F97FFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F98000    | 0x00F9BFFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00F9C000    | 0x00F9FFFF  | 16 KB data Flash | 2                    | available     | available |

| 0x00FA0000    | 0x00FA3FFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FA4000    | 0x00FA7FFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FA8000    | 0x00FABFFF  | 16 KB data Flash | 3                    | not available | available |

| 0x00FAC000    | 0x00FAFFFF  | 16 KB data Flash | 3                    | not available | available |

### Table 4. MPC5746C Family Comparison - RAM Memory Map

| Start Address | End Address | Allocated size | Description | MPC5744   | MPC5745   | MPC5746   |

|---------------|-------------|----------------|-------------|-----------|-----------|-----------|

| 0x4000000     | 0x40001FFF  | 8 KB           | SRAM0       | available | available | available |

| 0x40002000    | 0x4000FFFF  | 56 KB          | SRAM1       | available | available | available |

| 0x40010000    | 0x4001FFFF  | 64 KB          | SRAM2       | available | available | available |

| 0x40020000    | 0x4002FFFF  | 64 KB          | SRAM3       | available | available | available |

Table continues on the next page...

# 4.2 Recommended operating conditions

The following table describes the operating conditions for the device, and for which all specifications in the data sheet are valid, except where explicitly noted. The device operating conditions must not be exceeded in order to guarantee proper operation and reliability. The ranges in this table are design targets and actual data may vary in the given range.

### NOTE

- For normal device operations, all supplies must be within operating range corresponding to the range mentioned in following tables. This is required even if some of the features are not used.

- If VDD\_HV\_A is in 3.3V range, VDD\_HV\_FLA should be externally supplied using a 3.3V source. If VDD\_HV\_A is in 3.3V range, VDD\_HV\_FLA should be shorted to VDD\_HV\_A.

- VDD\_HV\_A, VDD\_HV\_B and VDD\_HV\_C are all independent supplies and can each be set to 3.3V or 5V. The following tables: 'Recommended operating conditions (VDD\_HV\_x = 3.3 V)' and table 'Recommended operating conditions (VDD\_HV\_x = 5 V)' specify their ranges when configured in 3.3V or 5V respectively.

| Symbol                                             | Parameter                                                   | Conditions <sup>1</sup> | Min <sup>2</sup>                                   | Max  | Unit |

|----------------------------------------------------|-------------------------------------------------------------|-------------------------|----------------------------------------------------|------|------|

| V <sub>DD_HV_A</sub>                               | HV IO supply voltage                                        | —                       | 3.15                                               | 3.6  | V    |

| $V_{DD_HV_B}$                                      |                                                             |                         |                                                    |      |      |

| $V_{DD_HV_C}$                                      |                                                             |                         |                                                    |      |      |

| V <sub>DD_HV_FLA</sub> <sup>3</sup>                | HV flash supply voltage                                     | _                       | 3.15                                               | 3.6  | V    |

| V <sub>DD_HV_ADC1_REF</sub>                        | HV ADC1 high reference voltage                              |                         | 3.0                                                | 5.5  | V    |

| V <sub>DD_HV_ADC0</sub><br>V <sub>DD_HV_ADC1</sub> | HV ADC supply voltage                                       | _                       | max(VDD_H<br>V_A,VDD_H<br>V_B,VDD_H<br>V_C) - 0.05 | 3.6  | V    |

| V <sub>SS_HV_ADC0</sub><br>V <sub>SS_HV_ADC1</sub> | HV ADC supply ground                                        | _                       | -0.1                                               | 0.1  | V    |

| V <sub>DD_LV</sub> <sup>4, 5</sup>                 | Core supply voltage                                         | _                       | 1.2                                                | 1.32 | V    |

| V <sub>IN1_CMP_REF</sub> <sup>6, 7</sup>           | Analog Comparator DAC reference voltage                     | —                       | 3.15                                               | 3.6  | V    |

| I <sub>INJPAD</sub>                                | Injected input current on any pin during overload condition | _                       | -3.0                                               | 3.0  | mA   |

### Table 6. Recommended operating conditions ( $V_{DD_HV_x} = 3.3 V$ )

Table continues on the next page ...

#### Peripheral operating requirements and behaviours

| Symbol              | Parameter                                      | Conditions                                                                                       |      | Value |     |    |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-------|-----|----|

|                     |                                                |                                                                                                  | Min  | Тур   | Max |    |

| V <sub>HYS</sub>    | CMOS Input Buffer hysterisis                   | —                                                                                                | 300  | —     | _   | mV |

| V <sub>DD_POR</sub> | Minimum supply for strong pull-down activation | -                                                                                                | —    | _     | 1.2 | V  |

| I <sub>OL_R</sub>   | Strong pull-down current <sup>1, 1</sup>       | $\label{eq:Device under power-on reset} $V_{DD_HV_A} = V_{DD_POR}$$V_{OL} = 0.35^*V_{DD_HV_A}$$$ | 0.2  | _     |     | mA |

|                     |                                                | Device under power-on reset<br>$V_{DD_{HV}A} = V_{DD_{POR}}$<br>$V_{OL} = 0.35^*V_{DD_{HV}IO}$   | 11   | _     |     | mA |

| W <sub>FRST</sub>   | RESET input filtered pulse                     | —                                                                                                | _    | _     | 500 | ns |

| W <sub>NFRST</sub>  | RESET input not filtered pulse                 | -                                                                                                | 2000 | —     | _   | ns |

| ll <sub>WPU</sub> l | Weak pull-up current absolute value            | RESET pin V <sub>IN</sub> = V <sub>DD</sub>                                                      | 23   | —     | 82  | μA |

Table 18.

Functional reset pad electrical specifications (continued)

1. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for RESET.

# 5.6 PORST electrical specifications

### Table 19. PORST electrical specifications

| Symbol              | Parameter                      |                                | Value |                                |    |

|---------------------|--------------------------------|--------------------------------|-------|--------------------------------|----|

|                     |                                | Min                            | Тур   | Max                            |    |

| W <sub>FPORST</sub> | PORST input filtered pulse     |                                | —     | 200                            | ns |

| WNFPORST            | PORST input not filtered pulse | 1000                           | —     | _                              | ns |

| V <sub>IH</sub>     | Input high level               | 0.65 x<br>V <sub>DD_HV_A</sub> | _     | _                              | V  |

| V <sub>IL</sub>     | Input low level                | -                              | _     | 0.35 x<br>V <sub>DD_HV_A</sub> | V  |

# 6 Peripheral operating requirements and behaviours

# 6.1 Analog

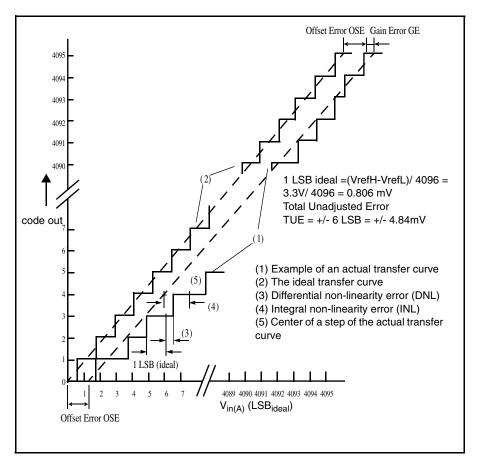

### 6.1.1 ADC electrical specifications

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Figure 5. ADC characteristics and error definitions

| Symbol                           | Parameter                                                        | Conditions                          | Min | Typ <sup>1</sup> | Max  | Unit |

|----------------------------------|------------------------------------------------------------------|-------------------------------------|-----|------------------|------|------|

| t <sub>conv</sub>                | Conversion time <sup>4</sup>                                     | 80 MHz                              | 550 |                  | —    | ns   |

| t <sub>total_conv</sub>          | Total Conversion time tsample + tconv (for standard channels)    | 80 MHz                              | 1   | _                |      | μs   |

|                                  | Total Conversion time tsample +<br>tconv (for extended channels) |                                     | 1.5 | _                | _    |      |

| C <sub>S</sub> <sup>5</sup>      | ADC input sampling capacitance                                   | —                                   | —   | 3                | 5    | pF   |

| C <sub>P1</sub> <sup>5</sup>     | ADC input pin capacitance 1                                      | —                                   | _   | _                | 5    | pF   |

| C <sub>P2</sub> <sup>5</sup>     | ADC input pin capacitance 2                                      | —                                   | _   | _                | 0.8  | pF   |

| R <sub>SW1</sub> <sup>5</sup>    | Internal resistance of analog                                    | $V_{REF}$ range = 4.5 to 5.5 V      | _   | _                | 0.3  | kΩ   |

|                                  | source                                                           | $V_{REF}$ range = 3.15 to 3.6 V     | _   | _                | 875  | Ω    |

| R <sub>AD</sub> <sup>5</sup>     | Internal resistance of analog source                             | —                                   | _   | _                | 825  | Ω    |

| INL                              | Integral non-linearity                                           | —                                   | -2  | _                | 2    | LSB  |

| DNL                              | Differential non-linearity                                       | —                                   | -1  |                  | 1    | LSB  |

| OFS                              | Offset error                                                     | —                                   | -4  |                  | 4    | LSB  |

| GNE                              | Gain error                                                       | —                                   | -4  | —                | 4    | LSB  |

| ADC Analog Pad                   | Max leakage (standard channel)                                   | 150 °C                              | _   | _                | 2500 | nA   |

| (pad going to one<br>ADC)        | Max positive/negative injection                                  |                                     | -5  | _                | 5    | mA   |

| AD0)                             | Max leakage (standard channel)                                   | 105 °C <sub>TA</sub>                | _   | 5                | 250  | nA   |

| TUE <sub>standard/extended</sub> | Total unadjusted error for standard                              | Without current injection           | -4  | +/-3             | 4    | LSB  |

| channels                         | channels                                                         | With current injection <sup>6</sup> |     | +/-4             |      | LSB  |

| t <sub>recovery</sub>            | STOP mode to Run mode recovery time                              |                                     |     |                  | < 1  | μs   |

Table 21. ADC conversion characteristics (for 10-bit) (continued)

- Active ADC Input, VinA < [min(ADC\_ADV, IO\_Supply\_A,B,C)]. Violation of this condition would lead to degradation of ADC performance. Please refer to Table: 'Absolute maximum ratings' to avoid damage. Refer to Table: 'Recommended operating conditions' for required relation between IO\_supply\_A, B, C and ADC\_Supply.</li>

- 2. The internally generated clock (known as AD\_clk or ADCK) could be same as the peripheral clock or half of the peripheral clock based on register configuration in the ADC.

- During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal

resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the

sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample

clock t<sub>sample</sub> depend on programming.

- This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 5. See Figure 65

- 6. Current injection condition for ADC channels is defined for an inactive ADC channel (on which conversion is NOT being performed), and this occurs when voltage on the ADC pin exceeds the I/O supply or ground. However, absolute maximum voltage spec on pad input (VINA, see Table: Absolute maximum ratings) must be honored to meet TUE spec quoted here

#### Memory interfaces

| Symbol                 | Characteristic                                                | Min    | Typical | Max <sup>1, 1</sup>          | Units<br>2, 2 |

|------------------------|---------------------------------------------------------------|--------|---------|------------------------------|---------------|

| tai256kseq             | Array Integrity time for sequential sequence on 256 KB block. | -      | _       | 8192 x<br>Tperiod x<br>Nread | _             |

| t <sub>mr16kseq</sub>  | Margin Read time for sequential sequence on 16 KB block.      | 73.81  | _       | 110.7                        | μs            |

| t <sub>mr32kseq</sub>  | Margin Read time for sequential sequence on 32 KB block.      | 128.43 | _       | 192.6                        | μs            |

| t <sub>mr64kseq</sub>  | Margin Read time for sequential sequence on 64 KB block.      | 237.65 | —       | 356.5                        | μs            |

| t <sub>mr256kseq</sub> | Margin Read time for sequential sequence on 256 KB block.     | 893.01 |         | 1,339.5                      | μs            |

#### Table 31. Flash memory Array Integrity and Margin Read specifications (continued)

- Array Integrity times need to be calculated and is dependent on system frequency and number of clocks per read. The

equation presented require Tperiod (which is the unit accurate period, thus for 200 MHz, Tperiod would equal 5e-9) and

Nread (which is the number of clocks required for read, including pipeline contribution. Thus for a read setup that requires

6 clocks to read with no pipeline, Nread would equal 6. For a read setup that requires 6 clocks to read, and has the

address pipeline set to 2, Nread would equal 4 (or 6 2).)

- 2. The units for Array Integrity are determined by the period of the system clock. If unit accurate period is used in the equation, the results of the equation are also unit accurate.

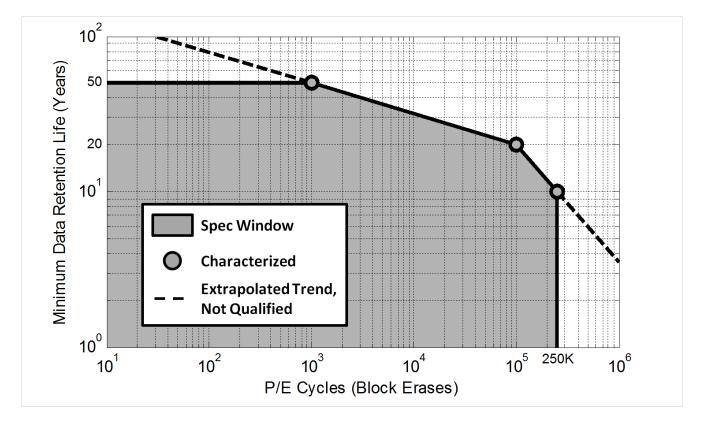

### 6.3.3 Flash memory module life specifications Table 32. Flash memory module life specifications

| Symbol              | Characteristic                                                                                 | Conditions                        | Min     | Typical | Units         |

|---------------------|------------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|---------------|

| Array P/E<br>cycles | Number of program/erase cycles per block<br>for 16 KB, 32 KB and 64 KB blocks. <sup>1, 1</sup> | —                                 | 250,000 | _       | P/E<br>cycles |

|                     | Number of program/erase cycles per block for 256 KB blocks. <sup>2, 2</sup>                    | —                                 | 1,000   | 250,000 | P/E<br>cycles |

| Data<br>retention   | Minimum data retention.                                                                        | Blocks with 0 - 1,000 P/E cycles. | 50      | -       | Years         |

|                     |                                                                                                | Blocks with 100,000 P/E cycles.   | 20      | -       | Years         |

|                     |                                                                                                | Blocks with 250,000 P/E cycles.   | 10      | -       | Years         |

1. Program and erase supported across standard temperature specs.

2. Program and erase supported across standard temperature specs.

### 6.3.4 Data retention vs program/erase cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits.

### 6.3.5 Flash memory AC timing specifications Table 33. Flash memory AC timing specifications

| Symbol             | Characteristic                                                                                                | Min | Typical                                        | Max                                             | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub>  | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.                                          | _   | 9.4<br>plus four<br>system<br>clock<br>periods | 11.5<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>esus</sub>  | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.                                          | _   | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

| t <sub>res</sub>   | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1 until DONE goes low.                                 |     | _                                              | 100                                             | ns    |

| t <sub>done</sub>  | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared.  | —   | _                                              | 5                                               | ns    |

| t <sub>dones</sub> | Time from 1 to 0 transition on the MCR-EHV bit aborting a program/erase until the MCR-DONE bit is set to a 1. |     | 16<br>plus four<br>system<br>clock<br>periods  | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |

Table continues on the next page...

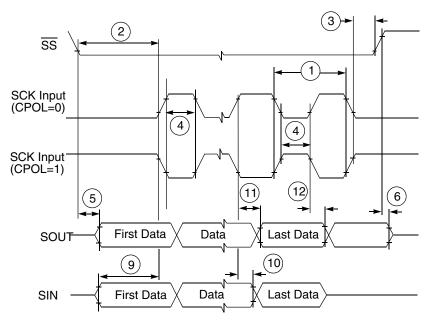

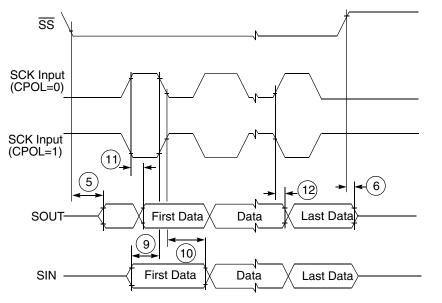

Figure 14. DSPI modified transfer format timing – slave, CPHA = 0

Figure 15. DSPI modified transfer format timing — slave, CPHA = 1

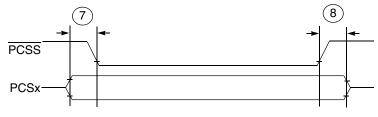

Figure 16. DSPI PCS strobe (PCSS) timing

# 6.4.2 FlexRay electrical specifications

### 6.4.2.1 FlexRay timing

This section provides the FlexRay Interface timing characteristics for the input and output signals. It should be noted that these are recommended numbers as per the FlexRay EPL v3.0 specification, and subject to change per the final timing analysis of the device.

### 6.4.2.2 TxEN

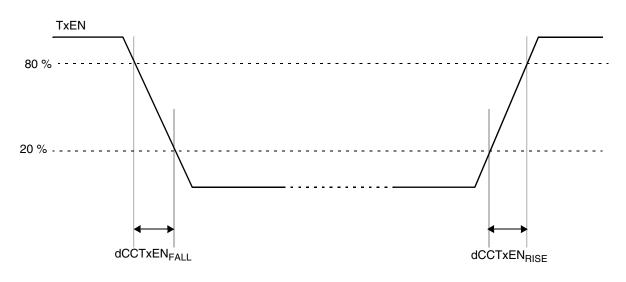

### Figure 17. TxEN signal

| Table 38. | TxEN output | characteristics <sup>1</sup> |

|-----------|-------------|------------------------------|

|-----------|-------------|------------------------------|

| Name                      | Description                                                                            | Min | Max | Unit |

|---------------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| dCCTxEN <sub>RISE25</sub> | Rise time of TxEN signal at CC                                                         | —   | 9   | ns   |

| dCCTxEN <sub>FALL25</sub> | Fall time of TxEN signal at CC                                                         | —   | 9   | ns   |

| dCCTxEN <sub>01</sub>     | Sum of delay between Clk to Q of the last FF and the final output buffer, rising edge  | _   | 25  | ns   |

| dCCTxEN <sub>10</sub>     | Sum of delay between Clk to Q of the last FF and the final output buffer, falling edge |     | 25  | ns   |

1. All parameters specified for  $V_{DD_HV_IOx}$  = 3.3 V -5%, +±10%, TJ = -40 °C / 150 °C, TxEN pin load maximum 25 pF

| No  | Parameter                                 | Value |     | Unit |

|-----|-------------------------------------------|-------|-----|------|

|     |                                           | Min   | Мах |      |

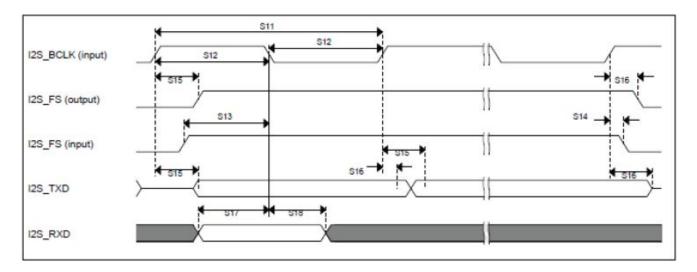

| S15 | SAI_BCLK to SAI_TXD/SAI_FS output valid   | -     | 28  | ns   |

| S16 | SAI_BCLK to SAI_TXD/SAI_FS output invalid | 0     | -   | ns   |

| S17 | SAI_RXD setup before SAI_BCLK             | 10    | -   | ns   |

| S18 | SAI_RXD hold after SAI_BCLK               | 2     | -   | ns   |

Table 44. Slave mode SAI Timing (continued)

Figure 24. Slave mode SAI Timing

# 6.5 Debug specifications

## 6.5.1 JTAG interface timing

Table 45. JTAG pin AC electrical characteristics <sup>1</sup>

| #  | Symbol                                | Characteristic                      | Min  | Мах                 | Unit |

|----|---------------------------------------|-------------------------------------|------|---------------------|------|

| 1  | t <sub>JCYC</sub>                     | TCK Cycle Time <sup>2, 2</sup>      | 62.5 | —                   | ns   |

| 2  | t <sub>JDC</sub>                      | TCK Clock Pulse Width               | 40   | 60                  | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK Rise and Fall Times (40% - 70%) |      | 3                   | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI Data Setup Time            | 5    | _                   | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI Data Hold Time             | 5    |                     | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK Low to TDO Data Valid           | —    | 20 <sup>3, 3</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK Low to TDO Data Invalid         | 0    | _                   | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK Low to TDO High Impedance       |      | 15                  | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK Falling Edge to Output Valid    | —    | 600 <sup>4, 4</sup> | ns   |

Table continues on the next page ...

### Table 46. Nexus debug port timing <sup>1</sup> (continued)

| No. | Symbol                                     | Parameter                     | Condition<br>s | Min | Мах | Unit |

|-----|--------------------------------------------|-------------------------------|----------------|-----|-----|------|

| 9   | t <sub>NTDIH</sub> ,<br>t <sub>NTMSH</sub> | TDI, TMS Data Hold Time       | _              | 5   | _   | ns   |

| 10  | t <sub>JOV</sub>                           | TCK Low to TDO/RDY Data Valid |                | 0   | 25  | ns   |

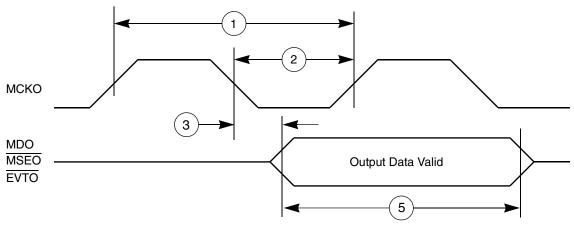

1. JTAG specifications in this table apply when used for debug functionality. All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

- 2. For all Nexus modes except DDR mode, MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- 3. The system clock frequency needs to be four times faster than the TCK frequency.

Figure 28. Nexus output timing

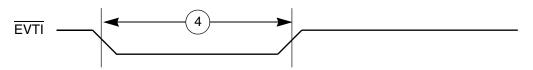

Figure 29. Nexus EVTI Input Pulse Width

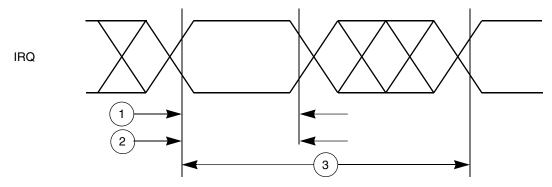

### 6.5.4 External interrupt timing (IRQ pin) Table 48. External interrupt timing specifications

| No. | Symbol            | Parameter               | Conditions | Min | Max | Unit             |

|-----|-------------------|-------------------------|------------|-----|-----|------------------|

| 1   | t <sub>IPWL</sub> | IRQ pulse width low —   |            | 3   | —   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | IRQ pulse width high —  |            | 3   | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | IRQ edge to edge time — |            | 6   |     | t <sub>CYC</sub> |

These values applies when IRQ pins are configured for rising edge or falling edge events, but not both.

Figure 31. External interrupt timing

# 7 Thermal attributes

# 7.1 Thermal attributes

| Board type        | Symbol                                                        | Description                                                                | 176LQFP | Unit | Notes    |

|-------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|---------|------|----------|

| Single-layer (1s) | layer (1s) R <sub>0JA</sub> Therr<br>resist<br>to am<br>conve |                                                                            | 50.7    | °C/W | 11, 22   |

| Four-layer (2s2p) | R <sub>θJA</sub>                                              | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 24.2    | °C/W | 1, 2, 33 |

| Single-layer (1s) | R <sub>ejma</sub>                                             | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 38.1    | °C/W | 1, 3     |

Table continues on the next page ...

#### Thermal attributes

| Board type | Symbol               | Description                                                                                                          | 256 MAPBGA | Unit | Notes |

|------------|----------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|-------|

| -          | R <sub>θJC</sub>     | Thermal<br>resistance, junction<br>to case                                                                           | 7.9        | °C/W | 55    |

|            | Ψ <sub>JT</sub>      | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection)    | 0.2        | °C/W | 66    |

| _          | R <sub>0JB_CSB</sub> | Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) | 9.0        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Board type        | Symbol            | Description                                                                | 100 MAPBGA | Unit | Notes   |

|-------------------|-------------------|----------------------------------------------------------------------------|------------|------|---------|

| Single-layer (1s) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 50.9       | °C/W | 1, 21,2 |

| Four-layer (2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance, junction<br>to ambient (natural<br>convection)      | 27.0       | °C/W | 1,2,33  |

| Single-layer (1s) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 38.0       | °C/W | 1,3     |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed) | 22.2       | °C/W | 1,3     |

Table continues on the next page ...

| Board type | Symbol                                                                                                                               | Description                                 | 100 MAPBGA | Unit | Notes |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|------|-------|

| -          | R <sub>θJB</sub>                                                                                                                     | Thermal<br>resistance, junction<br>to board | 10.8       | °C/W | 44    |

| -          | R <sub>θJC</sub>                                                                                                                     | Thermal<br>resistance, junction<br>to case  | 8.2        | °C/W | 55    |

|            | Ψ <sub>JT</sub> Thermal<br>characteriza<br>parameter, j<br>to package<br>outside cent<br>(natural                                    |                                             | 0.2        | °C/W | 66    |

| _          | Ψ <sub>JB</sub> Thermal<br>characterization<br>parameter, junction<br>to package bottom<br>outside center<br>(natural<br>convection) |                                             | 7.8        | °C/W | 77    |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

# 8 Dimensions

# 8.1 Obtaining package dimensions

Package dimensions are provided in package drawing.

To find a package drawing, go to www.nxp.com and perform a keyword search for the drawing's document number:

| Package    | NXP Document Number |

|------------|---------------------|

| 100 MAPBGA | 98ASA00802D         |

Table continues on the next page...

# 10.1.2 BAF execution duration

Following table specifies the typical BAF execution time in case BAF boot header is present at first location (Typical) and last location (worst case). Total Boot time is the sum of reset sequence duration and BAF execution time.

| BAF execution<br>duration                                | Min | Тур | Мах | Unit |

|----------------------------------------------------------|-----|-----|-----|------|

| BAF execution time<br>(boot header at first<br>location) | _   | 200 | _   | μs   |

| BAF execution time<br>(boot header at last<br>location)  | _   | _   | 320 | μs   |

Table 50. BAF execution duration

# 10.1.3 Reset sequence description

The figures in this section show the internal states of the device during the five different reset sequences. The dotted lines in the figures indicate the starting point and the end point for which the duration is specified in .

With the beginning of DRUN mode, the first instruction is fetched and executed. At this point, application execution starts and the internal reset sequence is finished.

The following figures show the internal states of the device during the execution of the reset sequence and the possible states of the RESET\_B signal pin.

### NOTE

RESET\_B is a bidirectional pin. The voltage level on this pin can either be driven low by an external reset generator or by the device internal reset circuitry. A high level on this pin can only be generated by an external pullup resistor which is strong enough to overdrive the weak internal pulldown resistor. The rising edge on RESET\_B in the following figures indicates the time when the device stops driving it low. The reset sequence durations given in are applicable only if the internal reset sequence is not prolonged by an external reset generator keeping RESET\_B asserted low beyond the last Phase3.

| Rev. No. | Date | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>In section: Voltage monitor electrical characteristics         <ul> <li>Updated description for Low Voltage detector block.</li> <li>Added note, BCP56, MCP68 and MJD31 are guaranteed ballasts.</li> <li>In table: Voltage regulator electrical specifications                 <ul></ul></li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |      | <ul> <li>In section: Supply current characteristics <ul> <li>In table: Current consumption characteristics</li> <li>I<sub>DD_BODY_4</sub>: Updated SYS_CLK to 120 MHz.</li> <li>I<sub>DD_BODY_4</sub>: Updated Max for T<sub>a</sub>= 105 °C fand 85 °C )</li> <li>I<sub>dd_STOP</sub>: Added condition for T<sub>a</sub>= 105 °C and removed Max value for T<sub>a</sub>= 85 °C.</li> <li>I<sub>DD_HV_ADC_REF</sub>: Added condition for T<sub>a</sub>= 105 °C and 85 °C and removed Max value for T<sub>a</sub>= 25 °C.</li> <li>I<sub>DD_HV_FLASH</sub>: Added condition for T<sub>a</sub>= 105 °C and 85 °C</li> </ul> </li> <li>In table: Low Power Unit (LPU) Current consumption characteristics <ul> <li>LPU_RUN and LPU_STOP: Added condition for T<sub>a</sub>= 105 °C and 85 °C</li> <li>In table: STANDBY Current consumption characteristics</li> <li>Added condition for T<sub>a</sub>= 105 °C for all entries.</li> </ul> </li> </ul> |

|          |      | <ul> <li>In section: I/O parameters <ul> <li>In table: Functional Pad AC Specifications @ 3.3 V Range</li> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table: DC electrical specifications @ 3.3V Range <ul> <li>Updateded Min and Max values for Vih and Vil respectively.</li> </ul> </li> <li>In table: Functional Pad AC Specifications @ 5 V Range <ul> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table DC electrical specifications @ 5 V Range <ul> <li>Updated values for 'pad_sr_hv (output)'</li> </ul> </li> <li>In table DC electrical specifications @ 5 V Range <ul> <li>Updated Min value for Vhys</li> </ul> </li> </ul>                                                                                                                                                                                                                                                           |

Table 51. Revision History (continued)

Table continues on the next page...

| Rev. No. | Date         | Substantial Changes                                                                                                                                                         |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 3    | 2 March 2016 | In section, Recommended operating conditions                                                                                                                                |

|          |              | Added a new Note                                                                                                                                                            |

|          |              | In section, Voltage regulator electrical characteristics                                                                                                                    |

|          |              | <ul> <li>In table, Voltage regulator electrical specifications:</li> </ul>                                                                                                  |

|          |              | <ul> <li>Added a new row for C<sub>HV_VDD_B</sub></li> <li>Added a factorite on V/</li> </ul>                                                                               |

|          |              | <ul> <li>Added a footnote on V<sub>DD_HV_BALLAST</sub></li> <li>Added a new Note at the end of this section</li> </ul>                                                      |

|          |              |                                                                                                                                                                             |

|          |              | In section, Voltage monitor electrical characteristics                                                                                                                      |

|          |              | <ul> <li>In table, Voltage monitor electrical characteristics:</li> <li>Removed "V<sub>LVD FLASH</sub>" and "V<sub>LVD FLASH</sub> during low power mode using</li> </ul>   |

|          |              | LPBG as reference" rows                                                                                                                                                     |

|          |              | <ul> <li>Updated Fall and Rise trimmed Minimum values for V<sub>HVD_LV_cold</sub></li> </ul>                                                                                |

|          |              | In section, Supply current characteristics                                                                                                                                  |

|          |              | In table, Current consumption characteristics:                                                                                                                              |

|          |              | <ul> <li>Updated the footnote mentioned in the Condition column of I<sub>DD_STOP</sub> row</li> </ul>                                                                       |

|          |              | Updated all TBD values     In table Law Power Unit (LBL) Current consumption above staristics:                                                                              |

|          |              | <ul> <li>In table, Low Power Unit (LPU) Current consumption characteristics:</li> <li>Updated the typical value of LPU_STOP to 0.18 mA</li> </ul>                           |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | <ul> <li>In table, STANDBY Current consumption characteristics:</li> </ul>                                                                                                  |

|          |              | Updated all TBD values                                                                                                                                                      |

|          |              | In section, AC specifications @ 3.3 V Range                                                                                                                                 |

|          |              | In table, Functional Pad AC Specifications @ 3.3 V Range:                                                                                                                   |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | In section, DC electrical specifications @ 3.3V Range                                                                                                                       |

|          |              | In table, DC electrical specifications @ 3.3V Range:                                                                                                                        |

|          |              | <ul> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                                                                                             |

|          |              | In section, AC specifications @ 5 V Range                                                                                                                                   |

|          |              | In table, Functional Pad AC Specifications @ 5 V Range:                                                                                                                     |

|          |              | Updated Rise/Fall Edge values                                                                                                                                               |

|          |              | <ul> <li>In section, DC electrical specifications @ 5 V Range</li> </ul>                                                                                                    |

|          |              | In table, DC electrical specifications @ 5 V Range:                                                                                                                         |

|          |              | <ul> <li>Updated Min and Max values for Pull_Ioh and Pull_Iol rows</li> <li>Updated Max value for Vol to 0.1 * VDD_HV_x</li> </ul>                                          |

|          |              |                                                                                                                                                                             |

|          |              | In section, Reset pad electrical characteristics                                                                                                                            |

|          |              | <ul> <li>In table, Functional reset pad electrical specifications:</li> <li>Updated parameter column for V<sub>IH</sub>, V<sub>IL</sub> and V<sub>HYS</sub> rows</li> </ul> |

|          |              | • Updated Min and Max values for $V_{IH}$ and $V_{IL}$ rows                                                                                                                 |

|          |              |                                                                                                                                                                             |

|          |              | <ul> <li>In section, PORST electrical specifications</li> <li>In table, PORST electrical specifications:</li> </ul>                                                         |

|          |              | <ul> <li>Updated Unit and Min/Max values for V<sub>IH</sub> and V<sub>IL</sub> rows</li> </ul>                                                                              |

|          |              | <ul> <li>In section, input equivalent size it and ADC conversion sharestaristics</li> </ul>                                                                                 |

|          |              | <ul> <li>In section, Input equivalent circuit and ADC conversion characteristics</li> <li>In table, ADC conversion characteristics (for 12-bit):</li> </ul>                 |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | In table, ADC conversion characteristics (for 10-bit):                                                                                                                      |

|          |              | <ul> <li>Updated "ADC Analog Pad (pad going to one ADC)" row</li> </ul>                                                                                                     |

|          |              | In section, Analog Comparator (CMP) electrical specifications                                                                                                               |

|          |              | <ul> <li>In table, Comparator and 6-bit DAC electrical specifications:</li> </ul>                                                                                           |

|          | MPC57        | • Updated Min and Max values for Valo to ±47 mV<br>46C Microcontroller Datasneet Data Sheet, Rev. 5.1, 05/2017.                                                             |

| 74       |              | NXP Semiconductors                                                                                                                                                          |

|          |              | In section, Main oscillator electrical characteristics                                                                                                                      |

#### How to Reach Us:

Home Page: www.nxp.com

Web Support: www.nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2017 NXP B.V.

Document Number: MPC5746C Rev. 5.1, 05/2017