#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | <u>.</u>                                                                |

| RAM Size                   | 36 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c71-04-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C71X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C710 | 512 x 14          | 36 x 8      |

| PIC16C71  | 1K x 14           | 36 x 8      |

| PIC16C711 | 1K x 14           | 68 x 8      |

| PIC16C715 | 2K x 14           | 128 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

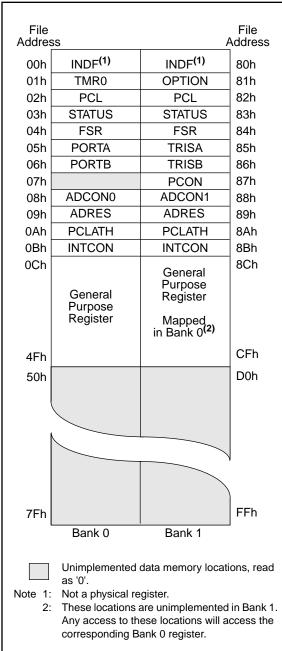

# FIGURE 4-5: PIC16C711 REGISTER FILE MAP

# FIGURE 4-6: PIC16C715 REGISTER FILE MAP

| File<br>Address                                                                          | 3                              |                                | File<br>Address |  |

|------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|-----------------|--|

| 00h                                                                                      | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>            | 80h             |  |

| 01h                                                                                      | TMR0                           | OPTION                         | 81h             |  |

| 02h                                                                                      | PCL                            | PCL                            | 82h             |  |

| 03h                                                                                      | STATUS                         | STATUS                         | 83h             |  |

| 04h                                                                                      | FSR                            | FSR                            |                 |  |

| 05h                                                                                      | PORTA                          | TRISA                          |                 |  |

| 06h                                                                                      | PORTB                          | TRISB                          |                 |  |

| 07h                                                                                      |                                |                                | 87h             |  |

| 08h                                                                                      |                                |                                |                 |  |

| 09h                                                                                      |                                |                                |                 |  |

| 0Ah                                                                                      | PCLATH                         | PCLATH                         | 8Ah             |  |

| 0Bh                                                                                      | INTCON                         | INTCON                         | 8Bh             |  |

| 0Ch                                                                                      | PIR1                           | PIE1                           | 8Ch             |  |

| 0Dh                                                                                      |                                |                                | 8Dh             |  |

| 0Eh                                                                                      |                                | PCON                           | 8Eh             |  |

| 0Fh                                                                                      |                                |                                | 8Fh             |  |

| 10h                                                                                      |                                |                                | 90h             |  |

| 11h                                                                                      |                                |                                | 91h             |  |

| 12h                                                                                      |                                |                                |                 |  |

| 13h                                                                                      |                                |                                | 93h             |  |

| 14h                                                                                      |                                |                                | 94h             |  |

| 15h                                                                                      |                                |                                | 95h             |  |

| 16h                                                                                      |                                |                                | 96h             |  |

| 17h                                                                                      |                                |                                |                 |  |

| 18h                                                                                      |                                |                                | 98h             |  |

| 19h                                                                                      |                                |                                | 99h             |  |

| 1Ah                                                                                      |                                |                                | 9Ah             |  |

| 1Bh                                                                                      |                                |                                | 9Bh             |  |

| 1Ch                                                                                      |                                |                                | 9Ch             |  |

| 1Dh                                                                                      |                                |                                | 9Dh             |  |

| 1Eh                                                                                      | ADRES                          |                                | 9Eh             |  |

| 1Fh                                                                                      | ADCON0                         | ADCON1                         | 9Fh             |  |

| 20h                                                                                      | General<br>Purpose<br>Register | General<br>Purpose<br>Register | A0h             |  |

|                                                                                          | rtogiotor                      |                                | BFh             |  |

|                                                                                          |                                |                                | C0h             |  |

|                                                                                          |                                |                                |                 |  |

| l                                                                                        |                                |                                |                 |  |

|                                                                                          |                                |                                |                 |  |

| 7Fh                                                                                      | Deels                          | Bank 1                         | _ FFh           |  |

|                                                                                          | Bank 0                         | Bank 1                         |                 |  |

| Unimplemented data memory locations, read<br>as '0'.<br>Note 1: Not a physical register. |                                |                                |                 |  |

|                                                                                          |                                |                                |                 |  |

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

#### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x | 500      |                                                      |

|--------|----------|------------------------------------------------------|

| BSF    | pclath,3 | ;Select page 1 (800h-FFFh)                           |

| BCF    | pclath,4 | ;Only on >4K devices                                 |

| CALL   | SUB1_P1  | ;Call subroutine in                                  |

|        | :        | ;page 1 (800h-FFFh)                                  |

|        | :        |                                                      |

|        | :        |                                                      |

| ORG 0x | 900      |                                                      |

| SUB1_P | 1:       | ;called subroutine                                   |

|        | :        | ;page 1 (800h-FFFh)                                  |

|        | :        |                                                      |

| RETURN |          | ;return to Call subroutine<br>;in page 0 (000h-7FFh) |

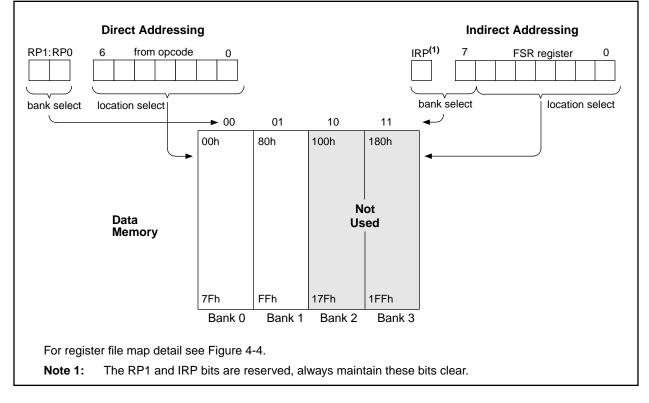

#### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-15. However, IRP is not used in the PIC16C71X devices.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | 0x20<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |                                               |                                                                                                    |

|          | :                     |                                               | ;yes continue                                                                                      |

#### FIGURE 4-15: DIRECT/INDIRECT ADDRESSING

### 5.0 I/O PORTS

#### Applicable Devices 710 71 711 715

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

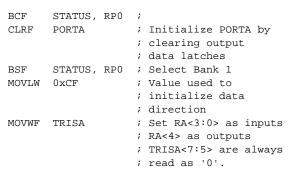

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

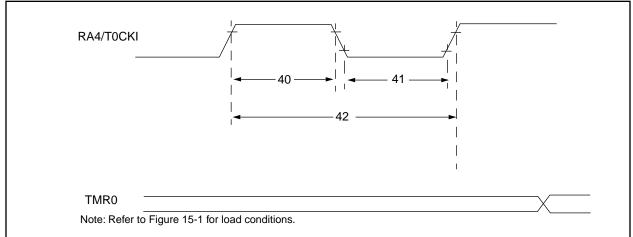

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 5-1: INITIALIZING PORTA

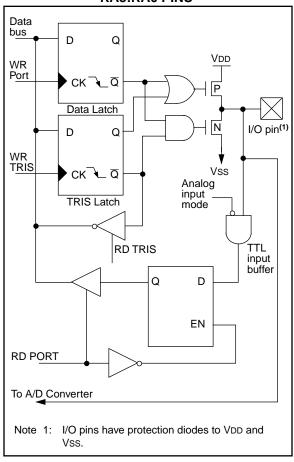

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 PINS

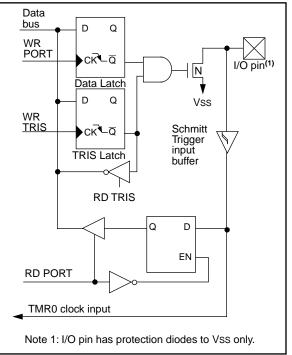

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

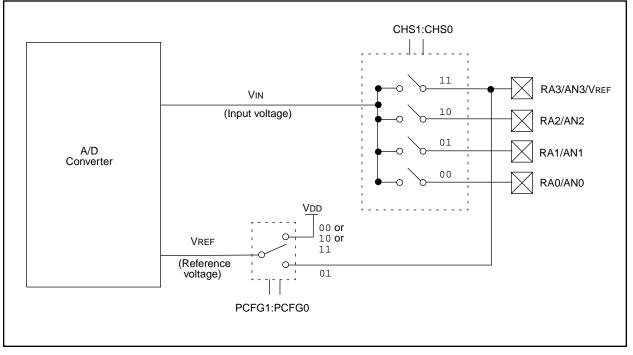

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 7-4.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 7.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- Set GIE bit

- 3. Wait the required acquisition time.

2. Configure A/D interrupt (if desired):

4. Start conversion:

Clear ADIF bit

Set ADIE bit

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 7-4: A/D BLOCK DIAGRAM

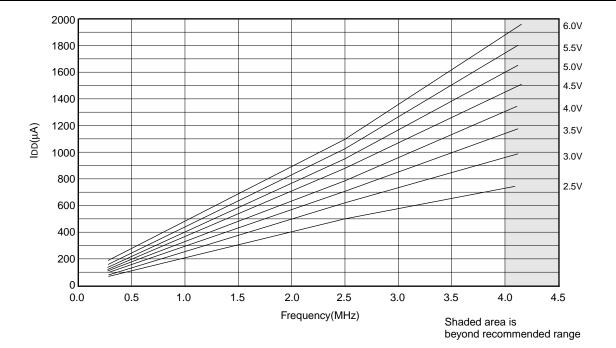

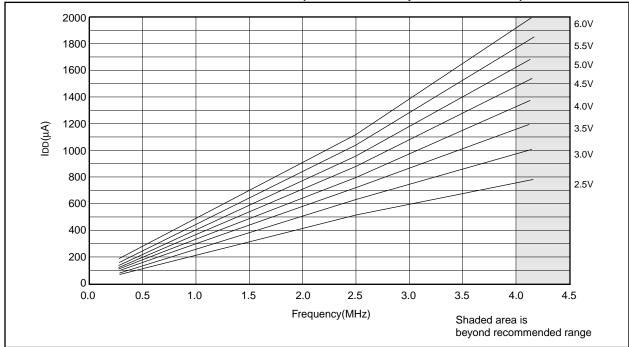

#### 7.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of:

2.0 µs for the PIC16C71

1.6 µs for all other PIC16C71X devices

Table 7-1 and Table 7-2 and show the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 7.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

#### TABLE 7-1: TAD VS. DEVICE OPERATING FREQUENCIES, PIC16C71

| AD Cloc           | k Source (TAD) | Device Frequency          |                           |                           |                         |                         |  |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|-------------------------|-------------------------|--|

| Operation         | ADCS1:ADCS0    | 20 MHz                    | 333.33 kHz                |                           |                         |                         |  |

| 2Tosc             | 00             | 100 ns <sup>(2)</sup>     | 125 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 2.0 μs                  | 6 µs                    |  |

| 8Tosc             | 01             | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 2.0 μs                    | 8.0 μs                  | 24 μs <b>(3)</b>        |  |

| 32Tosc            | 10             | 1.6 μs <sup>(2)</sup>     | 2.0 μs                    | 8.0 µs                    | 32.0 μs <sup>(3)</sup>  | 96 μs <sup>(3)</sup>    |  |

| RC <sup>(5)</sup> | 11             | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> | 2 - 6 μs <sup>(1)</sup> |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu s.$

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

5: For extended voltage devices (LC), please refer to Electrical Specifications section.

#### TABLE 7-2: TAD vs. DEVICE OPERATING FREQUENCIES, PIC16C710/711, PIC16C715

| AD Clock          | Source (TAD) |                           | Device Frequency          |                           |                         |  |  |

|-------------------|--------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|

| Operation         | ADCS1:ADCS0  | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |

| 2Tosc             | 00           | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |

| 8Tosc             | 01           | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |

| 32Tosc            | 10           | 1.6 μs                    | 6.4 μs                    | 25.6 μs <b>(3)</b>        | 96 μs <b>(3)</b>        |  |  |

| RC <sup>(5)</sup> | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu s.$

2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

### 8.0 SPECIAL FEATURES OF THE CPU

#### Applicable Devices 710 71 711 715

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PER) (PIC16C715)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 8.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 8-1: CONFIGURATION WORD FOR PIC16C71

| bit13     | -   -                                                                                                                     | —                                   | —       | —        | _        | _    | — | CP0 | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|-----------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|----------|----------|------|---|-----|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5: | Unimpler                                                                                                                  | nented                              | : Read  | as '1'   |          |      |   |     |       |      |       |               |                      |                 |

| bit 4:    | <b>CP0:</b> Code protection bit<br>1 = Code protection off<br>0 = All memory is code protected, but 00h - 3Fh is writable |                                     |         |          |          |      |   |     |       |      |       |               |                      |                 |

| bit 3:    | <b>PWRTE:</b><br>1 = Power<br>0 = Power                                                                                   | -up Tin                             | ner ena | bled     | le bit   |      |   |     |       |      |       |               |                      |                 |

| bit 2:    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                                                                                      | enabled                             | ł       | Enable   | e bit    |      |   |     |       |      |       |               |                      |                 |

| bit 1-0:  | FOSC1:F<br>11 = RC c<br>10 = HS c<br>01 = XT c<br>00 = LP o                                                               | oscillato<br>oscillato<br>oscillato | or<br>r | tor Sele | ection b | vits |   |     |       |      |       |               |                      |                 |

# TABLE 8-3:CERAMIC RESONATORS,<br/>PIC16C710/711/715

| Ranges Tested: |                                             |                                         |                          |  |  |

|----------------|---------------------------------------------|-----------------------------------------|--------------------------|--|--|

| Mode           | Freq                                        | OSC2                                    |                          |  |  |

| XT             | 455 kHz<br>2.0 MHz<br>4.0 MHz               | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |                          |  |  |

| HS             | 8.0 MHz<br>16.0 MHz                         | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF |  |  |

|                | <b>se values are f</b><br>es at bottom of p | <b>ior design guidar</b><br>bage.       | nce only. See            |  |  |

| Resonator      | rs Used:                                    |                                         |                          |  |  |

| 455 kHz        | Panasonic E                                 | FO-A455K04B                             | ± 0.3%                   |  |  |

| 2.0 MHz        | Murata Erie (                               | CSA2.00MG                               | ± 0.5%                   |  |  |

| 4.0 MHz        | Murata Erie (                               | CSA4.00MG                               | ± 0.5%                   |  |  |

| 8.0 MHz        | Murata Erie CSA8.00MT ± 0.5%                |                                         |                          |  |  |

| 16.0 MHz       | Murata Erie CSA16.00MX ± 0.5%               |                                         |                          |  |  |

| All reso       | onators used did                            | d not have built-in                     | capacitors.              |  |  |

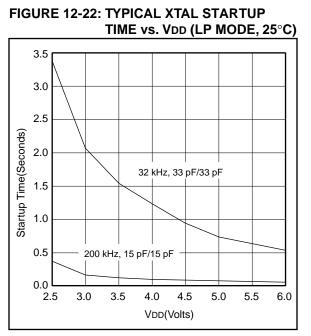

# TABLE 8-4:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR,<br/>PIC16C710/711/715

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1  | Cap. Range<br>C2 |

|----------|-----------------|-------------------|------------------|

| LP       | 32 kHz          | 33 pF             | 33 pF            |

|          | 200 kHz         | 15 pF             | 15 pF            |

| XT       | 200 kHz         | 47-68 pF          | 47-68 pF         |

|          | 1 MHz           | 15 pF             | 15 pF            |

|          | 4 MHz           | 15 pF             | 15 pF            |

| HS       | 4 MHz           | 15 pF             | 15 pF            |

|          | 8 MHz           | 15-33 pF          | 15-33 pF         |

|          | 20 MHz          | 15-33 pF          | 15-33 pF         |

| These    | values are      | for declars avide | nee entry Coo    |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |              |  |  |  |  |

|---------------|------------------------|--------------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM     |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM     |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | $\pm$ 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM     |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM     |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM     |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested table.

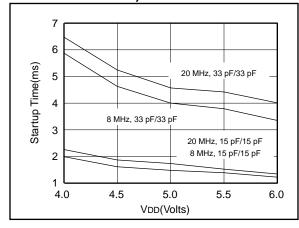

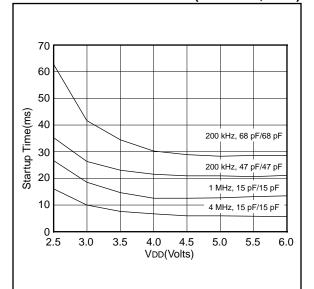

2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 8.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST), and Brown-out Reset</u> (BOR)

#### 8.4.1 POWER-ON RESET (POR)

#### Applicable Devices 710 71 711 715

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

8.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

8.4.3 OSCILLATOR START-UP TIMER (OST)

#### Applicable Devices 710 71 711 715

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

8.4.4 BROWN-OUT RESET (BOR)

#### Applicable Devices 710 71 711 715

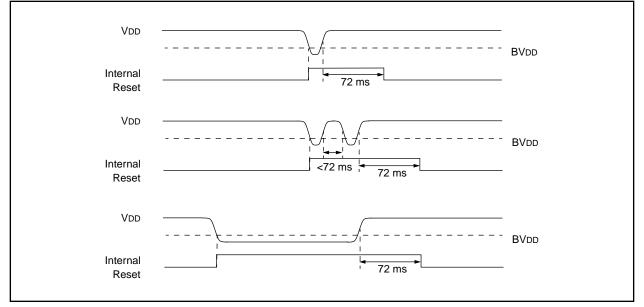

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 8-10 shows typical brown-out situations.

#### FIGURE 8-10: BROWN-OUT SITUATIONS

### 9.1 Instruction Descriptions

|                   | •                                                                                                                               |                  |                |         |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|---------|--|--|

| ADDLW             | Add Lite                                                                                                                        | ral and \        | N              |         |  |  |

| Syntax:           | [ <i>label</i> ] ADDLW k                                                                                                        |                  |                |         |  |  |

| Operands:         | $0 \le k \le 255$                                                                                                               |                  |                |         |  |  |

| Operation:        | $(W) + k \to (W)$                                                                                                               |                  |                |         |  |  |

| Status Affected:  | C, DC, Z                                                                                                                        |                  |                |         |  |  |

| Encoding:         | 11                                                                                                                              | 111x             | kkkk           | kkkk    |  |  |

| Description:      | The conter<br>added to the result is play                                                                                       | ne eight b       | it literal 'k' | and the |  |  |

| Words:            | 1                                                                                                                               |                  |                |         |  |  |

| Cycles:           | 1                                                                                                                               |                  |                |         |  |  |

| Q Cycle Activity: | Q1                                                                                                                              | Q2               | Q3             | Q4      |  |  |

|                   | Decode Read Process Write<br>literal 'k' data W                                                                                 |                  |                |         |  |  |

| Example:          | ADDLW $0 \ge 15$<br>Before Instruction<br>$W = 0 \ge 10$<br>After Instruction<br>$W = 0 \ge 25$                                 |                  |                |         |  |  |

| ADDWF             | Add W a                                                                                                                         | nd f             |                |         |  |  |

| Syntax:           | [ <i>label</i> ] Al                                                                                                             | DDWF             | f,d            |         |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$                                                       | 7                |                |         |  |  |

| Operation:        | (W) + (f) -                                                                                                                     | ightarrow (dest) |                |         |  |  |

| Status Affected:  | C, DC, Z                                                                                                                        |                  |                |         |  |  |

| Encoding:         | 00                                                                                                                              | 0111             | dfff           | ffff    |  |  |

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the |                  |                |         |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff             |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|------------------|--|--|

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                         |                 |                  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4               |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to<br>Dest |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                  |  |  |

|                   | W = 0x17<br>FSR = 0xC2                                                                                                                                                    |                         |                 |                  |  |  |

|                   | After Instruction                                                                                                                                                         |                         |                 |                  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                  |  |  |

| ANDLW             | AND Literal with W                                                                                                  |                        |                 |               |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|---------------|--|--|

| Syntax:           | [ <i>label</i> ] ANDLW k                                                                                            |                        |                 |               |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                     | 55                     |                 |               |  |  |

| Operation:        | (W) .ANE                                                                                                            | D. (k) $\rightarrow$ ( | W)              |               |  |  |

| Status Affected:  | Z                                                                                                                   |                        |                 |               |  |  |

| Encoding:         | 11 1001 kkkk kkkk                                                                                                   |                        |                 |               |  |  |

| Description:      | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                        |                 |               |  |  |

| Words:            | 1                                                                                                                   |                        |                 |               |  |  |

| Cycles:           | 1                                                                                                                   |                        |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                                                                  | Q2                     | Q3              | Q4            |  |  |

|                   | Decode                                                                                                              | Read<br>literal "k"    | Process<br>data | Write to<br>W |  |  |

| Example           | ANDLW                                                                                                               | 0x5F                   |                 |               |  |  |

|                   | Before In                                                                                                           | struction              | 0xA3            |               |  |  |

|                   | After Inst                                                                                                          | •• –                   | UXAU            |               |  |  |

|                   |                                                                                                                     | = W                    | 0x03            |               |  |  |

|                   |                                                                                                                     |                        |                 |               |  |  |

| ANDWF             | AND W with f                                                          |                                    |                                              |                  |  |  |

|-------------------|-----------------------------------------------------------------------|------------------------------------|----------------------------------------------|------------------|--|--|

| Syntax:           | [ <i>label</i> ] A                                                    | [ <i>label</i> ] ANDWF f,d         |                                              |                  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                        | $0 \le f \le 127$<br>$d \in [0,1]$ |                                              |                  |  |  |

| Operation:        | (W) .ANE                                                              | D. (f) $\rightarrow$ (c            | dest)                                        |                  |  |  |

| Status Affected:  | Z                                                                     |                                    |                                              |                  |  |  |

| Encoding:         | 00                                                                    | 0101                               | dfff                                         | ffff             |  |  |

| Description:      | 'd' is 0 the                                                          | result is a 'd' is 1 the           | with regist<br>stored in th<br>e result is s | ie W             |  |  |

| Words:            | 1                                                                     |                                    |                                              |                  |  |  |

| Cycles:           | 1                                                                     |                                    |                                              |                  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                                 | Q3                                           | Q4               |  |  |

|                   | Decode                                                                | Read<br>register<br>'f'            | Process<br>data                              | Write to<br>Dest |  |  |

| Example           | ANDWF                                                                 | FSR,                               | 1                                            |                  |  |  |

|                   | Before In                                                             |                                    |                                              |                  |  |  |

|                   | W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02 |                                    |                                              |                  |  |  |

| BCF               | Bit Clear f                                                         | BTFSC             | Bit Test, Skip if Clear                                                       |  |  |

|-------------------|---------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] BCF f,b                                            | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |  |  |

| Operation:        | 0  ightarrow (f <b>)</b>                                            | Operation:        | skip if (f <b>) = 0</b>                                                       |  |  |

| Status Affected:  | None                                                                | Status Affected:  | None                                                                          |  |  |

| Encoding:         | 01 00bb bfff ffff                                                   | Encoding:         | 01 10bb bfff ffff                                                             |  |  |

| Description:      | Bit 'b' in register 'f' is cleared.                                 | Description:      | If bit 'b' in register 'f' is '1' then the next                               |  |  |

| Words:            | 1                                                                   |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |  |  |

| Cycles:           | 1                                                                   |                   | instruction is discarded, and a NOP is                                        |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                         |                   | executed instead, making this a 2TCY instruction.                             |  |  |

|                   | Decode Read register 'f' Write register 'f'                         | Words:<br>Cycles: | 1<br>1(2)                                                                     |  |  |

| Example           | BCF FLAG REG, 7                                                     | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |  |  |

| _//01/19/0        | Before Instruction                                                  |                   | Decode Read Process NOP register 'f'                                          |  |  |

|                   | FLAG_REG = 0xC7<br>After Instruction                                | If Skip:          | (2nd Cycle)                                                                   |  |  |

|                   | $FLAG_REG = 0x47$                                                   | ·                 | Q1 Q2 Q3 Q4                                                                   |  |  |

|                   |                                                                     |                   | NOP NOP NOP NOP                                                               |  |  |

|                   |                                                                     | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |  |  |

| •                     |      |  |  |  |  |  |

|-----------------------|------|--|--|--|--|--|

| Before Instruction    |      |  |  |  |  |  |

| PC = address          | HERE |  |  |  |  |  |

| After Instruction     |      |  |  |  |  |  |

| if $FLAG < 1 > = 0$ , |      |  |  |  |  |  |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                                                                     |                 |                       |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|-----------------------|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                                              | [ <i>label</i> ] BSF f,b                                            |                 |                       |  |  |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                 |                       |  |  |

| Operation:        | $1 \rightarrow (f < b;$                                                                          | >)                                                                  |                 |                       |  |  |

| Status Affected:  | None                                                                                             |                                                                     |                 |                       |  |  |

| Encoding:         | 01                                                                                               | 01bb                                                                | bfff            | ffff                  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is                                                       | s set.          |                       |  |  |

| Words:            | 1                                                                                                |                                                                     |                 |                       |  |  |

| Cycles:           | 1                                                                                                |                                                                     |                 |                       |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                                                                  | Q3              | Q4                    |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'                                             | Process<br>data | Write<br>register 'f' |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                                                                     |                 |                       |  |  |

| BTFSS             | Bit Test f                                                                                                                                                 | f, Skip if S          | Set                  |              | CALL                                  | Call Sub                             | oroutine                                               |                                             |                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--------------|---------------------------------------|--------------------------------------|--------------------------------------------------------|---------------------------------------------|----------------|

| Syntax:           | [ <i>label</i> ] B1                                                                                                                                        | FSS f,b               |                      |              | Syntax:                               | [ label ]                            | [ <i>label</i> ] CALL k                                |                                             |                |

| Operands:         | $0 \le f \le 12$                                                                                                                                           |                       |                      |              | Operands:                             | $0 \le k \le 2047$                   |                                                        |                                             |                |

|                   | 0 ≤ b < 7                                                                                                                                                  |                       |                      |              | Operation:                            | (PC)+ 1-                             | (PC)+ 1 $\rightarrow$ TOS,                             |                                             |                |

| Operation:        | skip if (f<                                                                                                                                                | :b>) = 1              |                      |              |                                       |                                      | $k \rightarrow PC < 10:0>,$                            |                                             |                |

| Status Affected:  | None                                                                                                                                                       | None                  |                      |              |                                       | ,                                    | $(PCLATH<4:3>) \rightarrow PC<12:11>$                  |                                             |                |

| Encoding:         | 01                                                                                                                                                         | 11bb                  | bfff                 | ffff         | Status Affected:                      | None                                 |                                                        |                                             |                |

| Description:      |                                                                                                                                                            | register 'f' is       |                      | ne next      | Encoding:                             | 10                                   | 0kkk                                                   | kkkk                                        | kkkk           |

|                   | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2TCY instruction. |                       |                      | Description: | (PC+1) is<br>eleven bit<br>into PC bi | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the sta<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |                |

| Words:            | 1                                                                                                                                                          |                       |                      |              |                                       |                                      |                                                        | rom PCLA<br>instruction                     |                |

| Cycles:           | 1(2)                                                                                                                                                       |                       |                      |              | Words:                                | 1                                    |                                                        |                                             |                |

| Q Cycle Activity: | Q1                                                                                                                                                         | Q2                    | Q3                   | Q4           | Cycles:                               | 2                                    |                                                        |                                             |                |

|                   | Decode                                                                                                                                                     | Read<br>register 'f'  | Process<br>data      | NOP          | Q Cycle Activity:                     | Q1                                   | Q2                                                     | Q3                                          | Q4             |

| If Skip:          | (2nd Cyc                                                                                                                                                   | :le)                  |                      |              | 1st Cycle                             | Decode                               | Read<br>literal 'k',                                   | Process<br>data                             | Write to<br>PC |

|                   | Q1                                                                                                                                                         | Q2                    | Q3                   | Q4           | 1                                     |                                      | Push PC<br>to Stack                                    |                                             |                |

|                   | NOP                                                                                                                                                        | NOP                   | NOP                  | NOP          | 2nd Cycle                             | NOP                                  | NOP                                                    | NOP                                         | NOP            |

| Example           | HERE<br>FALSE                                                                                                                                              |                       | FLAG,1<br>PROCESS_   | _CODE        | Example                               | HERE                                 | CALL                                                   | THERE                                       |                |

|                   | TRUE                                                                                                                                                       | •                     |                      |              |                                       | Before Ir                            |                                                        |                                             |                |

|                   |                                                                                                                                                            | •                     |                      |              |                                       | After Ins                            |                                                        | Address HE                                  | RE             |

|                   | Before In                                                                                                                                                  | struction             |                      |              |                                       |                                      | -                                                      | ddress TH                                   |                |

|                   |                                                                                                                                                            |                       | address H            | IERE         |                                       |                                      | TOS = A                                                | Address HE                                  | RE+1           |

|                   | After Inst                                                                                                                                                 | ruction<br>if FLAG<1> | - 0                  |              |                                       |                                      |                                                        |                                             |                |

|                   |                                                                                                                                                            | -                     | > = 0,<br>address F≠ | ALSE         |                                       |                                      |                                                        |                                             |                |

|                   |                                                                                                                                                            | if FLAG<1><br>PC =    | ,                    |              |                                       |                                      |                                                        |                                             |                |

|                   |                                                                                                                                                            | FU = 1                | address TF           | KUE          |                                       |                                      |                                                        |                                             |                |

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 10.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 10.12 <u>C Compiler (MPLAB-C)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

#### 10.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 10.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 10.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

Applicable Devices 710 71 711 715

### 11.0 ELECTRICAL CHARACTERISTICS FOR PIC16C710 AND PIC16C711

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                            | 55 to +125°C                         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Storage temperature                                                                                       |                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                        |                                      |

| Voltage on VDD with respect to VSS                                                                        |                                      |

| Voltage on MCLR with respect to Vss                                                                       | 0 to +14V                            |

| Voltage on RA4 with respect to Vss                                                                        |                                      |

| Total power dissipation (Note 1)                                                                          |                                      |

| Maximum current out of Vss pin                                                                            |                                      |

| Maximum current into VDD pin                                                                              |                                      |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                              |                                      |

| Output clamp current, Ioк (Vo < 0 or Vo > Voo)                                                            | ±20 mA                               |

| Maximum output current sunk by any I/O pin                                                                | 25 mA                                |

| Maximum output current sourced by any I/O pin                                                             | 25 mA                                |

| Maximum current sunk by PORTA                                                                             | 200 mA                               |

| Maximum current sourced by PORTA                                                                          | 200 mA                               |

| Maximum current sunk by PORTB                                                                             |                                      |

| Maximum current sourced by PORTB                                                                          | 200 mA                               |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | - VOH) x IOH} + $\Sigma$ (VOI x IOL) |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# TABLE 11-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C710-04<br>PIC16C711-04                                                                                | PIC16C710-10<br>PIC16C711-10                                                                     | PIC16C710-20<br>PIC16C711-20                                                                    | PIC16LC710-04<br>PIC16LC711-04                                                                            | PIC16C710/JW<br>PIC16C711/JW                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|