#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 36 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c71-20i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16C71X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C710/71** devices have 36 bytes of RAM, the **PIC16C711** has 68 bytes of RAM and the **PIC16C715** has 128 bytes of RAM. Each device has 13 I/O pins. In addition a timer/counter is available. Also a 4-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

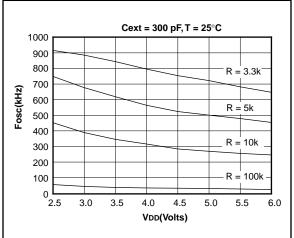

The PIC16C71X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C71X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C71X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

## 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

## 1.2 <u>Development Support</u>

PIC16C71X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 10.0 for more details about Microchip's development tools.

NOTES:

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# <sup>(4)</sup> | SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type                  | Description                                                                                                                                                                                              |

|-----------------|-------------|-----------------------------|--------------|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 16          | 18                          | 16           | I             | ST/CMOS <sup>(3)</sup>          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT     | 15          | 17                          | 15           | 0             | _                               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp        | 4           | 4                           | 4            | I/P           | ST                              | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|                 |             |                             |              |               |                                 | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0         | 17          | 19                          | 17           | I/O           | TTL                             | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1         | 18          | 20                          | 18           | I/O           | TTL                             | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2         | 1           | 1                           | 1            | I/O           | TTL                             | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF    | 2           | 2                           | 2            | I/O           | TTL                             | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI       | 3           | 3                           | 3            | I/O           | ST                              | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                         |

|                 |             |                             |              |               |                                 | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT         | 6           | 7                           | 6            | I/O           | TTL/ST <sup>(1)</sup>           | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1             | 7           | 8                           | 7            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB2             | 8           | 9                           | 8            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB3             | 9           | 10                          | 9            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB4             | 10          | 11                          | 10           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB5             | 11          | 12                          | 11           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB6             | 12          | 13                          | 12           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7             | 13          | 14                          | 13           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss             | 5           | 4, 6                        | 5            | Р             | —                               | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd             | 14          | 15, 16                      | 14           | Р             | —                               | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I = inp |             | O = outp<br>— = Not         |              |               | /O = input/out<br>TTL = TTL inp | I I                                                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The PIC16C71 is not available in SSOP package.

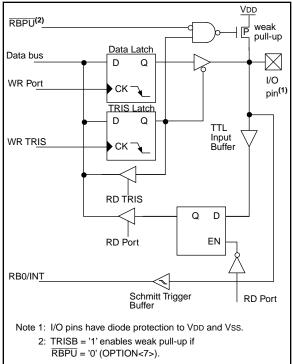

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

### EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, RPC | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPC | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

### FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

| Note: | For the PIC16C71                                 |

|-------|--------------------------------------------------|

|       | if a change on the I/O pin should occur          |

|       | when the read operation is being executed        |

|       | (start of the Q2 cycle), then interrupt flag bit |

|       | RBIF may not get set.                            |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### 7.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 7-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 20 MHz and 16 MHz (The A/D clock is programmed for 32TOSC), and assumes that immediately after 6TAD, the A/D clock is programmed for 2TOSC.

The 2Tosc violates the minimum TAD time since the last 4-bits will not be converted to correct values.

| EXAMPLE 7-3: | 4-BIT vs. 8-BIT CONVERSION TIMES |

|--------------|----------------------------------|

| $\mathbf{L}$ |                                  |

|                                 | - (1)                      | Resolution |         |  |  |

|---------------------------------|----------------------------|------------|---------|--|--|

|                                 | Freq. (MHz) <sup>(1)</sup> | 4-bit      | 8-bit   |  |  |

| TAD                             | 20                         | 1.6 μs     | 1.6 μs  |  |  |

|                                 | 16                         | 2.0 μs     | 2.0 μs  |  |  |

| Tosc                            | 20                         | 50 ns      | 50 ns   |  |  |

|                                 | 16                         | 62.5 ns    | 62.5 ns |  |  |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 20                         | 10 μs      | 16 μs   |  |  |

|                                 | 16                         | 12.5 μs    | 20 µs   |  |  |

Note 1: The PIC16C71 has a minimum TAD time of 2.0 µs.

All other PIC16C71X devices have a minimum TAD time of 1.6  $\mu$ s.

### 8.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST), and Brown-out Reset</u> (BOR)

### 8.4.1 POWER-ON RESET (POR)

## Applicable Devices 710 71 711 715

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

8.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

8.4.3 OSCILLATOR START-UP TIMER (OST)

## Applicable Devices 710 71 711 715

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

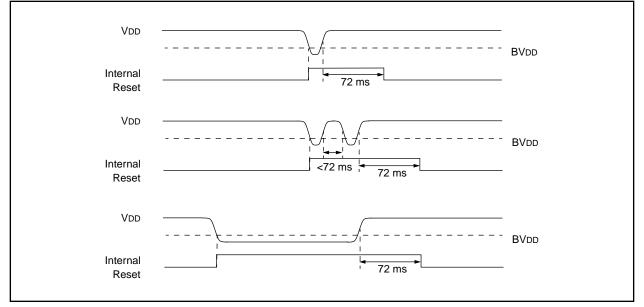

8.4.4 BROWN-OUT RESET (BOR)

### Applicable Devices 710 71 711 715

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 8-10 shows typical brown-out situations.

### FIGURE 8-10: BROWN-OUT SITUATIONS

## 8.5 Interrupts

## Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |

|-------------------------------------------------------|

| External interrupt RB0/INT                            |

| TMR0 overflow interrupt                               |

| PORTB change interrupts (pins RB7:RB4)                |

| A/D Interrupt                                         |

| The interrupt control register (INTCON) records indi- |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

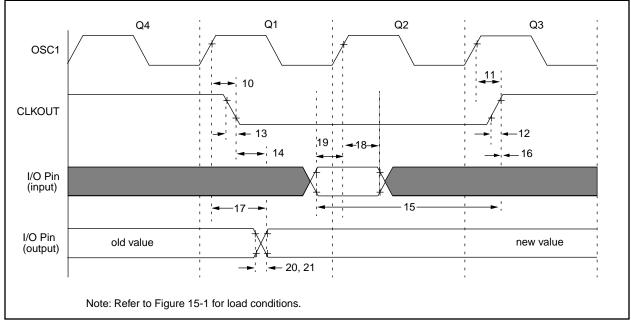

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~                                                                                                                                                                                                                                                                            |      |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Note: For the PIC16C71<br>If an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events the would cause this to occur are: |      |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              | 1    | . An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              | 2    | . The program branches to the Interrupt vector and executes the Interrupt Service Routine.                                                                                                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              | 3    | . The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts. |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              |      | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                              |  |  |  |  |  |  |

| LOOP                                                                                                                                                                                                                                                                         | BCF  | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              |      | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                              | GOTO | LOOP ; NO, try again                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

:

Yes, continue

with program

flow

## TABLE 9-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  |       | 14-Bit Opcode |      |      |      | Status   | Notes |

|------------|--------|------------------------------|-------|---------------|------|------|------|----------|-------|

| Operands   |        |                              |       | MSb           |      |      | LSb  | Affected |       |

| BYTE-ORIEI |        | FILE REGISTER OPERATIONS     |       |               |      |      |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1     | 00            | 0001 | 0xxx | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1     | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1     | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1     | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1     | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1     | 00            | 0000 | lfff | ffff |          |       |

| NOP        | -      | No Operation                 | 1     | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1     | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1     | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1     | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |       |               |      |      |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1     | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1     | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2) | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL AN |        | NTROL OPERATIONS             |       |               |      |      |      |          |       |

| ADDLW      | k      | Add literal and W            | 1     | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1     | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2     | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1     | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2     | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1     | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1     | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2     | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2     | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2     | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1     | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1     | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

| OUDLIN     |        |                              |       |               |      |      |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# **PIC16C71X**

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] CLRF f                                               |                         |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 127$                                                     |                         |                 |                       |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                         |                 |                       |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | G_REG           |                       |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |                         |                 |                       |  |  |  |

|                   | $FLAG\_REG = 0x00$ $Z = 1$                                            |                         |                 |                       |  |  |  |

| CLRW                                                                | Clear W                                                                                                                                                    |                                                          |                                                           |                                                                               |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|

| Syntax:                                                             | [ label ]                                                                                                                                                  | CLRW                                                     |                                                           |                                                                               |

| Operands:                                                           | None                                                                                                                                                       |                                                          |                                                           |                                                                               |

| Operation:                                                          | $00h \rightarrow (V 1 \rightarrow Z$                                                                                                                       | V)                                                       |                                                           |                                                                               |

| Status Affected:                                                    | Z                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Encoding:                                                           | 00                                                                                                                                                         | 0001                                                     | 0xxx                                                      | xxxx                                                                          |

| Description:                                                        | W register set.                                                                                                                                            | is cleare                                                | d. Zero bit                                               | (Z) is                                                                        |

| Words:                                                              | 1                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Cycles:                                                             | 1                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Q Cycle Activity:                                                   | Q1                                                                                                                                                         | Q2                                                       | Q3                                                        | Q4                                                                            |

|                                                                     | Decode                                                                                                                                                     | NOP                                                      | Process<br>data                                           | Write to<br>W                                                                 |

| Example                                                             | CLRW                                                                                                                                                       |                                                          |                                                           |                                                                               |

|                                                                     | Before In                                                                                                                                                  | struction                                                | 1                                                         |                                                                               |

|                                                                     |                                                                                                                                                            | W =                                                      | 0x5A                                                      |                                                                               |

|                                                                     | After Inst                                                                                                                                                 |                                                          |                                                           |                                                                               |

|                                                                     |                                                                                                                                                            | W =<br>Z =                                               | 0x00<br>1                                                 |                                                                               |

|                                                                     |                                                                                                                                                            | -                                                        | •                                                         |                                                                               |

| CLRWDT                                                              | Clear Wa                                                                                                                                                   | tchdog                                                   | Timer                                                     |                                                                               |

| Syntax:                                                             | [ label ]                                                                                                                                                  | CLRWD                                                    | Т                                                         |                                                                               |

| Operands:                                                           | None                                                                                                                                                       |                                                          |                                                           |                                                                               |

| Operation:                                                          | $00h \rightarrow W$                                                                                                                                        |                                                          |                                                           |                                                                               |

|                                                                     | $0 \rightarrow WDT \\ 1 \rightarrow \overline{TO}$                                                                                                         | r presca                                                 | ler,                                                      |                                                                               |

|                                                                     | $1 \rightarrow \overline{PD}$                                                                                                                              |                                                          |                                                           |                                                                               |

|                                                                     |                                                                                                                                                            |                                                          |                                                           |                                                                               |

| Status Affected:                                                    | TO, PD                                                                                                                                                     |                                                          |                                                           |                                                                               |

| Status Affected:<br>Encoding:                                       | <b>TO</b> , <b>PD</b>                                                                                                                                      | 0000                                                     | 0110                                                      | 0100                                                                          |

| Encoding:                                                           | 00<br>CLRWDT in                                                                                                                                            | struction                                                | resets the                                                | Watch-                                                                        |

|                                                                     | 00                                                                                                                                                         | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:                                                           | 00<br>CLRWDT in<br>dog Timer<br>of the WD                                                                                                                  | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:                                           | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.                                                                                                      | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:<br>Words:                                 | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1                                                                                                 | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:<br>Words:<br>Cycles:                      | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1                                                                                            | Instruction<br>It also re<br>T. Status I                 | resets the<br>set <u>s</u> the pr<br>bits TO and          | Watch-<br>re <u>sca</u> ler<br>d PD                                           |

| Encoding:<br>Description:<br>Words:<br>Cycles:                      | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1                                                                                | Istruction<br>It also re<br>T. Status I                  | resets the<br>sets the pl<br>pits TO and<br>Q3<br>Process | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1<br>Decode                                                                       | Q2                                                       | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>2<br>4<br>2<br>1<br>2<br>2<br>2<br>2<br>CLRWDT<br>Before In                             | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>0<br>2<br>1<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2 | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                     | Watch-<br>re <u>sc</u> aler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter          |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>0<br>2<br>0<br>2<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou<br>WDT pres | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00<br>0 |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1<br>Decode<br>CLRWDT<br>Before In<br>After Inst                                 | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou             | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00      |

| NOP               | No Operation  |             |      |      |  |  |  |  |  |  |

|-------------------|---------------|-------------|------|------|--|--|--|--|--|--|

| Syntax:           | [ label ]     | [label] NOP |      |      |  |  |  |  |  |  |

| Operands:         | None          |             |      |      |  |  |  |  |  |  |

| Operation:        | No operation  |             |      |      |  |  |  |  |  |  |

| Status Affected:  | None          |             |      |      |  |  |  |  |  |  |

| Encoding:         | 00            | 0000        | 0xx0 | 0000 |  |  |  |  |  |  |

| Description:      | No operation. |             |      |      |  |  |  |  |  |  |

| Words:            | 1             |             |      |      |  |  |  |  |  |  |

| Cycles:           | 1             |             |      |      |  |  |  |  |  |  |

| Q Cycle Activity: | Q1            | Q2          | Q3   | Q4   |  |  |  |  |  |  |

|                   | Decode        | NOP         | NOP  | NOP  |  |  |  |  |  |  |

| Example           | NOP           |             |      |      |  |  |  |  |  |  |

| RETFIE            | Return fi                                                                                                                                                                  | rom Inte | rrupt              |                    |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|--------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                  | RETFIE   |                    |                    |  |  |  |

| Operands:         | None                                                                                                                                                                       |          |                    |                    |  |  |  |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                      | PC,      |                    |                    |  |  |  |

| Status Affected:  | None                                                                                                                                                                       |          |                    |                    |  |  |  |

| Encoding:         | 00                                                                                                                                                                         | 0000     | 0000               | 1001               |  |  |  |

| Monda             | and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |          |                    |                    |  |  |  |

| Words:            | 1                                                                                                                                                                          |          |                    |                    |  |  |  |

| Cycles:           | 2                                                                                                                                                                          |          |                    |                    |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                         | Q2       | Q3                 | Q4                 |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                     | NOP      | Set the<br>GIE bit | Pop from the Stack |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                        | NOP      | NOP                | NOP                |  |  |  |

| Example           | RETFIE                                                                                                                                                                     |          |                    |                    |  |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                           | tion Reg                                       | gister                                               |                                         |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|

| Syntax:          | [ label ]                                                                                          | OPTION                                         | ٧                                                    |                                         |

| Operands:        | None                                                                                               |                                                |                                                      |                                         |

| Operation:       | $(W)\toOF$                                                                                         | PTION                                          |                                                      |                                         |

| Status Affected: | None                                                                                               |                                                |                                                      |                                         |

| Encoding:        | 00                                                                                                 | 0000                                           | 0110                                                 | 0010                                    |

| Description:     | The conter<br>loaded in the<br>instruction<br>patibility with<br>Since OPT<br>register, the<br>it. | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |

| Words:           | 1                                                                                                  |                                                |                                                      |                                         |

| Cycles:          | 1                                                                                                  |                                                |                                                      |                                         |

| Example          |                                                                                                    |                                                |                                                      |                                         |

|                  | To mainta<br>with futur<br>not use th                                                              | re PIC16                                       | CXX prod                                             |                                         |

| RETLW Return with Literal in W                                    |                                                                        |                                        |                                    |                                         |  |  |  |  |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------|------------------------------------|-----------------------------------------|--|--|--|--|--|

| Syntax:                                                           | [ label ]                                                              | RETLW                                  | k                                  |                                         |  |  |  |  |  |

| Operands:                                                         | $0 \le k \le 2$                                                        | 55                                     |                                    |                                         |  |  |  |  |  |

| Operation:                                                        | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow F \end{array}$ | ъс                                     |                                    |                                         |  |  |  |  |  |

| Status Affected:                                                  | None                                                                   |                                        |                                    |                                         |  |  |  |  |  |

| Encoding:                                                         | 11                                                                     | 01xx                                   | kkkk                               | kkkk                                    |  |  |  |  |  |

| Description:                                                      | The W reg<br>bit literal 'k<br>loaded fro<br>return add<br>instruction | t'. The pro<br>m the top<br>ress). Thi | gram cour<br>of the stac           | nter is<br>ck (the                      |  |  |  |  |  |

| Words:                                                            | 1                                                                      |                                        |                                    |                                         |  |  |  |  |  |

| Cycles:                                                           | 2                                                                      |                                        |                                    |                                         |  |  |  |  |  |

| Q Cycle Activity:                                                 | Q1                                                                     | Q2                                     | Q3                                 | Q4                                      |  |  |  |  |  |

| 1st Cycle                                                         | Decode                                                                 | Read<br>literal 'k'                    | NOP                                | Write to<br>W, Pop<br>from the<br>Stack |  |  |  |  |  |

| 2nd Cycle                                                         | NOP                                                                    | NOP                                    | NOP                                | NOP                                     |  |  |  |  |  |

| Example                                                           | CALL TABLI                                                             | ;offse                                 | tains tab<br>t value<br>ow has tab |                                         |  |  |  |  |  |

| TABLE ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ; |                                                                        |                                        |                                    |                                         |  |  |  |  |  |

|                                                                   | RETLW kn<br>Before In                                                  | ; End o<br>struction                   |                                    |                                         |  |  |  |  |  |

|                                                                   |                                                                        | W =                                    | 0x07                               |                                         |  |  |  |  |  |

|                                                                   | After Inst                                                             | ruction<br>W =                         | value of k                         | 8                                       |  |  |  |  |  |

| Syntax:           | [ label ]                                                                                                                                               | RETUR | N    |                       |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------|--|--|--|

| Operands:         | None                                                                                                                                                    |       |      |                       |  |  |  |

| Operation:        | $TOS \to F$                                                                                                                                             | ъС    |      |                       |  |  |  |

| Status Affected:  | None                                                                                                                                                    |       |      |                       |  |  |  |

| Encoding:         | 00                                                                                                                                                      | 0000  | 0000 | 1000                  |  |  |  |

| Description:      | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |       |      |                       |  |  |  |

| Words:            | 1                                                                                                                                                       |       |      |                       |  |  |  |

| Cycles:           | 2                                                                                                                                                       |       |      |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                      | Q2    | Q3   | Q4                    |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                  | NOP   | NOP  | Pop from<br>the Stack |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                     | NOP   | NOP  | NOP                   |  |  |  |

| Example           | RETURN                                                                                                                                                  | rrupt |      |                       |  |  |  |

|                   |                                                                                                                                                         | PC =  | TOS  |                       |  |  |  |

|                   |                                                                                                                                                         |       |      |                       |  |  |  |

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                      |                                                                                  |                                                |                                    |                                              |                                                  | >                                                   | 7                                 |                                      |          |          |          | 7                                     |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------|----------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----------------------------------|--------------------------------------|----------|----------|----------|---------------------------------------|

|                            |                                                    |                                       |                                                    |                      |                                                                                  |                                                |                                    |                                              |                                                  | -                                                   | -                                 |                                      |          |          |          | -                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                      |                                                                                  |                                                | 7                                  |                                              |                                                  | 7                                                   |                                   | 7                                    |          |          |          |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 7                    |                                                                                  |                                                |                                    |                                              | 7                                                | 7                                                   |                                   |                                      |          |          |          |                                       |

| PIC17C4X                   | >                                                  |                                       | 2                                                  | 2                    | 7                                                                                | 7                                              |                                    |                                              | 7                                                | 7                                                   |                                   |                                      | 7        |          |          |                                       |

| PIC16C9XX                  | 2                                                  |                                       | 2                                                  | 2                    | 7                                                                                |                                                |                                    |                                              | 7                                                | 7                                                   |                                   |                                      |          |          | ٢        |                                       |

| PIC16C8X                   | 2                                                  | 7                                     | 7                                                  | 7                    | 7                                                                                | 7                                              |                                    | 7                                            | 7                                                | 2                                                   |                                   |                                      | 7        |          |          |                                       |