Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 36 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c71-20i-so |

|                            |                                                                           |

TABLE 1-1: PIC16C71X FAMILY OF DEVICES

|             |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|-------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|             | EPROM Program Memory (x14 words)                | 512                                 | 1K                  | 1K                                  | 2K                                  | 2K                         | _                          |

| Memory      | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2K                         |

|             | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|             | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| Peripherals | Capture/Compare/PWM<br>Module(s)                | _                                   | _                   | _                                   | _                                   | 1                          | 1                          |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|             | Parallel Slave Port                             | _                                   | _                   | _                                   | _                                   | _                          | _                          |

|             | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|             | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|             | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|             | Voltage Range (Volts)                           | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| Features    | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Brown-out Reset                                 | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

|             |                                                 | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|-------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory (x14 words)                | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                             | 192                         | 192                                       | 376                         | 376                                       |

|             | Timer Module(s)                                 | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM<br>Module(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                             | _                           | Yes                                       | _                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                  | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                               | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                        | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                           | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| Features    | In-Circuit Serial Programming                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                 | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                        | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name   | Bit 7              | Bit 6                                                                                         | Bit 5         | Bit 4        | Bit 3          | Bit 2            | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR, PER | Value on all other resets (3) |

|----------------------|--------|--------------------|-----------------------------------------------------------------------------------------------|---------------|--------------|----------------|------------------|-------------|---------|-------------------------------|-------------------------------|

| Bank 0               |        |                    |                                                                                               |               |              |                |                  |             |         |                               |                               |

| 00h <sup>(1)</sup>   | INDF   | Addressing         | ddressing this location uses contents of FSR to address data memory (not a physical register) |               |              |                |                  |             |         |                               | 0000 0000                     |

| 01h                  | TMR0   | Timer0 mod         | dule's register                                                                               | r             |              |                |                  |             |         | xxxx xxxx                     | uuuu uuuu                     |

| 02h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)                                                                                 | Least Signif  | ficant Byte  |                |                  |             |         | 0000 0000                     | 0000 0000                     |

| 03h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                            | RP0           | TO           | PD             | Z                | DC          | С       | 0001 1xxx                     | 000q quuu                     |

| 04h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ad                                                                                   | dress pointe  | er           |                |                  |             |         | xxxx xxxx                     | uuuu uuuu                     |

| 05h                  | PORTA  | _                  | _                                                                                             | _             | PORTA Dat    | a Latch whe    | n written: PO    | RTA pins wh | en read | x 0000                        | u 0000                        |

| 06h                  | PORTB  | PORTB Da           | ta Latch whe                                                                                  | n written: PC | RTB pins wl  | nen read       |                  |             |         | xxxx xxxx                     | uuuu uuuu                     |

| 07h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 08h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 09h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 0Ah <sup>(1,2)</sup> | PCLATH | _                  | _                                                                                             | _             | Write Buffer | r for the uppe | er 5 bits of the | e Program C | ounter  | 0 0000                        | 0 0000                        |

| 0Bh <sup>(1)</sup>   | INTCON | GIE                | PEIE                                                                                          | TOIE          | INTE         | RBIE           | TOIF             | INTF        | RBIF    | 0000 000x                     | 0000 000u                     |

| 0Ch                  | PIR1   | _                  | ADIF                                                                                          | _             | _            | _              | _                | _           | _       | -0                            | -0                            |

| 0Dh                  | _      | Unimpleme          | Jnimplemented                                                                                 |               |              |                |                  |             |         |                               | _                             |

| 0Eh                  | _      | Unimpleme          | Jnimplemented                                                                                 |               |              |                |                  |             |         |                               | _                             |

| 0Fh                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 10h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 11h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 12h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 13h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 14h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 15h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 16h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 17h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 18h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 19h                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 1Ah                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 1Bh                  | _      | Unimpleme          | nted                                                                                          |               |              |                |                  |             |         | _                             | _                             |

| 1Ch                  | _      | Unimpleme          | Jnimplemented —                                                                               |               |              |                |                  |             |         |                               | _                             |

| 1Dh                  |        | Unimpleme          | Unimplemented —                                                                               |               |              |                |                  |             |         | _                             |                               |

| 1Eh                  | ADRES  | A/D Result         | VD Result Register xxxx xxxx 1                                                                |               |              |                |                  |             |         |                               | uuuu uuuu                     |

| 1Fh                  | ADCON0 | ADCS1              | ADCS0                                                                                         | CHS2          | CHS1         | CHS0           | GO/DONE          | _           | ADON    | 0000 00-0                     | 0000 00-0                     |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non power-up) resets include external reset through  $\overline{\text{MCLR}}$  and Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

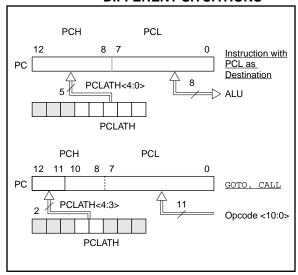

#### 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-14 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-14: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

### 4.4 Program Memory Paging

The PIC16C71X devices ignore both paging bits (PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC16C71X is not recommended since this may affect upward compatibility with future products.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

## **EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)**

BCF STATUS, RPO ;Bank 0

CLRF TMRO ;Clear TMRO & Prescaler

BSF STATUS, RPO ;Bank 1

CLRWDT ;Clears WDT

MOVLW b'xxxxlxxx' ;Selects new prescale value

MOVWF OPTION\_REG ;and assigns the prescaler to the WDT

BCF STATUS, RPO ;Bank 0

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2.

#### **EXAMPLE 6-2:** CHANGING PRESCALER (WDT→TIMER0)

CLRWDT ;Clear WDT and prescaler

BSF STATUS, RP0 ;Bank 1

MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and

MOVWF OPTION\_REG ;clock source

BCF STATUS, RP0 ;Bank 0

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMERO

| Address  | Name   | Bit 7  | Bit 6                    | Bit 5 | Bit 4   | Bit 3      | Bit 2      | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|----------|--------|--------|--------------------------|-------|---------|------------|------------|--------|--------|--------------------------|---------------------------|

| 01h      | TMR0   | Timer0 | Timer0 module's register |       |         |            |            |        |        |                          | uuuu uuuu                 |

| 0Bh,8Bh, | INTCON | GIE    | ADIE                     | TOIE  | INTE    | RBIE       | TOIF       | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h      | OPTION | RBPU   | INTEDG                   | T0CS  | T0SE    | PSA        | PS2        | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h      | TRISA  | _      | _                        | _     | PORTA [ | Data Direc | tion Regis | 1 1111 | 1 1111 |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

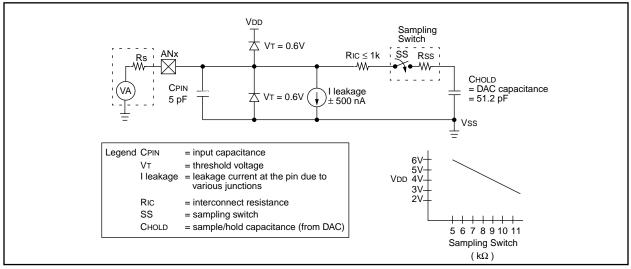

### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is  $10~\text{k}\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

# EQUATION 7-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-TCAP/CHOLD(RIC + RSS + RS))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 pF)(1 k\Omega + Rss + Rs) ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 k\Omega$

1/2 LSb error

$\text{Vdd} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

**Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

Note 4: After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

# EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time +

Temperature Coefficient

TACQ =  $5 \mu s + TCAP + [(Temp - 25°C)(0.05 \mu s/°C)]$

TCAP = -CHOLD (Ric + Rss + Rs) In(1/511)

-51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020)

-51.2 pF (18 k $\Omega$ ) ln(0.0020)

-0.921 μs (-6.2364)

$5.747 \mu s$

TACQ =  $5 \mu s + 5.747 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

$10.747 \,\mu s + 1.25 \,\mu s$

$11.997 \mu s$

#### FIGURE 7-5: ANALOG INPUT MODEL

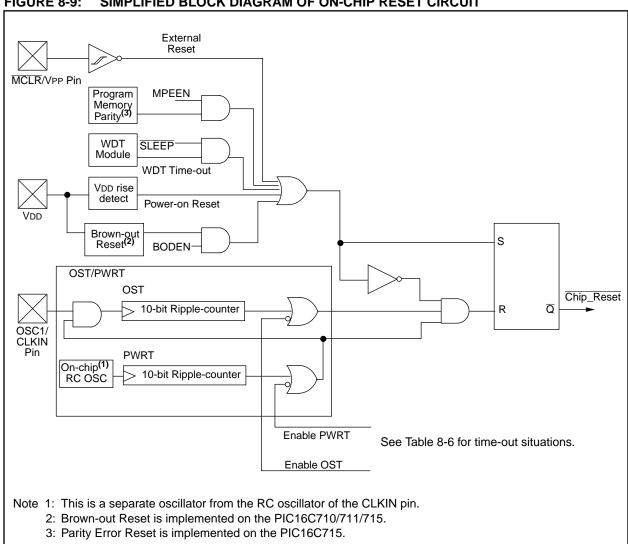

#### 8.3 Reset

#### Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- · Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- · WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT FIGURE 8-9:

TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000q quuu <sup>(3)</sup> | uuuq quuu(3)                       |

| FSR                 | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu(1)                       |

| ADRES               | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | uuuu uuuu                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | uuuu uuuu                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       | uu                                 |

| ADCON1              | 00                                                | 00                       | uu                                 |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

- 3: See Table 8-10 for reset value for specific condition.

- 4: The PCON register is not implemented on the PIC16C71.

- 5: Brown-out reset is not implemented on the PIC16C71.

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

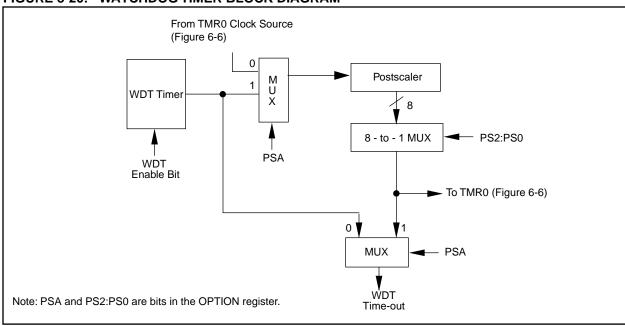

### 8.7 Watchdog Timer (WDT)

# Applicable Devices 710 71 711 715

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 8.1).

#### 8.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be

assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 8.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 8-20: WATCHDOG TIMER BLOCK DIAGRAM

FIGURE 8-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 8-1, Figure 8-2 and Figure 8-3 for operation of these bits.

| SUBWF             | Subtract                       | W from f                      |                                                                  |                  |  |  |  |  |

|-------------------|--------------------------------|-------------------------------|------------------------------------------------------------------|------------------|--|--|--|--|

| Syntax:           | [ label ]                      | SUBWF                         | f,d                                                              |                  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$ | 7                             |                                                                  |                  |  |  |  |  |

| Operation:        | (f) - (W) -                    | → (dest)                      |                                                                  |                  |  |  |  |  |

| Status Affected:  | C, DC, Z                       |                               |                                                                  |                  |  |  |  |  |

| Encoding:         | 00                             | 0010                          | dfff                                                             | ffff             |  |  |  |  |

| Description:      | ister from r<br>stored in th   | egister 'f'. I<br>ne W regist | nent metho<br>f 'd' is 0 the<br>er. If 'd' is 1<br>n register 'f | result is<br>the |  |  |  |  |

| Words:            | 1                              |                               |                                                                  |                  |  |  |  |  |

| Cycles:           | 1                              |                               |                                                                  |                  |  |  |  |  |

| Q Cycle Activity: | Q1                             | Q2                            | Q3                                                               | Q4               |  |  |  |  |

|                   | Decode                         | Read<br>register 'f'          | Process<br>data                                                  | Write to dest    |  |  |  |  |

| Example 1:        | SUBWF                          | REG1,1                        |                                                                  |                  |  |  |  |  |

|                   | Before Instruction             |                               |                                                                  |                  |  |  |  |  |

|                   | REG1                           |                               | 3                                                                |                  |  |  |  |  |

|                   | W<br>C                         | =                             | 2                                                                |                  |  |  |  |  |

|                   | Z                              | =                             | ?                                                                |                  |  |  |  |  |

|                   | After Inst                     | ruction                       |                                                                  |                  |  |  |  |  |

|                   | REG1                           |                               | 1                                                                |                  |  |  |  |  |

|                   | W<br>C                         | =                             | 2<br>1; result is                                                | positive         |  |  |  |  |

|                   | Z                              | =                             | 0                                                                |                  |  |  |  |  |

| Example 2:        | Before In:                     | struction                     |                                                                  |                  |  |  |  |  |

|                   | REG1<br>W                      |                               | 2                                                                |                  |  |  |  |  |

|                   | C                              | =                             | ?                                                                |                  |  |  |  |  |

|                   | Z                              | =                             | ?                                                                |                  |  |  |  |  |

|                   | After Inst                     | ruction                       |                                                                  |                  |  |  |  |  |

|                   | REG1<br>W                      | =                             | 0                                                                |                  |  |  |  |  |

|                   | C                              | =                             | 1; result is                                                     | zero             |  |  |  |  |

|                   | Z                              | =                             | 1                                                                |                  |  |  |  |  |

| Example 3:        | Before In:                     | struction                     |                                                                  |                  |  |  |  |  |

|                   | REG1<br>W                      | =                             | 1                                                                |                  |  |  |  |  |

|                   | C                              | =                             | ?                                                                |                  |  |  |  |  |

|                   | Z                              | =                             | ?                                                                |                  |  |  |  |  |

|                   | After Inst                     | ruction                       |                                                                  |                  |  |  |  |  |

|                   | REG1<br>W                      | =                             | 0xFF<br>2                                                        |                  |  |  |  |  |

|                   | С                              | =                             | 0; result is                                                     | negative         |  |  |  |  |

|                   | Z                              | =                             | 0                                                                |                  |  |  |  |  |

|                   |                                |                               |                                                                  |                  |  |  |  |  |

| SWAPF             | Swap Ni                                                                                                                                                      | bbles in             | f               |               |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|---------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                    | SWAPF 1              | f,d             |               |  |  |  |

| Operands:         | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                           |                      |                 |               |  |  |  |

| Operation:        |                                                                                                                                                              | $\rightarrow$ (dest< |                 |               |  |  |  |

| Status Affected:  | None                                                                                                                                                         |                      |                 |               |  |  |  |

| Encoding:         | 00                                                                                                                                                           | 1110                 | dfff            | ffff          |  |  |  |

| Description:      | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0 the result is placed in W register. If 'd' is 1 the result is placed in register 'f'. |                      |                 |               |  |  |  |

| Words:            | 1                                                                                                                                                            |                      |                 |               |  |  |  |

| Cycles:           | 1                                                                                                                                                            |                      |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                           | Q2                   | Q3              | Q4            |  |  |  |

|                   | Decode                                                                                                                                                       | Read<br>register 'f' | Process<br>data | Write to dest |  |  |  |

| Example           | SWAPF                                                                                                                                                        | REG,                 | 0               |               |  |  |  |

|                   | Before In                                                                                                                                                    | struction            |                 |               |  |  |  |

|                   |                                                                                                                                                              | REG1                 | = 0xA           | <b>\</b> 5    |  |  |  |

|                   | After Inst                                                                                                                                                   | ruction              |                 |               |  |  |  |

|                   |                                                                                                                                                              | REG1<br>W            | = 0x/<br>= 0x5  |               |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                     |  |  |  |  |  |  |

| Operation:       | $\text{(W)} \rightarrow \text{TRIS register f;}$                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                   |  |  |  |  |  |  |

| Description:     | The instruction is supported for code compatibility with the PIC16C5X products. Since TRIS registers are readable and writable, the user can directly address them. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |  |

| Example          |                                                                                                                                                                     |  |  |  |  |  |  |

|                  | To maintain upward compatibility with future PIC16CXX products, do not use this instruction.                                                                        |  |  |  |  |  |  |

|                  |                                                                                                                                                                     |  |  |  |  |  |  |

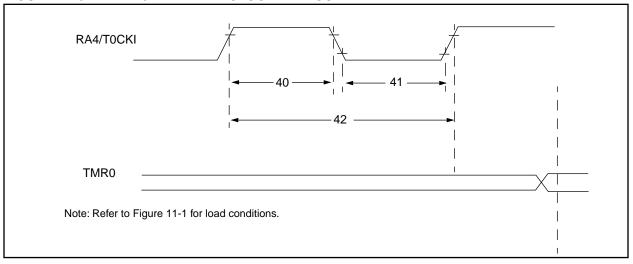

FIGURE 11-6: TIMERO EXTERNAL CLOCK TIMINGS

### TABLE 11-5: TIMERO EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                    |                    | Min                                    | Тур† | Max   | Units | Conditions                      |  |

|--------------|-----------|-----------------------------------|--------------------|----------------------------------------|------|-------|-------|---------------------------------|--|

| 40           | Tt0H      | T0CKI High Pulse Width            | No Prescaler       | 0.5Tcy + 20*                           | _    | _     | ns    | Must also meet                  |  |

|              |           |                                   | With Prescaler     | 10*                                    | _    | _     | ns    | parameter 42                    |  |

| 41           | Tt0L      | T0CKI Low Pulse Width No Prescale |                    | 0.5Tcy + 20*                           | _    | _     | ns    | Must also meet                  |  |

|              |           |                                   | With Prescaler     | 10*                                    | _    | _     | ns    | parameter 42                    |  |

| 42           | Tt0P      | T0CKI Period                      |                    | Greater of:<br>20 ns or TCY + 40*<br>N | _    | _     | ns    | N = prescale value (2, 4,, 256) |  |

| 48           | Tcke2tmrl | Delay from external clock edge    | to timer increment | 2Tosc                                  | _    | 7Tosc | _     |                                 |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

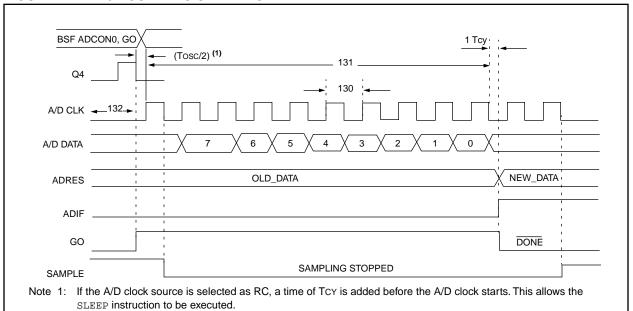

# FIGURE 11-7: A/D CONVERSION TIMING

TABLE 11-7: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                     |                                 | Min    | Тур†    | Max          | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|----------------------------------------------------|---------------------------------|--------|---------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                   | PIC16 <b>C</b> 710/711          | 1.6    | _       | _            | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                                    | PIC16 <b>LC</b> 710/711         | 2.0    | _       | _            | μs    | Tosc based, VREF full range                                                                                                                                                                                 |

|              |      |                                                    | PIC16 <b>C</b> 710/711          | 2.0*   | 4.0     | 6.0          | μs    | A/D RC mode                                                                                                                                                                                                 |

|              |      |                                                    | PIC16 <b>LC</b> 710/711         | 3.0*   | 6.0     | 9.0          | μs    | A/D RC mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not including S/H time). (Note 1) |                                 | _      | 9.5     | _            | TAD   |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                                   |                                 | Note 2 | 20      | _            | μs    |                                                                                                                                                                                                             |

|              |      |                                                    |                                 | 5*     | Ι       | _            | μs    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 19.5 mV @ 5.12V) from the last sampled voltage (as stated on Chold). |

| 134          | TGO  | Q4 to AD clock sta                                 | art                             | _      | Tosc/2§ | <del>_</del> | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

| 135          | Tswc | Switching from co                                  | $nvert \rightarrow sample time$ | 1.5§   | _       | _            | TAD   |                                                                                                                                                                                                             |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

<sup>§</sup> This specification ensured by design.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>2:</sup> See Section 7.1 for min conditions.

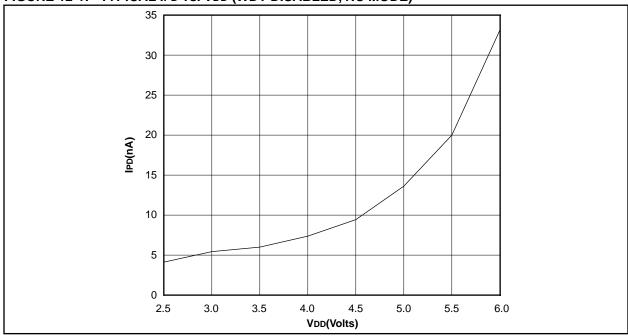

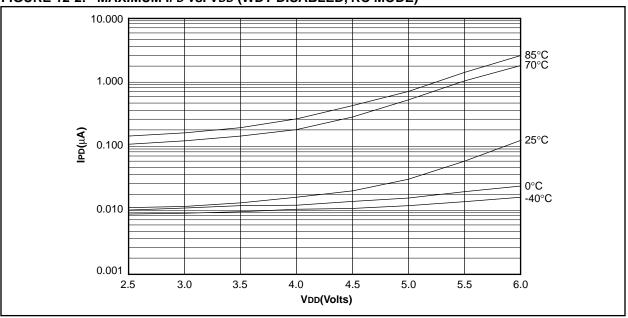

# 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

13.1 **DC Characteristics:** PIC16C715-04 (Commercial, Industrial, Extended)

PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (Commercial, Industrial, Extended)) Standard Operating Conditions (unless otherwise stated)

> Operating temperature 0°C  $\leq$  TA  $\leq$  +70°C (commercial) -40°C  $\leq$  TA  $\leq$  +85°C (industrial)

|                                |                                                                   |             |            |                    |                |                      | 40°C ≤ TA ≤ +65°C (industrial)<br>40°C ≤ TA ≤ +125°C (extended)                                                                                                    |

|--------------------------------|-------------------------------------------------------------------|-------------|------------|--------------------|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym         | Min        | Тур†               | Max            | Units                | Conditions                                                                                                                                                         |

| D001<br>D001A                  | Supply Voltage                                                    | VDD         | 4.0<br>4.5 | -                  | 5.5<br>5.5     | V<br>V               | XT, RC and LP osc configuration HS osc configuration                                                                                                               |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | VDR         | -          | 1.5                | -              | V                    | Device in SLEEP mode                                                                                                                                               |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR        | -          | Vss                | -              | V                    | See section on Power-on Reset for details                                                                                                                          |

| D004*                          | VDD rise rate to ensure internal Power-on Reset signal            | SVDD        | 0.05       | -                  | -              | V/ms                 | See section on Power-on Reset for details                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                           | Bvdd        | 3.7        | 4.0                | 4.3            | V                    | BODEN configuration bit is enabled                                                                                                                                 |

| D010                           | Supply Current (Note 2)                                           | IDD         | -          | 2.7                | 5              | mA .                 | XT, RC osc configuration (PIC16C715-04)<br>FOSC = 4-MHz, VDD = 5.5V (Note 4)                                                                                       |

| D013                           |                                                                   |             | -          | 13.5               | 30             | mA                   | HS osc configuration (PIC16C715-20)<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                   |

| D015                           | Brown-out Reset Current (Note 5)                                  | ΔIBOR       | -<         | 300*               | 500            | hA                   | BOR enabled VDD = 5.0V                                                                                                                                             |

| D020<br>D021<br>D021A<br>D021B | Power-down Current (Note 3)                                       | IPD (       | -          | 10.5<br>1.5<br>1.5 | 21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D023                           | Brown-out Reset Current (Note 5)                                  | <b>MBOR</b> | //         | 300*               | 500            | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

- These parameters are characterized but not tested.

- Data in "Typ"\_column is at 5 1/, 25° C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which You can be lowered in SLEEP mode without losing RAM data.

- 2: The supply gurrent is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC/ = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**DC CHARACTERISTICS**

TABLE 13-6: A/D CONVERTER CHARACTERISTICS:

PIC16C715-04 (COMMERCIAL, INDUSTRIAL, EXTENDED) PIC16C715-10 (COMMERCIAL, INDUSTRIAL, EXTENDED) PIC16C715-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Parameter No. | Sym  | Characteristic                                 | Min       | Тур†       | Max                 | Units    | Conditions                                           |

|---------------|------|------------------------------------------------|-----------|------------|---------------------|----------|------------------------------------------------------|

|               | NR   | Resolution                                     | _         | _          | 8-bits              | _        | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|               | NINT | Integral error                                 | _         | _          | less than<br>±1 LSb | _        | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|               | NDIF | Differential error                             | _         |            | less than<br>±1 LSb | _        | VREF = VDD, VSS ≤ AIN \$ VREF                        |

|               | NFS  | Full scale error                               | _         | _          | less than<br>±1 LSb | _        | VREF = VDD, VSS \( \le AIN \( \le \)VREF             |

|               | Noff | Offset error                                   | _         | _          | less than<br>±1 LSb | _        | VREF = VDØ, VSS & AIN ≤ VREF                         |

|               | _    | Monotonicity                                   | _         | guaranteed | _                   | _        | VSS S AIN VREF                                       |

|               | VREF | Reference voltage                              | 2.5V      | _          | VDD + 0.3           | ٧/       |                                                      |

|               | Vain | Analog input voltage                           | Vss - 0.3 | _          | VREF + 0.3          | V\       |                                                      |

|               | Zain | Recommended impedance of analog voltage source | _         | _          | 10.0                | kΩ       |                                                      |

|               | lad  | A/D conversion current (VDD)                   | _         | 180        |                     |          | Average current consumption when A/D is on. (Note 1) |

|               | IREF | VREF input current (Note 2)                    | _         |            | 1 10                | mA<br>μA | During sampling All other times                      |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

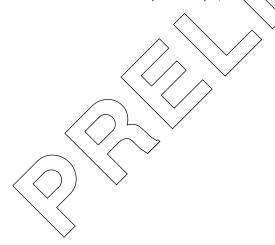

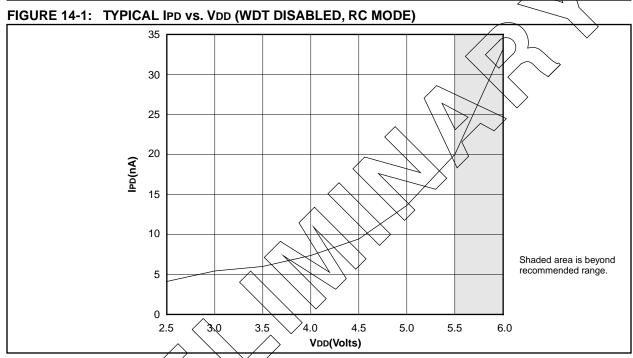

## 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

# 15.5 <u>Timing Diagrams and Specifications</u>

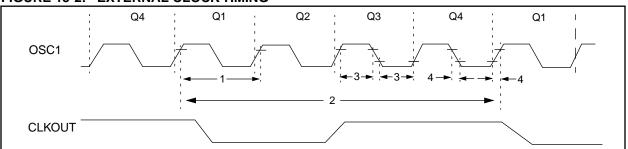

## FIGURE 15-2: EXTERNAL CLOCK TIMING

TABLE 15-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions        |

|---------------|-------|----------------------------------|-----|------|--------|-------|-------------------|

|               | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT osc mode       |

|               |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04) |

|               |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20) |

|               |       |                                  | DC  | _    | 200    | kHz   | LP osc mode       |

|               |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode       |

|               |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode       |

|               |       |                                  | 1   | _    | 4      | MHz   | HS osc mode       |

|               |       |                                  | 1   | _    | 20     | MHz   | HS osc mode       |

| 1             | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT osc mode       |

|               |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04) |

|               |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20) |

|               |       |                                  | 5   | _    | _      | μs    | LP osc mode       |

|               |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode       |

|               |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode       |

|               |       |                                  | 250 | _    | 1,000  | ns    | HS osc mode (-04) |

|               |       |                                  | 50  | _    | 1,000  | ns    | HS osc mode (-20) |

|               |       |                                  | 5   | _    | _      | μs    | LP osc mode       |

| 2             | Tcy   | Instruction Cycle Time (Note 1)  | 1.0 | Tcy  | DC     | μs    | Tcy = 4/Fosc      |

| 3             | TosL, | External Clock in (OSC1) High or | 50  | _    | _      | ns    | XT oscillator     |

|               | TosH  | Low Time                         | 2.5 | _    | _      | μs    | LP oscillator     |

|               |       |                                  | 10  | _    | _      | ns    | HS oscillator     |

| 4             | TosR, | External Clock in (OSC1) Rise or | 25  | _    | _      | ns    | XT oscillator     |

|               | TosF  | Fall Time                        | 50  | _    | _      | ns    | LP oscillator     |

|               |       |                                  | 15  | _    | _      | ns    | HS oscillator     |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C71.

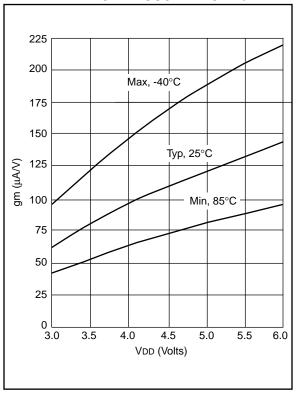

FIGURE 16-17: TRANSCONDUCTANCE (gm) OF LP OSCILLATOR vs. VDD

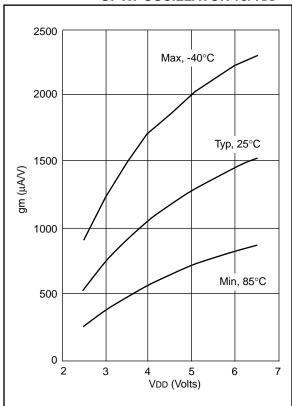

FIGURE 16-18: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

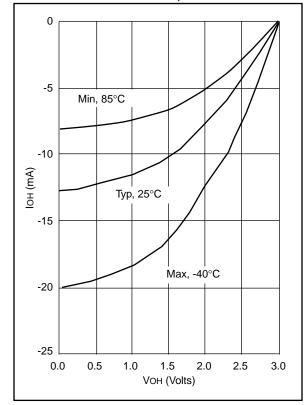

FIGURE 16-19: IOH VS. VOH, VDD = 3V

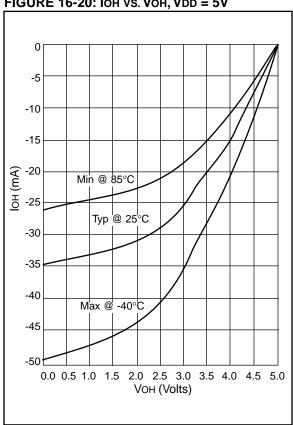

FIGURE 16-20: IOH VS. VOH, VDD = 5V

# **PIC16C71X**

| Figure 7-3:    | ADCON1 Register, PIC16C710/71/711 (Address 88h), | Figure 12-9:                     | Maximum IPD vs. VDD Brown-out Detection (85°C to -40°C, RC Mode) |     |

|----------------|--------------------------------------------------|----------------------------------|------------------------------------------------------------------|-----|

|                | PIC16C715 (Address 9Fh)38                        | Figure 12-10:                    | Typical IPD vs. Timer1 Enabled                                   |     |

| Figure 7-4:    | A/D Block Diagram39                              | · ·                              |                                                                  |     |

| Figure 7-5:    | Analog Input Model40                             |                                  |                                                                  | 103 |

| Figure 7-6:    | A/D Transfer Function45                          | Figure 12-11                     |                                                                  |     |

| Figure 7-7:    | Flowchart of A/D Operation45                     | ga. 0                            |                                                                  |     |

| Figure 8-1:    | Configuration Word for PIC16C7147                |                                  |                                                                  | 103 |

| Figure 8-2:    | Configuration Word, PIC16C710/711 48             | Figure 12 12:                    |                                                                  | 100 |

| -              |                                                  | Figure 12-12.                    |                                                                  | 104 |

| Figure 8-3:    | Configuration Word, PIC16C715                    | Figure 40 40.                    |                                                                  | 104 |

| Figure 8-4:    | Crystal/Ceramic Resonator Operation              | Figure 12-13:                    |                                                                  | 404 |

|                | (HS, XT or LP OSC Configuration) 49              | =                                | •                                                                | 104 |

| Figure 8-5:    | External Clock Input Operation                   | Figure 12-14:                    |                                                                  |     |

|                | (HS, XT or LP OSC Configuration) 49              |                                  |                                                                  | 105 |

| Figure 8-6:    | External Parallel Resonant Crystal               | Figure 12-15:                    | • •                                                              |     |

|                | Oscillator Circuit51                             |                                  | (RC Mode @ 100 pF, -40°C to 85°C)                                | 105 |

| Figure 8-7:    | External Series Resonant Crystal                 | Figure 12-16:                    | Typical IDD vs. Frequency                                        |     |

|                | Oscillator Circuit51                             |                                  | (RC Mode @ 300 pF, 25°C)                                         | 106 |

| Figure 8-8:    | RC Oscillator Mode51                             | Figure 12-17:                    | Maximum IDD vs. Frequency                                        |     |

| Figure 8-9:    | Simplified Block Diagram of On-chip              | •                                | (RC Mode @ 300 pF, -40°C to 85°C)                                | 106 |

| J              | Reset Circuit52                                  | Figure 12-18:                    |                                                                  |     |

| Figure 8-10:   | Brown-out Situations53                           | 9                                | •                                                                | 107 |

| Figure 8-11:   | Time-out Sequence on Power-up                    | Figure 12-19                     | · · · · · · · · · · · · · · · · · · ·                            |     |

| rigaro o TT.   | (MCLR not Tied to VDD): Case 159                 | 1 iguio 12 10.                   |                                                                  | 107 |

| Figure 8-12:   | Time-out Sequence on Power-up                    | Figure 12 20:                    |                                                                  | 101 |

| rigule 0-12.   | ·                                                | Figure 12-20.                    |                                                                  | 107 |

| F: 0 40.       | (MCLR Not Tied To VDD): Case 2                   | Figure 40 04.                    |                                                                  | 107 |

| Figure 8-13:   | Time-out Sequence on Power-up                    | Figure 12-21:                    | (0)                                                              | 407 |

|                | (MCLR Tied to VDD)59                             | =:                               |                                                                  | 107 |