Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E-XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 36 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c710t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2 Data Memory Organization

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow \text{Bank } 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

|                     | 1117 \                                                   |                                                                      |                 |  |  |  |  |

|---------------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------|--|--|--|--|

| File<br>Addres      | s                                                        | ,                                                                    | File<br>Address |  |  |  |  |

| 00h                 | INDF <sup>(1)</sup>                                      | INDF <sup>(1)</sup>                                                  | 80h             |  |  |  |  |

| 01h                 | TMR0                                                     | OPTION                                                               | 81h             |  |  |  |  |

| 02h                 | PCL                                                      | PCL                                                                  | 82h             |  |  |  |  |

| 03h                 | STATUS                                                   | STATUS                                                               | 83h             |  |  |  |  |

| 04h                 | FSR                                                      | FSR                                                                  | 84h             |  |  |  |  |

| 05h                 | PORTA                                                    | TRISA                                                                | 85h             |  |  |  |  |

| 06h                 | PORTB                                                    | TRISB                                                                | 86h             |  |  |  |  |

| 07h                 |                                                          | PCON <sup>(2)</sup>                                                  | 87h             |  |  |  |  |

| 08h                 | ADCON0                                                   | ADCON1                                                               | 88h             |  |  |  |  |

| 09h                 | ADRES                                                    | ADRES                                                                | 89h             |  |  |  |  |

| 0Ah                 | PCLATH                                                   | PCLATH                                                               | 8Ah             |  |  |  |  |

| 0Bh                 | INTCON                                                   | INTCON                                                               | 8Bh             |  |  |  |  |

| 0Ch                 | General<br>Purpose<br>Register                           | General<br>Purpose<br>Register<br>Mapped<br>in Bank 0 <sup>(3)</sup> | 8Ch             |  |  |  |  |

| 2Fh                 |                                                          |                                                                      | AFh             |  |  |  |  |

| 30h                 |                                                          |                                                                      | B0h             |  |  |  |  |

| 3011                |                                                          |                                                                      |                 |  |  |  |  |

| l                   | <                                                        |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

| Ν                   |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      | )               |  |  |  |  |

| 7Fh                 |                                                          |                                                                      | FFh             |  |  |  |  |

| L                   | Bank 0                                                   | Bank 1                                                               | 1               |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

| Note 1:<br>2:<br>3: | 2: The PCON register is not implemented on the PIC16C71. |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

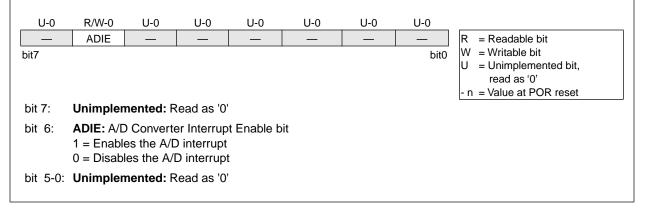

### 4.2.2.4 PIE1 REGISTER

### Applicable Devices 710 71 711 715

This register contains the individual enable bits for the Peripheral interrupts.

### FIGURE 4-10: PIE1 REGISTER (ADDRESS 8Ch)

### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### FIGURE 7-2: ADCON0 REGISTER (ADDRESS 1Fh), PIC16C715

| R/W-0    | R/W-0                                                           | R/W-0                      | R/W-0       | R/W-0       | R/W-0           | U-0          | R/W-0        |                                       |  |  |  |

|----------|-----------------------------------------------------------------|----------------------------|-------------|-------------|-----------------|--------------|--------------|---------------------------------------|--|--|--|

| ADCS1    | ADCS0                                                           | —                          | CHS1        | CHS0        | GO/DONE         | —            | ADON         | R = Readable bit                      |  |  |  |

| bit7     |                                                                 |                            |             |             |                 |              | bit0         | W = Writable bit                      |  |  |  |

|          |                                                                 |                            |             |             |                 |              |              | U = Unimplemented bit,<br>read as '0' |  |  |  |

|          |                                                                 |                            |             |             |                 |              |              | - n = Value at POR reset              |  |  |  |

| bit 7-6: | ADCS1:A                                                         | ADCS0: A                   | D Conver    | sion Clock  | Select bits     |              |              |                                       |  |  |  |

|          | 00 = Fos                                                        |                            |             |             |                 |              |              |                                       |  |  |  |

|          | 01 = Fos                                                        |                            |             |             |                 |              |              |                                       |  |  |  |

|          | 10 = Fosc/32<br>11 = FRC (clock derived from an RC oscillation) |                            |             |             |                 |              |              |                                       |  |  |  |

| bit 5:   | Unused                                                          | · ·                        |             |             | ,               |              |              |                                       |  |  |  |

| bit 6-3: | 000 = cha                                                       | annel 0, (F                |             | l Select bi | its             |              |              |                                       |  |  |  |

|          |                                                                 | annel 1, (F                |             |             |                 |              |              |                                       |  |  |  |

|          |                                                                 | annel 2, (F<br>annel 3, (F |             |             |                 |              |              |                                       |  |  |  |

|          |                                                                 | annel 0, (F                |             |             |                 |              |              |                                       |  |  |  |

|          |                                                                 | annel 1, (F                | ,           |             |                 |              |              |                                       |  |  |  |

|          |                                                                 | annel 2, (F                | ,           |             |                 |              |              |                                       |  |  |  |

|          |                                                                 | annel 3, (F<br>—           | ,           |             |                 |              |              |                                       |  |  |  |

| bit 2:   |                                                                 |                            | nversion S  | Status bit  |                 |              |              |                                       |  |  |  |

|          | If ADON :                                                       | -                          |             | <i>/</i>    |                 |              | • 、          |                                       |  |  |  |

|          |                                                                 |                            |             |             | this bit starts |              |              | lware when the A/D conver-            |  |  |  |

|          | sion is co                                                      |                            | not in pro  | grood (Th   |                 | ationally of | area by hare |                                       |  |  |  |

| bit 1:   | Unimple                                                         | mented: F                  | Read as '0' |             |                 |              |              |                                       |  |  |  |

| bit 0:   | ADON: A                                                         | /D On bit                  |             |             |                 |              |              |                                       |  |  |  |

|          |                                                                 |                            | nodule is c |             |                 |              |              |                                       |  |  |  |

|          | 0 = A/D c                                                       | converter r                | nodule is s | shutoff and | d consumes no   | o operating  | l current    |                                       |  |  |  |

# FIGURE 7-3: ADCON1 REGISTER, PIC16C710/71/711 (ADDRESS 88h), PIC16C715 (ADDRESS 9Fh)

| bit, read as '0'                                                                                                                                                                                                                             | ) U-0                                    | U-0 U-0                                       | U-0                       | U-0                   | R/W-0             | R/W-0 |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|---------------------------|-----------------------|-------------------|-------|-------------------|

| <ul> <li>U = Unimplemented:<br/>bit, read as '0'</li> <li>PCFG1:PCFG0: A/D Port Configuration Control bits</li> <li>PCFG1:PCFG0 RA1 &amp; RA0 RA2 RA3 VREF</li> <li>00 A A A A VDD</li> <li>01 A A VREF RA3</li> <li>10 A D D VDD</li> </ul> | · _                                      |                                               | _                         | _                     | PCFG1             | PCFG0 | R = Readable bit  |

| 00AAAVDD01AAVREFRA310ADDVDD                                                                                                                                                                                                                  | 2: Unimplemen                            | <b>ted:</b> Read as '0                        | '                         |                       |                   | bitO  | U = Unimplemented |

| 01AAVREFRA310ADDVDD                                                                                                                                                                                                                          | 0: PCFG1:PCFC                            | GO: A/D Port Co                               | nfiguration C             | Control bits          |                   |       |                   |

| 10 A D D VDD                                                                                                                                                                                                                                 |                                          | 1                                             | -                         |                       | VREF              |       |                   |

|                                                                                                                                                                                                                                              | PCFG1:PCFG0                              | RA1 & RA0                                     | RA2                       | RA3                   | _                 |       |                   |

| 11 D D D VDD                                                                                                                                                                                                                                 | <b>PCFG1:PCFG0</b>                       | <b>RA1 &amp; RA0</b><br>A                     | <b>RA2</b>                | <b>RA3</b>            | Vdd               |       |                   |

|                                                                                                                                                                                                                                              | <b>PCFG1:PCFG0</b> 00 01                 | <b>RA1 &amp; RA0</b><br>A<br>A                | <b>RA2</b><br>A<br>A      | RA3<br>A<br>VREF      | VDD<br>RA3        |       |                   |

| D = Digital I/O                                                                                                                                                                                                                              | PCFG1:PCFG0 00 01 10 11 A = Analog input | RA1 & RA0           A           A           D | <b>RA2</b><br>A<br>A<br>D | RA3<br>A<br>VREF<br>D | VDD<br>RA3<br>VDD |       |                   |

### 7.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

### 7.6 <u>A/D Accuracy/Error</u>

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at <  $\pm$ 1 LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from TOSC, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

## 7.7 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

### 7.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | Care must be taken when using the RA0       |

|-------|---------------------------------------------|

|       | pin in A/D conversions due to its proximity |

|       | to the OSC1 pin.                            |

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

## 8.0 SPECIAL FEATURES OF THE CPU

## Applicable Devices 710 71 711 715

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PER) (PIC16C715)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 8.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### FIGURE 8-1: CONFIGURATION WORD FOR PIC16C71

| bit13     | -   -                                                       | —                                   | —       | —        | _        | _       | —       | CP0      | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|-----------|-------------------------------------------------------------|-------------------------------------|---------|----------|----------|---------|---------|----------|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5: | Unimpler                                                    | nented                              | : Read  | as '1'   |          |         |         |          |       |      |       |               |                      |                 |

| bit 4:    | <b>CP0:</b> Cod<br>1 = Code<br>0 = All me                   | protect                             | ion off |          | ed, but  | 00h - 3 | Fh is w | /ritable |       |      |       |               |                      |                 |

| bit 3:    | <b>PWRTE:</b><br>1 = Power<br>0 = Power                     | -up Tin                             | ner ena | bled     | le bit   |         |         |          |       |      |       |               |                      |                 |

| bit 2:    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                        | enabled                             | ł       | Enable   | e bit    |         |         |          |       |      |       |               |                      |                 |

| bit 1-0:  | FOSC1:F<br>11 = RC c<br>10 = HS c<br>01 = XT c<br>00 = LP o | oscillato<br>oscillato<br>oscillato | or<br>r | tor Sele | ection b | vits    |         |          |       |      |       |               |                      |                 |

## 8.3 <u>Reset</u>

## Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and

WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

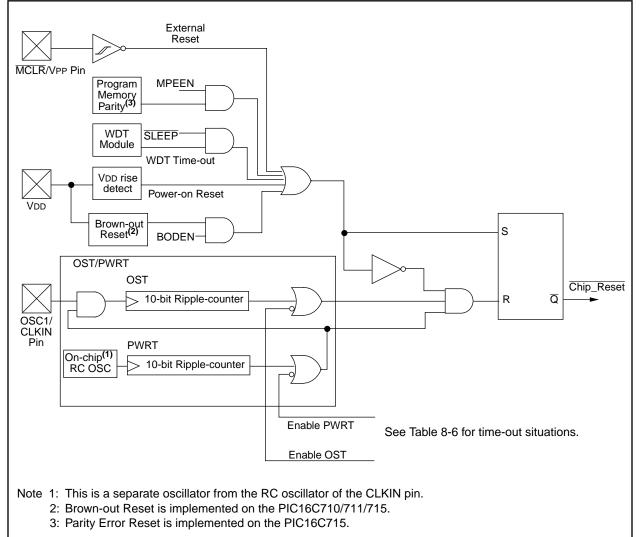

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

### FIGURE 8-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

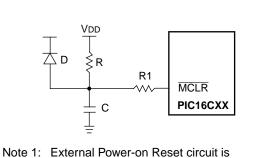

### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

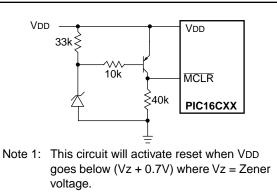

### FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

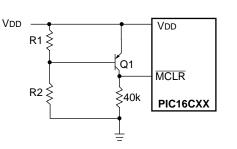

## FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### 8.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 8.8 for details on SLEEP mode.

#### 8.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). (Section 6.0)

#### 8.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

For the PIC16C71 Note: if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

|                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                     |

|--------------------------|-------------------|-------------------|--------------------------------------------|-------------------|---------------------------------------|

| OSC1 /                   |                   |                   |                                            |                   |                                       |

| CLKOUT ③                 | (4)               |                   |                                            | /                 |                                       |

| INT pin                  |                   | 1                 | 1<br>1<br>1<br>1                           |                   | 1 1<br>1 1<br>1 1<br>1 1              |

| INTF flag<br>(INTCON<1>) |                   |                   | Interrupt Latency (2)                      |                   |                                       |

| GIE bit<br>(INTCON<7>)   |                   |                   |                                            |                   |                                       |

| INSTRUCTION              | FLOW              |                   | ,<br>, , , , , , , , , , , , , , , , , , , |                   | · · · · · · · · · · · · · · · · · · · |

| PC                       | PC                | PC+1              | PC+1                                       | X 0004h           | X 0005h                               |

| Instruction (<br>fetched | Inst (PC)         | Inst (PC+1)       | _                                          | Inst (0004h)      | Inst (0005h)                          |

| Instruction {            | Inst (PC-1)       | Inst (PC)         | Dummy Cycle                                | Dummy Cycle       | Inst (0004h)                          |

|                          |                   |                   |                                            |                   |                                       |

## FIGURE 8-19: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode. 4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

### 8.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

### 8.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. A/D conversion (when A/D clock source is RC).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the subset (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 8.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# PIC16C71X

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |

|                   | FLAG_REG = 0xC7<br>After Instruction   | If Skip:          | (2nd Cycle)                                                                   |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |

| •                     |      |  |  |  |  |  |  |

|-----------------------|------|--|--|--|--|--|--|

| Before Instruction    |      |  |  |  |  |  |  |

| PC = address          | HERE |  |  |  |  |  |  |

| After Instruction     |      |  |  |  |  |  |  |

| if $FLAG < 1 > = 0$ , |      |  |  |  |  |  |  |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                                                                     |                 |                       |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                                              | SF f,b                                                              |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                 |                       |  |  |  |

| Operation:        | $1 \rightarrow (f < b)$                                                                          | >)                                                                  |                 |                       |  |  |  |

| Status Affected:  | None                                                                                             |                                                                     |                 |                       |  |  |  |

| Encoding:         | 01                                                                                               | 01bb                                                                | bfff            | ffff                  |  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is                                                       | s set.          | ·                     |  |  |  |

| Words:            | 1                                                                                                |                                                                     |                 |                       |  |  |  |

| Cycles:           | 1                                                                                                |                                                                     |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                                                                  | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'                                             | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG REG = 0x8A |                                                                     |                 |                       |  |  |  |

# PIC16C71X

| Appli | cable Devices | 710 71  | 711 715                                                                                                                                                                                                                                                                                                  |             |

|-------|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 11.1  | DC Character  | istics: | PIC16C710-04 (Commercial, Industrial, Extended<br>PIC16C711-04 (Commercial, Industrial, Extended<br>PIC16C710-10 (Commercial, Industrial, Extended<br>PIC16C711-10 (Commercial, Industrial, Extended<br>PIC16C710-20 (Commercial, Industrial, Extended<br>PIC16C711-20 (Commercial, Industrial, Extended | )<br>)<br>) |

| DC CHARACTERISTICS             |                                                                   |               | Operating temperature |                           |                      | ture (               | ditions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended)                             |

|--------------------------------|-------------------------------------------------------------------|---------------|-----------------------|---------------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min                   | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                         |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5            | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -                     | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                    |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -                     | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                          |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD          | 0.05                  | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                           | Bvdd          | 3.7                   | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                 |

|                                |                                                                   |               | 3.7                   | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                           | IDD           | -                     | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                      |

| D013                           |                                                                   |               | -                     | 13.5                      | 30                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                     | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |

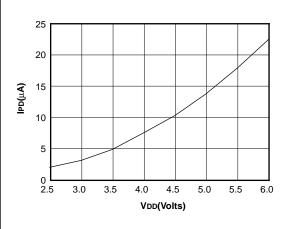

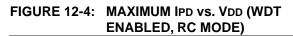

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>-<br>-      | 10.5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 4.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -0^{\circ}C to +70^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                     | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDDMCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### Applicable Devices 710 71 711 715

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS                     |                                                                   |               |             | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended) |                    |                      |                                                                                                                                                                                                      |

|----------------------------------------|-------------------------------------------------------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                           | Characteristic                                                    | Sym           | Min         | Тур†                                                                                                                                                                                                                                              | Max                | Units                | Conditions                                                                                                                                                                                           |

| D001                                   | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0  | -                                                                                                                                                                                                                                                 | 6.0<br>6.0         | V<br>V               | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                               |

| D002*                                  | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -           | 1.5                                                                                                                                                                                                                                               | -                  | V                    |                                                                                                                                                                                                      |

| D003                                   | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -           | Vss                                                                                                                                                                                                                                               | -                  | V                    | See section on Power-on Reset for details                                                                                                                                                            |

| D004*                                  | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | SVDD          | 0.05        | -                                                                                                                                                                                                                                                 | -                  | V/ms                 | See section on Power-on Reset for details                                                                                                                                                            |

| D005                                   | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7         | 4.0                                                                                                                                                                                                                                               | 4.3                | V                    | BODEN configuration bit is enabled                                                                                                                                                                   |

| D010                                   | Supply Current<br>(Note 2)                                        | IDD           | -           | 2.0                                                                                                                                                                                                                                               | 3.8                | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                        |

| D010A                                  |                                                                   |               | -           | 22.5                                                                                                                                                                                                                                              | 48                 | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                      |

| D015                                   | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -           | 300*                                                                                                                                                                                                                                              | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                               |

| D020<br>D021<br>D021A<br>D021B<br>D022 | Power-down Current<br>(Note 3)<br>Brown-out Reset                 |               | -<br>-<br>- | 7.5<br>0.9<br>0.9<br>0.9                                                                                                                                                                                                                          | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V, WDT enabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, 0°C to +70°C<br>VDD = 3.0V, WDT disabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, -40°C to +125°C<br>ROB enabled VDD = 5.0V |

| D023                                   | Brown-out Reset<br>Current (Note 5)                               | ΔIBOR         | -           | 300*                                                                                                                                                                                                                                              | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                               |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## Applicable Devices 710 71 711 715

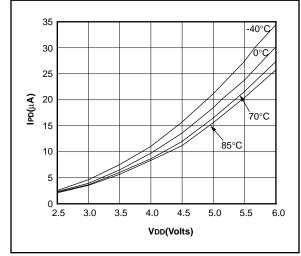

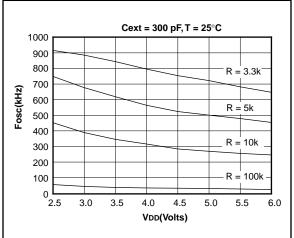

### FIGURE 12-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

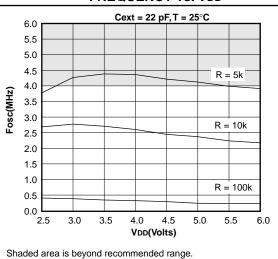

### FIGURE 12-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

# PIC16C71X

## Applicable Devices 710 71 711 715

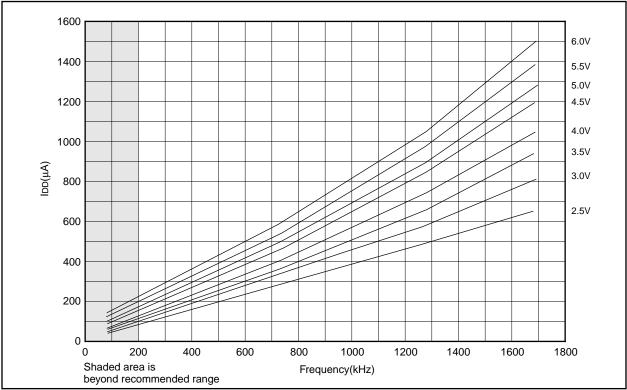

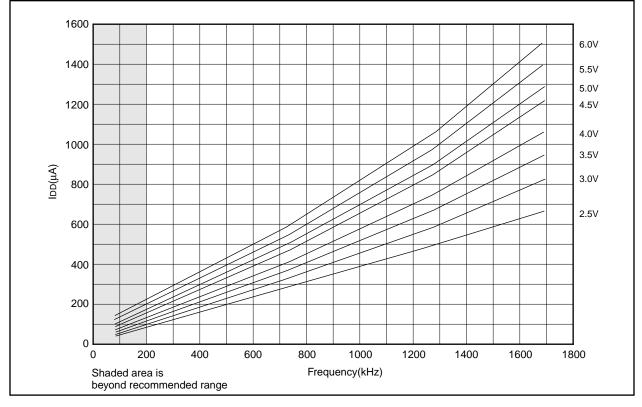

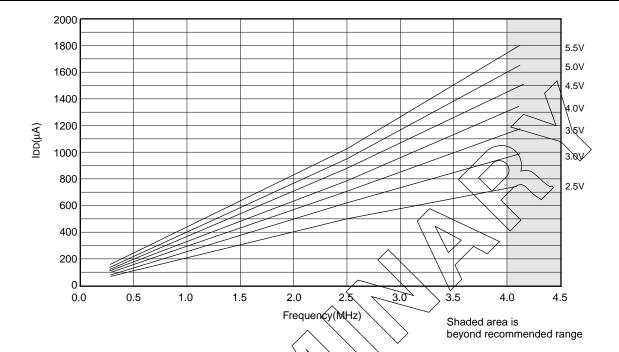

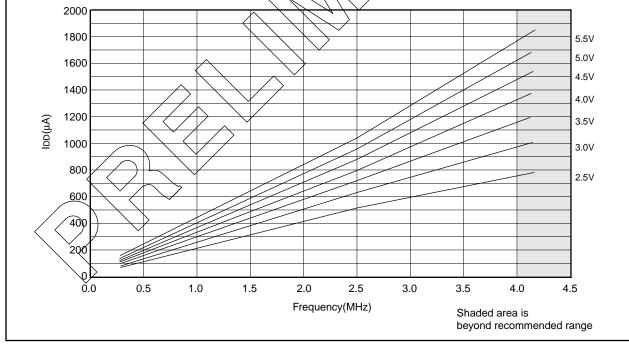

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

# Applicable Devices 710 71 711 715

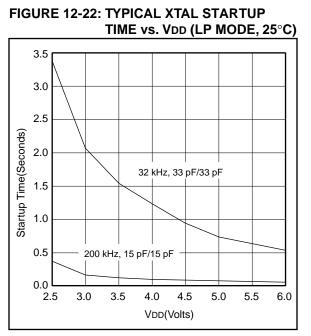

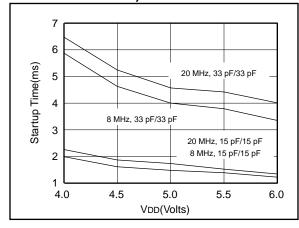

FIGURE 12-23: TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

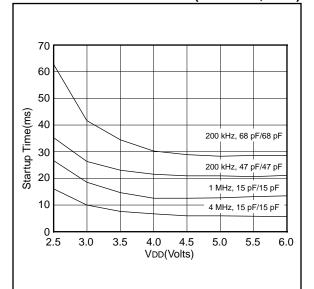

### FIGURE 12-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

|                  |                 | <b>A B</b>       | <b>a b</b>       |

|------------------|-----------------|------------------|------------------|

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

| LP               | 32 kHz          | 33 pF            | 33 pF            |

|                  | 200 kHz         | 15 pF            | 15 pF            |

| ХТ               | 200 kHz         | 47-68 pF         | 47-68 pF         |

|                  | 1 MHz           | 15 pF            | 15 pF            |

|                  | 4 MHz           | 15 pF            | 15 pF            |

| HS               | 4 MHz           | 15 pF            | 15 pF            |

|                  | 8 MHz           | 15-33 pF         | 15-33 pF         |

|                  | 20 MHz          | 15-33 pF         | 15-33 pF         |

|                  |                 |                  |                  |

| Crystals<br>Used |                 |                  |                  |

| 32 kHz           | Epson C-00      | )1R32.768K-A     | ± 20 PPM         |

| 200 kHz          | STD XTL 2       | ± 20 PPM         |                  |

| 1 MHz            | ECS ECS-1       | ± 50 PPM         |                  |

| 4 MHz            | ECS ECS-4       | ± 50 PPM         |                  |

| 8 MHz            | EPSON CA        | ± 30 PPM         |                  |

| 20 MHz           | EPSON CA        | ± 30 PPM         |                  |

# Applicable Devices 710 71 711 715

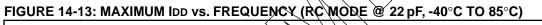

## FIGURE 14-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

# PIC16C71X

## INDEX

|   | Δ. |

|---|----|

| • | •  |

| A/D                                             |     |

|-------------------------------------------------|-----|

| Accuracy/Error                                  | 44  |

| ADIF bit                                        |     |

| Analog Input Model Block Diagram                |     |

| Analog-to-Digital Converter                     | 37  |

| Configuring Analog Port Pins                    |     |

| Configuring the Interrupt                       |     |

| Configuring the Module                          |     |

| Connection Considerations                       |     |

| Conversion Clock                                |     |

| Conversion Time                                 |     |

|                                                 |     |

| Conversions                                     |     |

| Converter Characteristics                       |     |

| Delays                                          |     |

| Effects of a Reset                              |     |

| Equations                                       |     |

| Faster Conversion - Lower Resolution Trade-off4 |     |

| Flowchart of A/D Operation                      |     |

| GO/DONE bit                                     | 39  |

| Internal Sampling Switch (Rss) Impedence        |     |

| Minimum Charging Time                           |     |

| Operation During Sleep                          | 44  |

| Sampling Requirements                           | 40  |

| Source Impedence                                | 40  |

| Time Delays                                     | 40  |

| Transfer Function                               | 45  |

| Absolute Maximum Ratings                        | 35  |

| AC Characteristics                              |     |

| PIC16C710                                       | 01  |

| PIC16C71110                                     |     |

| PIC16C715                                       |     |

| ADCON0 Register                                 |     |

| ADCON1                                          |     |

| ADCON1 Register                                 |     |

| ADCS0 bit                                       |     |

| ADCS1 bit                                       |     |

| ADIE bit                                        |     |

| ADIE bit                                        |     |

|                                                 |     |

| ADON bit                                        |     |

| ADRES Register                                  |     |

| ALU                                             | . 7 |

| Application Notes                               |     |

| AN546                                           |     |

| AN552                                           |     |

| AN5562                                          |     |

| AN607, Power-up Trouble Shooting                | 53  |

| Architecture                                    |     |

| Harvard                                         | . 7 |

| Overview                                        | . 7 |

| von Neumann                                     | . 7 |

| Assembler                                       |     |

| MPASM Assembler                                 | 36  |

|                                                 |     |

| В                                               |     |

|                                                 |     |

| Block Diagrams        |   |

|-----------------------|---|

| Analog Input Model    |   |

| On-Chip Reset Circuit |   |

| PIC16C71X             | 8 |

| RA3/RA0 Port Pins     |   |

| RA4/T0CKI Pin         |   |

| RB3:RB0 Port Pins     |   |

| RB7:RB4 Pins          |   |

|                       |   |

| RB7:RB4 Port Pins     | 28     |

|-----------------------|--------|

|                       | -      |

| Timer0                |        |

| Timer0/WDT Prescaler  |        |

| Watchdog Timer        | 65     |

| BODEN bit             | 48     |

| BOR bit               | 22, 54 |

| Brown-out Reset (BOR) | 53     |

|                       |        |

# С

| C bit                                      | 17     |

|--------------------------------------------|--------|

| C16C71                                     | 47     |

| Carry bit                                  | 7      |

| CHS0 bit                                   | 37     |

| CHS1 bit                                   | 37     |

| Clocking Scheme                            | 10     |

| Code Examples                              |        |

| Call of a Subroutine in Page 1 from Page 0 | 24     |

| Changing Prescaler (Timer0 to WDT)         | 35     |

| Changing Prescaler (WDT to Timer0)         | 35     |

| Doing an A/D Conversion                    | 42     |

| I/O Programming                            | 30     |

| Indirect Addressing                        |        |

| Initializing PORTA                         | 25     |

| Initializing PORTB                         | 27     |

| Saving STATUS and W Registers in RAM       | 64     |

| Code Protection                            | 47, 67 |

| Computed GOTO                              |        |

| Configuration Bits                         | 47     |

| CP0 bit                                    | 47, 48 |

| CP1 bit                                    | 48     |

|                                            |        |

# D

| DC bit                        | 17       |

|-------------------------------|----------|

| DC Characteristics            | 147      |

| PIC16C71                      | 136      |

| PIC16C710                     | 90, 101  |

| PIC16C711                     | 90, 101  |

| PIC16C715                     | 113, 125 |

| Development Support           |          |

| Development Tools             | 85       |

| Diagrams - See Block Diagrams |          |

| Digit Carry bit               | 7        |

| Direct Addressing             | 24       |

| -                             |          |

# Е

| Electrical Characteristics            |     |

|---------------------------------------|-----|

| PIC16C71                              | 135 |

| PIC16C710                             | 89  |

| PIC16C711                             | 89  |

| PIC16C715                             | 111 |

| External Brown-out Protection Circuit | 60  |

| External Power-on Reset Circuit       | 60  |

# F

| Family of Devices                                    |        |

|------------------------------------------------------|--------|

| PIC16C71X                                            | 4      |

| FOSC0 bit                                            | 47, 48 |

| FOSC1 bit                                            | 47, 48 |

| FSR Register                                         |        |

| Fuzzy Logic Dev. System (fuzzyTECH <sup>®</sup> -MP) | 87     |

| G                                                    |        |

| General Description                                  | 3      |

| General Description |  |

|---------------------|--|

| GIE bit             |  |

| GO/DONE bit         |  |

|                     |  |

| TO bit           |   |

|------------------|---|

| TOSE bit         |   |

| TRISA Register   |   |

| TRISB Register   |   |

| Two's Complement | 7 |

| U                |   |

| 0                    |   |

|----------------------|---|

| Upward Compatibility |   |

| UV Erasable Devices  | 5 |

### W

| W Register                 |    |

|----------------------------|----|

| ĂLU                        | 7  |

| Wake-up from SLEEP         |    |

| Watchdog Timer (WDT)       |    |

| WDT                        |    |

| Block Diagram              | 65 |

| Programming Considerations | 65 |

| Timeout                    |    |

| WDT Period                 | 65 |

| WDTE bit                   |    |

| Z                          |    |

| Z bit . |     |   |

|---------|-----|---|

| Zero b  | bit | 7 |

# LIST OF EXAMPLES

| Example 3-1:  | Instruction Pipeline Flow10         |

|---------------|-------------------------------------|

| Example 4-1:  | Call of a Subroutine in Page 1 from |

|               | Page 0 24                           |

| Example 4-2:  | Indirect Addressing 24              |

| Example 5-1:  | Initializing PORTA25                |

| Example 5-2:  | Initializing PORTB27                |

| Example 5-3:  | Read-Modify-Write Instructions      |

|               | on an I/O Port 30                   |

| Example 6-1:  | Changing Prescaler (Timer0→WDT) 35  |

| Example 6-2:  | Changing Prescaler (WDT→Timer0) 35  |

| Equation 7-1: | A/D Minimum Charging Time 40        |

| Example 7-1:  | Calculating the Minimum Required    |

|               | Aquisition Time 40                  |

| Example 7-2:  | A/D Conversion 42                   |

| Example 7-3:  | 4-bit vs. 8-bit Conversion Times 43 |

| Example 8-1:  | Saving STATUS and W Registers       |

|               | in RAM 64                           |

# LIST OF FIGURES

| Figure 3-1:  | PIC16C71X Block Diagram               | 8  |

|--------------|---------------------------------------|----|

| Figure 3-2:  | Clock/Instruction Cycle               |    |

| Figure 4-1:  | PIC16C710 Program Memory Map          |    |

|              | and Stack                             | 11 |

| Figure 4-2:  | PIC16C71/711 Program Memory Map       |    |

| -            | and Stack                             | 11 |

| Figure 4-3:  | PIC16C715 Program Memory Map          |    |

|              | and Stack                             | 11 |

| Figure 4-4:  | PIC16C710/71 Register File Map        | 12 |

| Figure 4-5:  | PIC16C711 Register File Map           | 13 |

| Figure 4-6:  | PIC16C715 Register File Map           |    |

| Figure 4-7:  | Status Register (Address 03h, 83h)    | 17 |

| Figure 4-8:  | OPTION Register (Address 81h, 181h)   | 18 |

| Figure 4-9:  | INTCON Register (Address 0Bh, 8Bh)    | 19 |

| Figure 4-10: | PIE1 Register (Address 8Ch)           | 20 |

| Figure 4-11: | PIR1 Register (Address 0Ch)           | 21 |

| Figure 4-12: | PCON Register (Address 8Eh),          |    |

|              | PIC16C710/711                         | 22 |