Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 36 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c710t-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

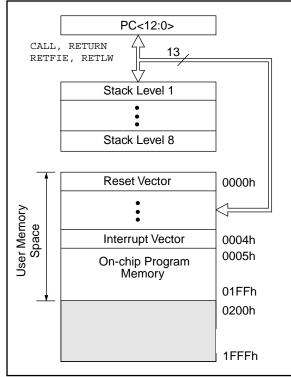

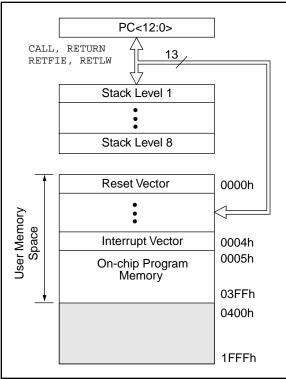

## 4.1 Program Memory Organization

The PIC16C71X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C710 | 512 x 14          | 0000h-01FFh   |

| PIC16C71  | 1K x 14           | 0000h-03FFh   |

| PIC16C711 | 1K x 14           | 0000h-03FFh   |

| PIC16C715 | 2K x 14           | 0000h-07FFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC16C710 PROGRAM MEMORY MAP AND STACK

## FIGURE 4-2: PIC16C71/711 PROGRAM MEMORY MAP AND STACK

## FIGURE 4-3: PIC16C715 PROGRAM MEMORY MAP AND STACK

#### 4.2.2.3 INTCON REGISTER

## Applicable Devices 710 71 711 715

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

#### FIGURE 4-9: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0   | R/W-0                                                  | R/W-0        | R/W-0        | R/W-0                                      | R/W-0                            | R/W-0       | R/W-x        |                                                                                       |

|---------|--------------------------------------------------------|--------------|--------------|--------------------------------------------|----------------------------------|-------------|--------------|---------------------------------------------------------------------------------------|

| GIE     | ADIE                                                   | TOIE         | INTE         | RBIE                                       | TOIF                             | INTF        | RBIF         | R = Readable bit                                                                      |

| bit7    |                                                        |              |              | -                                          |                                  |             | bitO         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:  | <b>GIE:<sup>(1)</sup></b> GI<br>1 = Enabl<br>0 = Disab | es all un-r  | nasked in    |                                            |                                  |             |              |                                                                                       |

| bit 6:  | ADIE: A/E<br>1 = Enabl<br>0 = Disab                    | es A/D int   | errupt       | t Enable b                                 | bit                              |             |              |                                                                                       |

| bit 5:  |                                                        | es the TM    | R0 interru   |                                            | bit                              |             |              |                                                                                       |

| bit 4:  | 1 = Enabl                                              | es the RB    | 0/INT exte   | rupt Enab<br>ernal interi<br>ernal inter   | rupt                             |             |              |                                                                                       |

| bit 3:  | 1 = Enabl                                              | es the RB    | port char    | upt Enable<br>nge interru<br>nge interru   | pt                               |             |              |                                                                                       |

| bit 2:  | <b>TOIF:</b> TMF<br>1 = TMR0<br>0 = TMR0               | ) register h | nas overflo  | wed (mus                                   | t be cleare                      | d in softwa | ire)         |                                                                                       |

| bit 1:  | 1 = The R                                              | B0/INT ex    | cternal inte | rupt Flag b<br>errupt occu<br>errupt did i | urred (must                      | be cleare   | d in softwar | e)                                                                                    |

| bit 0:  | 1 = At lea                                             | st one of    | the RB7:R    |                                            | it<br>nanged stat<br>anged state |             | e cleared in | software)                                                                             |

| Note 1: |                                                        | -enabled l   | oy the RET   |                                            |                                  |             |              | ed, the GIE bit may be uninten-<br>ce Routine. Refer to Section 8.5                   |

| globa   |                                                        | GIE (INTC    |              |                                            |                                  |             |              | corresponding enable bit or the rupt flag bits are clear prior to                     |

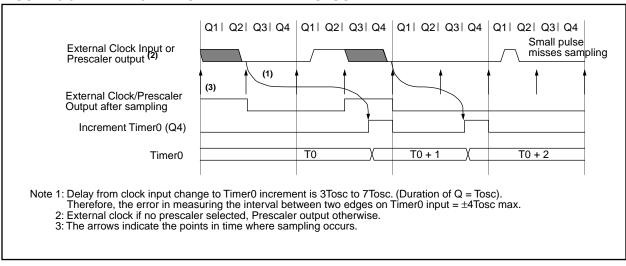

### 6.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

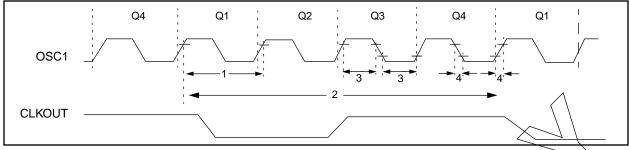

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

## TABLE 8-3:CERAMIC RESONATORS,<br/>PIC16C710/711/715

| Ranges Tested:                                                          |                               |                                         |                                         |  |

|-------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|

| Mode                                                                    | Freq                          | OSC1                                    | OSC2                                    |  |

| XT                                                                      | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |

| HS                                                                      | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |

| These values are for design guidance only. See notes at bottom of page. |                               |                                         |                                         |  |

| Resonator                                                               | Resonators Used:              |                                         |                                         |  |

| 455 kHz Panasonic EFO-A455K04B ± 0.3%                                   |                               |                                         |                                         |  |

| 2.0 MHz                                                                 | Murata Erie (                 | Murata Erie CSA2.00MG ± 0.5%            |                                         |  |

| 4.0 MHz                                                                 | Murata Erie (                 | CSA4.00MG                               | ± 0.5%                                  |  |

| 8.0 MHz                                                                 | Murata Erie (                 | CSA8.00MT                               | ± 0.5%                                  |  |

| 16.0 MHz                                                                | Murata Erie (                 | CSA16.00MX                              | ± 0.5%                                  |  |

| All reso                                                                | onators used did              | d not have built-in                     | capacitors.                             |  |

# TABLE 8-4:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR,<br/>PIC16C710/711/715

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

| These    | values are      | far daalam auida | nee entry Coo    |

These values are for design guidance only. See notes at bottom of page.

|         | Crystals Used          |              |

|---------|------------------------|--------------|

| 32 kHz  | Epson C-001R32.768K-A  | ± 20 PPM     |

| 200 kHz | STD XTL 200.000KHz     | ± 20 PPM     |

| 1 MHz   | ECS ECS-10-13-1        | $\pm$ 50 PPM |

| 4 MHz   | ECS ECS-40-20-1        | ± 50 PPM     |

| 8 MHz   | EPSON CA-301 8.000M-C  | ± 30 PPM     |

| 20 MHz  | EPSON CA-301 20.000M-C | ± 30 PPM     |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested table.

2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

### 8.5 Interrupts

## Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |

|-------------------------------------------------------|

| External interrupt RB0/INT                            |

| TMR0 overflow interrupt                               |

| PORTB change interrupts (pins RB7:RB4)                |

| A/D Interrupt                                         |

| The interrupt control register (INTCON) records indi- |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~    |                  |                                                                                                                                                                                                                                                                                   |  |  |  |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No   | l<br>r<br>(<br>t | or the PIC16C71<br>an interrupt occurs while the Global Inter-<br>upt Enable (GIE) bit is being cleared, the<br>GIE bit may unintentionally be re-enabled<br>y the user's Interrupt Service Routine (the<br>ETFIE instruction). The events that<br>yould cause this to occur are: |  |  |  |

|      | 1                | 1. An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                                       |  |  |  |

|      | 2                | The program branches to the Interrupt vector and executes the Interrupt Service Routine.                                                                                                                                                                                          |  |  |  |

|      | 3                | . The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts.           |  |  |  |

|      |                  | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                                        |  |  |  |

| LOOP | BCF              | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                                   |  |  |  |

|      |                  | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                                     |  |  |  |

|      | GOTO             | LOOP ; NO, try again                                                                                                                                                                                                                                                              |  |  |  |

:

Yes, continue

with program

flow

| COMF                                                              | Complement f                                                                                                                                                                | DECFSZ            | Decreme                                                                                                                                                                                                             | ent f, Sk               | ip if 0                     |                  |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|------------------|

| Syntax:                                                           | [ label ] COMF f,d                                                                                                                                                          | Syntax:           | [ label ]                                                                                                                                                                                                           | DECFS                   | Z f,d                       |                  |

| Operands:                                                         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  | Operands:         | 0 ≤ f ≤ 12<br>d ∈ [0,1]                                                                                                                                                                                             | 27                      |                             |                  |

| Operation:                                                        | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         | Operation:        | (f) - 1 $\rightarrow$                                                                                                                                                                                               | (dest);                 | skip if re                  | sult = 0         |

| Status Affected:                                                  | Z                                                                                                                                                                           | Status Affected:  | None                                                                                                                                                                                                                |                         |                             |                  |

| Encoding:                                                         | 00 1001 dfff ffff                                                                                                                                                           | Encoding:         | 00                                                                                                                                                                                                                  | 1011                    | dfff                        | ffff             |

| Description:                                                      | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>W. If 'd' is 1 the result is stored back in<br>register 'f'.                     | Description:      | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction, is |                         |                             | aced in<br>It is |

| Words:<br>Cycles:                                                 | 1<br>1                                                                                                                                                                      |                   | executed.                                                                                                                                                                                                           | f the resul             | t is 0, then a king it a 2T | a NOP is         |

| Q Cycle Activity:                                                 | Q1 Q2 Q3 Q4                                                                                                                                                                 | Words:            | 1                                                                                                                                                                                                                   |                         |                             |                  |

|                                                                   | Decode Read Process Write to register data dest                                                                                                                             | Cycles:           | 1(2)                                                                                                                                                                                                                |                         |                             |                  |

|                                                                   | 'f' data dest                                                                                                                                                               | Q Cycle Activity: | Q1                                                                                                                                                                                                                  | Q2                      | Q3                          | Q4               |

| Example                                                           | COMF REG1,0                                                                                                                                                                 |                   | Decode                                                                                                                                                                                                              | Read<br>register<br>'f' | Process<br>data             | Write to<br>dest |

|                                                                   | Before Instruction<br>REG1 = 0x13                                                                                                                                           | If Skip:          | (and Cur                                                                                                                                                                                                            |                         |                             |                  |

|                                                                   | After Instruction                                                                                                                                                           | li Skip.          | (2nd Cyc<br>Q1                                                                                                                                                                                                      | Q2                      | Q3                          | Q4               |

|                                                                   | $\begin{array}{rcl} REG1 &=& 0x13\\ W &=& 0xEC \end{array}$                                                                                                                 |                   | NOP                                                                                                                                                                                                                 | NOP                     | NOP                         | NOP              |

| DECF                                                              | Decrement f                                                                                                                                                                 | Example           | HERE                                                                                                                                                                                                                | DECF                    |                             | , 1              |

| Syntax:                                                           | [ <i>label</i> ] DECF f,d                                                                                                                                                   |                   | GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                        |                         |                             |                  |

| Operands:                                                         | $0 \le f \le 127$<br>d \equiv [0,1]                                                                                                                                         |                   |                                                                                                                                                                                                                     |                         |                             |                  |

| Operation:                                                        | (f) - 1 $\rightarrow$ (dest)                                                                                                                                                |                   | Before Ir<br>PC                                                                                                                                                                                                     |                         | ר<br>dress here             |                  |

| Status Affected:                                                  | Z                                                                                                                                                                           |                   | After Inst                                                                                                                                                                                                          |                         | UIC33 HERE                  |                  |

| Encoding:                                                         | 00 0011 dfff ffff                                                                                                                                                           |                   | CNT<br>if CNT                                                                                                                                                                                                       |                         | IT - 1                      |                  |

| Decerintien                                                       | Decrement register 'f'. If 'd' is 0 the                                                                                                                                     |                   | PC<br>if CN1                                                                                                                                                                                                        | = ad                    | dress CON                   | TINUE            |

| Description:                                                      | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'.                                 |                   | PC                                                                                                                                                                                                                  | = ad                    | dress heri                  | 5+1              |

| ·                                                                 | result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'.<br>1                                                                       |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 5+1              |

| Words:                                                            | 'f'.                                                                                                                                                                        |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 5+1              |

| Words:<br>Cycles:                                                 | т.<br>1                                                                                                                                                                     |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 2+1              |

| Words:<br>Cycles:                                                 | Ψ.<br>1<br>1                                                                                                                                                                |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 2+1              |

| Words:<br>Cycles:<br>Q Cycle Activity:                            | <ul> <li>f.</li> <li>1</li> <li>1</li> <li>Q1 Q2 Q3 Q4</li> <li>Decode Read Process Write to dest dest</li> </ul>                                                           |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 5+1              |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Example | <ul> <li>Process</li> <li>Process</li> <li>Decode</li> <li>Read<br/>register</li> <li>'f'</li> <li>Process</li> <li>Write to<br/>data</li> <li>Write to<br/>dest</li> </ul> |                   |                                                                                                                                                                                                                     | = ad                    | dress heri                  | 6+1              |

#### SLEEP

| [ label ]                                                                                                                                                              | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| None                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TO, PD                                                                                                                                                                 |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00                                                                                                                                                                     | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          | TO is<br>pres-<br>EEP<br>ped.                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                                                                                                                     | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                                                                                                                 | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SLEEP                                                                                                                                                                  |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                        | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |

| SUBLW             | Subtract              | W from             | Literal                                                                    |  |  |

|-------------------|-----------------------|--------------------|----------------------------------------------------------------------------|--|--|

| Syntax:           | [ label ]             | SUBL               | N k                                                                        |  |  |

| Operands:         | $0 \le k \le 255$     |                    |                                                                            |  |  |

| Operation:        | k - (W) $\rightarrow$ | • (W)              |                                                                            |  |  |

| Status Affected:  | C, DC, Z              |                    |                                                                            |  |  |

| Encoding:         | 11                    | 110x               | kkkk kkkł                                                                  |  |  |

| Description:      | ment meth             | od) from           | ubtracted (2's complet<br>the eight bit literal 'k<br>I in the W register. |  |  |

| Words:            | 1                     |                    |                                                                            |  |  |

| Cycles:           | 1                     |                    |                                                                            |  |  |

| Q Cycle Activity: | Q1                    | Q2                 | Q3 Q4                                                                      |  |  |

|                   | Decode                | Read<br>literal 'k | Process Write to data                                                      |  |  |

| Example 1:        | SUBLW                 | 0x02               |                                                                            |  |  |

|                   | Before In:            | structior          | ı                                                                          |  |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>?<br>?                                                                |  |  |

|                   | After Inst            | ruction            |                                                                            |  |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>1; result is positive<br>0                                            |  |  |

| Example 2:        | Before In:            | structior          | n                                                                          |  |  |

|                   |                       | W =<br>C =<br>Z =  | 2<br>?<br>?                                                                |  |  |

|                   | After Inst            | ruction            |                                                                            |  |  |

|                   |                       | W =<br>C =<br>Z =  | 0<br>1; result is zero<br>1                                                |  |  |

| Example 3:        | Before In             | structior          | ı                                                                          |  |  |

| Example 0.        |                       | W =                | 3                                                                          |  |  |

| Example 0.        |                       |                    |                                                                            |  |  |

| Example 0.        |                       | C =<br>Z =         | ?<br>?                                                                     |  |  |

|                   | After Inst            | Z =                |                                                                            |  |  |

|                   | After Inst            | Z =                |                                                                            |  |  |

|                   | After Inst            | Z =<br>ruction     | ?                                                                          |  |  |

| SUBWF             | Subtract                                                          | W from f                     |                                   |               |

|-------------------|-------------------------------------------------------------------|------------------------------|-----------------------------------|---------------|

| Syntax:           | [ label ]                                                         | SUBWF                        | f,d                               |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ | 7                            |                                   |               |

| Operation:        | (f) - (W) –                                                       | → (dest)                     |                                   |               |

| Status Affected:  | C, DC, Z                                                          |                              |                                   |               |

| Encoding:         | 00                                                                | 0010                         | dfff                              | ffff          |

| Description:      | Subtract (2<br>ister from r<br>stored in th<br>result is sto      | egister 'f'. I<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the |

| Words:            | 1                                                                 |                              |                                   |               |

| Cycles:           | 1                                                                 |                              |                                   |               |

| Q Cycle Activity: | Q1                                                                | Q2                           | Q3                                | Q4            |

|                   | Decode                                                            | Read                         | Process                           | Write to      |

|                   |                                                                   | register 'f'                 | data                              | dest          |

| Example 1:        | SUBWF                                                             | reg1,1                       |                                   |               |

|                   | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 3                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?                                 |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 1                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>1; result is                 | positive      |

|                   | Z                                                                 | =                            | 0                                 | poolito       |

| Example 2:        | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 2                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?<br>?                            |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 0                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | C<br>Z                                                            | =                            | 1; result is                      | zero          |

| Example 3:        | Eefore Ins                                                        | _                            |                                   |               |

|                   | REG1                                                              | _                            | 1                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | С                                                                 | =                            | ?                                 |               |

|                   | Z<br>After Instr                                                  | =                            | ?                                 |               |

|                   | REG1                                                              |                              | 0xFF                              |               |

|                   | W                                                                 | =                            | 0xFF<br>2                         |               |

|                   | c                                                                 | =                            | 0; result is                      | negative      |

|                   | Z                                                                 | =                            | 0                                 |               |

| SWAPF             | Swap Ni                                                          | bbles in                                            | f                            |                   |  |  |  |  |

|-------------------|------------------------------------------------------------------|-----------------------------------------------------|------------------------------|-------------------|--|--|--|--|

| Syntax:           | [label] SWAPF f,d                                                |                                                     |                              |                   |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 0 ≤ f ≤ 127<br>d ∈ [0,1]                            |                              |                   |  |  |  |  |

| Operation:        | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                |                                                     |                              |                   |  |  |  |  |

| Status Affected:  | None                                                             |                                                     |                              |                   |  |  |  |  |

| Encoding:         | 00                                                               | 1110                                                | dfff                         | ffff              |  |  |  |  |

| Description:      | ter 'f' are e<br>result is pl                                    | and lower<br>exchanged<br>aced in W<br>is placed in | . If 'd' is 0<br>register. I | the<br>f 'd' is 1 |  |  |  |  |

| Words:            | 1                                                                |                                                     |                              |                   |  |  |  |  |

| Cycles:           | 1                                                                |                                                     |                              |                   |  |  |  |  |

| Q Cycle Activity: | Q1                                                               | Q2                                                  | Q3                           | Q4                |  |  |  |  |

|                   | Decode                                                           | Read<br>register 'f'                                | Process<br>data              | Write to<br>dest  |  |  |  |  |

| Example           | SWAPF                                                            | REG,                                                | 0                            |                   |  |  |  |  |

|                   | Before In                                                        | struction                                           |                              |                   |  |  |  |  |

|                   | REG1 = 0xA                                                       |                                                     |                              |                   |  |  |  |  |

|                   | After Instruction                                                |                                                     |                              |                   |  |  |  |  |

|                   |                                                                  | REG1<br>W                                           | = 0x4<br>= 0x5               |                   |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |  |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |  |  |  |  |

| Example          |                                                                                                                                                                                     |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |  |  |  |  |

|                  |                                                                                                                                                                                     |  |  |  |  |

| XORLW             | Exclusi         | ve OR Li                                  | iteral wit      | h W           |

|-------------------|-----------------|-------------------------------------------|-----------------|---------------|

| Syntax:           | [label]         | XORL                                      | V k             |               |

| Operands:         | $0 \le k \le 2$ | 255                                       |                 |               |

| Operation:        | (W) .XO         | $R.k \rightarrow (N)$                     | N)              |               |

| Status Affected:  | Z               |                                           |                 |               |

| Encoding:         | 11              | 1010                                      | kkkk            | kkkk          |

| Description:      | XOR'ed v        | ents of the<br>vith the ei<br>t is placed | ght bit lite    | ral 'k'.      |

| Words:            | 1               |                                           |                 |               |

| Cycles:           | 1               |                                           |                 |               |

| Q Cycle Activity: | Q1              | Q2                                        | Q3              | Q4            |

|                   | Decode          | Read<br>literal 'k'                       | Process<br>data | Write to<br>W |

| Example:          | XORLW           | 0xAF                                      |                 |               |

|                   | Before I        | nstructio                                 | n               |               |

|                   |                 | W =                                       | 0xB5            |               |

|                   | After Ins       | truction                                  |                 |               |

|                   |                 | W =                                       | 0x1A            |               |

|                   |                 |                                           |                 |               |

| XORWF             | Exclusiv                                                         | e OR W                   | with f                         |                     |

|-------------------|------------------------------------------------------------------|--------------------------|--------------------------------|---------------------|

| Syntax:           | [label]                                                          | XORWF                    | f,d                            |                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                       |                                |                     |

| Operation:        | (W) .XOF                                                         | $R.\left(f\right)\to($   | dest)                          |                     |

| Status Affected:  | Z                                                                |                          |                                |                     |

| Encoding:         | 00                                                               | 0110                     | dfff                           | ffff                |

| Description:      | Exclusive<br>register wi<br>result is st<br>is 1 the res         | th registe<br>ored in th | r 'f'. If 'd' is<br>e W regist | o the<br>er. If 'd' |

| Words:            | 1                                                                |                          |                                |                     |

| Cycles:           | 1                                                                |                          |                                |                     |

| Q Cycle Activity: | Q1                                                               | Q2                       | Q3                             | Q4                  |

|                   | Decode                                                           | Read<br>register<br>'f'  | Process<br>data                | Write to<br>dest    |

| Example           | XORWF                                                            | REG                      | 1                              |                     |

|                   | Before In                                                        | struction                | 1                              |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | AF<br>B5            |

|                   | After Inst                                                       | ruction                  |                                |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | 1A<br>B5            |

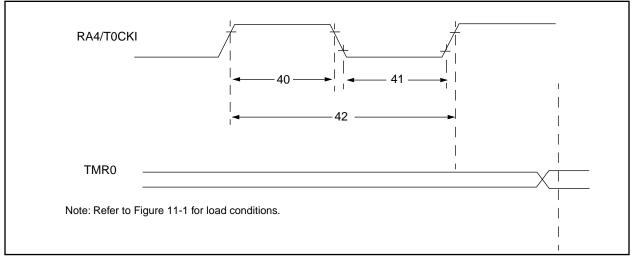

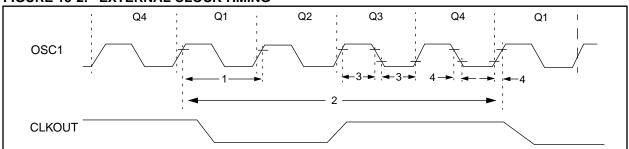

### FIGURE 11-6: TIMER0 EXTERNAL CLOCK TIMINGS

#### TABLE 11-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                    |                | Min                                            | Тур† | Max   | Units | Conditions                         |

|--------------|-----------|---------------------------------------------------|----------------|------------------------------------------------|------|-------|-------|------------------------------------|

| 40           | Tt0H      | T0CKI High Pulse Width                            | No Prescaler   | 0.5Tcy + 20*                                   | —    |       | ns    | Must also meet                     |

|              |           |                                                   | With Prescaler | 10*                                            | —    | _     | ns    | parameter 42                       |

| 41           | Tt0L      | T0CKI Low Pulse Width                             | No Prescaler   | 0.5TCY + 20*                                   | —    | _     | ns    | Must also meet                     |

|              |           |                                                   | With Prescaler | 10*                                            | —    | -     | ns    | parameter 42                       |

| 42           | Tt0P      | T0CKI Period                                      |                | Greater of:<br>20 ns or <u>Tcy + 40</u> *<br>N | _    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 48           | Tcke2tmrl | Delay from external clock edge to timer increment |                | 2Tosc                                          | —    | 7Tosc | —     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

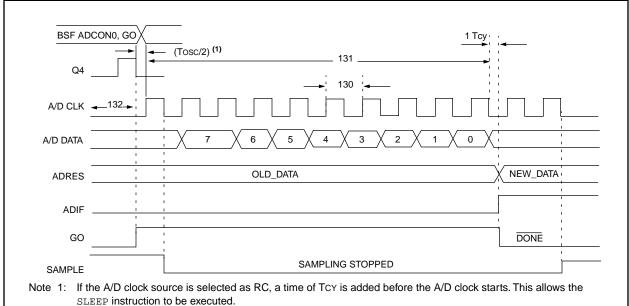

### FIGURE 11-7: A/D CONVERSION TIMING

#### **TABLE 11-7: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                                        |                                 | Min    | Тур†    | Max | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|-------------------------------------------------------|---------------------------------|--------|---------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                      | PIC16 <b>C</b> 710/711          | 1.6    | _       | _   | μs    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                               |

|              |      |                                                       | PIC16LC710/711                  | 2.0    | _       | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                                |