Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 36 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                     |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c710t-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

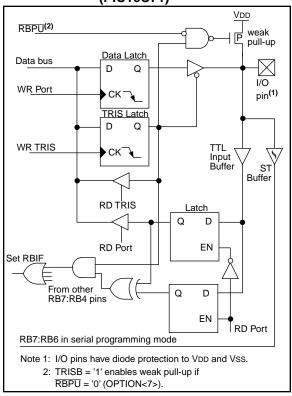

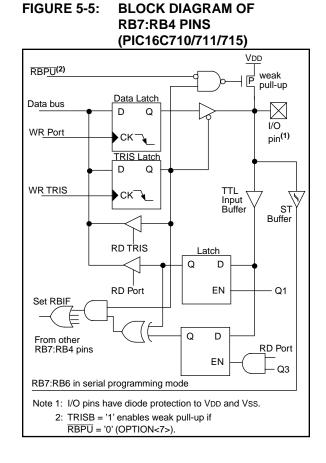

#### FIGURE 5-4: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C71)

#### TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 7.4 <u>A/D Conversions</u>

Example 7-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0). **Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 7-2: A/D CONVERSION

| BSF    | STATUS,     | RP0        | ; Select Bank 1                                          |

|--------|-------------|------------|----------------------------------------------------------|

| CLRF   | ADCON1      |            | ; Configure A/D inputs                                   |

| BCF    | STATUS,     | RP0        | ; Select Bank 0                                          |

| MOVL   | W 0xCl      |            | ; RC Clock, A/D is on, Channel 0 is selected             |

| MOVW   | F ADCON0    |            | ;                                                        |

| BSF    | INTCON,     | ADIE       | ; Enable A/D Interrupt                                   |

| BSF    | INTCON,     | GIE        | ; Enable all interrupts                                  |

|        |             |            |                                                          |

| Ensure | that the re | equired sa | ampling time for the selected input channel has elapsed. |

Then the conversion may be started.

;

;;

;

| BSF | ADCON0, GO | ; Start A/D Conversion                              |

|-----|------------|-----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit      |

| :   |            | ; is cleared upon completion of the A/D Conversion. |

#### FIGURE 8-2: CONFIGURATION WORD, PIC16C710/711

| CP0 C                      | P0 CI                                      | P0 CP0                                                                           | CP0                                   | CP0     | CP0     | BODEN | CP0     | CP0      | PWRTE    | WDTE   | FOSC1 | FOSC0 | Register:      | CONFIG |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------|---------|-------|---------|----------|----------|--------|-------|-------|----------------|--------|

| bit13                      |                                            | •                                                                                |                                       |         |         |       |         |          |          |        |       | bit0  | Address        | 2007h  |

| bit 13-7<br>5-4:<br>bit 6: | 1 = Co<br>0 = All<br><b>BODE</b><br>1 = BC | Code prote<br>ode protec<br>memory<br><b>N:</b> Brown<br>OR enable<br>OR disable | ction off<br>is code<br>-out Re<br>ed | protec  |         |       | Fh is w | vritable |          |        |       |       |                |        |

| bit 3:                     | 1 = PV                                     | <b>Ē:</b> Power<br>VRT disal<br>VRT enat                                         | bled                                  | er Ena  | ble bit | (1)   |         |          |          |        |       |       |                |        |

| bit 2:                     | 1 = W                                      | : Watchd<br>DT enable<br>DT disabl                                               | ed                                    | er Enab | le bit  |       |         |          |          |        |       |       |                |        |

| bit 1-0:                   | 11 = F<br>10 = F<br>01 = X                 | 1:FOSC0<br>RC oscilla<br>IS oscillat<br>(T oscillat<br>P oscillat                | tor<br>tor<br>tor                     | ator Se | lection | bits  |         |          |          |        |       |       |                |        |

| Note 1:                    | Ensur                                      | e the Pow                                                                        | er-up T                               | imer is | enable  |       | ne Brov | vn-out l | Reset is | enable | d.    |       | value of bit F | PWRTE. |

#### 2: All of the CP0 bits have to be given the same value to enable the code protection scheme listed.

#### FIGURE 8-3: CONFIGURATION WORD, PIC16C715

| CP1             | CP0               | CP1                                           | CP0                           | CP1                           | CP0                    | MPEEN                               | BODEN                  | CP1    | CP0   | PWRTE     | WDTE     | FOSC1    | FOSC0      | Register:    | CONFIG |

|-----------------|-------------------|-----------------------------------------------|-------------------------------|-------------------------------|------------------------|-------------------------------------|------------------------|--------|-------|-----------|----------|----------|------------|--------------|--------|

| bit13           |                   |                                               |                               |                               |                        |                                     |                        |        |       |           |          |          | bit0       | Address      | 2007h  |

| bit 13-8<br>5-4 | 4: 11<br>10<br>01 | L = Up                                        | de prot<br>per hal<br>per 3/4 | ection<br>f of pro<br>th of p | off<br>ogram<br>rogran | memory                              | r code pr<br>ry code p |        |       |           |          |          |            |              |        |

| bit 7:          | 1                 | = Mem                                         | ory Pa                        | rity Ch                       | ecking                 | or Enabl<br>g is enat<br>g is disal | oled                   |        |       |           |          |          |            |              |        |

| bit 6:          | 1                 | <b>oden</b> :<br>= Bor<br>= Bor               | enable                        | ed                            | Reset E                | Enable b                            | <sub>it</sub> (1)      |        |       |           |          |          |            |              |        |

| bit 3:          | 1                 | <b>WRTE</b> :<br>= PWF<br>= PWF               | RT disa                       | bled                          | mer Ei                 | nable bit                           | (1)                    |        |       |           |          |          |            |              |        |

| bit 2:          | 1                 | <b>DTE:</b> \<br>= WDT<br>= WDT               | enabl                         | ed                            | ner En                 | able bit                            |                        |        |       |           |          |          |            |              |        |

| bit 1-0         | 11<br>10<br>01    | DSC1:<br>L = RC<br>D = HS<br>L = XT<br>D = LP | oscilla<br>oscilla<br>oscilla | ator<br>itor<br>tor           | llator \$              | Selectior                           | n bits                 |        |       |           |          |          |            |              |        |

| Note 7          |                   |                                               |                               |                               |                        |                                     | cally ena<br>ed anytir |        | •     |           | ,        | 0        | ess of the | value of bit | PWRTE. |

|                 | 2: Al             | l of the                                      | CP1:0                         | CP0 pa                        | airs ha                | ve to be                            | given the              | e same | value | to enable | e the co | de prote | ection sch | eme listed.  |        |

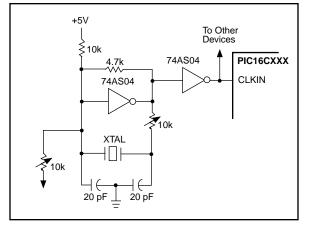

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 8-6 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 8-6: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

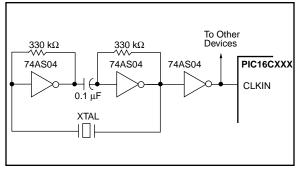

Figure 8-7 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 8-7: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

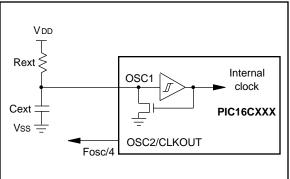

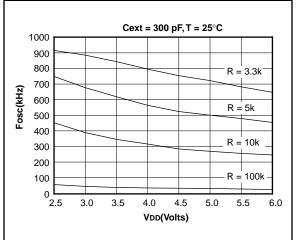

#### 8.2.4 RC OSCILLATOR

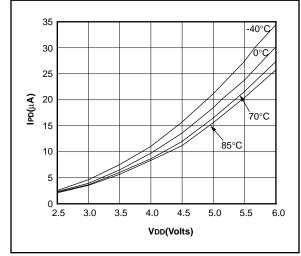

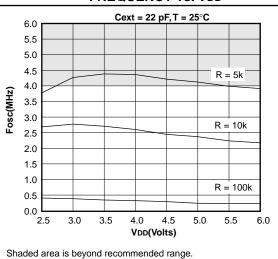

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 8-8 shows how the R/C combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

#### FIGURE 8-8: RC OSCILLATOR MODE

| Register | Power-on Reset,<br>Brown-out Reset<br>Parity Error Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|----------|----------------------------------------------------------|--------------------------|------------------------------------|

| W        | XXXX XXXX                                                | นนนน นนนน                | นนนน นนนน                          |

| INDF     | N/A                                                      | N/A                      | N/A                                |

| TMR0     | xxxx xxxx                                                | <u>uuuu</u> uuuu         | uuuu uuuu                          |

| PCL      | 0000 0000                                                | 0000 0000                | PC + 1(2)                          |

| STATUS   | 0001 1xxx                                                | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR      | xxxx xxxx                                                | uuuu uuuu                | uuuu uuuu                          |

| PORTA    | x 0000                                                   | u 0000                   | u uuuu                             |

| PORTB    | XXXX XXXX                                                | uuuu uuuu                | uuuu uuuu                          |

| PCLATH   | 0 0000                                                   | 0 0000                   | u uuuu                             |

| INTCON   | 0000 000x                                                | 0000 000u                | uuuu uuuu(1)                       |

| PIR1     | -0                                                       | -0                       | _ <sub>u</sub> _(1)                |

| ADCON0   | 0000 00-0                                                | 0000 00-0                | uuuu uu-u                          |

| OPTION   | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| TRISA    | 1 1111                                                   | 1 1111                   | u uuuu                             |

| TRISB    | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| PIE1     | -0                                                       | -0                       | -u                                 |

| PCON     | वेर्वेवे                                                 | luu                      | luu                                |

| ADCON1   | 00                                                       | 00                       |                                    |

#### TABLE 8-13: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C715

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-11 for reset value for specific condition.

#### 9.1 Instruction Descriptions

|                   |                                                                           | •                   | _               |               |

|-------------------|---------------------------------------------------------------------------|---------------------|-----------------|---------------|

| ADDLW             | Add Lite                                                                  | ral and \           | N               |               |

| Syntax:           | [ <i>label</i> ] Al                                                       | DDLW                | k               |               |

| Operands:         | $0 \le k \le 25$                                                          | 55                  |                 |               |

| Operation:        | (W) + k –                                                                 | → (W)               |                 |               |

| Status Affected:  | C, DC, Z                                                                  |                     |                 |               |

| Encoding:         | 11                                                                        | 111x                | kkkk            | kkkk          |

| Description:      | The conter<br>added to the<br>result is pla                               | ne eight b          | it literal 'k'  | and the       |

| Words:            | 1                                                                         |                     |                 |               |

| Cycles:           | 1                                                                         |                     |                 |               |

| Q Cycle Activity: | Q1                                                                        | Q2                  | Q3              | Q4            |

|                   | Decode                                                                    | Read<br>literal 'k' | Process<br>data | Write to<br>W |

| Example:          | After Inst                                                                | W =                 | 0x10<br>0x25    |               |

| ADDWF             | Add W a                                                                   | nd f                |                 |               |

| Syntax:           | [ <i>label</i> ] Al                                                       | DDWF                | f,d             |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$ | 7                   |                 |               |

| Operation:        | (W) + (f) -                                                               | ightarrow (dest)    |                 |               |

| Status Affected:  | C, DC, Z                                                                  |                     |                 |               |

| Encoding:         | 00                                                                        | 0111                | dfff            | ffff          |

| Description:      | Add the co<br>with regist<br>stored in th                                 | er 'f'. If 'd'      | is 0 the re     | sult is       |

| Encoding:         | 00                                                        | 0111                        | dfff                           | ffff               |

|-------------------|-----------------------------------------------------------|-----------------------------|--------------------------------|--------------------|

| Description:      | Add the co<br>with regist<br>stored in th<br>result is st | er 'f'. If 'd'<br>he W regi | is 0 the re<br>ster. If 'd' is | sult is<br>s 1 the |

| Words:            | 1                                                         |                             |                                |                    |

| Cycles:           | 1                                                         |                             |                                |                    |

| Q Cycle Activity: | Q1                                                        | Q2                          | Q3                             | Q4                 |

|                   | Decode                                                    | Read<br>register<br>'f'     | Process<br>data                | Write to<br>Dest   |

| Example           | ADDWF                                                     | FSR,                        | 0                              |                    |

|                   | Before In                                                 |                             |                                |                    |

|                   |                                                           | W =<br>FSR =                | 0x17<br>0xC2                   |                    |

|                   | After Inst                                                |                             | 0                              |                    |

|                   |                                                           | W =<br>FSR =                | 0xD9<br>0xC2                   |                    |

| ANDLW             | AND Lite                           | eral with              | w               |               |

|-------------------|------------------------------------|------------------------|-----------------|---------------|

| Syntax:           | [ <i>label</i> ] A                 | NDLW                   | k               |               |

| Operands:         | $0 \le k \le 2$                    | 55                     |                 |               |

| Operation:        | (W) .ANE                           | D. (k) $\rightarrow$ ( | W)              |               |

| Status Affected:  | Z                                  |                        |                 |               |

| Encoding:         | 11                                 | 1001                   | kkkk            | kkkk          |

| Description:      | The conte<br>AND'ed wiresult is pl | ith the eig            | ht bit litera   | 'k'.The       |

| Words:            | 1                                  |                        |                 |               |

| Cycles:           | 1                                  |                        |                 |               |

| Q Cycle Activity: | Q1                                 | Q2                     | Q3              | Q4            |

|                   | Decode                             | Read<br>literal "k"    | Process<br>data | Write to<br>W |

| Example           | ANDLW                              | 0x5F                   |                 |               |

|                   | Before In                          | struction              | 0xA3            |               |

|                   | After Inst                         | •• –                   | UXAU            |               |

|                   |                                    | = W                    | 0x03            |               |

|                   |                                    |                        |                 |               |

| ANDWF             | AND W v                        | vith f                                  |                                              |                  |

|-------------------|--------------------------------|-----------------------------------------|----------------------------------------------|------------------|

| Syntax:           | [ <i>label</i> ] A             | NDWF                                    | f,d                                          |                  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$ | .7                                      |                                              |                  |

| Operation:        | (W) .ANE                       | D. (f) $\rightarrow$ (c                 | dest)                                        |                  |

| Status Affected:  | Z                              |                                         |                                              |                  |

| Encoding:         | 00                             | 0101                                    | dfff                                         | ffff             |

| Description:      | 'd' is 0 the                   | result is a 'd' is 1 the                | with regist<br>stored in th<br>e result is s | ie W             |

| Words:            | 1                              |                                         |                                              |                  |

| Cycles:           | 1                              |                                         |                                              |                  |

| Q Cycle Activity: | Q1                             | Q2                                      | Q3                                           | Q4               |

|                   | Decode                         | Read<br>register<br>'f'                 | Process<br>data                              | Write to<br>Dest |

| Example           | ANDWF                          | FSR,                                    | 1                                            |                  |

|                   | Before In                      |                                         |                                              |                  |

|                   | After Inst                     | W =<br>FSR =<br>ruction<br>W =<br>FSR = | 0x17<br>0xC2<br>0x17<br>0x02                 |                  |

| COMF                                                              | Complement f                                                                                                                                                                | DECFSZ            | Decreme                                 | ent f, Sk                                     | ip if 0                                                                     |                  |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|------------------|

| Syntax:                                                           | [ label ] COMF f,d                                                                                                                                                          | Syntax:           | [ label ]                               | DECFS                                         | Z f,d                                                                       |                  |

| Operands:                                                         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                  | Operands:         | 0 ≤ f ≤ 12<br>d ∈ [0,1]                 | 27                                            |                                                                             |                  |

| Operation:                                                        | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         | Operation:        | (f) - 1 $ ightarrow$                    | (dest);                                       | skip if re                                                                  | sult = 0         |

| Status Affected:                                                  | Z                                                                                                                                                                           | Status Affected:  | None                                    |                                               |                                                                             |                  |

| Encoding:                                                         | 00 1001 dfff ffff                                                                                                                                                           | Encoding:         | 00                                      | 1011                                          | dfff                                                                        | ffff             |

| Description:                                                      | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>W. If 'd' is 1 the result is stored back in<br>register 'f'.                     | Description:      | mented. If<br>the W regin<br>placed bac | 'd' is 0 the<br>ster. If 'd' i<br>k in regist | ster 'f' are d<br>result is pla<br>s 1 the resu<br>ter 'f'.<br>next instruc | aced in<br>It is |

| Words:<br>Cycles:                                                 | 1<br>1                                                                                                                                                                      |                   | executed.                               | f the resul                                   | t is 0, then a king it a 2T                                                 | a NOP is         |

| Q Cycle Activity:                                                 | Q1 Q2 Q3 Q4                                                                                                                                                                 | Words:            | 1                                       |                                               |                                                                             |                  |

|                                                                   | Decode Read Process Write to register data dest                                                                                                                             | Cycles:           | 1(2)                                    |                                               |                                                                             |                  |

|                                                                   | 'f' data dest                                                                                                                                                               | Q Cycle Activity: | Q1                                      | Q2                                            | Q3                                                                          | Q4               |

| Example                                                           | COMF REG1,0                                                                                                                                                                 |                   | Decode                                  | Read<br>register<br>'f'                       | Process<br>data                                                             | Write to<br>dest |

|                                                                   | Before Instruction<br>REG1 = 0x13                                                                                                                                           | If Skip:          | (and Cur                                |                                               |                                                                             |                  |

|                                                                   | After Instruction                                                                                                                                                           | li Skip.          | (2nd Cyc<br>Q1                          | Q2                                            | Q3                                                                          | Q4               |

|                                                                   | $\begin{array}{rcl} REG1 &=& 0x13\\ W &=& 0xEC \end{array}$                                                                                                                 |                   | NOP                                     | NOP                                           | NOP                                                                         | NOP              |

| DECF                                                              | Decrement f                                                                                                                                                                 | Example           | HERE                                    | DECF                                          |                                                                             | , 1              |

| Syntax:                                                           | [ <i>label</i> ] DECF f,d                                                                                                                                                   |                   | CONTIN                                  | GOTC<br>UE •                                  | LOC                                                                         | P                |

| Operands:                                                         | $0 \le f \le 127$<br>d \equiv [0,1]                                                                                                                                         |                   |                                         | •                                             |                                                                             |                  |

| Operation:                                                        | (f) - 1 $\rightarrow$ (dest)                                                                                                                                                |                   | Before Ir<br>PC                         |                                               | ר<br>dress here                                                             |                  |

| Status Affected:                                                  | Z                                                                                                                                                                           |                   | After Inst                              |                                               | UIC33 HERE                                                                  |                  |

| Encoding:                                                         | 00 0011 dfff ffff                                                                                                                                                           |                   | CNT<br>if CNT                           |                                               | IT - 1                                                                      |                  |

| Decerintien                                                       | Decrement register 'f'. If 'd' is 0 the                                                                                                                                     |                   | PC<br>if CN1                            | = ad                                          | dress CON                                                                   | TINUE            |

| Description:                                                      | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'.                                 |                   | PC                                      | = ad                                          | dress heri                                                                  | 5+1              |

| ·                                                                 | result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'.<br>1                                                                       |                   |                                         | = ad                                          | dress heri                                                                  | 5+1              |

| Words:                                                            | 'f'.                                                                                                                                                                        |                   |                                         | = ad                                          | dress heri                                                                  | 5+1              |

| Words:<br>Cycles:                                                 | т.<br>1                                                                                                                                                                     |                   |                                         | = ad                                          | dress heri                                                                  | 2+1              |

| Words:<br>Cycles:                                                 | Ψ.<br>1<br>1                                                                                                                                                                |                   |                                         | = ad                                          | dress heri                                                                  | 2+1              |

| Words:<br>Cycles:<br>Q Cycle Activity:                            | <ul> <li>f.</li> <li>1</li> <li>1</li> <li>Q1 Q2 Q3 Q4</li> <li>Decode Read Process Write to dest dest</li> </ul>                                                           |                   |                                         | = ad                                          | dress heri                                                                  | 5+1              |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>Example | <ul> <li>Process</li> <li>Process</li> <li>Decode</li> <li>Read<br/>register</li> <li>'f'</li> <li>Process</li> <li>Write to<br/>data</li> <li>Write to<br/>dest</li> </ul> |                   |                                         | = ad                                          | dress heri                                                                  | 6+1              |

#### 10.0 DEVELOPMENT SUPPORT

#### 10.1 <u>Development Tools</u>

The PICmicro<sup>™</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

#### 10.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 10.3 ICEPIC: Low-Cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

|         |                                            | Standard Operating Conditions (unless otherwise stated)                            |           |      |       |          |                                                                         |  |  |  |  |

|---------|--------------------------------------------|------------------------------------------------------------------------------------|-----------|------|-------|----------|-------------------------------------------------------------------------|--|--|--|--|

|         |                                            | Operati                                                                            | ng temper | atur |       | ,<br>≤ T | $A \leq +70^{\circ}C$ (commercial)                                      |  |  |  |  |

|         |                                            |                                                                                    | •         |      | -40°0 |          | A ≤ +85°C (industrial)                                                  |  |  |  |  |

| DC CHAP | RACTERISTICS                               | -40°C $\leq$ TA $\leq$ +125°C (extended)                                           |           |      |       |          |                                                                         |  |  |  |  |

|         |                                            | Operating voltage VDD range as described in DC spec Section 11.1 and Section 11.2. |           |      |       |          |                                                                         |  |  |  |  |

| Param   | Characteristic                             | Sym                                                                                | Min       | Тур  | Max   | Units    | Conditions                                                              |  |  |  |  |

| No.     |                                            | - C.J                                                                              |           | t    | max   | 0        |                                                                         |  |  |  |  |

|         | Output Low Voltage                         |                                                                                    |           | -    |       |          |                                                                         |  |  |  |  |

| D080    | I/O ports                                  | Vol                                                                                | -         | -    | 0.6   | V        | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |  |  |  |

| D080A   |                                            |                                                                                    | -         | -    | 0.6   | V        | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |  |  |

| D083    | OSC2/CLKOUT (RC osc config)                |                                                                                    | -         | -    | 0.6   | V        | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |  |  |  |

| D083A   |                                            |                                                                                    | -         | -    | 0.6   | V        | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |  |  |

|         | Output High Voltage                        |                                                                                    |           |      |       |          |                                                                         |  |  |  |  |

| D090    | I/O ports (Note 3)                         | Vон                                                                                | Vdd - 0.7 | -    | -     | V        | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |  |

| D090A   |                                            |                                                                                    | Vdd - 0.7 | -    | -     | V        | ІОН = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |  |

| D092    | OSC2/CLKOUT (RC osc config)                |                                                                                    | Vdd - 0.7 | -    | -     | V        | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |  |

| D092A   |                                            |                                                                                    | Vdd - 0.7 | -    | -     | V        | ІОН = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |  |

| D130*   | Open-Drain High Voltage                    | Vod                                                                                | -         | -    | 14    | V        | RA4 pin                                                                 |  |  |  |  |

|         | Capacitive Loading Specs on<br>Output Pins |                                                                                    |           |      |       |          |                                                                         |  |  |  |  |

| D100    | OSC2 pin                                   | Cosc2                                                                              | -         | -    | 15    | pF       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |  |

| D101    | All I/O pins and OSC2 (in RC mode)         | Сю                                                                                 | -         | -    | 50    | pF       |                                                                         |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

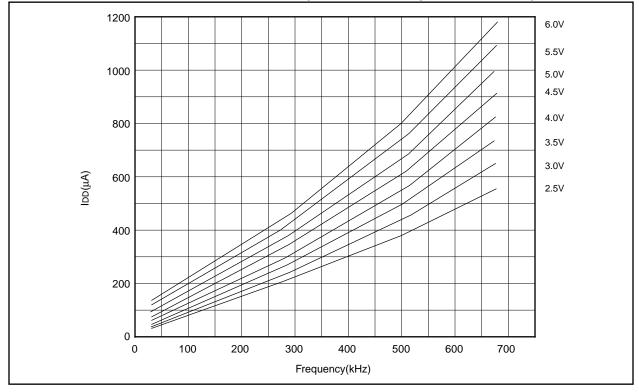

#### FIGURE 12-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### FIGURE 12-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

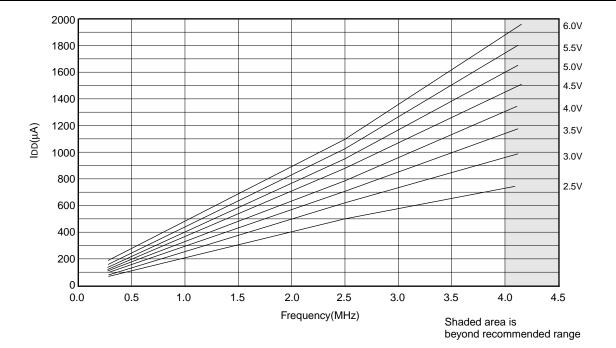

#### FIGURE 12-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

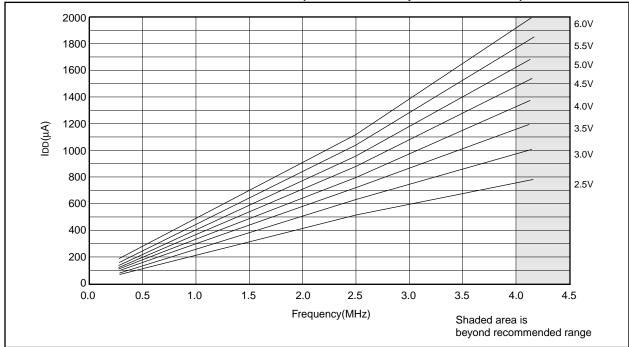

#### FIGURE 12-13: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 22 pF, -40°C TO 85°C)

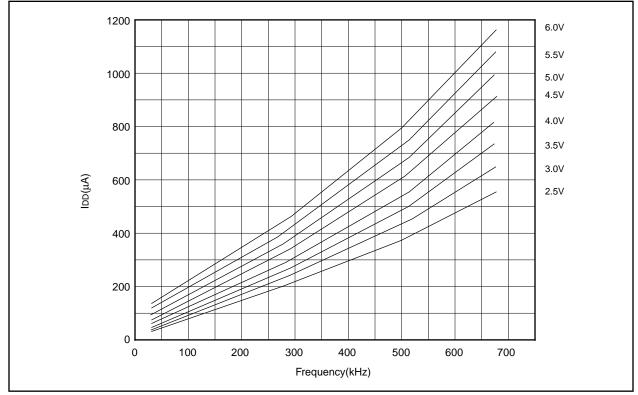

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

## PIC16C71X

#### Applicable Devices71071711715

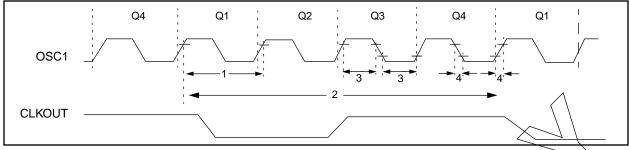

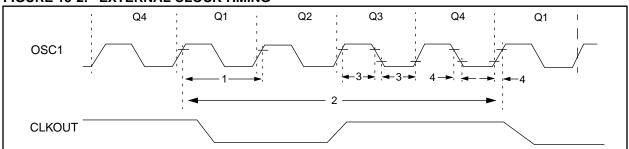

#### 13.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 13-2: EXTERNAL CLOCK TIMING

#### TABLE 13-2: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym       | Characteristic                  | Min | Тур†                     | Мах      | Units | Conditions                 |

|------------------|-----------|---------------------------------|-----|--------------------------|----------|-------|----------------------------|

|                  | Fos       | External CLKIN Frequency        | DC  | _                        | 4        | MHz   | XT osc mode                |

|                  |           | (Note 1)                        | DC  | _                        | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |           |                                 | DC  | _                        | 20/      | MHz   | HS osc mode (PIC16C715-20) |

|                  |           |                                 | DC  | _                        | 200      | kHz ` | LP osc mode                |

|                  |           | Oscillator Frequency            | DC  | —                        | 1        | MHz   | RØ osc mode                |

|                  |           | (Note 1)                        | 0.1 |                          | <u> </u> | MHz   | XT osc mode                |

|                  |           |                                 | 4   | $  \langle \rangle$      | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |           |                                 | 4   | $\wedge - \land$         | 10       | MHz   | HS osc mode (PIC16C715-10) |

|                  |           |                                 | 4   | $\langle \not F \rangle$ | 20       | MHz   | HS osc mode (PIC16C715-20) |

|                  |           |                                 | 5   | $\overline{M}$           | 200      | kHz   | LP osc mode                |

| 1                | Tosc      | External CLKIN Period           | 250 | $ \rightarrow $          | _        | ns    | XT osc mode                |

|                  |           | (Note 1)                        | 250 | Ň                        | -        | ns    | HS osc mode (PIC16C715-04) |

|                  |           |                                 | 100 | $ ^{\sim}-$              | _        | ns    | HS osc mode (PIC16C715-10) |

|                  |           |                                 | 50  | _                        | —        | ns    | HS osc mode (PIC16C715-20) |

|                  |           |                                 | 5   | _                        | —        | μs    | LP osc mode                |

|                  |           | Oscillator Períod               | 250 | —                        | —        | ns    | RC osc mode                |

|                  |           | (Note 1)                        | 250 | _                        | 10,000   | ns    | XT osc mode                |

|                  |           |                                 | 250 | _                        | 250      | ns    | HS osc mode (PIC16C715-04) |

|                  | /         | $\square \setminus \vee /$      | 100 | —                        | 250      | ns    | HS osc mode (PIC16C715-10) |

|                  |           | $\langle \rangle \leq \vee$     | 50  | _                        | 250      | ns    | HS osc mode (PIC16C715-20) |

|                  |           | $\sim$                          | 5   | _                        | _        | μs    | LP osc mode                |

| 2                | TGY       | Instruction Cycle Time (Note 1) | 200 | _                        | DC       | ns    | Tcy = 4/Fosc               |

| 3                | TosL,     | External Clock in (OSC1) High   | 50  | —                        | —        | ns    | XT oscillator              |

| $\setminus$      | TosH      | or Low Time                     | 2.5 | —                        | —        | μs    | LP oscillator              |

| $\searrow$       | $\langle$ |                                 | 10  | _                        | —        | ns    | HS oscillator              |

| 4                | TosR,     | External Clock in (OSC1) Rise   | _   | —                        | 25       | ns    | XT oscillator              |

|                  | TosF      | or Fall Time                    | —   | _                        | 50       | ns    | LP oscillator              |

|                  |           |                                 | _   | _                        | 15       | ns    | HS oscillator              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C715.

# TABLE 13-6:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C715-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C715-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C715-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Parameter<br>No. | Sym  | Characteristic                                       | Min       | Тур†       | Мах                   | Units                       | Conditions                                           |

|------------------|------|------------------------------------------------------|-----------|------------|-----------------------|-----------------------------|------------------------------------------------------|

|                  | Nr   | Resolution                                           | _         | _          | 8-bits                | _                           | $VREF=VDD,VSS\leqAin\leqVREF$                        |

|                  | Nint | Integral error                                       | _         | _          | less than<br>±1 LSb   | —                           | $VREF = VDD, VSS \le AIN \le VREF$                   |

|                  | Ndif | Differential error                                   | _         | _          | less than<br>±1 LSb   | —                           | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|                  | NFS  | Full scale error                                     | _         |            | less than<br>±1 LSb   | _                           | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|                  | Noff | Offset error                                         | _         | _          | less than<br>±1 LSb   | —                           | VREF = VDØ, VSS ≤ AIN ≤ VREF                         |

|                  | _    | Monotonicity                                         | _         | guaranteed | _                     | _                           | VSS S AIN S VREF                                     |

|                  | Vref | Reference voltage                                    | 2.5V      | _          | Vdd + 0.3             | V                           |                                                      |

|                  | VAIN | Analog input voltage                                 | Vss - 0.3 |            | Vref + 0.3            | V                           |                                                      |

|                  | ZAIN | Recommended<br>impedance of analog<br>voltage source | _         | _          | 10.0                  | kΩ                          |                                                      |

|                  | IAD  | A/D conversion cur-<br>rent (VDD)                    | _         | 180        | $\overline{\langle }$ | <u></u><br>→<br>A<br>→<br>A | Average current consumption when A/D is on. (Note 1) |

|                  | IREF | VREF input current<br>(Note 2)                       | _         |            | 1                     | μA<br>μA                    | During sampling<br>All other times                   |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

#### Applicable Devices71071711715

#### 15.1 DC Characteristics: PIC16C71-04 (Commercial, Industrial) PIC16C71-20 (Commercial, Industrial)

| DC CH                 | ARACTERISTICS                                                    |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) |                 |                |                |                                                                                                                                                                                            |  |  |

|-----------------------|------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          | Characteristic                                                   | Sym  | Min                                                                                                                                                                                        | Тур†            | Max            | Units          | Conditions                                                                                                                                                                                 |  |  |

| D001<br>D001A         | Supply Voltage                                                   | Vdd  | 4.0<br>4.5                                                                                                                                                                                 |                 | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                    |  |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -                                                                                                                                                                                          | 1.5             | -              | V              |                                                                                                                                                                                            |  |  |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -                                                                                                                                                                                          | Vss             | -              | V              | See section on Power-on Reset for details                                                                                                                                                  |  |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD | 0.05                                                                                                                                                                                       | -               | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                  |  |  |

| D010                  | Supply Current (Note 2)                                          | IDD  | -                                                                                                                                                                                          | 1.8             | 3.3            | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                              |  |  |

| D013                  |                                                                  |      | -                                                                                                                                                                                          | 13.5            | 30             | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                          |  |  |

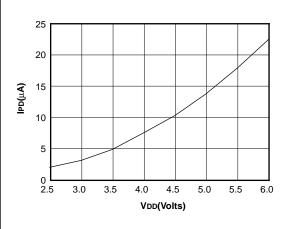

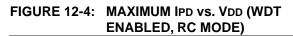

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3)                                   | IPD  |                                                                                                                                                                                            | 7<br>1.0<br>1.0 | 28<br>14<br>16 | μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, $-40^{\circ}$ C to $+85^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-0^{\circ}$ C to $+70^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to $+85^{\circ}$ C |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

# PIC16C71X

#### Applicable Devices 710 71 711 715

#### 15.5 Timing Diagrams and Specifications

#### FIGURE 15-2: EXTERNAL CLOCK TIMING

#### TABLE 15-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units | Conditions        |

|------------------|-------|----------------------------------|-----|------|--------|-------|-------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT osc mode       |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04) |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20) |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode       |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode       |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode       |

|                  |       |                                  | 1   | _    | 4      | MHz   | HS osc mode       |

|                  |       |                                  | 1   | —    | 20     | MHz   | HS osc mode       |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | —      | ns    | XT osc mode       |

|                  |       | (Note 1)                         | 250 | _    | —      | ns    | HS osc mode (-04) |

|                  |       |                                  | 50  | _    | —      | ns    | HS osc mode (-20) |

|                  |       |                                  | 5   | —    | _      | μs    | LP osc mode       |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode       |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode       |

|                  |       |                                  | 250 | _    | 1,000  | ns    | HS osc mode (-04) |

|                  |       |                                  | 50  | _    | 1,000  | ns    | HS osc mode (-20) |

|                  |       |                                  | 5   | _    | —      | μs    | LP osc mode       |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 1.0 | Тсү  | DC     | μs    | TCY = 4/Fosc      |

| 3                | TosL, | External Clock in (OSC1) High or | 50  | _    | —      | ns    | XT oscillator     |

|                  | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator     |

|                  |       |                                  | 10  | —    | —      | ns    | HS oscillator     |

| 4                | TosR, | External Clock in (OSC1) Rise or | 25  | —    | —      | ns    | XT oscillator     |

|                  | TosF  | Fall Time                        | 50  | —    | —      | ns    | LP oscillator     |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator     |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C71.

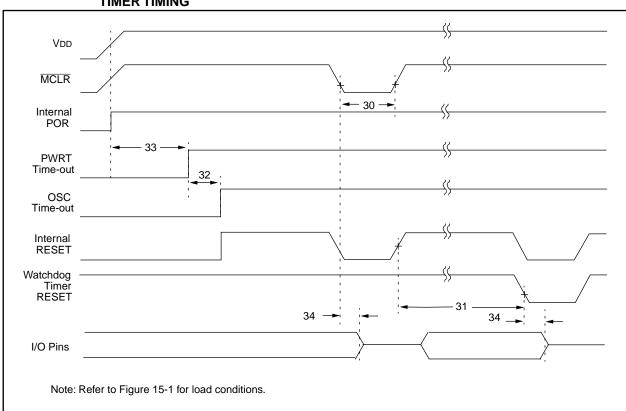

## FIGURE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 15-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†      | Мах  | Units | Conditions               |

|------------------|-------|--------------------------------------------------|-----|-----------|------|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 200 | —         | _    | ns    | VDD = 5V, -40°C to +85°C |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*  | 18        | 33*  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | _   | 1024 Tosc | -    | —     | Tosc = OSC1 period       |

| 33               | Tpwrt | Power-up Timer Period                            | 28* | 72        | 132* | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O High Impedance from MCLR<br>Low              | —   | —         | 100  | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### **APPENDIX A:**

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (1K now as opposed to 512 before) and register file (68 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- 9. Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

#### APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

#### **APPENDIX C: WHAT'S NEW**

1. Consolidated all pin compatible 18-pin A/D based devices into one data sheet.

#### **APPENDIX D: WHAT'S CHANGED**

- 1. Minor changes, spelling and grammatical changes.

- 2. Low voltage operation on the PIC16LC710/711/ 715 has been reduced from 3.0V to 2.5V.

- 3. Part numbers of the PIC16C70 and PIC16C71A have changed to PIC16C710 and PIC16C711, respectively.

NOTES: