Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 68 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

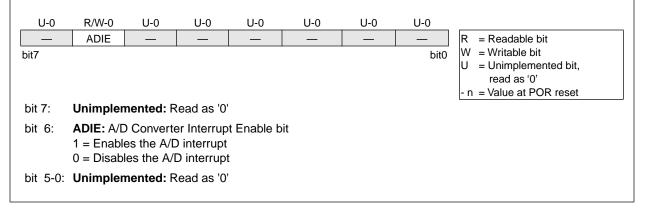

#### 4.2.2.4 PIE1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual enable bits for the Peripheral interrupts.

#### FIGURE 4-10: PIE1 REGISTER (ADDRESS 8Ch)

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

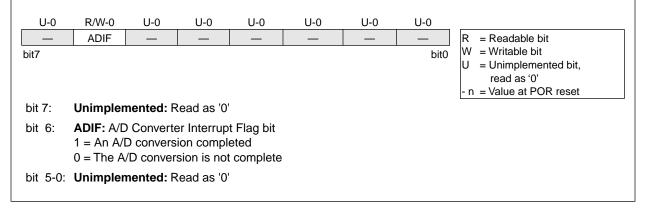

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

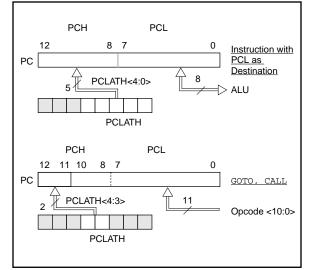

#### 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-14 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-14: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc- | Note 1: | There are no status bits to indicate stack overflow or stack underflow conditions.                                                                                   |

|----------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  | Note 2: | called PUSH or POP. These are actions<br>that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc-<br>tions, or the vectoring to an interrupt |

#### 4.4 <u>Program Memory Paging</u>

The PIC16C71X devices ignore both paging bits (PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC16C71X is not recommended since this may affect upward compatibility with future products.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution. **Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

BCFSTATUS, RP0;Bank 0CLRFTMR0;Clear TMR0 & PrescalerBSFSTATUS, RP0;Bank 1CLRWDT;Clears WDTMOVLWb'xxxxlxxx';Selects new prescale valueMOVWFOPTION\_REG;and assigns the prescaler to the WDTBCFSTATUS, RP0;Bank 0

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT → TIMER0)

| CLRWDT |             | ;Clear WDT and prescaler             |

|--------|-------------|--------------------------------------|

| BSF    | STATUS, RPO | ;Bank 1                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new prescale value and |

| MOVWF  | OPTION_REG  | ;clock source                        |

| BCF    | STATUS, RPO | ;Bank 0                              |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address  | Name   | Bit 7  | Bit 6      | Bit 5   | Bit 4   | Bit 3      | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|----------|--------|--------|------------|---------|---------|------------|------------|-------|-------|--------------------------|---------------------------|

| 01h      | TMR0   | Timer0 | module's r | egister |         |            |            |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh, | INTCON | GIE    | ADIE       | TOIE    | INTE    | RBIE       | TOIF       | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h      | OPTION | RBPU   | INTEDG     | T0CS    | TOSE    | PSA        | PS2        | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h      | TRISA  | —      | —          | _       | PORTA D | Data Direc | tion Regis | ster  |       | 1 1111                   | 1 1111                    |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 8.5 Interrupts

#### Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |

|-------------------------------------------------------|

| External interrupt RB0/INT                            |

| TMR0 overflow interrupt                               |

| PORTB change interrupts (pins RB7:RB4)                |

| A/D Interrupt                                         |

| The interrupt control register (INTCON) records indi- |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~                                                                                                                                                                                                                                                                           |                                                                                                                        |                                                                                                                                                                                                                                                                         |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note: For the PIC16C71<br>If an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enable by the user's Interrupt Service Routine (the RETFIE instruction). The events the would cause this to occur are: |                                                                                                                        |                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                             | 1                                                                                                                      | . An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                             | <ol> <li>The program branches to the Interrupt<br/>vector and executes the Interrupt Ser-<br/>vice Routine.</li> </ol> |                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                             | 3                                                                                                                      | . The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts. |  |  |  |  |

|                                                                                                                                                                                                                                                                             |                                                                                                                        | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                              |  |  |  |  |

| LOOP                                                                                                                                                                                                                                                                        | BCF                                                                                                                    | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                             |                                                                                                                        | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                           |  |  |  |  |

|                                                                                                                                                                                                                                                                             | GOTO                                                                                                                   | LOOP ; NO, try again                                                                                                                                                                                                                                                    |  |  |  |  |

:

Yes, continue

with program

flow

# PIC16C71X

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |  |  |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |  |  |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |  |  |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |  |  |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |  |  |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |  |  |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |  |  |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |  |  |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |  |  |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |  |  |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |  |  |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |  |  |

|                   | FLAG_REG = 0xC7<br>After Instruction   | If Skip:          | (2nd Cycle)                                                                   |  |  |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |  |  |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |  |  |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |  |  |

| •                     |      |

|-----------------------|------|

| Before Instruction    |      |

| PC = address          | HERE |

| After Instruction     |      |

| if $FLAG < 1 > = 0$ , |      |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                          |                 |                       |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|--------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                                              | [ <i>label</i> ] BSF f,b |                 |                       |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                              |                          |                 |                       |  |  |  |

| Operation:        | $1 \rightarrow (f < b)$                                                                          | >)                       |                 |                       |  |  |  |

| Status Affected:  | None                                                                                             |                          |                 |                       |  |  |  |

| Encoding:         | 01                                                                                               | 01bb                     | bfff            | ffff                  |  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is            | s set.          | ·                     |  |  |  |

| Words:            | 1                                                                                                |                          |                 |                       |  |  |  |

| Cycles:           | 1                                                                                                |                          |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                       | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'  | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                          |                 |                       |  |  |  |

| INCFSZ            | Increme                                                                                                                                                                                                                                                                                                           | nt f, Skip              | o if O          |               |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|---------------|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | INCFSZ                  | f,d             |               |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | 27                      |                 |               |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (dest), s               | kip if resu     | ult = 0       |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              |                         |                 |               |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                    | dfff            | ffff          |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                         |                 |               |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                         |                 |               |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                         |                 |               |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                      | Q3              | Q4            |  |

|                   | Decode                                                                                                                                                                                                                                                                                                            | Read<br>register<br>'f' | Process<br>data | Write to dest |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                                          | le)                     |                 | •             |  |

|                   | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                  | Q3              | Q4            |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                     | NOP             | NOP           |  |

| Example           | HERE                                                                                                                                                                                                                                                                                                              | INCF:<br>GOTO<br>UE     |                 | NT, 1<br>DOP  |  |

|                   | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE +1                                                                                                                                                  |                         |                 |               |  |

| IORLW             |                 |                     | eral with                                  |               |

|-------------------|-----------------|---------------------|--------------------------------------------|---------------|

| Syntax:           | [ label ]       | IORLW               | K                                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                                            |               |

| Operation:        | (W) .OR.        | $k \rightarrow (W)$ | 1                                          |               |

| Status Affected:  | Z               |                     |                                            |               |

| Encoding:         | 11              | 1000                | kkkk                                       | kkkk          |

| Description:      | OR'ed wit       | h the eigh          | W register<br>t bit literal<br>le W regist | 'k'. The      |

| Words:            | 1               |                     |                                            |               |

| Cycles:           | 1               |                     |                                            |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                                         | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data                            | Write to<br>W |

| Example           | IORLW           | 0x35                |                                            |               |

|                   | Before In       |                     | l                                          |               |

|                   |                 | W =                 | 0x9A                                       |               |

|                   | After Inst      | W =                 | 0xBF                                       |               |

|                   |                 |                     |                                            |               |

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHAF                        | RACTERISTICS                                                      |               |             | ard Ope<br>ing tem       |                    | ire 0°<br>-4         | itions (unless otherwise stated)C $\leq$ TA $\leq$ +70°C (commercial)0°C $\leq$ TA $\leq$ +85°C (industrial)0°C $\leq$ TA $\leq$ +125°C (extended)                                                                                |

|--------------------------------|-------------------------------------------------------------------|---------------|-------------|--------------------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym           | Min         | Тур†                     | Мах                | Units                | Conditions                                                                                                                                                                                                                        |

| D001                           | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0  | -                        | 6.0<br>6.0         | V<br>V               | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -           | 1.5                      | -                  | V                    |                                                                                                                                                                                                                                   |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -           | Vss                      | -                  | V                    | See section on Power-on Reset for details                                                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | Svdd          | 0.05        | -                        | -                  | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                         |

| D005                           | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7         | 4.0                      | 4.3                | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                |

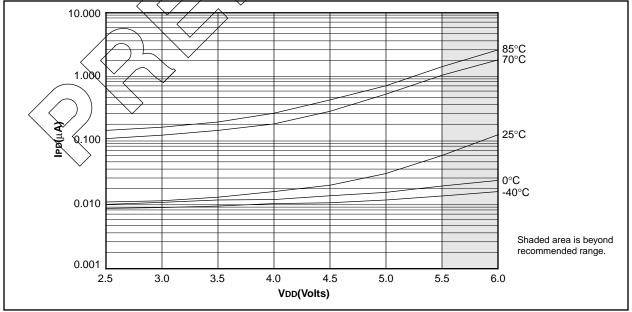

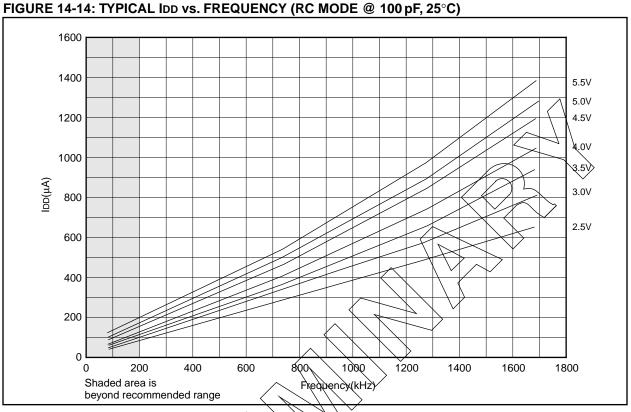

| D010                           | Supply Current<br>(Note 2)                                        | IDD           | -           | 2.0                      | 3.8                | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                     |

| D010A                          |                                                                   |               | -           | 22.5                     | 48                 | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                   |

| D015                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -           | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

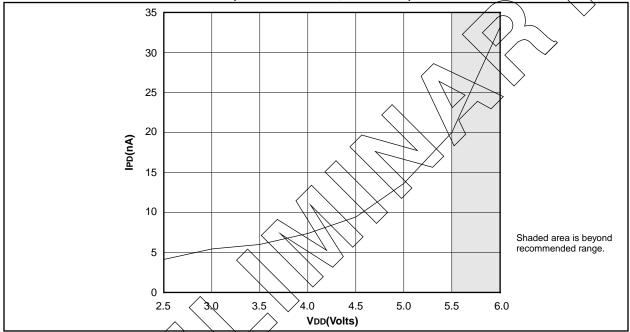

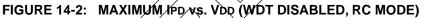

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9<br>0.9 | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |

| D023                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ Ibor | -           | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

#### 1. TppS2ppS

2. TppS

| 2. 1990 |                                      |     |              |  |

|---------|--------------------------------------|-----|--------------|--|

| Т       |                                      |     |              |  |

| F       | Frequency                            | Т   | Time         |  |

| Lowerc  | ase letters (pp) and their meanings: |     |              |  |

| рр      |                                      |     |              |  |

| сс      | CCP1                                 | osc | OSC1         |  |

| ck      | CLKOUT                               | rd  | RD           |  |

| cs      | CS                                   | rw  | RD or WR     |  |

| di      | SDI                                  | sc  | SCK          |  |

| do      | SDO                                  | SS  | SS           |  |

| dt      | Data in                              | tO  | TOCKI        |  |

| io      | I/O port                             | t1  | T1CKI        |  |

| mc      | MCLR                                 | wr  | WR           |  |

| Upperc  | case letters and their meanings:     |     |              |  |

| S       |                                      |     |              |  |

| F       | Fall                                 | P   | Period       |  |

| н       | High                                 | R   | Rise         |  |

| I       | Invalid (Hi-impedance)               | V   | Valid        |  |

| L       | Low                                  | Z   | Hi-impedance |  |

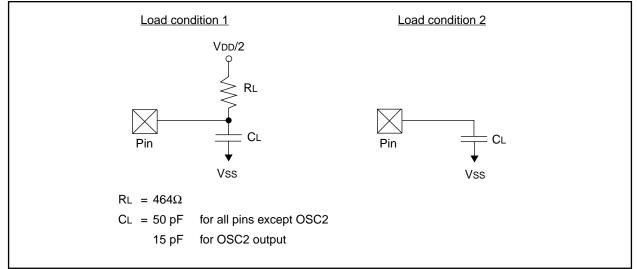

#### FIGURE 11-1: LOAD CONDITIONS

#### 11.5 Timing Diagrams and Specifications

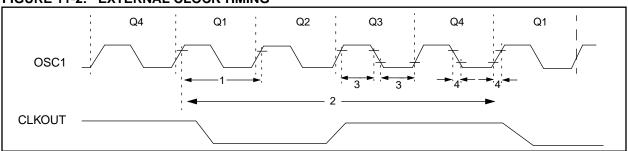

#### FIGURE 11-2: EXTERNAL CLOCK TIMING

#### TABLE 11-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                  | Min       | Тур† | Мах        | Units      | Conditions                             |

|------------------|-------|---------------------------------|-----------|------|------------|------------|----------------------------------------|

|                  | Fosc  | External CLKIN Frequency        | DC        | _    | 4          | MHz        | XT osc mode                            |

|                  |       | (Note 1)                        | DC        | —    | 4          | MHz        | HS osc mode (-04)                      |

|                  |       |                                 | DC        | —    | 10         | MHz        | HS osc mode (-10)                      |

|                  |       |                                 | DC        | —    | 20         | MHz        | HS osc mode (-20)                      |

|                  |       |                                 | DC        | —    | 200        | kHz        | LP osc mode                            |

|                  |       | Oscillator Frequency            | DC        | _    | 4          | MHz        | RC osc mode                            |

|                  |       | (Note 1)                        | 0.1       | —    | 4          | MHz        | XT osc mode                            |

|                  |       |                                 | 4<br>5    | —    | 20<br>200  | MHz<br>kHz | HS osc mode<br>LP osc mode             |

| 1                | Tosc  | External CLKIN Period           | 250       | _    | _          | ns         | XT osc mode                            |

|                  |       | (Note 1)                        | 250       | —    | _          | ns         | HS osc mode (-04)                      |

|                  |       |                                 | 100       | —    | _          | ns         | HS osc mode (-10)                      |

|                  |       |                                 | 50        | —    | _          | ns         | HS osc mode (-20)                      |

|                  |       |                                 | 5         | —    | _          | μs         | LP osc mode                            |

|                  |       | Oscillator Period               | 250       |      | _          | ns         | RC osc mode                            |

|                  |       | (Note 1)                        | 250       | —    | 10,000     | ns         | XT osc mode                            |

|                  |       |                                 | 250       | —    | 250        | ns         | HS osc mode (-04)                      |

|                  |       |                                 | 100<br>50 | _    | 250<br>250 | ns<br>ns   | HS osc mode (-10)<br>HS osc mode (-20) |

|                  |       |                                 | 5         | _    | _          | μs         | LP osc mode                            |

| 2                | Тсү   | Instruction Cycle Time (Note 1) | 200       |      | DC         | ns         | Tcy = 4/Fosc                           |

| 3                | TosL, | External Clock in (OSC1) High   | 50        | _    |            | ns         | XT oscillator                          |

|                  | TosH  | or Low Time                     | 2.5       | _    | _          | μs         | LP oscillator                          |

|                  |       |                                 | 10        | _    | _          | ns         | HS oscillator                          |

| 4                | TosR, | External Clock in (OSC1) Rise   | _         | _    | 25         | ns         | XT oscillator                          |

|                  | TosF  | or Fall Time                    | _         | —    | 50         | ns         | LP oscillator                          |

|                  |       |                                 | _         |      | 15         | ns         | HS oscillator                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C710/711.

## PIC16C71X

Applicable Devices 710 71 711 715

#### 13.0 ELECTRICAL CHARACTERISTICS FOR PIC16C715

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                              |         |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Storage temperature                                                                                                                         | +150°C  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                | + 0.3V) |

| Voltage on VDD with respect to Vss                                                                                                          | €+7.5V  |

| Voltage on MCLR with respect to Vss0 to                                                                                                     | o +14V  |

| Voltage on RA4 with respect to Vss0 to                                                                                                      | o +14V  |

| Total power dissipation (Note 1)                                                                                                            | 1.0W    |

| Maximum current out of Vss pin                                                                                                              | 300 mA  |

| Maximum current into VDD pin                                                                                                                | 250 mA  |

|                                                                                                                                             | 20 mA   |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)±                                                                                             | 20 mA   |

| Maximum output current sunk by any I/O pin                                                                                                  | .25 mA  |

|                                                                                                                                             | .20     |

| Maximum current sunk by PORTA                                                                                                               | 200 mA  |

| Maximum current sourced by PORTA                                                                                                            | 200 mA  |

| Maximum current sunk by PORTB                                                                                                               | 200 mA  |

| Maximum current sourced by PORTB                                                                                                            | 200 mA  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Rdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD - VOH) x IOH} + $\Sigma$ (VOI |         |

| + NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to t                                      | the     |

TNOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

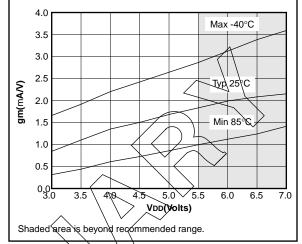

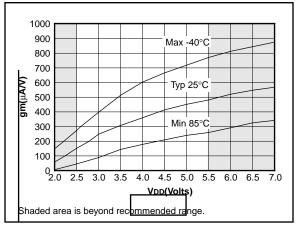

### 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

## PIC16C71X

#### Applicable Devices 710 71 711 715

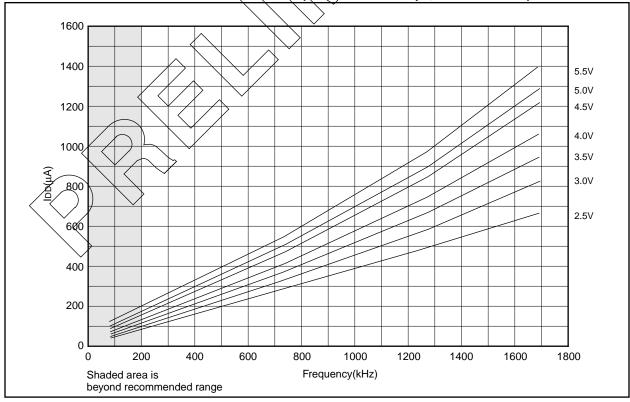

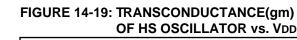

FIGURE 14-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

#### TABLE 14-1: RC OSCILLATOR FREQUENCIES

FIGURE 14-18: TYPICAL IDD vs.

| Cext   | Rext | Average         |        |  |  |  |  |  |

|--------|------|-----------------|--------|--|--|--|--|--|

| Cext   | Rext | Fosc @ 5V, 25°C |        |  |  |  |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |  |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |  |  |  |

|        | 100k | 268 kHz         | ±⁄1,1% |  |  |  |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ±1.0%  |  |  |  |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |  |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |  |  |  |

|        | 100k | 77.2 kHz        | ± 1.0% |  |  |  |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |  |  |  |

|        | 5k   | 501 kHz /       | ± 1.2% |  |  |  |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |  |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |  |  |  |

The percentage variation-indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

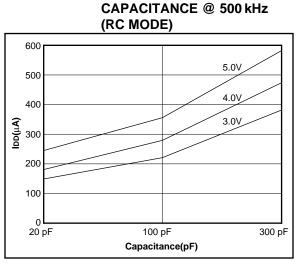

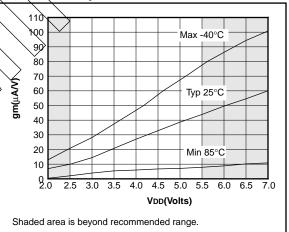

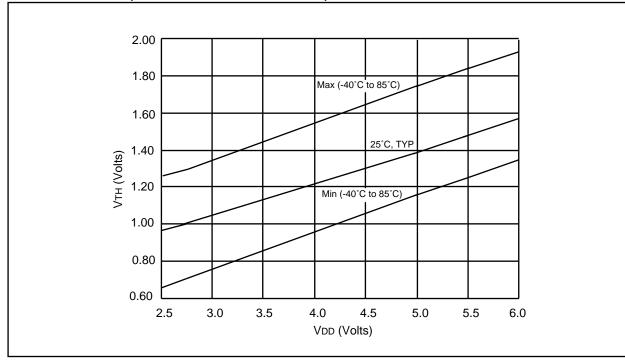

#### FIGURE 14-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

#### FIGURE 14-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

| Standard Operating Conditions (unless otherwise source of the conditions)DC CHARACTERISTICSDC CHARACTERISTICS $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (indust of the conditions)Operating voltage VDD range as described in DC spect and Section 15.2. |                                                                                                              |       |     | TA ≤ +70°C (commercial)<br>TA ≤ +85°C (industrial) |     |       |                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-----|----------------------------------------------------|-----|-------|-------------------------------------------------------------------------|

| Param<br>No.                                                                                                                                                                                                                                            | Characteristic                                                                                               | Sym   | Min | Typ<br>+                                           | Мах | Units | Conditions                                                              |

| 110.                                                                                                                                                                                                                                                    | Capacitive Loading Specs on<br>Output Pins                                                                   |       |     | 1                                                  |     |       |                                                                         |

| D100                                                                                                                                                                                                                                                    | OSC2 pin                                                                                                     | Cosc2 |     |                                                    | 15  |       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101                                                                                                                                                                                                                                                    | All I/O pins and OSC2 (in RC mode)                                                                           | Сю    |     |                                                    | 50  | pF    |                                                                         |

| † [                                                                                                                                                                                                                                                     | † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only |       |     |                                                    |     |       |                                                                         |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt trigger input. It is not recommended that the PIC16C71 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

3: Negative current is defined as current sourced by the pin.

4: PIC16C71 Rev. "Ax" INT pin has a TTL input buffer. PIC16C71 Rev. "Bx" INT pin has a Schmitt Trigger input buffer.

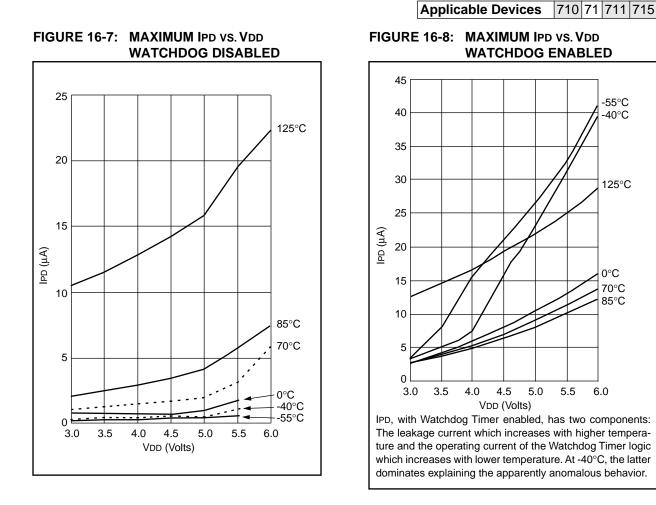

FIGURE 16-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS VS. VDD

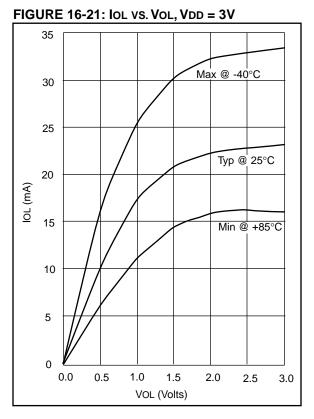

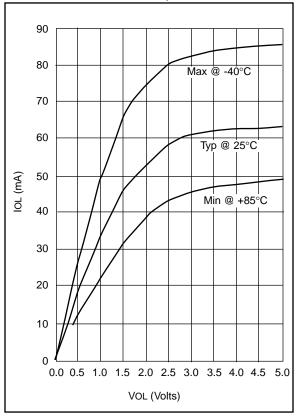

FIGURE 16-22: IOL VS. VOL, VDD = 5V

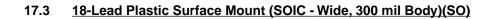

|        | Package Group: Plastic SOIC (SO) |             |           |        |            |           |  |  |  |  |

|--------|----------------------------------|-------------|-----------|--------|------------|-----------|--|--|--|--|

|        |                                  | Millimeters |           | Inches |            |           |  |  |  |  |

| Symbol | Min                              | Max         | Notes     | Min    | Мах        | Notes     |  |  |  |  |

| α      | 0°                               | 8°          |           | 0°     | <b>8</b> ° |           |  |  |  |  |

| А      | 2.362                            | 2.642       |           | 0.093  | 0.104      |           |  |  |  |  |

| A1     | 0.101                            | 0.300       |           | 0.004  | 0.012      |           |  |  |  |  |

| В      | 0.355                            | 0.483       |           | 0.014  | 0.019      |           |  |  |  |  |

| С      | 0.241                            | 0.318       |           | 0.009  | 0.013      |           |  |  |  |  |

| D      | 11.353                           | 11.735      |           | 0.447  | 0.462      |           |  |  |  |  |

| E      | 7.416                            | 7.595       |           | 0.292  | 0.299      |           |  |  |  |  |

| е      | 1.270                            | 1.270       | Reference | 0.050  | 0.050      | Reference |  |  |  |  |

| Н      | 10.007                           | 10.643      |           | 0.394  | 0.419      |           |  |  |  |  |

| h      | 0.381                            | 0.762       |           | 0.015  | 0.030      |           |  |  |  |  |

| L      | 0.406                            | 1.143       |           | 0.016  | 0.045      |           |  |  |  |  |

| Ν      | 18                               | 18          |           | 18     | 18         |           |  |  |  |  |

| CP     | _                                | 0.102       |           | _      | 0.004      |           |  |  |  |  |

#### **APPENDIX A:**

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (1K now as opposed to 512 before) and register file (68 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- 9. Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

#### APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.