Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 68 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

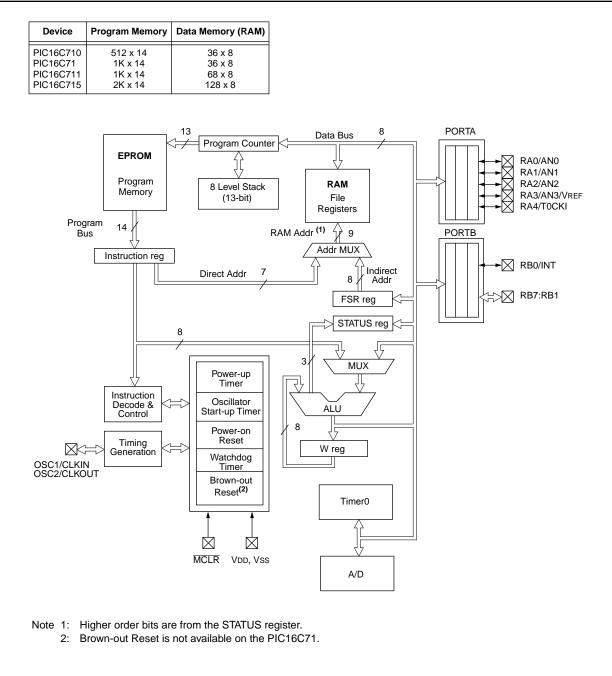

#### 1.0 GENERAL DESCRIPTION

The PIC16C71X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C710/71** devices have 36 bytes of RAM, the **PIC16C711** has 68 bytes of RAM and the **PIC16C715** has 128 bytes of RAM. Each device has 13 I/O pins. In addition a timer/counter is available. Also a 4-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C71X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C71X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C71X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

#### 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

#### 1.2 <u>Development Support</u>

PIC16C71X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 10.0 for more details about Microchip's development tools.

#### FIGURE 3-1: PIC16C71X BLOCK DIAGRAM

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# <sup>(4)</sup> | SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type                  | Description                                                                                                                                                                                              |

|-----------------|-------------|-----------------------------|--------------|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 16          | 18                          | 16           | I             | ST/CMOS <sup>(3)</sup>          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT     | 15          | 17                          | 15           | 0             | _                               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp        | 4           | 4                           | 4            | I/P           | ST                              | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|                 |             |                             |              |               |                                 | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0         | 17          | 19                          | 17           | I/O           | TTL                             | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1         | 18          | 20                          | 18           | I/O           | TTL                             | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2         | 1           | 1                           | 1            | I/O           | TTL                             | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF    | 2           | 2                           | 2            | I/O           | TTL                             | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI       | 3           | 3                           | 3            | I/O           | ST                              | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                         |

|                 |             |                             |              |               |                                 | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT         | 6           | 7                           | 6            | I/O           | TTL/ST <sup>(1)</sup>           | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1             | 7           | 8                           | 7            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB2             | 8           | 9                           | 8            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB3             | 9           | 10                          | 9            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB4             | 10          | 11                          | 10           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB5             | 11          | 12                          | 11           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB6             | 12          | 13                          | 12           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7             | 13          | 14                          | 13           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss             | 5           | 4, 6                        | 5            | Р             | —                               | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd             | 14          | 15, 16                      | 14           | Р             | —                               | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I = inp |             | O = outp<br>— = Not         |              |               | /O = input/out<br>TTL = TTL inp | I I                                                                                                                                                                                                      |

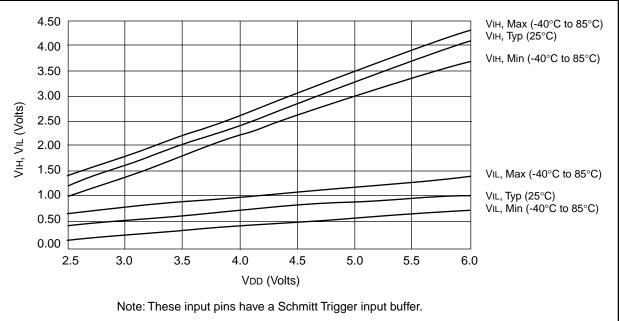

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The PIC16C71 is not available in SSOP package.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name                                                                                                | Bit 7               | Bit 6              | Bit 5         | Bit 4        | Bit 3         | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(1) |

|----------------------|-----------------------------------------------------------------------------------------------------|---------------------|--------------------|---------------|--------------|---------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |                                                                                                     |                     |                    |               | •            | •             |                  |               |           |                          |                                     |

| 00h <sup>(3)</sup>   | INDF Addressing this location uses contents of FSR to address data memory (not a physical register) |                     |                    |               |              |               |                  |               |           | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0                                                                                                | Timer0 mod          | lule's register    | r             |              |               |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(3)</sup>   | PCL                                                                                                 | Program Co          | ounter's (PC)      | Least Signif  | icant Byte   |               |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(3)</sup>   | STATUS                                                                                              | IRP <sup>(5)</sup>  | RP1 <sup>(5)</sup> | RP0           | TO           | PD            | Z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(3)</sup>   | FSR                                                                                                 | Indirect data       | a memory ad        | dress pointe  | r            |               |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA                                                                                               | —                   | —                  | —             | PORTA Dat    | a Latch whe   | n written: PO    | RTA pins wh   | en read   | x 0000                   | u 0000                              |

| 06h                  | PORTB                                                                                               | PORTB Dat           | a Latch whe        | n written: PC | DRTB pins wł | nen read      |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | —                                                                                                   | Unimpleme           | nted               |               |              |               |                  |               |           | —                        | —                                   |

| 08h                  | ADCON0                                                                                              | ADCS1               | ADCS0              | (6)           | CHS1         | CHS0          | GO/DONE          | ADIF          | ADON      | 00-0 0000                | 00-0 0000                           |

| 09h <sup>(3)</sup>   | ADRES                                                                                               | A/D Result Register |                    |               |              |               |                  |               |           |                          | uuuu uuuu                           |

| 0Ah <sup>(2,3)</sup> | PCLATH                                                                                              | _                   | —                  | _             | Write Buffer | for the uppe  | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <b>(3)</b>       | INTCON                                                                                              | GIE                 | ADIE               | TOIE          | INTE         | RBIE          | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| Bank 1               |                                                                                                     |                     |                    |               |              |               |                  |               |           |                          |                                     |

| 80h <sup>(3)</sup>   | INDF                                                                                                | Addressing          | this location      | uses conten   | ts of FSR to | address dat   | a memory (no     | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION                                                                                              | RBPU                | INTEDG             | TOCS          | TOSE         | PSA           | PS2              | PS1           | PS0       | 1111 1111                | 1111 1111                           |

| 82h <sup>(3)</sup>   | PCL                                                                                                 | Program Co          | ounter's (PC)      | Least Signif  | icant Byte   |               |                  |               |           | 0000 0000                | 0000 0000                           |

| 83h <sup>(3)</sup>   | STATUS                                                                                              | IRP <sup>(5)</sup>  | RP1 <sup>(5)</sup> | RP0           | TO           | PD            | z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(3)</sup>   | FSR                                                                                                 | Indirect data       | a memory ad        | dress pointe  | er           |               |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA                                                                                               | —                   | —                  | —             | PORTA Dat    | a Direction F | Register         |               |           | 1 1111                   | 1 1111                              |

| 86h                  | TRISB                                                                                               | PORTB Dat           | a Direction C      | Control Regis | ster         |               |                  |               |           | 1111 1111                | 1111 1111                           |

| 87h <sup>(4)</sup>   | PCON                                                                                                | —                   | —                  | —             | _            | —             | _                | POR           | BOR       | dd                       | uu                                  |

| 88h                  | ADCON1                                                                                              | —                   | —                  | _             | _            | _             | —                | PCFG1         | PCFG0     | 00                       | 00                                  |

| 89h <sup>(3)</sup>   | ADRES                                                                                               | A/D Result          | Register           |               |              |               |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 8Ah <b>(2,3)</b>     | PCLATH                                                                                              | _                   | —                  | —             | Write Buffer | for the uppe  | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(3)</sup>   | INTCON                                                                                              | GIE                 | ADIE               | TOIE          | INTE         | RBIE          | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

#### TABLE 4-1: PIC16C710/71/711 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: These registers can be addressed from either bank.

4: The PCON register is not physically implemented in the PIC16C71, read as '0'.

5: The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear.

6: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

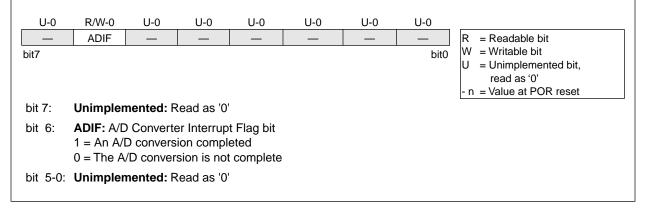

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

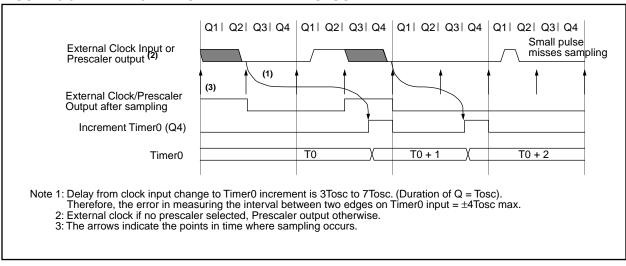

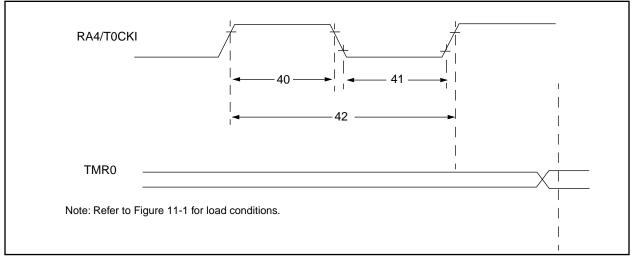

#### 6.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Applicable Devices 710 71 711 715

The analog-to-digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 7-1 and Figure 7-2, controls the operation of the A/D module. The ADCON1 register, shown in Figure 7-3 configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0<br>ADCS1 | R/W-0<br>ADCS0                                                                                                                                            | U-0                                           | R/W-0<br>CHS1 | R/W-0<br>CHS0 | R/W-0<br>GO/DONE                   | R/W-0<br>ADIF | R/W-0<br>ADON | R = Readable bit                                                                     |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|---------------|------------------------------------|---------------|---------------|--------------------------------------------------------------------------------------|--|--|

| bit7           | ADCSU                                                                                                                                                     |                                               | CHST          | CHSU          | GO/DONE                            | ADIF          | bit0          | W = Writable bit<br>U = Unimplemented<br>bit, read as '0'<br>- n =Value at POR reset |  |  |

| bit 7-6:       | 00 = Fos<br>01 = Fos<br>10 = Fos                                                                                                                          | c/8                                           |               |               |                                    |               |               |                                                                                      |  |  |

| bit 5:         | Unimple                                                                                                                                                   | <b>nented:</b> Re                             | ad as '0'.    |               |                                    |               |               |                                                                                      |  |  |

| bit 4-3:       | CHS1:CHS0: Analog Channel Select bits<br>00 = channel 0, (RA0/AN0)<br>01 = channel 1, (RA1/AN1)<br>10 = channel 2, (RA2/AN2)<br>11 = channel 3, (RA3/AN3) |                                               |               |               |                                    |               |               |                                                                                      |  |  |

| bit 2:         | GO/DON                                                                                                                                                    | E: A/D Con                                    | version Sta   | atus bit      |                                    |               |               |                                                                                      |  |  |

|                |                                                                                                                                                           | onversion ir<br>onversion r                   |               |               | is bit starts th<br>bit is automat |               |               | are when the A/D conver-                                                             |  |  |

|                | 1 = conve                                                                                                                                                 | D Conversio<br>ersion is cor<br>ersion is not | nplete (mu    |               | t Flag bit<br>red in softwar       | e)            |               |                                                                                      |  |  |

|                |                                                                                                                                                           | onverter mo                                   | •             | •             | consumes no                        | operating o   | current       |                                                                                      |  |  |

| Note 1:        |                                                                                                                                                           | DCON0 is a nented, read                       |               | Purpose R     | /W bit for the                     | PIC16C71      | 0/711 only. I | For the PIC16C71, this bit is                                                        |  |  |

#### FIGURE 7-1: ADCON0 REGISTER (ADDRESS 08h), PIC16C710/71/711

#### 8.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 8.8 for details on SLEEP mode.

#### 8.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). (Section 6.0)

#### 8.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

For the PIC16C71 Note: if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

|                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                     |

|--------------------------|-------------------|-------------------|--------------------------------------------|-------------------|---------------------------------------|

| OSC1 /                   |                   |                   |                                            |                   |                                       |

| CLKOUT ③                 | (4)               |                   |                                            | /                 |                                       |

| INT pin                  |                   | 1                 | 1<br>1<br>1<br>1                           |                   | 1 1<br>1 1<br>1 1<br>1 1              |

| INTF flag<br>(INTCON<1>) |                   |                   | Interrupt Latency (2)                      |                   |                                       |

| GIE bit<br>(INTCON<7>)   |                   |                   |                                            |                   |                                       |

| INSTRUCTION              | FLOW              |                   | ,<br>, , , , , , , , , , , , , , , , , , , |                   | · · · · · · · · · · · · · · · · · · · |

| PC                       | PC                | PC+1              | PC+1                                       | X 0004h           | X 0005h                               |

| Instruction (<br>fetched | Inst (PC)         | Inst (PC+1)       | _                                          | Inst (0004h)      | Inst (0005h)                          |

| Instruction {            | Inst (PC-1)       | Inst (PC)         | Dummy Cycle                                | Dummy Cycle       | Inst (0004h)                          |

|                          |                   |                   |                                            |                   |                                       |

#### FIGURE 8-19: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode. 4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

# PIC16C71X

Applicable Devices 710 71 711 715

#### 11.0 ELECTRICAL CHARACTERISTICS FOR PIC16C710 AND PIC16C711

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                            | 55 to +125°C                         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Storage temperature                                                                                       |                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                        |                                      |

| Voltage on VDD with respect to VSS                                                                        |                                      |

| Voltage on MCLR with respect to Vss                                                                       | 0 to +14V                            |

| Voltage on RA4 with respect to Vss                                                                        |                                      |

| Total power dissipation (Note 1)                                                                          |                                      |

| Maximum current out of Vss pin                                                                            |                                      |

| Maximum current into VDD pin                                                                              |                                      |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                              |                                      |

| Output clamp current, Ioк (Vo < 0 or Vo > Voo)                                                            | ±20 mA                               |

| Maximum output current sunk by any I/O pin                                                                | 25 mA                                |

| Maximum output current sourced by any I/O pin                                                             | 25 mA                                |

| Maximum current sunk by PORTA                                                                             | 200 mA                               |

| Maximum current sourced by PORTA                                                                          | 200 mA                               |

| Maximum current sunk by PORTB                                                                             |                                      |

| Maximum current sourced by PORTB                                                                          | 200 mA                               |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | - VOH) x IOH} + $\Sigma$ (VOI x IOL) |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 11-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C710-04<br>PIC16C711-04                                                                                | PIC16C710-10<br>PIC16C711-10                                                                     | PIC16C710-20<br>PIC16C711-20                                                                    | PIC16LC710-04<br>PIC16LC711-04                                                                            | PIC16C710/JW<br>PIC16C711/JW                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 $\mu$ A max. at 4V<br>Freq:4 MHz max.                | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.      | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.     | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA typ. at 3.0V<br>IPD: 5.0 μA typ. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq:4 MHz max.                      |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V IDD: 2.7 mA typ. at 5.5V IPD: 1.5 $\mu A$ typ. at 4V Freq: 4 MHz max.          | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.     | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA typ. at 3.0V<br>IPD: 5.0 μA typ. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                     |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.           | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq:20 MHz max. | Not recommended for<br>use in HS mode                                                                     | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max.             |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for<br>use in LP mode                                                            | Not recommended for<br>use in LP mode                                                           | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at<br>3.0V<br>Freq: 200 kHz max. |

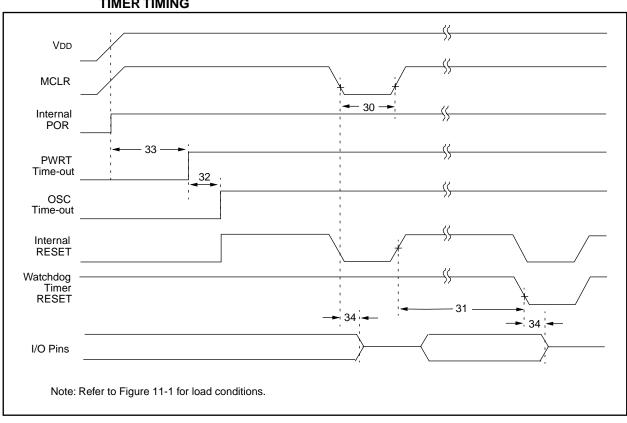

## FIGURE 11-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

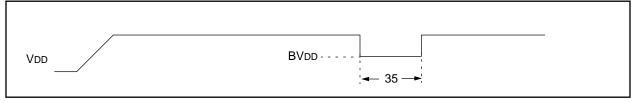

#### FIGURE 11-5: BROWN-OUT RESET TIMING

## TABLE 11-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max  | Units | Conditions                       |

|------------------|-------|--------------------------------------------------------|-----|----------|------|-------|----------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 1   | _        | _    | μs    | VDD = 5V, -40°C to +125°C        |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7*  | 18       | 33*  | ms    | VDD = 5V, -40°C to +125°C        |

| 32               | Tost  | Oscillation Start-up Timer Period                      | —   | 1024Tosc | _    | -     | Tosc = OSC1 period               |

| 33               | Tpwrt | Power up Timer Period                                  | 28* | 72       | 132* | ms    | VDD = 5V, -40°C to +125°C        |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 1.1  | μs    |                                  |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | _    | μs    | $3.8V \leq V\text{DD} \leq 4.2V$ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 11-6: TIMER0 EXTERNAL CLOCK TIMINGS

#### TABLE 11-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                |                      | Min                                            | Тур† | Max   | Units | Conditions                         |  |

|--------------|-----------|-------------------------------|----------------------|------------------------------------------------|------|-------|-------|------------------------------------|--|

| 40           | Tt0H      | T0CKI High Pulse Width        | No Prescaler         | 0.5Tcy + 20*                                   | —    |       | ns    | Must also meet                     |  |

|              |           |                               | With Prescaler       | 10*                                            | —    | _     | ns    | parameter 42                       |  |

| 41           | Tt0L      | T0CKI Low Pulse Width         | No Prescaler         | 0.5TCY + 20*                                   | —    | _     | ns    | Must also meet                     |  |

|              |           |                               | With Prescaler       | 10*                                            | —    | -     | ns    | parameter 42                       |  |

| 42           | Tt0P      | T0CKI Period                  |                      | Greater of:<br>20 ns or <u>Tcy + 40</u> *<br>N | _    | _     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 48           | Tcke2tmrl | Delay from external clock edg | e to timer increment | 2Tosc                                          | —    | 7Tosc | —     |                                    |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

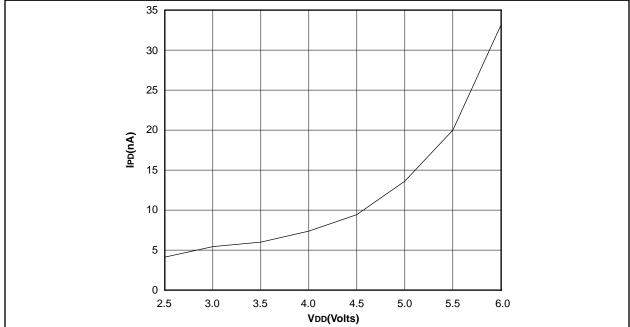

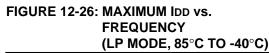

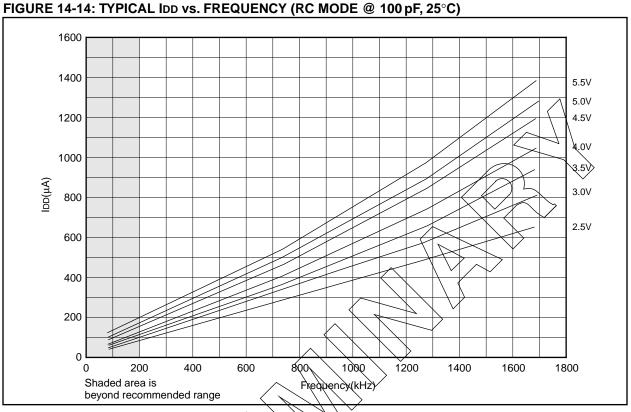

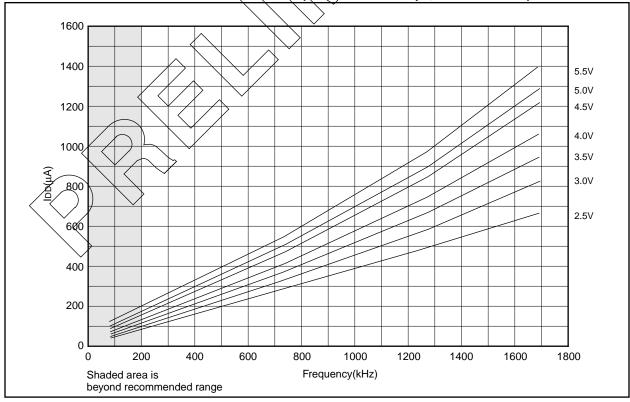

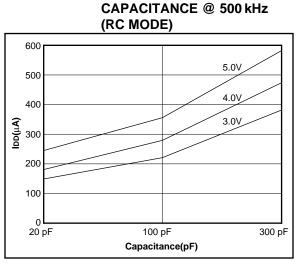

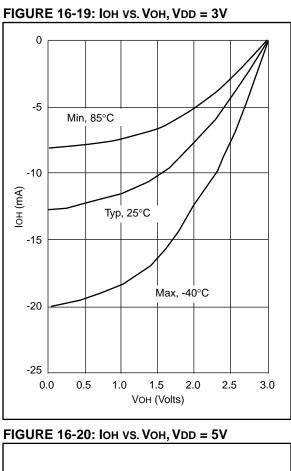

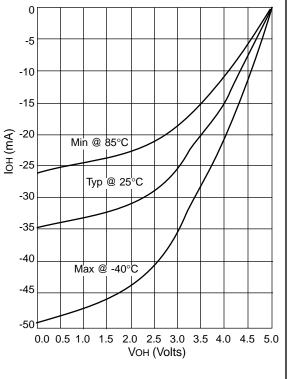

#### 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

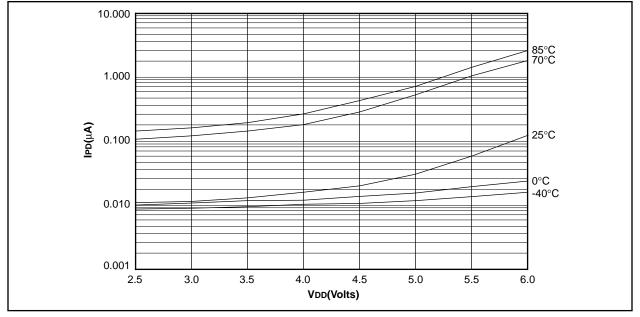

#### FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

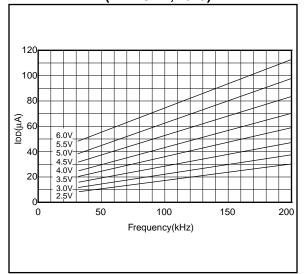

#### FIGURE 12-25: TYPICAL IDD vs. FREQUENCY (LP MODE, 25°C)

## Applicable Devices 710 71 711 715

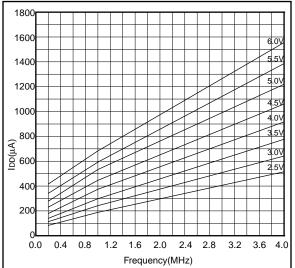

FIGURE 12-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

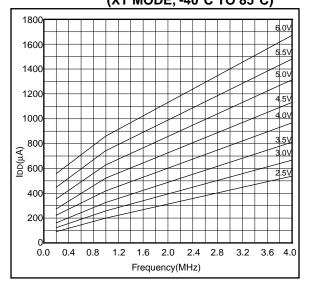

FIGURE 12-28: MAXIMUM IDD vs. FREQUENCY (XT MODE, -40°C TO 85°C)

# PIC16C71X

#### Applicable Devices 710 71 711 715

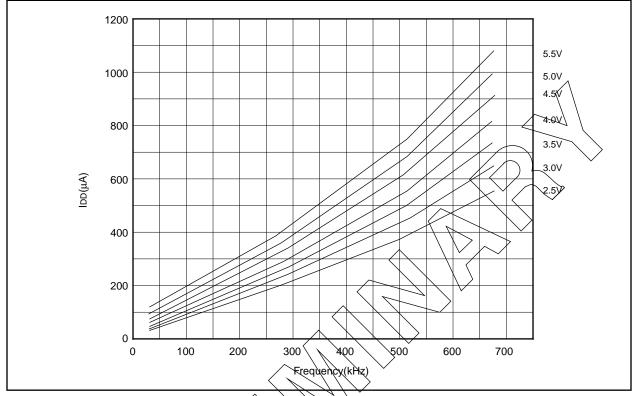

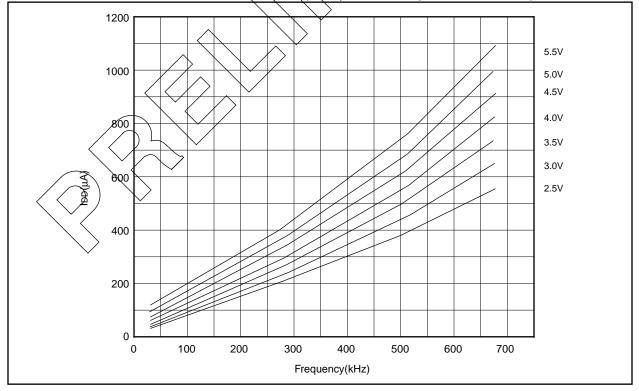

FIGURE 14-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

# PIC16C71X

## Applicable Devices 710 71 711 715

FIGURE 14-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

#### TABLE 14-1: RC OSCILLATOR FREQUENCIES

FIGURE 14-18: TYPICAL IDD vs.

| Cext   | Rext | Average         |        |  |  |  |  |

|--------|------|-----------------|--------|--|--|--|--|

| Cext   | Rext | Fosc @ 5V, 25°C |        |  |  |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |  |  |

|        | 100k | 268 kHz         | ±⁄1,1% |  |  |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ±1.0%  |  |  |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |  |  |

|        | 100k | 77.2 kHz        | ± 1.0% |  |  |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |  |  |

|        | 5k   | 501 kHz /       | ± 1.2% |  |  |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |  |  |

The percentage variation-indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

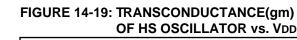

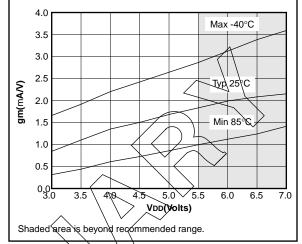

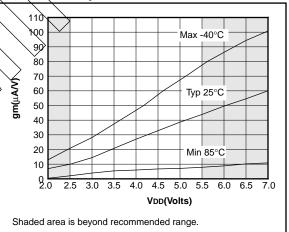

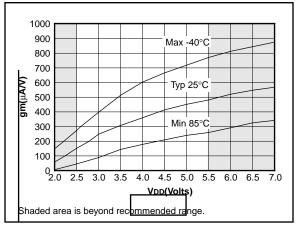

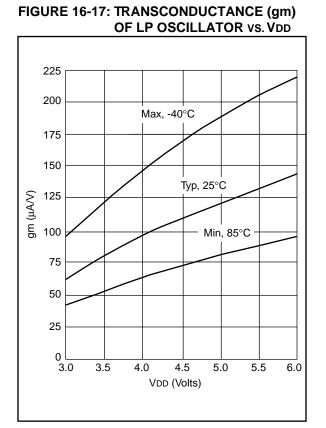

#### FIGURE 14-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

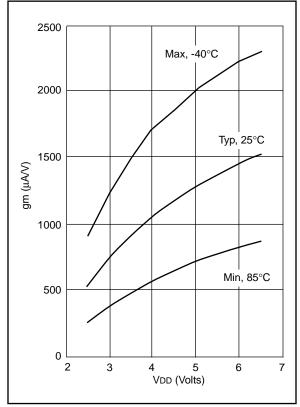

#### FIGURE 14-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

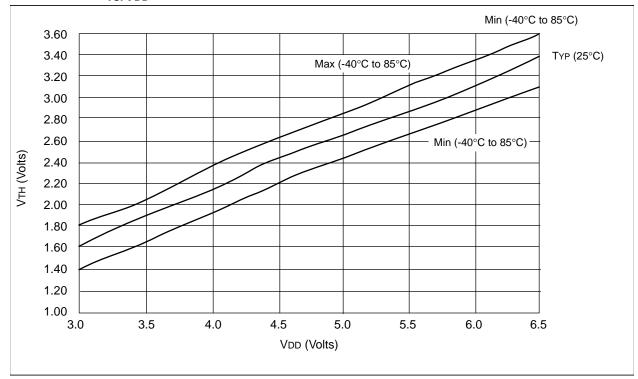

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) VS. VDD

#### FIGURE 16-11: VTH (INPUT THRESHOLD VOLTAGE) OF OSC1 INPUT (IN XT, HS, AND LP MODES) VS. VDD

# PIC16C71X

#### FIGURE 16-18: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

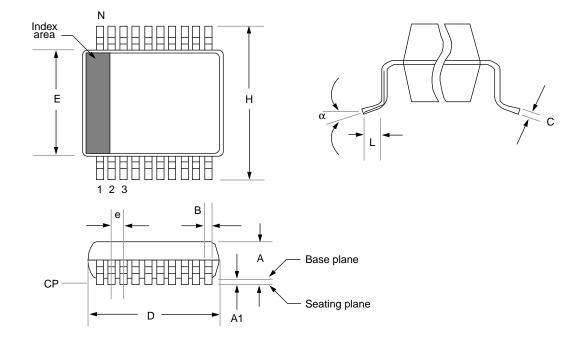

#### 17.4 20-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

|        | Package Group: Plastic SSOP |             |           |       |       |           |  |  |  |  |  |  |

|--------|-----------------------------|-------------|-----------|-------|-------|-----------|--|--|--|--|--|--|

|        |                             | Millimeters |           |       |       |           |  |  |  |  |  |  |

| Symbol | Min                         | Max         | Notes     | Min   | Max   | Notes     |  |  |  |  |  |  |

| α      | 0°                          | 8°          |           | 0°    | 8°    |           |  |  |  |  |  |  |

| А      | 1.730                       | 1.990       |           | 0.068 | 0.078 |           |  |  |  |  |  |  |

| A1     | 0.050                       | 0.210       |           | 0.002 | 0.008 |           |  |  |  |  |  |  |

| В      | 0.250                       | 0.380       |           | 0.010 | 0.015 |           |  |  |  |  |  |  |

| С      | 0.130                       | 0.220       |           | 0.005 | 0.009 |           |  |  |  |  |  |  |

| D      | 7.070                       | 7.330       |           | 0.278 | 0.289 |           |  |  |  |  |  |  |

| E      | 5.200                       | 5.380       |           | 0.205 | 0.212 |           |  |  |  |  |  |  |

| е      | 0.650                       | 0.650       | Reference | 0.026 | 0.026 | Reference |  |  |  |  |  |  |

| Н      | 7.650                       | 7.900       |           | 0.301 | 0.311 |           |  |  |  |  |  |  |

| L      | 0.550                       | 0.950       |           | 0.022 | 0.037 |           |  |  |  |  |  |  |

| N      | 20                          | 20          |           | 20    | 20    |           |  |  |  |  |  |  |

| CP     | -                           | 0.102       |           | -     | 0.004 |           |  |  |  |  |  |  |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

- 2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

- 3: This outline conforms to JEDEC MS-026.

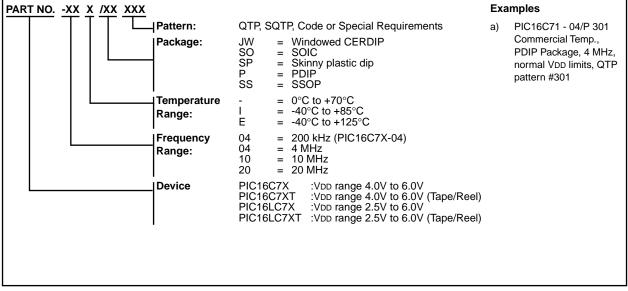

#### PIC16C71X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery refer to the factory or the listed sales office.

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

Products supported by a preliminary Data Sheet may possibly have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office (see below)

2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

3. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using. For latest version information and upgrade kits for Microchip Development Tools, please call 1-800-755-2345 or 1-602-786-7302.