#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

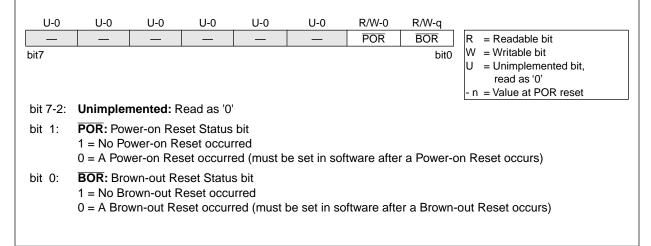

### 4.2.2.6 PCON REGISTER

# Applicable Devices71071711715

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset (BOR) condition from a Power-on Reset condition. For the PIC16C715 the PCON register also contains status bits MPEEN and PER. MPEEN reflects the value of the MPEEN bit in the configuration word. PER indicates a parity error reset has occurred. Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

# FIGURE 4-12: PCON REGISTER (ADDRESS 8Eh), PIC16C710/711

# FIGURE 4-13: PCON REGISTER (ADDRESS 8Eh), PIC16C715

| R-U<br>MPEEN | U-0                                                                                                                                                                                     | U-0       | U-0        | U-0 | R/W-1                   | R/W-0 | R/W-q<br>BOR <sup>(1)</sup> | R = Readable bit                                                                      |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----|-------------------------|-------|-----------------------------|---------------------------------------------------------------------------------------|--|--|

| bit7         |                                                                                                                                                                                         |           |            |     |                         |       | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:       | MPEEN: I<br>Reflects th                                                                                                                                                                 |           |            |     | Status bit<br>bit, MPEE | N     |                             |                                                                                       |  |  |

| bit 6-3:     | Unimplen                                                                                                                                                                                | nented: R | ead as '0' |     |                         |       |                             |                                                                                       |  |  |

| bit 2:       | bit 2: <b>PER:</b> Memory Parity Error Reset Status bit<br>1 = No Error occurred<br>0 = Program Memory Fetch Parity Error occurred (must be set in software after a Parity Error Reset) |           |            |     |                         |       |                             |                                                                                       |  |  |

| bit 1:       |                                                                                                                                                                                         |           |            |     |                         |       |                             |                                                                                       |  |  |

| bit 0:       |                                                                                                                                                                                         |           |            |     |                         |       |                             |                                                                                       |  |  |

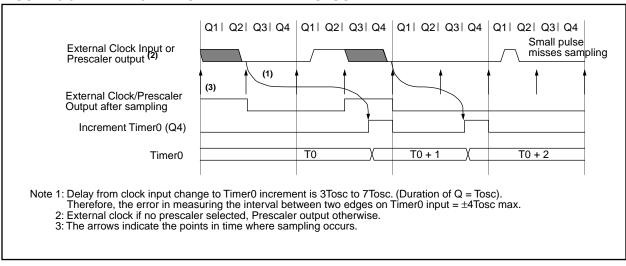

# 6.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

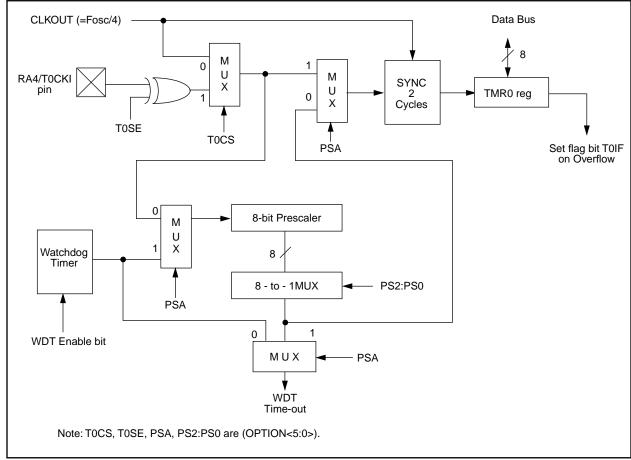

# 6.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

## FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

## TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

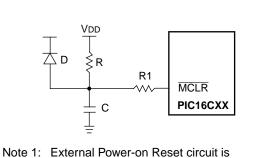

### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

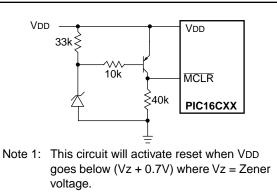

## FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

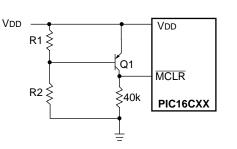

# FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

# 8.5 Interrupts

# Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |

|-------------------------------------------------------|

| External interrupt RB0/INT                            |

| TMR0 overflow interrupt                               |

| PORTB change interrupts (pins RB7:RB4)                |

| A/D Interrupt                                         |

| The interrupt control register (INTCON) records indi- |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Note: For the PIC16C71<br>If an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are: |      |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | 1    | . An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | 2    | 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | 3    | . The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts. |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               |      | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                              |  |  |  |  |  |  |  |

| LOOP                                                                                                                                                                                                                                                                          | BCF  | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               |      | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                               | GOTO | LOOP ; NO, try again                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

:

Yes, continue

with program

flow

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |  |  |  |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |  |  |  |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |  |  |  |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |  |  |  |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |  |  |  |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |  |  |  |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |  |  |  |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |  |  |  |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |  |  |  |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |  |  |  |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |  |  |  |

|                   | FLAG_REG = 0xC7<br>After Instruction   | If Skip:          | (2nd Cycle)                                                                   |  |  |  |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |  |  |  |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |  |  |  |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |  |  |  |

| •                     |      |

|-----------------------|------|

| Before Instruction    |      |

| PC = address          | HERE |

| After Instruction     |      |

| if $FLAG < 1 > = 0$ , |      |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                                                                     |                 |                       |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                                              | SF f,b                                                              |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                 |                       |  |  |  |

| Operation:        | $1 \rightarrow (f < b)$                                                                          | >)                                                                  |                 |                       |  |  |  |

| Status Affected:  | None                                                                                             |                                                                     |                 |                       |  |  |  |

| Encoding:         | 01                                                                                               | 01bb                                                                | bfff            | ffff                  |  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is                                                       | s set.          | ·                     |  |  |  |

| Words:            | 1                                                                                                |                                                                     |                 |                       |  |  |  |

| Cycles:           | 1                                                                                                |                                                                     |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                                                                  | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'                                             | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                                                                     |                 |                       |  |  |  |

| BTFSS             | Bit Test f                                                                                                                                                 | f, Skip if S          | Set                  |         | CALL              | Call Sub                                      | oroutine                             |                                                          |                                             |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|---------|-------------------|-----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------------------------------------------|--|

| Syntax:           | [ <i>label</i> ] B1                                                                                                                                        | FSS f,b               |                      |         | Syntax:           | [ label ]                                     | [ <i>label</i> ] CALL k              |                                                          |                                             |  |

| Operands:         | $0 \le f \le 127$                                                                                                                                          |                       |                      |         | Operands:         | $0 \le k \le 2047$                            |                                      |                                                          |                                             |  |

|                   | 0 ≤ b < 7                                                                                                                                                  |                       |                      |         | Operation:        | (PC)+ 1-                                      | → TOS,                               |                                                          |                                             |  |

| Operation:        | skip if (f<                                                                                                                                                | :b>) = 1              |                      |         |                   | $k \rightarrow PC < 10:0>,$                   |                                      |                                                          |                                             |  |

| Status Affected:  | None                                                                                                                                                       | i                     |                      |         |                   | $(PCLATH{<}4:3{>}) \rightarrow PC{<}12:11{>}$ |                                      |                                                          | :11>                                        |  |

| Encoding:         | 01                                                                                                                                                         | 11bb                  | bfff                 | ffff    | Status Affected:  | None                                          |                                      |                                                          |                                             |  |

| Description:      |                                                                                                                                                            | register 'f' is       |                      | ne next | Encoding:         | 10                                            | 0kkk                                 | kkkk                                                     | kkkk                                        |  |

|                   | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2Tcy instruction. |                       |                      |         | Description:      | (PC+1) is<br>eleven bit<br>into PC bi         | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the state<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |  |

| Words:            | 1                                                                                                                                                          |                       |                      |         |                   |                                               |                                      | rom PCLA<br>instruction                                  |                                             |  |

| Cycles:           | 1(2)                                                                                                                                                       |                       |                      |         | Words:            | 1                                             |                                      |                                                          |                                             |  |

| Q Cycle Activity: | Q1                                                                                                                                                         | Q2                    | Q3                   | Q4      | Cycles:           | 2                                             |                                      |                                                          |                                             |  |

|                   | Decode                                                                                                                                                     | Read<br>register 'f'  | Process<br>data      | NOP     | Q Cycle Activity: | Q1                                            | Q2                                   | Q3                                                       | Q4                                          |  |

| If Skip:          | (2nd Cyc                                                                                                                                                   | :le)                  |                      |         | 1st Cycle         | Decode                                        | Read<br>literal 'k',                 | Process<br>data                                          | Write to<br>PC                              |  |

|                   | Q1                                                                                                                                                         | Q2                    | Q3                   | Q4      | 1                 |                                               | Push PC<br>to Stack                  |                                                          |                                             |  |

|                   | NOP                                                                                                                                                        | NOP                   | NOP                  | NOP     | 2nd Cycle         | NOP                                           | NOP                                  | NOP                                                      | NOP                                         |  |

| Example           | HERE<br>FALSE                                                                                                                                              |                       | FLAG,1<br>PROCESS_   | _CODE   | Example           | HERE                                          | CALL                                 | THERE                                                    |                                             |  |

|                   | TRUE                                                                                                                                                       | •                     |                      |         |                   | Before Ir                                     |                                      |                                                          |                                             |  |

|                   |                                                                                                                                                            | •                     |                      |         |                   | After Ins                                     |                                      | Address HE                                               | RE                                          |  |

|                   | Before In                                                                                                                                                  | struction             |                      |         |                   |                                               | -                                    | ddress TH                                                |                                             |  |

|                   |                                                                                                                                                            |                       | address H            | IERE    |                   |                                               | TOS = A                              | Address HE                                               | RE+1                                        |  |

|                   | After Inst                                                                                                                                                 | ruction<br>if FLAG<1> | - 0                  |         |                   |                                               |                                      |                                                          |                                             |  |

|                   |                                                                                                                                                            | -                     | > = 0,<br>address F≠ | ALSE    |                   |                                               |                                      |                                                          |                                             |  |

|                   |                                                                                                                                                            | if FLAG<1><br>PC =    | ,                    |         |                   |                                               |                                      |                                                          |                                             |  |

|                   |                                                                                                                                                            | FU = 1                | address TF           | KUE     |                   |                                               |                                      |                                                          |                                             |  |

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] C                                                    | [ <i>label</i> ] CLRF f |                 |                       |  |  |  |  |

| Operands:         | $0 \le f \le 12$                                                      | 7                       |                 |                       |  |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                         |                 |                       |  |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | G_REG           |                       |  |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |                         |                 |                       |  |  |  |  |

|                   |                                                                       | FLAG_RE<br>Z            | =               | 0x00<br>1             |  |  |  |  |

| CLRW                                                   | Clear W                                                                                                         |                                                          |                                                          |                                                                        |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|

| Syntax:                                                | [ label ]                                                                                                       | CLRW                                                     |                                                          |                                                                        |

| Operands:                                              | None                                                                                                            |                                                          |                                                          |                                                                        |

| Operation:                                             | $00h \rightarrow (V 1 \rightarrow Z$                                                                            | V)                                                       |                                                          |                                                                        |

| Status Affected:                                       | Z                                                                                                               |                                                          |                                                          |                                                                        |

| Encoding:                                              | 00                                                                                                              | 0001                                                     | 0xxx                                                     | xxxx                                                                   |

| Description:                                           | W register set.                                                                                                 | is cleare                                                | d. Zero bit                                              | (Z) is                                                                 |

| Words:                                                 | 1                                                                                                               |                                                          |                                                          |                                                                        |

| Cycles:                                                | 1                                                                                                               |                                                          |                                                          |                                                                        |

| Q Cycle Activity:                                      | Q1                                                                                                              | Q2                                                       | Q3                                                       | Q4                                                                     |

|                                                        | Decode                                                                                                          | NOP                                                      | Process<br>data                                          | Write to<br>W                                                          |

| Example                                                | CLRW                                                                                                            |                                                          |                                                          |                                                                        |

| _///                                                   | Before In                                                                                                       | struction                                                | 1                                                        |                                                                        |

|                                                        |                                                                                                                 | W =                                                      | 0x5A                                                     |                                                                        |

|                                                        | After Inst                                                                                                      |                                                          |                                                          |                                                                        |

|                                                        |                                                                                                                 | W =<br>Z =                                               | 0x00<br>1                                                |                                                                        |

|                                                        |                                                                                                                 | _                                                        |                                                          |                                                                        |

| CLRWDT                                                 | Clear Wa                                                                                                        | tchdog                                                   | Timer                                                    |                                                                        |

| Syntax:                                                | [ label ]                                                                                                       | CLRWD                                                    | Т                                                        |                                                                        |

| Operands:                                              | None                                                                                                            |                                                          |                                                          |                                                                        |

| Operation:                                             | $00h \rightarrow W$                                                                                             |                                                          |                                                          |                                                                        |

|                                                        | $0 \rightarrow WDT \\ 1 \rightarrow \overline{TO}$                                                              | r presca                                                 | ier,                                                     |                                                                        |

|                                                        | $1 \rightarrow \overline{PD}$                                                                                   |                                                          |                                                          |                                                                        |

| Status Affected:                                       | TO, PD                                                                                                          |                                                          |                                                          |                                                                        |

| E a contra au                                          |                                                                                                                 |                                                          |                                                          |                                                                        |

| Encoding:                                              | 00                                                                                                              | 0000                                                     | 0110                                                     | 0100                                                                   |

| Encoding:<br>Description:                              | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.                                                           | struction<br>It also re                                  | resets the<br>sets the pi                                | Watch-<br>rescaler                                                     |

| C C                                                    | CLRWDT in<br>dog Timer<br>of the WD                                                                             | struction<br>It also re                                  | resets the<br>sets the pi                                | Watch-<br>rescaler                                                     |

| Description:<br>Words:                                 | CLRWDT in<br>dog Timer<br>of the WD<br>are set.                                                                 | struction<br>It also re                                  | resets the<br>sets the pi                                | Watch-<br>rescaler                                                     |

| Description:<br>Words:<br>Cycles:                      | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1                                                            | Istruction<br>It also re<br>T. Status I                  | resets the<br>sets the pr<br>bits TO and                 | Watch-<br>escaler<br>d PD                                              |

| Description:<br>Words:                                 | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1                                                            | struction<br>It also re                                  | resets the<br>sets the pi                                | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                       |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | CLRWDT in<br>dog Timer.<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode                                      | struction<br>It also re<br>T. Status I<br>Q2             | esets the<br>sets the pl<br>pits TO and<br>Q3<br>Process | Watch-<br>escaler<br>d PD<br>Q4<br>Clear                               |

| Description:<br>Words:<br>Cycles:                      | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode                                       | Q2                                                       | Q3<br>Process<br>data                                    | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                       |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode<br>CLRWDT<br>Before In                | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                    | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                       |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | CLRWDT in<br>dog Timer.<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode<br>CLRWDT<br>Before In<br>After Inst | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                    | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter            |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode<br>CLRWDT<br>Before In<br>After Inst  | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou<br>WDT pres | Q3<br>Process<br>data<br>nter =<br>scaler=               | Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00<br>0                        |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>Q1<br>Decode<br>CLRWDT<br>Before In<br>After Inst  | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou             | Q3<br>Process<br>data<br>nter =                          | Watch-<br>rescaler<br>PD<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00 |

| GOTO              | Unconditional Branch                                                                                                                                                                          |                     |                 |                |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                     | GOTO                | k               |                |  |  |  |  |

| Operands:         | $0 \le k \le 2047$                                                                                                                                                                            |                     |                 |                |  |  |  |  |

| Operation:        | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                             |                     |                 |                |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                          |                     |                 |                |  |  |  |  |

| Encoding:         | 10                                                                                                                                                                                            | 1kkk                | kkkk            | kkkk           |  |  |  |  |

| Description:      | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                 |                |  |  |  |  |

| Words:            | 1                                                                                                                                                                                             |                     |                 |                |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                             |                     |                 |                |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                            | Q2                  | Q3              | Q4             |  |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                        | Read<br>literal 'k' | Process<br>data | Write to<br>PC |  |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                           | NOP                 | NOP             | NOP            |  |  |  |  |

| Example           | GOTO TI<br>After Inst                                                                                                                                                                         |                     | Address         | THERE          |  |  |  |  |

| INCF              | Incremen                                              | nt f                        |                            |                  |

|-------------------|-------------------------------------------------------|-----------------------------|----------------------------|------------------|

| Syntax:           | [ label ]                                             | INCF f                      | ,d                         |                  |

| Operands:         | $0 \le f \le 12^{n}$ $d \in [0,1]$                    | 7                           |                            |                  |

| Operation:        | (f) + 1 $\rightarrow$                                 | (dest)                      |                            |                  |

| Status Affected:  | Z                                                     |                             |                            |                  |

| Encoding:         | 00                                                    | 1010                        | dfff                       | ffff             |

| Description:      | The conter<br>mented. If<br>in the W re<br>placed bac | d' is 0 the<br>gister. If ' | e result is<br>d' is 1 the | olaced           |

| Words:            | 1                                                     |                             |                            |                  |

| Cycles:           | 1                                                     |                             |                            |                  |

| Q Cycle Activity: | Q1                                                    | Q2                          | Q3                         | Q4               |

|                   | Decode                                                | Read<br>register<br>'f'     | Process<br>data            | Write to<br>dest |

| Example           | INCF                                                  | CNT,                        | 1                          |                  |

|                   |                                                       | struction<br>CNT<br>Z       | = 0xFF<br>= 0              | -                |

|                   | After Instr                                           | uction                      | -                          |                  |

|                   |                                                       | CNT<br>Z                    | = 0x00<br>= 1              | )                |

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHAF                        |                                                                   |               | ard Ope<br>ing tem |                          | ire 0°<br>-4       | itions (unless otherwise stated)C $\leq$ TA $\leq$ +70°C (commercial)0°C $\leq$ TA $\leq$ +85°C (industrial)0°C $\leq$ TA $\leq$ +125°C (extended) |                                                                                                                                                                                                                                   |

|--------------------------------|-------------------------------------------------------------------|---------------|--------------------|--------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym           | Min                | Тур†                     | Мах                | Units                                                                                                                                              | Conditions                                                                                                                                                                                                                        |

| D001                           | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0         | -                        | 6.0<br>6.0         | V<br>V                                                                                                                                             | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -                  | 1.5                      | -                  | V                                                                                                                                                  |                                                                                                                                                                                                                                   |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -                  | Vss                      | -                  | V                                                                                                                                                  | See section on Power-on Reset for details                                                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | Svdd          | 0.05               | -                        | -                  | V/ms                                                                                                                                               | See section on Power-on Reset for details                                                                                                                                                                                         |

| D005                           | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7                | 4.0                      | 4.3                | V                                                                                                                                                  | BODEN configuration bit is enabled                                                                                                                                                                                                |

| D010                           | Supply Current<br>(Note 2)                                        | IDD           | -                  | 2.0                      | 3.8                | mA                                                                                                                                                 | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                     |

| D010A                          |                                                                   |               | -                  | 22.5                     | 48                 | μA                                                                                                                                                 | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                   |

| D015                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -                  | 300*                     | 500                | μA                                                                                                                                                 | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>-        | 7.5<br>0.9<br>0.9<br>0.9 | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                                                               | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |

| D023                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ Ibor | -                  | 300*                     | 500                | μA                                                                                                                                                 | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

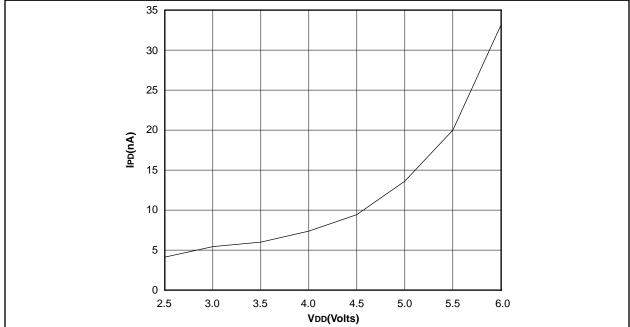

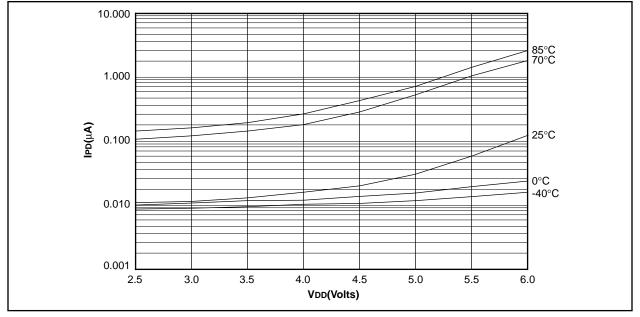

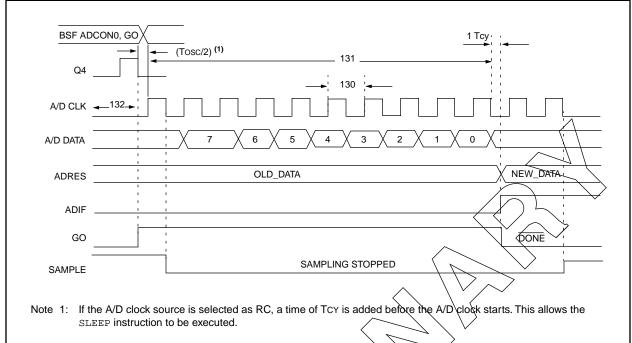

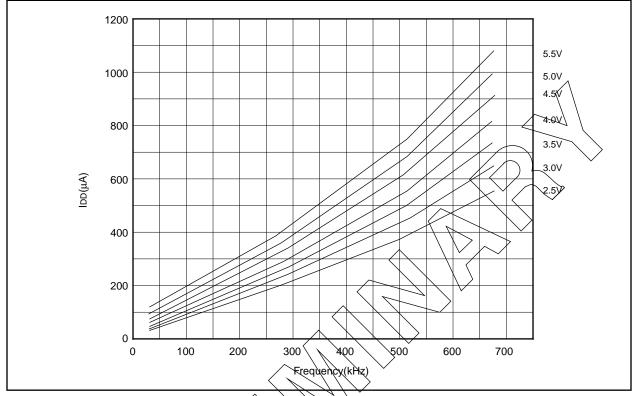

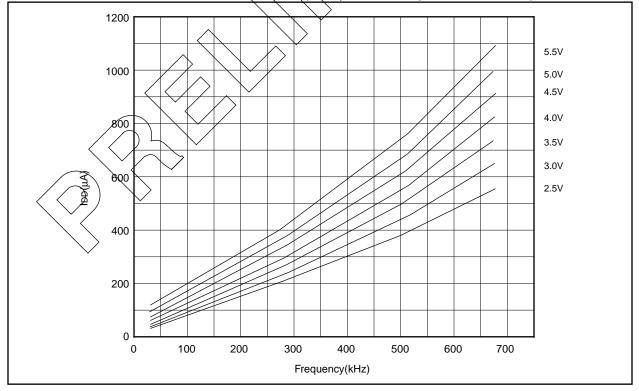

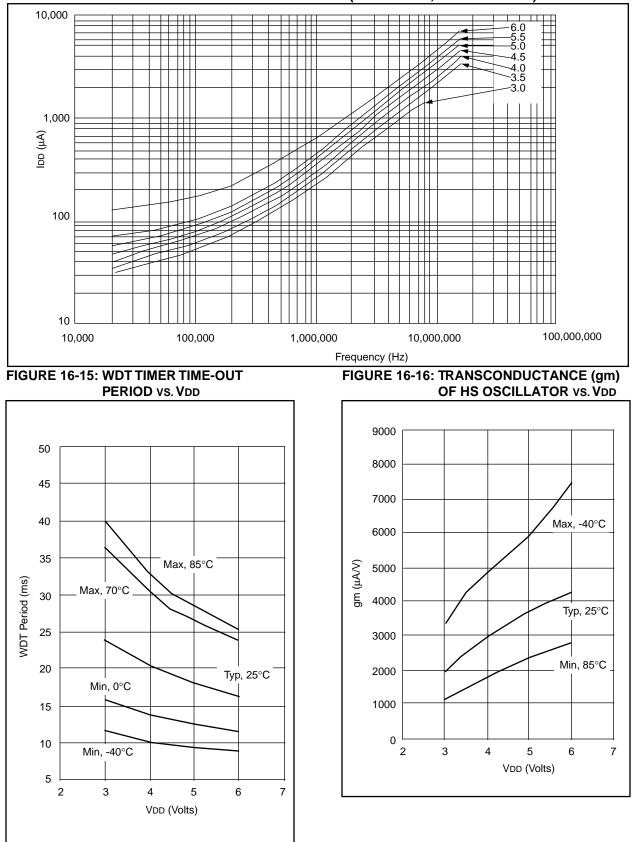

# 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

# FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

Applicable Devices 710 71 711 715

# 13.0 ELECTRICAL CHARACTERISTICS FOR PIC16C715

## Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                              |         |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Storage temperature                                                                                                                         | +150°C  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                | + 0.3V) |

| Voltage on VDD with respect to Vss                                                                                                          | €+7.5V  |

| Voltage on MCLR with respect to Vss0 to                                                                                                     | o +14V  |

| Voltage on RA4 with respect to Vss0 to                                                                                                      | o +14V  |

| Total power dissipation (Note 1)                                                                                                            | 1.0W    |

| Maximum current out of Vss pin                                                                                                              | 300 mA  |

| Maximum current into VDD pin                                                                                                                | 250 mA  |

|                                                                                                                                             | 20 mA   |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)±                                                                                             | 20 mA   |

| Maximum output current sunk by any I/O pin                                                                                                  | .25 mA  |

|                                                                                                                                             | .20     |

| Maximum current sunk by PORTA                                                                                                               | 200 mA  |

| Maximum current sourced by PORTA                                                                                                            | 200 mA  |

| Maximum current sunk by PORTB                                                                                                               | 200 mA  |

| Maximum current sourced by PORTB                                                                                                            | 200 mA  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Rdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD - VOH) x IOH} + $\Sigma$ (VOI |         |

| + NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to t                                      | the     |

TNOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# Applicable Devices 710 71 711 715

## 13.2 DC Characteristics: PIC16LC715-04 (Commercial, Industrial)

| DC CHAF               | RACTERISTICS                                                        |               |      | ard Ope<br>ing tem |      | ire 0°                 | itions (unless otherwise stated) $C \leq TA \leq +70^{\circ}C$ (commercial) $0^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)                                                              |