Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 68 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

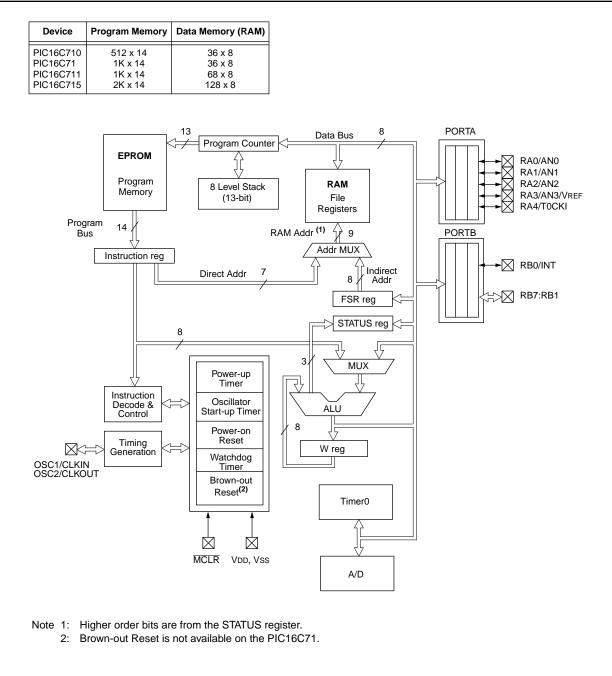

### FIGURE 3-1: PIC16C71X BLOCK DIAGRAM

NOTES:

### 8.0 SPECIAL FEATURES OF THE CPU

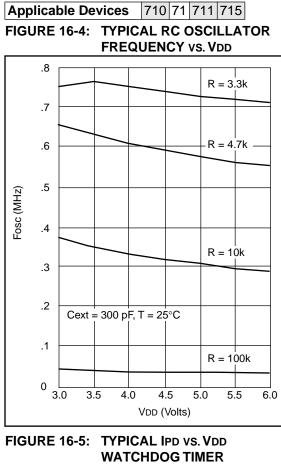

### Applicable Devices 710 71 711 715

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PER) (PIC16C715)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 8.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### FIGURE 8-1: CONFIGURATION WORD FOR PIC16C71

| bit13     | -   -                                                       | —                                   | —       | —        | _        | —       | —       | CP0      | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|-----------|-------------------------------------------------------------|-------------------------------------|---------|----------|----------|---------|---------|----------|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5: | Unimpler                                                    | nented                              | : Read  | as '1'   |          |         |         |          |       |      |       |               |                      |                 |

| bit 4:    | <b>CP0:</b> Cod<br>1 = Code<br>0 = All me                   | protect                             | ion off |          | ed, but  | 00h - 3 | Fh is w | /ritable |       |      |       |               |                      |                 |

| bit 3:    | <b>PWRTE:</b><br>1 = Power<br>0 = Power                     | -up Tin                             | ner ena | bled     | le bit   |         |         |          |       |      |       |               |                      |                 |

| bit 2:    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                        | enabled                             | ł       | Enable   | e bit    |         |         |          |       |      |       |               |                      |                 |

| bit 1-0:  | FOSC1:F<br>11 = RC c<br>10 = HS c<br>01 = XT c<br>00 = LP o | oscillato<br>oscillato<br>oscillato | or<br>r | tor Sele | ection b | vits    |         |          |       |      |       |               |                      |                 |

### 8.4.5 TIME-OUT SEQUENCE

### Applicable Devices 710 71 711 715

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

#### 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

### Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

#### 8.4.7 PARITY ERROR RESET (PER)

### Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

### TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

#### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power-up         |           | Brown out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

### TABLE 8-10: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C710/71/711

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C710/711 |

|------------------------------------|-----------------------|--------------------|-----------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x                                |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu                                |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu                                |

| WDT Reset                          | 000h                  | 0000 luuu          | uu                                |

| WDT Wake-up                        | PC + 1                | นนน0 0นนน          | uu                                |

| Brown-out Reset (PIC16C710/711)    | 000h                  | 0001 luuu          | u0                                |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu                                |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### TABLE 8-11: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C715

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | u10x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uuuu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | uuuu             |

| WDT Reset                          | 000h                  | 0000 luuu          | uuuu             |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uuuu             |

| Brown-out Reset                    | 000h                  | 0001 luuu          | uuu0             |

| Parity Error Reset                 | 000h                  | uuul Ouuu          | u0uu             |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

## PIC16C71X

| GOTO              | Unconditional Branch                                                                                                                                                                          |                     |                 |                |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                     | GOTO                | k               |                |  |  |  |

| Operands:         | $0 \le k \le 2047$                                                                                                                                                                            |                     |                 |                |  |  |  |

| Operation:        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow PC<12:11>$                                                                                                                               |                     |                 |                |  |  |  |

| Status Affected:  | None                                                                                                                                                                                          |                     |                 |                |  |  |  |

| Encoding:         | 10                                                                                                                                                                                            | 1kkk                | kkkk            | kkkk           |  |  |  |

| Description:      | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                 |                |  |  |  |

| Words:            | 1                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Cycles:           | 2                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                            | Q2                  | Q3              | Q4             |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                        | Read<br>literal 'k' | Process<br>data | Write to<br>PC |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                           | NOP                 | NOP             | NOP            |  |  |  |

| Example           | GOTO THERE<br>After Instruction<br>PC = Address THERE                                                                                                                                         |                     |                 |                |  |  |  |

| INCF              | Increment f                                                                                                                  |               |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|---------------|

| Syntax:           | [label] INCF f,d                                                                                                             |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                            |               |

| Operation:        | (f) + 1 $\rightarrow$ (dest)                                                                                                 |               |

| Status Affected:  | Z                                                                                                                            |               |

| Encoding:         | 00 1010 dfff                                                                                                                 | ffff          |

| Description:      | The contents of register 'f' a mented. If 'd' is 0 the result in the W register. If 'd' is 1 th placed back in register 'f'. | is placed     |

| Words:            | 1                                                                                                                            |               |

| Cycles:           | 1                                                                                                                            |               |

| Q Cycle Activity: | Q1 Q2 Q3                                                                                                                     | Q4            |

|                   | Decode Read register data                                                                                                    | Write to dest |

| Example           | INCF CNT, 1                                                                                                                  |               |

|                   | Before Instruction<br>CNT = 0<br>Z = 0                                                                                       | ٢F            |

|                   | After Instruction                                                                                                            |               |

|                   | $\begin{array}{rcl} CNT &=& 0;\\ Z &=& 1 \end{array}$                                                                        | <00           |

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                                                                                                            |                                                                   |                                   |               |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|---------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | [label] INCFSZ f,d                                                |                                   |               |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ |                                   |               |  |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (dest), s                                                         | kip if resu                       | ult = 0       |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              | None                                                              |                                   |               |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                                                              | dfff                              | ffff          |  |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                                                                   |                                   |               |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                                                                   |                                   |               |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                                                                   |                                   |               |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                                                                | Q3                                | Q4            |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                                                                            | Read<br>register<br>'f'                                           | Process<br>data                   | Write to dest |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                                          | le)                                                               |                                   | •             |  |  |  |  |

| ·                 | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                                                            | Q3                                | Q4            |  |  |  |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                                                               | NOP                               | NOP           |  |  |  |  |

| Example           | HERE INCFSZ CNT,<br>GOTO LOOP<br>CONTINUE •                                                                                                                                                                                                                                                                       |                                                                   |                                   |               |  |  |  |  |

|                   | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                                                                                                                                                                                                                              | $= adc$ ruction $= CN$ $= 0,$ $= adc$ $\neq 0,$                   | Iress HERE<br>T + 1<br>Iress CONT | TINUE         |  |  |  |  |

| IORLW             |                 |                     | eral with                                  |               |

|-------------------|-----------------|---------------------|--------------------------------------------|---------------|

| Syntax:           | [ label ]       | IORLW               | К                                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                                            |               |

| Operation:        | (W) .OR.        | $k \rightarrow (W)$ | )                                          |               |

| Status Affected:  | Z               |                     |                                            |               |

| Encoding:         | 11              | 1000                | kkkk                                       | kkkk          |

| Description:      | OR'ed wit       | h the eigh          | W register<br>t bit literal<br>ne W regist | 'k'. The      |

| Words:            | 1               |                     |                                            |               |

| Cycles:           | 1               |                     |                                            |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                                         | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data                            | Write to<br>W |

| Example           | IORLW           | 0x35                |                                            |               |

|                   | Before In       |                     | 1                                          |               |

|                   |                 | W =                 | 0x9A                                       |               |

|                   | After Inst      |                     |                                            |               |

|                   |                 | W =                 | 0xBF                                       |               |

| RETLW Return with Literal in W |                                                                                                                                                                                     |                                   |                                    |                                         |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|-----------------------------------------|--|--|

| Syntax:                        | [ label ]                                                                                                                                                                           | RETLW                             | k                                  |                                         |  |  |

| Operands:                      | $0 \le k \le 2$                                                                                                                                                                     | 55                                |                                    |                                         |  |  |

| Operation:                     | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow F \end{array}$                                                                                                              | ъс                                |                                    |                                         |  |  |

| Status Affected:               | None                                                                                                                                                                                |                                   |                                    |                                         |  |  |

| Encoding:                      | 11                                                                                                                                                                                  | 01xx                              | kkkk                               | kkkk                                    |  |  |

| Description:                   | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. |                                   |                                    |                                         |  |  |

| Words:                         | 1                                                                                                                                                                                   |                                   |                                    |                                         |  |  |

| Cycles:                        | 2                                                                                                                                                                                   |                                   |                                    |                                         |  |  |

| Q Cycle Activity:              | Q1                                                                                                                                                                                  | Q2                                | Q3                                 | Q4                                      |  |  |

| 1st Cycle                      | Decode                                                                                                                                                                              | Read<br>literal 'k'               | NOP                                | Write to<br>W, Pop<br>from the<br>Stack |  |  |

| 2nd Cycle                      | NOP                                                                                                                                                                                 | NOP                               | NOP                                | NOP                                     |  |  |

| Example                        | CALL TABLI                                                                                                                                                                          | ;offse                            | tains tab<br>t value<br>ow has tab |                                         |  |  |

| TABLE                          | ADDWF PC<br>RETLW k1<br>RETLW k2<br>•<br>•                                                                                                                                          | ;W = of<br>;Begin<br>;<br>; End o | table                              |                                         |  |  |

|                                | Before In                                                                                                                                                                           |                                   |                                    |                                         |  |  |

|                                |                                                                                                                                                                                     | W =                               | 0x07                               |                                         |  |  |

|                                | After Inst                                                                                                                                                                          | ruction<br>W =                    | value of k                         | 8                                       |  |  |

| Syntax:           | [ label ]                                                                                                                                               | RETUR | N    |                       |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------|--|--|

| Operands:         | None                                                                                                                                                    |       |      |                       |  |  |

| Operation:        | $TOS \to F$                                                                                                                                             | ъС    |      |                       |  |  |

| Status Affected:  | None                                                                                                                                                    |       |      |                       |  |  |

| Encoding:         | 00                                                                                                                                                      | 0000  | 0000 | 1000                  |  |  |

| Description:      | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |       |      |                       |  |  |

| Words:            | 1                                                                                                                                                       |       |      |                       |  |  |

| Cycles:           | 2                                                                                                                                                       |       |      |                       |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                      | Q2    | Q3   | Q4                    |  |  |

| 1st Cycle         | Decode                                                                                                                                                  | NOP   | NOP  | Pop from<br>the Stack |  |  |

| 2nd Cycle         | NOP                                                                                                                                                     | NOP   | NOP  | NOP                   |  |  |

| Example           | RETURN                                                                                                                                                  | rrupt |      |                       |  |  |

|                   |                                                                                                                                                         | PC =  | TOS  |                       |  |  |

|                   |                                                                                                                                                         |       |      |                       |  |  |

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                      |                                                                               |                                                |                                    |                                                          |                                                  | 、                                                   | 、                                 |                                      |          |          |            |                                       |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------|-------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----------------------------------|--------------------------------------|----------|----------|------------|---------------------------------------|

|                            |                                                    |                                       |                                                    |                      |                                                                               |                                                |                                    |                                                          |                                                  | 7                                                   | 2                                 |                                      |          |          |            | 7                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                      |                                                                               |                                                | 2                                  |                                                          |                                                  | 7                                                   |                                   | 2                                    |          |          |            |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 2                    |                                                                               |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC17C4X                   | 2                                                  |                                       | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C9XX                  | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          | 7          |                                       |

| PIC16C8X                   | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C7XX                  | 7                                                  | 7                                     | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16C6X                   | 7                                                  | 7                                     | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16CXXX                  | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 2        |          |            |                                       |

| PIC16C5X                   | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC14000                   | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC12C5XX                  | >                                                  | 7                                     | 7                                                  | >                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

|                            | PICMASTER®/<br>PICMASTER-CE<br>In-Circuit Emulator | CEPIC Low-Cost<br>In-Circuit Emulator | MPLAB™<br>Integrated<br>Development<br>Environment | MPLAB™ C<br>compiler | Lo fuzzyTECH <sup>®</sup> .MP<br>Explorer/Edition<br>Fuzzy Logic<br>Dev. Tool | MP-DriveWay™<br>Applications<br>Code Generator | Total Endurance™<br>Software Model | PICSTART <sup>®</sup><br>Lite Ultra Low-Cost<br>Dev. Kit | PICSTART®<br>Plus Low-Cost<br>Universal Dev. Kit | PRO MATE <sup>®</sup> II<br>Universal<br>Programmer | KEELOQ <sup>®</sup><br>Programmer | SEEVAL <sup>®</sup><br>Designers Kit | PICDEM-1 | PICDEM-2 | e PICDEM-3 | KEELOQ <sup>®</sup><br>Evaluation Kit |

### TABLE 10-1: DEVELOPMENT TOOLS FROM MICROCHIP

## PIC16C71X

| Appli | cable Devices | 710 7   | 1 711 715                            |                                                                                                                                                                                                                                                                            |

|-------|---------------|---------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1  | DC Character  | istics: | PIC16C<br>PIC16C<br>PIC16C<br>PIC16C | 710-04 (Commercial, Industrial, Extended)<br>711-04 (Commercial, Industrial, Extended)<br>710-10 (Commercial, Industrial, Extended)<br>711-10 (Commercial, Industrial, Extended)<br>710-20 (Commercial, Industrial, Extended)<br>711-20 (Commercial, Industrial, Extended) |

| DC CHARACTERISTICS             |                                                                   |               |                  | lard O<br>ating te        |                      | ture (               | ditions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended)                             |  |  |

|--------------------------------|-------------------------------------------------------------------|---------------|------------------|---------------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min              | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                         |  |  |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5       | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                            |  |  |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -                | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                    |  |  |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -                | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                          |  |  |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD          | 0.05             | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                          |  |  |

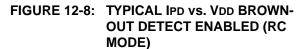

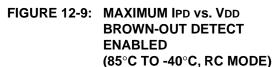

| D005                           | Brown-out Reset Voltage                                           | Bvdd          | 3.7              | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                 |  |  |

|                                |                                                                   |               | 3.7              | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                                                                                |  |  |

| D010                           | Supply Current (Note 2)                                           | IDD           | -                | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                      |  |  |

| D013                           |                                                                   |               | -                | 13.5                      | 30                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                  |  |  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |  |  |

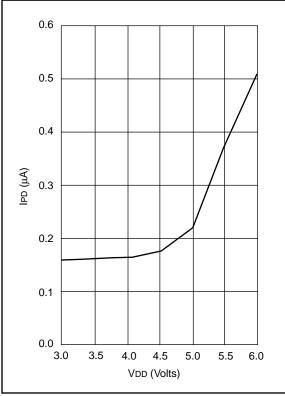

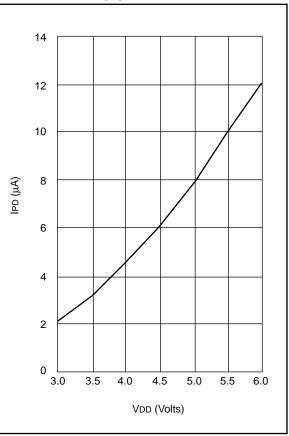

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>-<br>- | 10.5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 4.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -0^{\circ}C to +70^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |  |  |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

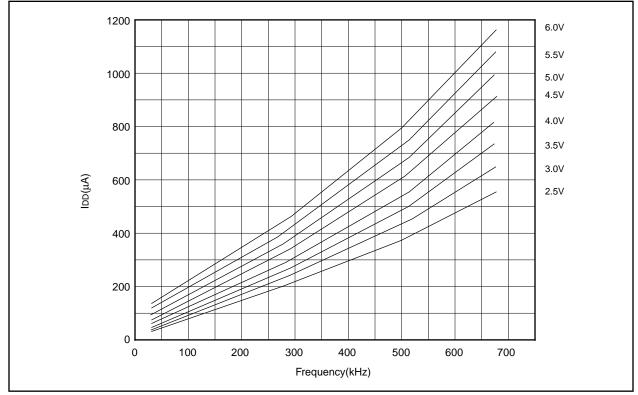

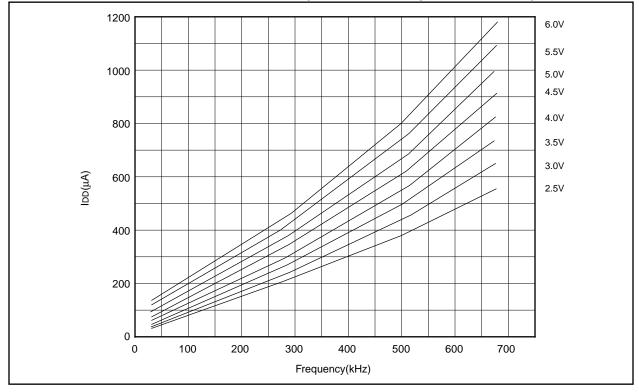

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDDMCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

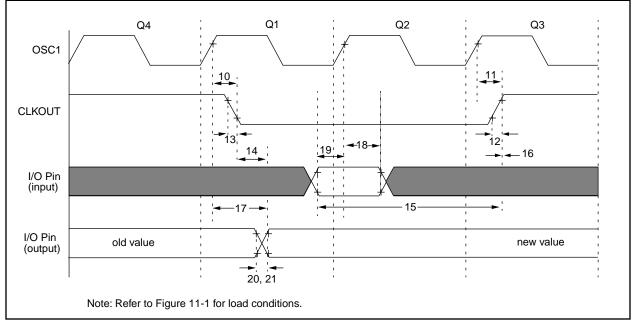

### FIGURE 11-3: CLKOUT AND I/O TIMING

### TABLE 11-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min                    | Тур† | Мах      | Units       | Conditions |        |

|------------------|----------|------------------------------------------------------------------|------------------------|------|----------|-------------|------------|--------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                                                 |                        | _    | 15       | 30          | ns         | Note 1 |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>                         |                        |      | 15       | 30          | ns         | Note 1 |

| 12*              | TckR     | CLKOUT rise time                                                 |                        | —    | 5        | 15          | ns         | Note 1 |

| 13*              | TckF     | CLKOUT fall time                                                 |                        |      | 5        | 15          | ns         | Note 1 |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid                            | d                      | _    | —        | 0.5Tcy + 20 | ns         | Note 1 |

| 15*              | TioV2ckH | Port in valid before CLKOL                                       | 0.25Tcy + 25           | —    | _        | ns          | Note 1     |        |

| 16*              | TckH2iol | Port in hold after CLKOUT                                        | 0                      | —    |          | ns          | Note 1     |        |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid                | _                      | _    | 80 - 100 | ns          |            |        |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to<br>Port input invalid (I/O in ho | ld time)               | TBD  | _        | _           | ns         |        |

| 19*              | TioV2osH | Port input valid to OSC11                                        | (I/O in setup time)    | TBD  | —        | _           | ns         |        |

| 20*              | TioR     | Port output rise time                                            | PIC16 <b>C</b> 710/711 |      | 10       | 25          | ns         |        |

|                  |          | PIC16 <b>LC</b> 710/711                                          |                        | _    | —        | 60          | ns         |        |

| 21*              | TioF     | Port output fall time PIC16 <b>C</b> 710/711                     |                        | —    | 10       | 25          | ns         |        |

|                  |          |                                                                  | PIC16LC710/711         | —    | —        | 60          | ns         |        |

| 22††*            | Tinp     | INT pin high or low time                                         |                        | 20   | —        | _           | ns         |        |

| 23††*            | Trbp     | RB7:RB4 change INT high                                          | or low time            | 20   | —        | —           | ns         |        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

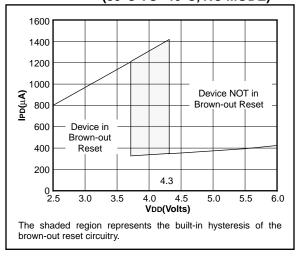

### FIGURE 12-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

Applicable Devices 710 71 711 715

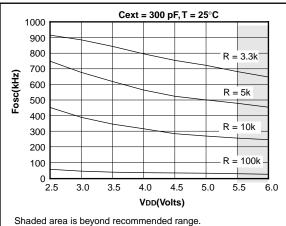

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

| OSC |                               | PIC16C715-04                                                                        | •                             | PIC16C715-10                                                                                                   |                       | PIC16C715-20                                                           |              | PIC16LC715-04                                                                     |                               | PIC16C715/JW                                                                      |

|-----|-------------------------------|-------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------|

| RC  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max.                                         | IDD:<br>IPD:          | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max. | IDD:<br>IPD: | 2.5V to 5.5V<br>2.0 mA typ. at 3.0V<br>0.9 μA typ. at 3V<br>4 MHz max.            | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.               |

| хт  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max.                                         | IDD:<br>NPD:          | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 µA typ. at 4V<br>4.MHz max, | IDD:<br>IPD: | 2.5V to 5.5V<br>2.0 mA typ. at 3.0V<br>0.9 μA typ. at 3V<br>4 MHz max.            | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.               |

| HS  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>13.5 mA typ. at 5.5V<br>1.5 μA typ. at 4.5V<br>4 MHz max.           | VDD:<br>IDD:<br>IPD:<br>Freq: | <ul> <li>4.5V to 5.5V</li> <li>30 mA max. at 5.5V</li> <li>1.5 μA typ. at 4.5V</li> <li>10 MHz max.</li> </ul> | · /·                  | 4.5V to 5,5V<br>30 mA max. at 5.5V<br>1.5 μA typ. at 4.5V              | Do no        | nt use in HS mode                                                                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>30 mA max. at 5.5V<br>1.5 μA typ. at 4.5V<br>10 MHz max.          |

| LP  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>52.5 μA typ. at 32 kHz, 4.0V<br>0.9 μA typ. at 4.0V<br>200 kHz max. | Do no                         | t use in LP mode                                                                                               | Do not use in LP mode |                                                                        | 1/ /         | 2.SV to 5.5V<br>48 μA max. at 32 kHz, 3.0V<br>5.0 μA max. at 3.0V<br>200 kHz max. | VDD:<br>IDD:<br>IPD:<br>Freq: | 2.5V to 5.5V<br>48 μA max. at 32 kHz, 3.0V<br>5.0 μA max. at 3.0V<br>200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

**TABLE 13-1:**

CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

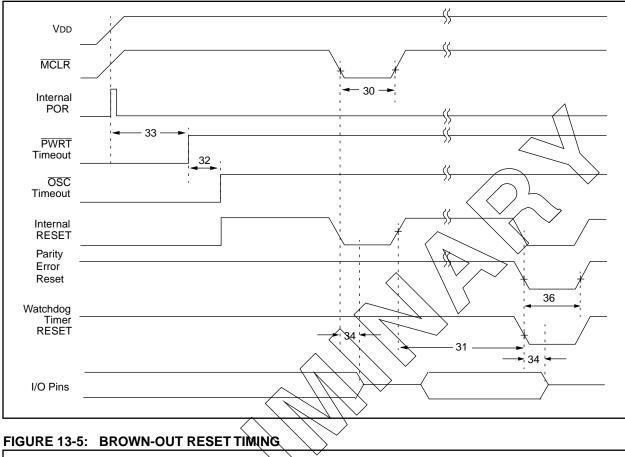

## FIGURE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, AND POWER-UP TIMER TIMING

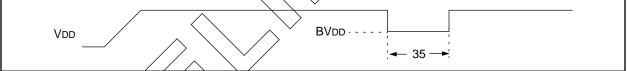

## TABLE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter | Sym              | Characteristic                                         | Min | Тур†     | Мах | Units | Conditions                |

|-----------|------------------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| No.       | $ \searrow \lor$ | $\frown$                                               |     |          |     |       |                           |

| 30        | √mc⊾             | MCLR Pulse Width (low)                                 | 2   | —        | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*       | Twdt             | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32        | < Tost           | Oscillation Start-up Timer Period                      | -   | 1024Tosc |     | —     | Tosc = OSC1 period        |

| 33*       | Tpwrt            | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34        | Tıoz             | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | _        | 2.1 | μs    |                           |

| 35        | TBOR             | Brown-out Reset pulse width                            | 100 | —        | _   | μs    | $VDD \le BVDD$ (D005)     |

| 36        | TPER             | Parity Error Reset                                     |     | TBD      |     | μs    |                           |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

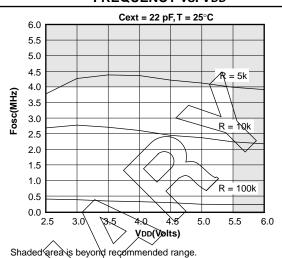

### FIGURE 14-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## FIGURE 14-6: TYPICAL RC OSCILLATOR

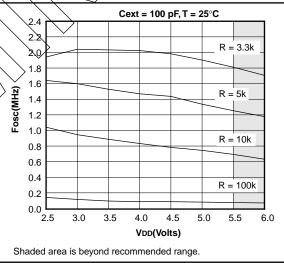

### FIGURE 14-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

# **PIC16C71X**

#### TABLE 16-1: **RC OSCILLATOR FREQUENCIES**

| Cart   | Devt | Average<br>Fosc @ 5V, 25°C |         |  |  |  |  |

|--------|------|----------------------------|---------|--|--|--|--|

| Cext   | Rext |                            |         |  |  |  |  |

| 20 pF  | 4.7k | 4.52 MHz                   | ±17.35% |  |  |  |  |

|        | 10k  | 2.47 MHz                   | ±10.10% |  |  |  |  |

|        | 100k | 290.86 kHz                 | ±11.90% |  |  |  |  |

| 100 pF | 3.3k | 1.92 MHz                   | ±9.43%  |  |  |  |  |

|        | 4.7k | 1.49 MHz                   | ±9.83%  |  |  |  |  |

|        | 10k  | 788.77 kHz                 | ±10.92% |  |  |  |  |

|        | 100k | 88.11 kHz                  | ±16.03% |  |  |  |  |

| 300 pF | 3.3k | 726.89 kHz                 | ±10.97% |  |  |  |  |

|        | 4.7k | 573.95 kHz                 | ±10.14% |  |  |  |  |

|        | 10k  | 307.31 kHz                 | ±10.43% |  |  |  |  |

|        | 100k | 33.82 kHz                  | ±11.24% |  |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

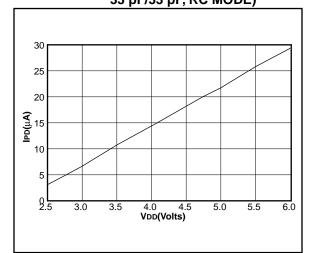

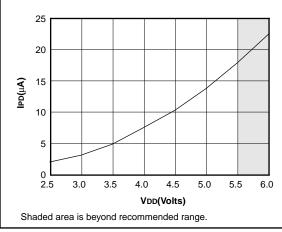

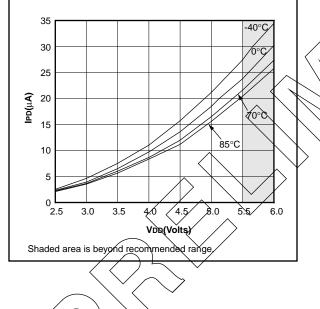

### FIGURE 16-6: TYPICAL IPD VS. VDD WATCHDOG TIMER ENABLED 25°C

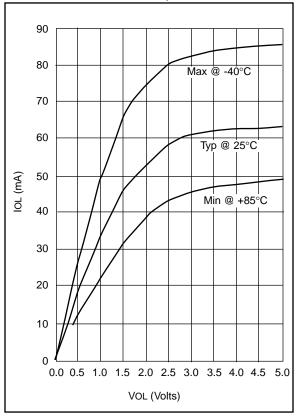

FIGURE 16-22: IOL VS. VOL, VDD = 5V

NOTES: