Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               |                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 68 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-20i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C71X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C710 | 512 x 14          | 36 x 8      |

| PIC16C71  | 1K x 14           | 36 x 8      |

| PIC16C711 | 1K x 14           | 68 x 8      |

| PIC16C715 | 2K x 14           | 128 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### 4.2.2.1 STATUS REGISTER

#### Applicable Devices 710 71 711 715

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| <u>R/W-0</u> | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                    | <u>R-1</u><br>TO | <u>R-1</u><br>PD | R/W-x<br>Z  | R/W-x     | R/W-x<br>C | D. Deedeble hit                                                                                           |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------|-----------|------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| IRP<br>bit7  | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RP0                                                                                                                      | 10               | <u>PD</u>        | 2           | DC        | bitO       | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |  |

| bit 7:       | 1 = Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh) |                  |                  |             |           |            |                                                                                                           |  |  |  |  |

| bit 6-5:     | RP1:RP0: Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes                                                                                                                                                                                                                                                                                               |                                                                                                                          |                  |                  |             |           |            |                                                                                                           |  |  |  |  |

| bit 4:       | <b>TO</b> : Time-<br>1 = After $\mu$<br>0 = A WD                                                                                                                                                                                                                                                                                                                                                                                                                                                        | power-up,                                                                                                                |                  | struction,       | or sleep ir | struction |            |                                                                                                           |  |  |  |  |

| bit 3:       | <b>PD</b> : Power $1 = \text{After } \mu$<br>0 = By exercised                                                                                                                                                                                                                                                                                                                                                                                                                                           | power-up o                                                                                                               | or by the c      |                  |             |           |            |                                                                                                           |  |  |  |  |

| bit 2:       | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |                  |                  |             |           |            |                                                                                                           |  |  |  |  |

| bit 1:       | <b>DC:</b> Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                                                                                                                                                                                                                                                      |                                                                                                                          |                  |                  |             |           |            |                                                                                                           |  |  |  |  |

| bit 0:       | <ul> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the most significant bit of the result occurred</li> <li>0 = No carry-out from the most significant bit of the result occurred</li> <li>Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |                                                                                                                          |                  |                  |             |           |            |                                                                                                           |  |  |  |  |

#### FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h)

#### 4.2.2.2 OPTION REGISTER

#### Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

#### FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                    | R/W-1       | R/W-1       | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                                                           |

|----------|--------------------------|-------------|-------------|------------|--------------|------------|-------|-----------------------------------------------------------|

| RBPU     | INTEDG                   | TOCS        | T0SE        | PSA        | PS2          | PS1        | PS0   | R = Readable bit                                          |

| bit7     | · · ·                    |             |             |            |              |            | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

|          |                          |             |             |            |              |            |       | - n = Value at POR reset                                  |

| bit 7:   | RBPU: PC                 | RTB Pull    | -up Enabl   | le bit     |              |            |       |                                                           |

|          | 1 = PORT                 |             |             |            |              |            |       |                                                           |

|          | 0 = PORTE                | 3 pull-ups  | s are enab  | led by ind | ividual port | latch valu | es    |                                                           |

| bit 6:   | INTEDG:                  | nterrupt E  | Edge Sele   | ct bit     |              |            |       |                                                           |

|          | 1 = Interru              | pt on risir | ng edge of  | f RB0/INT  | pin          |            |       |                                                           |

|          | 0 = Interru              | pt on falli | ng edge o   | f RB0/INT  | pin          |            |       |                                                           |

| bit 5:   | TOCS: TM                 | R0 Clock    | Source S    | elect bit  |              |            |       |                                                           |

|          | 1 = Transit              |             |             |            |              |            |       |                                                           |

|          | 0 = Interna              | al instruct | ion cycle ( | clock (CLk | (OUT)        |            |       |                                                           |

| bit 4:   | TOSE: TM                 |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            | on RA4/T00   |            |       |                                                           |

|          | 0 = Increm               | ent on lo   | w-to-high   | transition | on RA4/T00   | JKI pin    |       |                                                           |

| bit 3:   | PSA: Pres                |             | 0           |            |              |            |       |                                                           |

|          | 1 = Presca<br>0 = Presca |             |             |            | modulo       |            |       |                                                           |

|          |                          |             | •           |            | module       |            |       |                                                           |

| bit 2-0: | PS2:PS0:                 | Prescale    | r Rate Sel  | lect bits  |              |            |       |                                                           |

|          | Bit Value                | TMR0 R      | ate WD      | Γ Rate     |              |            |       |                                                           |

|          | 000                      | 1:2         | 1:          |            |              |            |       |                                                           |

|          | 001                      | 1:4         | 1:          |            |              |            |       |                                                           |

|          | 010<br>011               | 1:8         | 1:          |            |              |            |       |                                                           |

|          | 100                      | 1:16        |             | 16         |              |            |       |                                                           |

|          | 101                      | 1:64        | . 1:        | 32         |              |            |       |                                                           |

|          | 110                      | 1 : 12      |             | 64         |              |            |       |                                                           |

|          | 111                      | 1:25        | 6   1       | 128        |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

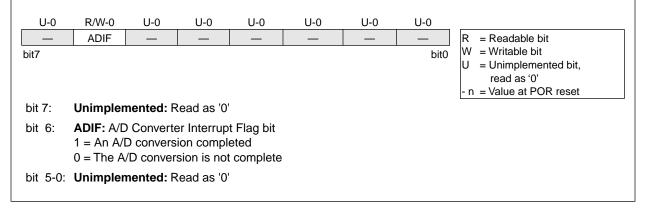

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

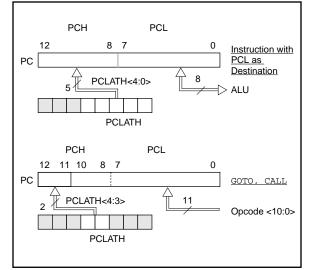

#### 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-14 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-14: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc- | Note 1: | There are no status bits to indicate stack overflow or stack underflow conditions.                                                                                   |  |  |  |  |  |

|----------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                  | Note 2: | called PUSH or POP. These are actions<br>that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc-<br>tions, or the vectoring to an interrupt |  |  |  |  |  |

#### 4.4 <u>Program Memory Paging</u>

The PIC16C71X devices ignore both paging bits (PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC16C71X is not recommended since this may affect upward compatibility with future products.

#### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |  |

|--------------|------|--------|-------------------------------------------------|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                    |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                    |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                    |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |  |

|              |      |        | Output is open drain type                       |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|--------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | —     | _     | RA4                           | RA3   | RA2   | RA1   | RA0    | x 0000                   | u 0000                    |

| 85h     | TRISA  | —     | —     | _     | PORTA Data Direction Register |       |       |       | 1 1111 | 1 1111                   |                           |

| 9Fh     | ADCON1 | _     | _     | _     | _                             | _     |       | PCFG1 | PCFG0  | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-3 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-3: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

;

| ; |     |        |       |   | PORT | latch | PORT p | ins  |

|---|-----|--------|-------|---|------|-------|--------|------|

| ; |     |        |       |   |      |       |        |      |

|   | BCF | PORTB, | 7     | ; | 01pp | pppp  | llpp j | pppp |

|   | BCF | PORTB, | б     | ; | 10pp | pppp  | 11pp   | pppp |

|   | BSF | STATUS | , RP0 | ; |      |       |        |      |

|   | BCF | TRISB, | 7     | ; | 10pp | pppp  | 11pp g | pppp |

|   | BCF | TRISB, | 6     | ; | 10pp | pppp  | 10pp j | pppp |

|   |     |        |       |   |      |       |        |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

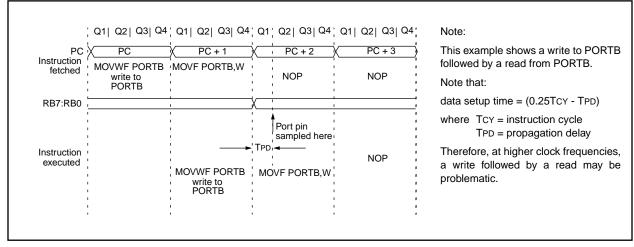

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-6). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-6: SUCCESSIVE I/O OPERATION

#### 7.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 7-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 20 MHz and 16 MHz (The A/D clock is programmed for 32TOSC), and assumes that immediately after 6TAD, the A/D clock is programmed for 2TOSC.

The 2Tosc violates the minimum TAD time since the last 4-bits will not be converted to correct values.

| EXAMPLE 7-3: | 4-BIT vs. 8-BIT CONVERSION TIMES |

|--------------|----------------------------------|

| $\mathbf{L}$ |                                  |

|                                 | - (1)                      | Resolution |         |  |

|---------------------------------|----------------------------|------------|---------|--|

|                                 | Freq. (MHz) <sup>(1)</sup> | 4-bit      | 8-bit   |  |

| TAD                             | 20                         | 1.6 μs     | 1.6 μs  |  |

|                                 | 16                         | 2.0 μs     | 2.0 μs  |  |

| Tosc                            | 20                         | 50 ns      | 50 ns   |  |

|                                 | 16                         | 62.5 ns    | 62.5 ns |  |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 20                         | 10 μs      | 16 μs   |  |

|                                 | 16                         | 12.5 μs    | 20 µs   |  |

Note 1: The PIC16C71 has a minimum TAD time of 2.0 µs.

All other PIC16C71X devices have a minimum TAD time of 1.6  $\mu$ s.

#### 8.2 <u>Oscillator Configurations</u>

#### 8.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

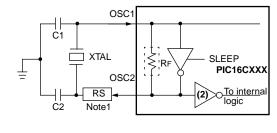

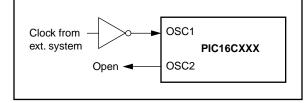

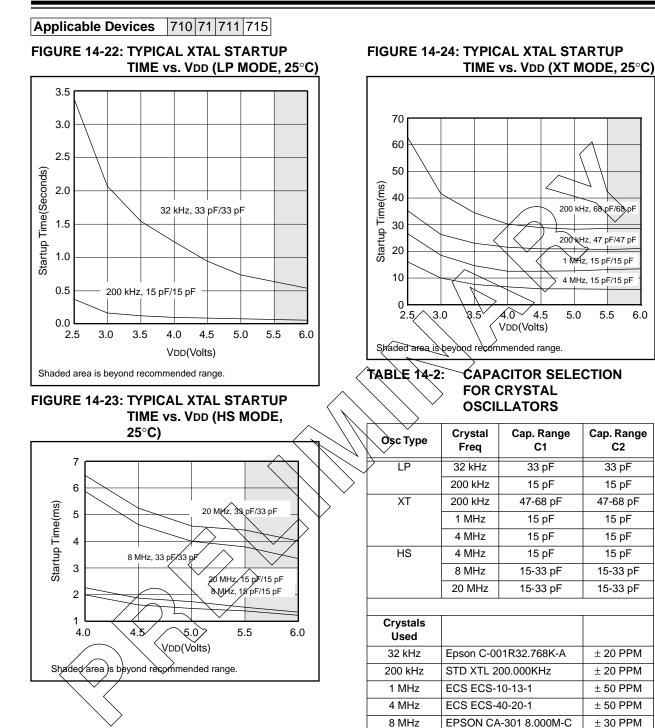

### 8.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-4). The PIC16CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 8-5).

#### FIGURE 8-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 8-1 and Table 8-1 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: The buffer is on the OSC2 pin.

#### FIGURE 8-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

## TABLE 8-1: CERAMIC RESONATORS, PIC16C71

| Ranges Tested:                                                          |                                     |                                         |                                         |  |  |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Mode                                                                    | Freq                                | Freq OSC1 OSC2                          |                                         |  |  |  |  |  |

| ХТ                                                                      | 455 kHz<br>2.0 MHz<br>4.0 MHz       | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |  |

| HS                                                                      | 8.0 MHz<br>16.0 MHz                 | 15 - 68 pF<br>10 - 47 pF                | 15 - 68 pF<br>10 - 47 pF                |  |  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                     |                                         |                                         |  |  |  |  |  |

| Resonator                                                               | s Used:                             |                                         |                                         |  |  |  |  |  |

| 455 kHz                                                                 | Panasonic EF                        | D-A455K04B                              | ± 0.3%                                  |  |  |  |  |  |

| 2.0 MHz                                                                 | Murata Erie CS                      | SA2.00MG                                | ± 0.5%                                  |  |  |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5%        |                                         |                                         |  |  |  |  |  |

| 8.0 MHz                                                                 | Murata Erie CSA8.00MT ± 0.5%        |                                         |                                         |  |  |  |  |  |

| 16.0 MHz                                                                | 0 MHz Murata Erie CSA16.00MX ± 0.5% |                                         |                                         |  |  |  |  |  |

| All resonators used did not have built-in capacitors.                   |                                     |                                         |                                         |  |  |  |  |  |

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16C71

| Mode                                                                    | Freq    | OSC1        | OSC2        |  |  |  |

|-------------------------------------------------------------------------|---------|-------------|-------------|--|--|--|

| LP                                                                      | 32 kHz  | 33 - 68 pF  | 33 - 68 pF  |  |  |  |

|                                                                         | 200 kHz | 15 - 47 pF  | 15 - 47 pF  |  |  |  |

| XT                                                                      | 100 kHz | 47 - 100 pF | 47 - 100 pF |  |  |  |

|                                                                         | 500 kHz | 20 - 68 pF  | 20 - 68 pF  |  |  |  |

|                                                                         | 1 MHz   | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

|                                                                         | 2 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |  |  |

|                                                                         | 4 MHz   | 15 - 33 pF  | 15 - 33 pF  |  |  |  |

| HS                                                                      | 8 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |  |  |

|                                                                         | 20 MHz  | 15 - 47 pF  | 15 - 47 pF  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |         |             |             |  |  |  |

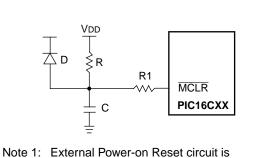

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

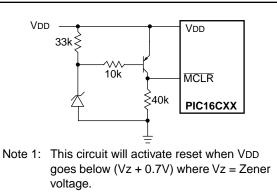

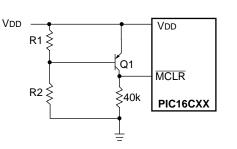

#### FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### TABLE 9-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  |       |     | 14-Bit | Opcode | Э    | Status   | Notes |

|------------|--------|------------------------------|-------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |       | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIEI |        | FILE REGISTER OPERATIONS     |       |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1     | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1     | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1     | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1     | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1     | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1     | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)  | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1     | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)  | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1     | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1     | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1     | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1     | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1     | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1     | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1     | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1     | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1     | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |       |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1     | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1     | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2) | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2) | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL AN |        | NTROL OPERATIONS             |       |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1     | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1     | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2     | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1     | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2     | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1     | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1     | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2     | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2     | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2     | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1     | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1     | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| JUDLW      |        |                              |       |     |        |        |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    | Syntax:           | [label] RRF f,d                                                                                                                                                                                                                                                                                              |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                  | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                            |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                                                                                                                        |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                                                                                                                            |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                                                            |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>$\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                        |

|                   |                                                                                                                                                                                                             |                   |                                                                                                                                                                                                                                                                                                              |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                                                                                                                            |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                                                                                                                            |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                  |

|                   | Decode Read Process Write to data dest                                                                                                                                                                      |                   | Decode Read register 'f' Virie to dest                                                                                                                                                                                                                                                                       |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                                                                                                                   |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | Before Instruction       REG1       =       1110       0110         C       =       0       -       -         After Instruction       -       -       -       -         REG1       =       1110       0110       -         W       =       0111       0011       -         C       =       0       -       - |

# PIC16C71X

#### SLEEP

| [ label ]                                                                                                                                            | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| None                                                                                                                                                 |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$ |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Status Affected: TO, PD                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 00                                                                                                                                                   | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with                                                                                      | ime-out s<br>ndog Time<br>cleared.<br>essor is pu<br>n the oscil                                                                                                                                                                                  | tatus bit, <sup>*</sup><br>er and its<br>ut into SLI<br>llator stop                                                                                                                                                                                                                                                                      | TO is<br>pres-<br>EEP<br>ped.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                                                                                                                                                    |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1                                                                                                                                                    |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Q1                                                                                                                                                   | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Decode                                                                                                                                               | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SLEEP                                                                                                                                                |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                      | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |  |  |

| SUBLW             | Subtract              | W from                                                                                                                               | Literal                  |            |  |  |  |  |

|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------|--|--|--|--|

| Syntax:           | [ label ]             | SUBL                                                                                                                                 | Nk                       |            |  |  |  |  |

| Operands:         | $0 \le k \le 25$      | 55                                                                                                                                   |                          |            |  |  |  |  |

| Operation:        | k - (W) $\rightarrow$ | • (W)                                                                                                                                |                          |            |  |  |  |  |

| Status Affected:  | C, DC, Z              |                                                                                                                                      |                          |            |  |  |  |  |

| Encoding:         | 11                    | 110x                                                                                                                                 | kkkk                     | kkkk       |  |  |  |  |

| Description:      | ment meth             | The W register is subtracted (2's comple-<br>ment method) from the eight bit literal 'k'.<br>The result is placed in the W register. |                          |            |  |  |  |  |

| Words:            | 1                     |                                                                                                                                      |                          |            |  |  |  |  |

| Cycles:           | 1                     |                                                                                                                                      |                          |            |  |  |  |  |

| Q Cycle Activity: | Q1                    | Q2                                                                                                                                   | Q3                       | Q4         |  |  |  |  |

|                   | Decode                | Read<br>literal 'k                                                                                                                   | Process<br>data          | Write to W |  |  |  |  |

| Example 1:        | SUBLW                 | 0x02                                                                                                                                 |                          |            |  |  |  |  |

|                   | Before In:            | structior                                                                                                                            | 1                        |            |  |  |  |  |

|                   |                       | W =<br>C =<br>Z =                                                                                                                    | 1<br>?<br>?              |            |  |  |  |  |

|                   | After Inst            | ruction                                                                                                                              |                          |            |  |  |  |  |

|                   |                       | W =<br>C =                                                                                                                           | 1<br>1; result i         | s positive |  |  |  |  |

|                   |                       | Z =                                                                                                                                  | 0                        |            |  |  |  |  |

| Example 2:        | Before In:            |                                                                                                                                      |                          |            |  |  |  |  |

|                   |                       | W =<br>C =                                                                                                                           | 2<br>?                   |            |  |  |  |  |

|                   |                       | Z =                                                                                                                                  | ?                        |            |  |  |  |  |

|                   | After Inst            | ruction                                                                                                                              |                          |            |  |  |  |  |

|                   |                       | W =<br>C =                                                                                                                           | 0<br>1: rocult           | ia zara    |  |  |  |  |

|                   |                       | C =<br>Z =                                                                                                                           | 1; result<br>1           | 15 2010    |  |  |  |  |

| Example 3:        | Before Instruction    |                                                                                                                                      |                          |            |  |  |  |  |

|                   |                       | W =                                                                                                                                  | 3                        |            |  |  |  |  |

|                   |                       | C =                                                                                                                                  | ?                        |            |  |  |  |  |

|                   |                       | Z =                                                                                                                                  | ?                        |            |  |  |  |  |

|                   | After Inst            | _                                                                                                                                    | ?                        |            |  |  |  |  |

|                   | After Inst            | _                                                                                                                                    |                          |            |  |  |  |  |

|                   | After Inst            | ruction                                                                                                                              | ?<br>0xFF<br>0; result i | s nega-    |  |  |  |  |

#### Applicable Devices 710 71 711 715

# 13.1 DC Characteristics: PIC16C715-04 (Commercial, Industrial, Extended) PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (

| DC CHA                         | RACTERISTICS                                                      |               |            | lard Op<br>ating ter      |                      | ture (               | ditions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)                                                                                           |

|--------------------------------|-------------------------------------------------------------------|---------------|------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min        | Тур†                      | Мах                  | Units                | Conditions                                                                                                                                                                                                                                                                                        |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5 | -                         | 5.5<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                           |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -          | 1.5                       | -                    | V                    | Device in SLEEP mode                                                                                                                                                                                                                                                                              |