#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711-20i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 GENERAL DESCRIPTION

The PIC16C71X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C710/71** devices have 36 bytes of RAM, the **PIC16C711** has 68 bytes of RAM and the **PIC16C715** has 128 bytes of RAM. Each device has 13 I/O pins. In addition a timer/counter is available. Also a 4-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C71X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C71X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C71X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

#### 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

#### 1.2 <u>Development Support</u>

PIC16C71X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 10.0 for more details about Microchip's development tools.

### 4.0 MEMORY ORGANIZATION

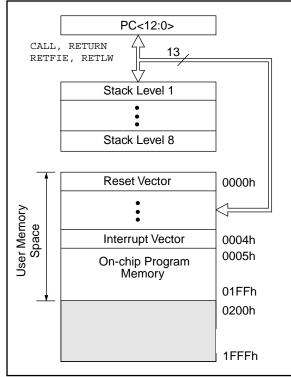

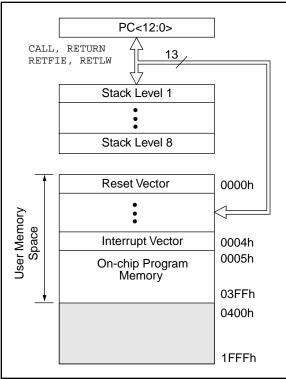

#### 4.1 Program Memory Organization

The PIC16C71X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C710 | 512 x 14          | 0000h-01FFh   |

| PIC16C71  | 1K x 14           | 0000h-03FFh   |

| PIC16C711 | 1K x 14           | 0000h-03FFh   |

| PIC16C715 | 2K x 14           | 0000h-07FFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC16C710 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-2: PIC16C71/711 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-3: PIC16C715 PROGRAM MEMORY MAP AND STACK

#### 4.2.2.2 OPTION REGISTER

#### Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

#### FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                    | R/W-1       | R/W-1       | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                                                           |

|----------|--------------------------|-------------|-------------|------------|--------------|------------|-------|-----------------------------------------------------------|

| RBPU     | INTEDG                   | TOCS        | T0SE        | PSA        | PS2          | PS1        | PS0   | R = Readable bit                                          |

| bit7     | · · ·                    |             |             |            |              |            | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

|          |                          |             |             |            |              |            |       | - n = Value at POR reset                                  |

| bit 7:   | RBPU: PC                 | RTB Pull    | -up Enabl   | le bit     |              |            |       |                                                           |

|          | 1 = PORT                 |             |             |            |              |            |       |                                                           |

|          | 0 = PORTE                | 3 pull-ups  | s are enab  | led by ind | ividual port | latch valu | es    |                                                           |

| bit 6:   | INTEDG:                  | nterrupt E  | Edge Sele   | ct bit     |              |            |       |                                                           |

|          | 1 = Interru              | pt on risir | ng edge of  | f RB0/INT  | pin          |            |       |                                                           |

|          | 0 = Interru              | pt on falli | ng edge o   | f RB0/INT  | pin          |            |       |                                                           |

| bit 5:   | TOCS: TM                 | R0 Clock    | Source S    | elect bit  |              |            |       |                                                           |

|          | 1 = Transit              |             |             |            |              |            |       |                                                           |

|          | 0 = Interna              | al instruct | ion cycle ( | clock (CLk | (OUT)        |            |       |                                                           |

| bit 4:   | TOSE: TM                 |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            | on RA4/T0    |            |       |                                                           |

|          | 0 = Increm               | ent on lo   | w-to-high   | transition | on RA4/T00   | JKI pin    |       |                                                           |

| bit 3:   | PSA: Pres                |             | 0           |            |              |            |       |                                                           |

|          | 1 = Presca<br>0 = Presca |             |             |            | modulo       |            |       |                                                           |

|          |                          |             | •           |            | module       |            |       |                                                           |

| bit 2-0: | PS2:PS0:                 | Prescale    | r Rate Sel  | lect bits  |              |            |       |                                                           |

|          | Bit Value                | TMR0 R      | ate WD      | Γ Rate     |              |            |       |                                                           |

|          | 000                      | 1:2         | 1:          |            |              |            |       |                                                           |

|          | 001                      | 1:4         | 1:          |            |              |            |       |                                                           |

|          | 010<br>011               | 1:8         | 1:          |            |              |            |       |                                                           |

|          | 100                      | 1:16        |             | 16         |              |            |       |                                                           |

|          | 101                      | 1:64        | . 1:        | 32         |              |            |       |                                                           |

|          | 110                      | 1 : 12      |             | 64         |              |            |       |                                                           |

|          | 111                      | 1:25        | 6   1       | 128        |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

#### 5.0 I/O PORTS

#### Applicable Devices 710 71 711 715

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

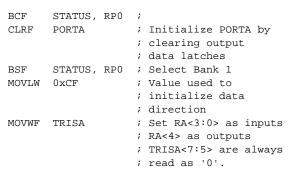

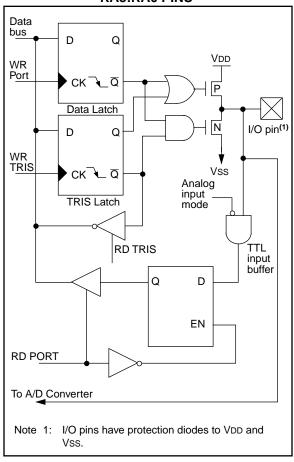

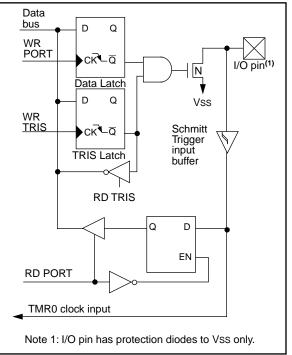

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 5-1: INITIALIZING PORTA

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 PINS

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

#### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |

|--------------|------|--------|-------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                    |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                    |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                    |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |

|              |      |        | Output is open drain type                       |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3                         | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|---------|-------------------------------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | —     | _     | RA4     | RA3                           | RA2   | RA1   | RA0   | x 0000                   | u 0000                    |

| 85h     | TRISA  | —     | —     | _     | PORTA D | PORTA Data Direction Register |       |       |       | 1 1111                   | 1 1111                    |

| 9Fh     | ADCON1 | _     | _     | _     | _       | _                             |       | PCFG1 | PCFG0 | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

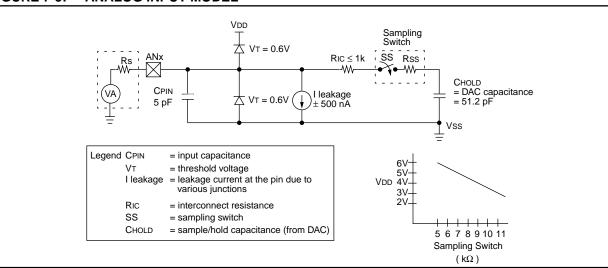

#### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

#### EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

#### FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

#### 7.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

#### 7.6 <u>A/D Accuracy/Error</u>

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at <  $\pm$ 1 LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from TOSC, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 7.7 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

#### 7.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | Care must be taken when using the RA0       |

|-------|---------------------------------------------|

|       | pin in A/D conversions due to its proximity |

|       | to the OSC1 pin.                            |

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

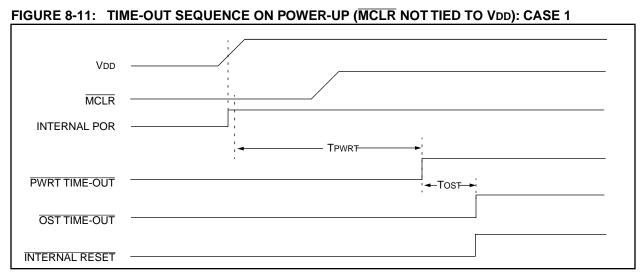

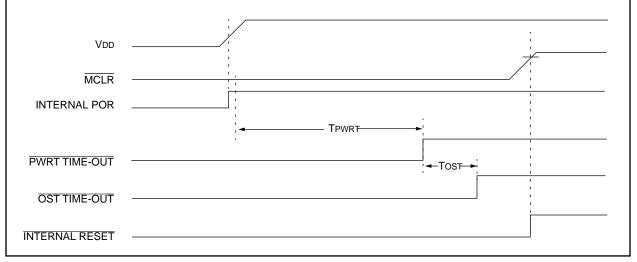

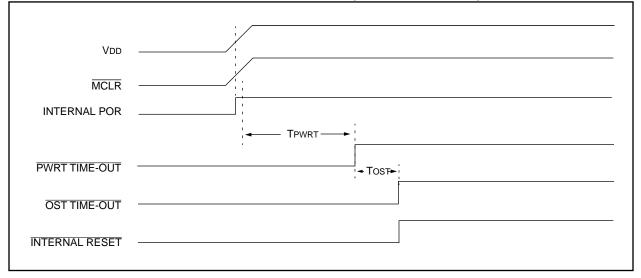

FIGURE 8-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### FIGURE 8-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 8.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 8.8 for details on SLEEP mode.

#### 8.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). (Section 6.0)

#### 8.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

For the PIC16C71 Note: if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

|                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                     |

|--------------------------|-------------------|-------------------|--------------------------------------------|-------------------|---------------------------------------|

| OSC1 /                   |                   |                   |                                            |                   |                                       |

| CLKOUT ③                 | (4)               |                   |                                            | /                 |                                       |

| INT pin                  |                   | 1                 | 1<br>1<br>1<br>1                           |                   | 1 1<br>1 1<br>1 1<br>1 1              |

| INTF flag<br>(INTCON<1>) |                   |                   | Interrupt Latency (2)                      |                   |                                       |

| GIE bit<br>(INTCON<7>)   |                   |                   |                                            |                   |                                       |

| INSTRUCTION              | FLOW              |                   | ,<br>, , , , , , , , , , , , , , , , , , , |                   | · · · · · · · · · · · · · · · · · · · |

| PC                       | PC                | PC+1              | PC+1                                       | X 0004h           | X 0005h                               |

| Instruction (<br>fetched | Inst (PC)         | Inst (PC+1)       | _                                          | Inst (0004h)      | Inst (0005h)                          |

| Instruction {            | Inst (PC-1)       | Inst (PC)         | Dummy Cycle                                | Dummy Cycle       | Inst (0004h)                          |

|                          |                   |                   |                                            |                   |                                       |

#### FIGURE 8-19: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode. 4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

### 10.0 DEVELOPMENT SUPPORT

#### 10.1 <u>Development Tools</u>

The PICmicro<sup>™</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

#### 10.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 10.3 ICEPIC: Low-Cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket. Applicable Devices 710 71 711 715

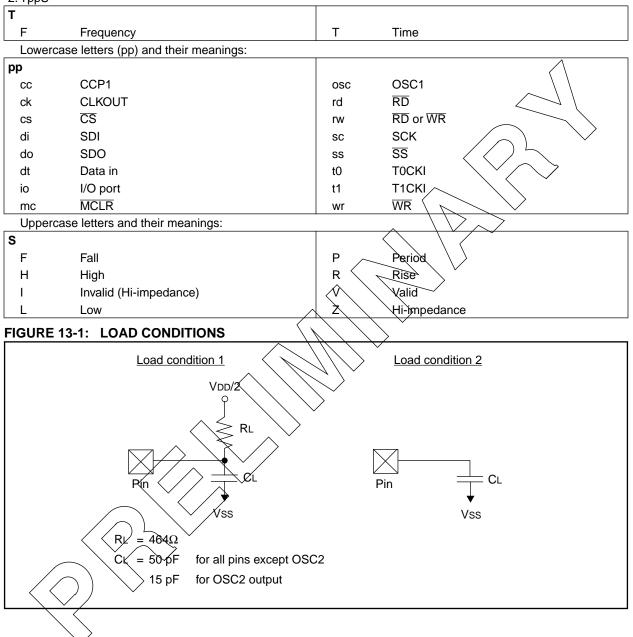

#### 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

#### 1. TppS2ppS

2. TppS

| 2. 1990 |                                       |     |              |  |

|---------|---------------------------------------|-----|--------------|--|

| Т       |                                       |     |              |  |

| F       | Frequency                             | Т   | Time         |  |

| Lowerc  | case letters (pp) and their meanings: |     |              |  |

| рр      |                                       |     |              |  |

| сс      | CCP1                                  | osc | OSC1         |  |

| ck      | CLKOUT                                | rd  | RD           |  |

| cs      | CS                                    | rw  | RD or WR     |  |

| di      | SDI                                   | sc  | SCK          |  |

| do      | SDO                                   | SS  | SS           |  |

| dt      | Data in                               | tO  | TOCKI        |  |

| io      | I/O port                              | t1  | T1CKI        |  |

| mc      | MCLR                                  | wr  | WR           |  |

| Upperc  | case letters and their meanings:      |     |              |  |

| S       |                                       |     |              |  |

| F       | Fall                                  | P   | Period       |  |

| н       | High                                  | R   | Rise         |  |

| I       | Invalid (Hi-impedance)                | V   | Valid        |  |

| L       | Low                                   | Z   | Hi-impedance |  |

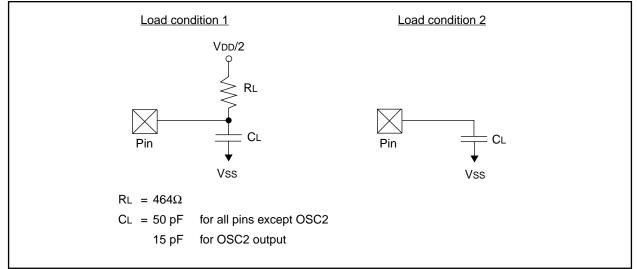

#### FIGURE 11-1: LOAD CONDITIONS

#### Applicable Devices 710 71 711 715

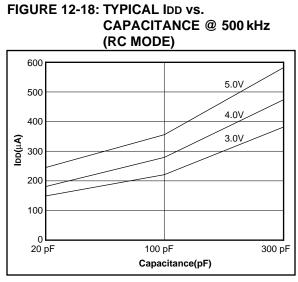

#### TABLE 12-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average         |        |  |  |  |

|--------|------|-----------------|--------|--|--|--|

| Cext   | Rext | Fosc @ 5V, 25°C |        |  |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |  |

|        | 100k | 268 kHz         | ± 1.1% |  |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ± 1.0% |  |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |  |

|        | 100k | 77.2 kHz        | ± 1.0% |  |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |  |

|        | 5k   | 501 kHz         | ± 1.2% |  |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

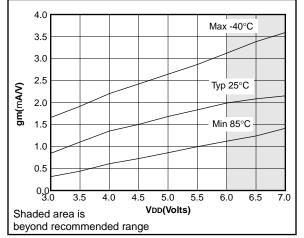

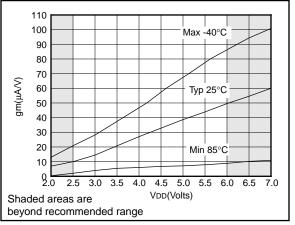

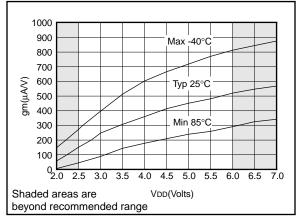

#### FIGURE 12-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

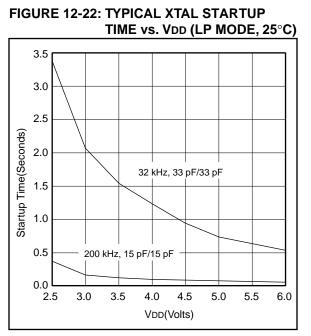

#### FIGURE 12-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

#### FIGURE 12-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

## Applicable Devices 710 71 711 715

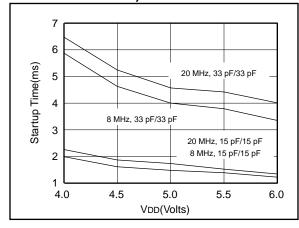

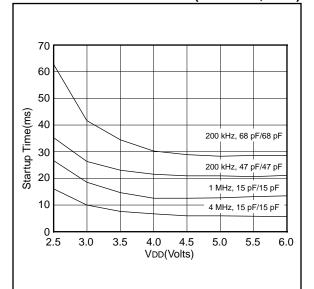

FIGURE 12-23: TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

#### FIGURE 12-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

#### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

|                  |                 | <b>A B</b>       | <b>a b</b>       |  |  |  |

|------------------|-----------------|------------------|------------------|--|--|--|

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |

| LP               | 32 kHz          | 33 pF            | 33 pF            |  |  |  |

|                  | 200 kHz         | 15 pF            | 15 pF            |  |  |  |

| ХТ               | 200 kHz         | 47-68 pF         | 47-68 pF         |  |  |  |

|                  | 1 MHz           | 15 pF            | 15 pF            |  |  |  |

|                  | 4 MHz           | 15 pF            | 15 pF            |  |  |  |

| HS               | 4 MHz           | 15 pF            | 15 pF            |  |  |  |

|                  | 8 MHz           | 15-33 pF         | 15-33 pF         |  |  |  |

|                  | 20 MHz          | 15-33 pF         | 15-33 pF         |  |  |  |

|                  |                 |                  |                  |  |  |  |

| Crystals<br>Used |                 |                  |                  |  |  |  |

| 32 kHz           | Epson C-00      | 01R32.768K-A     | ± 20 PPM         |  |  |  |

| 200 kHz          | STD XTL 2       | 00.000KHz        | ± 20 PPM         |  |  |  |

| 1 MHz            | ECS ECS-1       | 10-13-1          | ± 50 PPM         |  |  |  |

| 4 MHz            | ECS ECS-4       | ECS ECS-40-20-1  |                  |  |  |  |

| 8 MHz            | EPSON CA        | -301 8.000M-C    | ± 30 PPM         |  |  |  |

| 20 MHz           | EPSON CA        | -301 20.000M-C   | ± 30 PPM         |  |  |  |

#### Applicable Devices 710 71 711 715

# 13.1 DC Characteristics: PIC16C715-04 (Commercial, Industrial, Extended) PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (

| DC CHA                         | RACTERISTICS                                                      |               |            | lard Op<br>ating ter      |                      | ture (               | ditions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)                                                                                           |

|--------------------------------|-------------------------------------------------------------------|---------------|------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min        | Тур†                      | Мах                  | Units                | Conditions                                                                                                                                                                                                                                                                                        |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5 | -                         | 5.5<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                           |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -          | 1.5                       | -                    | V                    | Device in SLEEP mode                                                                                                                                                                                                                                                                              |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -          | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD          | 0.05       | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |

| D005                           | Brown-out Reset Voltage                                           | Bvdd          | 3.7        | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                           | IDD           | -          | 2.7                       | 5                    | mA .                 | XT, RC osc configuration (PIC16C715-04)<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                      |

| D013                           |                                                                   |               | -          | 13.5                      | 30                   | mA                   | HS øsc configuration (PIC16C715-20)<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ IBOR | -<         | 300*                      | 500                  | ha ~                 | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD <         | -          | 10,5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 4.0V, WDT enabled, -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -0^{\circ}C \text{ to } +70^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +125^{\circ}C$ |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | ALBOR         |            | >300*                     | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 51, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which Vod can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

(The)test conditions for all IDD measurements in active operation mode are:

OSCT = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## PIC16C71X

#### Applicable Devices 710 71 711 715

#### 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

#### Applicable Devices71071711715

#### 15.1 DC Characteristics: PIC16C71-04 (Commercial, Industrial) PIC16C71-20 (Commercial, Industrial)

| DC CHARACTERISTICS    |                                                                  |      |            | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) |                |                |                                                                                                                                                                                            |  |  |  |

|-----------------------|------------------------------------------------------------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.          | Characteristic                                                   | Sym  | Min        | Тур†                                                                                                                                                                                       | Max            | Units          | Conditions                                                                                                                                                                                 |  |  |  |

| D001<br>D001A         | Supply Voltage                                                   | Vdd  | 4.0<br>4.5 |                                                                                                                                                                                            | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                    |  |  |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -          | 1.5                                                                                                                                                                                        | -              | V              |                                                                                                                                                                                            |  |  |  |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -          | Vss                                                                                                                                                                                        | -              | V              | See section on Power-on Reset for details                                                                                                                                                  |  |  |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD | 0.05       | -                                                                                                                                                                                          | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                  |  |  |  |

| D010                  | Supply Current (Note 2)                                          | IDD  | -          | 1.8                                                                                                                                                                                        | 3.3            | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                              |  |  |  |

| D013                  |                                                                  |      | -          | 13.5                                                                                                                                                                                       | 30             | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                          |  |  |  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3)                                   | IPD  |            | 7<br>1.0<br>1.0                                                                                                                                                                            | 28<br>14<br>16 | μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, $-40^{\circ}$ C to $+85^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-0^{\circ}$ C to $+70^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to $+85^{\circ}$ C |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

Applicable Devices 710 71 711 715

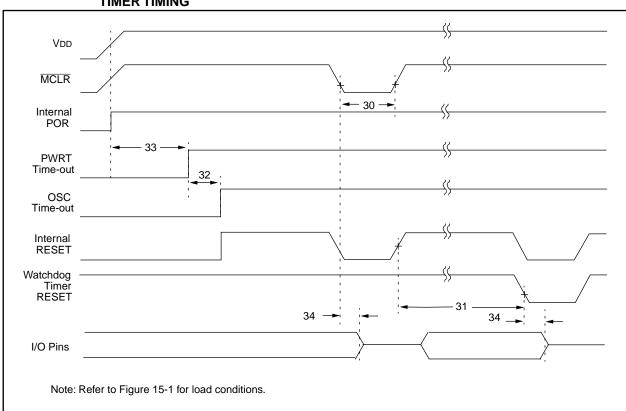

## FIGURE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 15-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†      | Мах  | Units | Conditions               |

|------------------|-------|--------------------------------------------------|-----|-----------|------|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 200 | —         | _    | ns    | VDD = 5V, -40°C to +85°C |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*  | 18        | 33*  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | _   | 1024 Tosc | -    | —     | Tosc = OSC1 period       |

| 33               | Tpwrt | Power-up Timer Period                            | 28* | 72        | 132* | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O High Impedance from MCLR<br>Low              | —   | —         | 100  | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

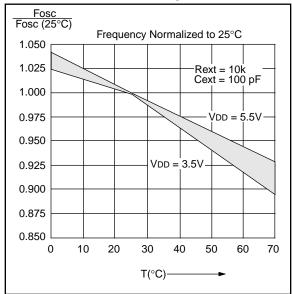

### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C71

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

#### FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

Applicable Devices71071711715

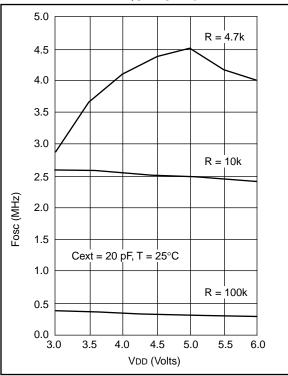

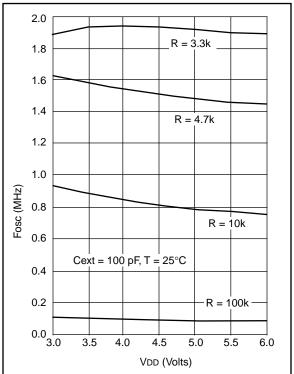

#### FIGURE 16-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

FIGURE 16-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### **ON-LINE SUPPORT**

Microchip provides two methods of on-line support. These are the Microchip BBS and the Microchip World Wide Web (WWW) site.

Use Microchip's Bulletin Board Service (BBS) to get current information and help about Microchip products. Microchip provides the BBS communication channel for you to use in extending your technical staff with microcontroller and memory experts.

To provide you with the most responsive service possible, the Microchip systems team monitors the BBS, posts the latest component data and software tool updates, provides technical help and embedded systems insights, and discusses how Microchip products provide project solutions.

The web site, like the BBS, is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.futureone.com/pub/microchip

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

#### **Connecting to the Microchip BBS**

Connect worldwide to the Microchip BBS using either the Internet or the CompuServe  $^{\circledast}$  communications network.

#### Internet:

You can telnet or ftp to the Microchip BBS at the address: mchipbbs.microchip.com

#### **CompuServe Communications Network:**

When using the BBS via the Compuserve Network, in most cases, a local call is your only expense. The Microchip BBS connection does not use CompuServe membership services, therefore you do not need CompuServe membership to join Microchip's BBS. There is no charge for connecting to the Microchip BBS. The procedure to connect will vary slightly from country to country. Please check with your local CompuServe agent for details if you have a problem. CompuServe service allow multiple users various baud rates depending on the local point of access.

The following connect procedure applies in most locations.

- 1. Set your modem to 8-bit, No parity, and One stop (8N1). This is not the normal CompuServe setting which is 7E1.

- 2. Dial your local CompuServe access number.

- 3. Depress the **<Enter>** key and a garbage string will appear because CompuServe is expecting a 7E1 setting.

- Type +, depress the <Enter> key and "Host Name:" will appear.

- 5. Type MCHIPBBS, depress the **<Enter>** key and you will be connected to the Microchip BBS.

In the United States, to find the CompuServe phone number closest to you, set your modem to 7E1 and dial (800) 848-4480 for 300-2400 baud or (800) 331-7166 for 9600-14400 baud connection. After the system responds with "Host Name:", type NETWORK, depress the **<Enter>** key and follow CompuServe's directions.

For voice information (or calling from overseas), you may call (614) 723-1550 for your local CompuServe number.

Microchip regularly uses the Microchip BBS to distribute technical information, application notes, source code, errata sheets, bug reports, and interim patches for Microchip systems software products. For each SIG, a moderator monitors, scans, and approves or disapproves files submitted to the SIG. No executable files are accepted from the user community in general to limit the spread of computer viruses.

#### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-602-786-7302 for the rest of the world.

970301

**Trademarks:** The Microchip name, logo, PIC, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB and *fuzzy*LAB, are trademarks and SQTP is a service mark of Microchip in the U.S.A.

*fuzzy*TECH is a registered trademark of Inform Software Corporation. IBM, IBM PC-AT are registered trademarks of International Business Machines Corp. Pentium is a trademark of Intel Corporation. Windows is a trademark and MS-DOS, Microsoft Windows are registered trademarks of Microsoft Corporation. CompuServe is a registered trademark of CompuServe Incorporated.

All other trademarks mentioned herein are the property of their respective companies.

NOTES: