Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711t-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

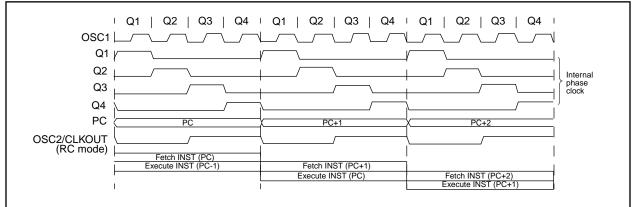

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

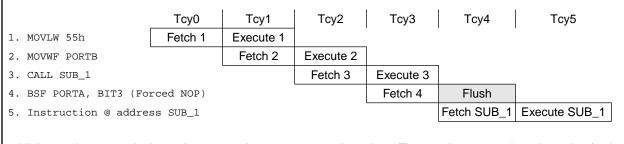

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name   | Bit 7              | Bit 6                                         | Bit 5         | Bit 4        | Bit 3                                                    | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(1) |

|----------------------|--------|--------------------|-----------------------------------------------|---------------|--------------|----------------------------------------------------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |        |                    |                                               |               | •            | •                                                        |                  |               |           |                          |                                     |

| 00h <sup>(3)</sup>   | INDF   | Addressing         | this location                                 | uses conten   | ts of FSR to | address dat                                              | a memory (no     | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0   | Timer0 mod         | imer0 module's register                       |               |              |                                                          |                  |               |           |                          | uuuu uuuu                           |

| 02h <sup>(3)</sup>   | PCL    | Program Co         | Program Counter's (PC) Least Significant Byte |               |              |                                                          |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(3)</sup>   | STATUS | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                            | RP0           | TO           | PD                                                       | Z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(3)</sup>   | FSR    | Indirect data      | a memory ad                                   | dress pointe  | r            |                                                          |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA  | _                  | —                                             | —             | PORTA Dat    | a Latch whe                                              | n written: PO    | RTA pins wh   | en read   | x 0000                   | u 0000                              |

| 06h                  | PORTB  | PORTB Dat          | a Latch whe                                   | n written: PC | DRTB pins wł | nen read                                                 |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | —      | Unimpleme          | nted                                          |               |              |                                                          |                  |               |           | —                        | —                                   |

| 08h                  | ADCON0 | ADCS1              | ADCS0                                         | (6)           | CHS1         | CHS0                                                     | GO/DONE          | ADIF          | ADON      | 00-0 0000                | 00-0 0000                           |

| 09h <sup>(3)</sup>   | ADRES  | A/D Result         | Register                                      |               |              |                                                          |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Ah <sup>(2,3)</sup> | PCLATH | _                  | —                                             | _             | Write Buffer | Nrite Buffer for the upper 5 bits of the Program Counter |                  |               |           |                          | 0 0000                              |

| 0Bh <b>(3)</b>       | INTCON | GIE                | ADIE                                          | TOIE          | INTE         | RBIE                                                     | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| Bank 1               |        |                    |                                               |               |              |                                                          |                  |               |           |                          |                                     |

| 80h <sup>(3)</sup>   | INDF   | Addressing         | this location                                 | uses conten   | ts of FSR to | address dat                                              | a memory (no     | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION | RBPU               | INTEDG                                        | TOCS          | TOSE         | PSA                                                      | PS2              | PS1           | PS0       | 1111 1111                | 1111 1111                           |

| 82h <sup>(3)</sup>   | PCL    | Program Co         | ounter's (PC)                                 | Least Signif  | icant Byte   |                                                          |                  |               |           | 0000 0000                | 0000 0000                           |

| 83h <sup>(3)</sup>   | STATUS | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                            | RP0           | TO           | PD                                                       | z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(3)</sup>   | FSR    | Indirect data      | a memory ad                                   | dress pointe  | er           |                                                          |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA  | —                  | —                                             | —             | PORTA Dat    | a Direction F                                            | Register         |               |           | 1 1111                   | 1 1111                              |

| 86h                  | TRISB  | PORTB Dat          | a Direction C                                 | Control Regis | ster         |                                                          |                  |               |           | 1111 1111                | 1111 1111                           |

| 87h <sup>(4)</sup>   | PCON   | —                  | —                                             | —             | _            | —                                                        | _                | POR           | BOR       | dd                       | uu                                  |

| 88h                  | ADCON1 | —                  | —                                             | _             | _            | _                                                        | —                | PCFG1         | PCFG0     | 00                       | 00                                  |

| 89h <sup>(3)</sup>   | ADRES  | A/D Result         | Register                                      |               |              |                                                          |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 8Ah <sup>(2,3)</sup> | PCLATH | _                  | —                                             | —             | Write Buffer | for the uppe                                             | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(3)</sup>   | INTCON | GIE                | ADIE                                          | TOIE          | INTE         | RBIE                                                     | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

# TABLE 4-1: PIC16C710/71/711 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: These registers can be addressed from either bank.

4: The PCON register is not physically implemented in the PIC16C71, read as '0'.

5: The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear.

6: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

#### 4.2.2.2 OPTION REGISTER

# Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

# FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                    | R/W-1       | R/W-1       | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                                                           |

|----------|--------------------------|-------------|-------------|------------|--------------|------------|-------|-----------------------------------------------------------|

| RBPU     | INTEDG                   | TOCS        | T0SE        | PSA        | PS2          | PS1        | PS0   | R = Readable bit                                          |

| bit7     | · · ·                    |             |             |            |              |            | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

|          |                          |             |             |            |              |            |       | - n = Value at POR reset                                  |

| bit 7:   | RBPU: PC                 | RTB Pull    | -up Enabl   | le bit     |              |            |       |                                                           |

|          | 1 = PORT                 |             |             |            |              |            |       |                                                           |

|          | 0 = PORTE                | 3 pull-ups  | s are enab  | led by ind | ividual port | latch valu | es    |                                                           |

| bit 6:   | INTEDG:                  | nterrupt E  | Edge Sele   | ct bit     |              |            |       |                                                           |

|          | 1 = Interru              | pt on risir | ng edge of  | f RB0/INT  | pin          |            |       |                                                           |

|          | 0 = Interru              | pt on falli | ng edge o   | f RB0/INT  | pin          |            |       |                                                           |

| bit 5:   | TOCS: TM                 | R0 Clock    | Source S    | elect bit  |              |            |       |                                                           |

|          | 1 = Transit              |             |             |            |              |            |       |                                                           |

|          | 0 = Interna              | al instruct | ion cycle ( | clock (CLk | (OUT)        |            |       |                                                           |

| bit 4:   | TOSE: TM                 |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            | on RA4/T0    |            |       |                                                           |

|          | 0 = Increm               | ent on lo   | w-to-high   | transition | on RA4/T00   | JKI pin    |       |                                                           |

| bit 3:   | PSA: Pres                |             | 0           |            |              |            |       |                                                           |

|          | 1 = Presca<br>0 = Presca |             |             |            | modulo       |            |       |                                                           |

|          |                          |             | •           |            | module       |            |       |                                                           |

| bit 2-0: | PS2:PS0:                 | Prescale    | r Rate Sel  | lect bits  |              |            |       |                                                           |

|          | Bit Value                | TMR0 R      | ate WD      | Γ Rate     |              |            |       |                                                           |

|          | 000                      | 1:2         | 1:          |            |              |            |       |                                                           |

|          | 001                      | 1:4         | 1:          |            |              |            |       |                                                           |

|          | 010<br>011               | 1:8         | 1:          |            |              |            |       |                                                           |

|          | 100                      | 1:16        |             | 16         |              |            |       |                                                           |

|          | 101                      | 1:64        | . 1:        | 32         |              |            |       |                                                           |

|          | 110                      | 1 : 12      |             | 64         |              |            |       |                                                           |

|          | 111                      | 1:25        | 6   1       | 128        |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

#### 4.2.2.3 INTCON REGISTER

# Applicable Devices 710 71 711 715

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

### FIGURE 4-9: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0   | R/W-0                                                  | R/W-0        | R/W-0        | R/W-0                                      | R/W-0                            | R/W-0       | R/W-x        |                                                                                       |

|---------|--------------------------------------------------------|--------------|--------------|--------------------------------------------|----------------------------------|-------------|--------------|---------------------------------------------------------------------------------------|

| GIE     | ADIE                                                   | TOIE         | INTE         | RBIE                                       | TOIF                             | INTF        | RBIF         | R = Readable bit                                                                      |

| bit7    |                                                        |              |              | -                                          |                                  |             | bitO         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:  | <b>GIE:<sup>(1)</sup></b> GI<br>1 = Enabl<br>0 = Disab | es all un-r  | nasked in    |                                            |                                  |             |              |                                                                                       |

| bit 6:  | ADIE: A/E<br>1 = Enabl<br>0 = Disab                    | es A/D int   | errupt       | t Enable b                                 | bit                              |             |              |                                                                                       |

| bit 5:  |                                                        | es the TM    | R0 interru   |                                            | bit                              |             |              |                                                                                       |

| bit 4:  | 1 = Enabl                                              | es the RB    | 0/INT exte   | rupt Enab<br>ernal interi<br>ernal inter   | rupt                             |             |              |                                                                                       |

| bit 3:  | 1 = Enabl                                              | es the RB    | port char    | upt Enable<br>nge interru<br>nge interru   | pt                               |             |              |                                                                                       |

| bit 2:  | <b>TOIF:</b> TMF<br>1 = TMR0<br>0 = TMR0               | ) register h | nas overflo  | wed (mus                                   | t be cleare                      | d in softwa | ire)         |                                                                                       |

| bit 1:  | 1 = The R                                              | B0/INT ex    | cternal inte | rupt Flag b<br>errupt occu<br>errupt did i | urred (must                      | be cleare   | d in softwar | e)                                                                                    |

| bit 0:  | 1 = At lea                                             | st one of    | the RB7:R    |                                            | it<br>nanged stat<br>anged state |             | e cleared in | software)                                                                             |

| Note 1: |                                                        | -enabled l   | oy the RET   |                                            |                                  |             |              | ed, the GIE bit may be uninten-<br>ce Routine. Refer to Section 8.5                   |

| globa   |                                                        | GIE (INTC    |              |                                            |                                  |             |              | corresponding enable bit or the rupt flag bits are clear prior to                     |

# 7.4 <u>A/D Conversions</u>

Example 7-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0). **Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

# EXAMPLE 7-2: A/D CONVERSION

| BSF    | STATUS,     | RP0        | ; Select Bank 1                                          |

|--------|-------------|------------|----------------------------------------------------------|

| CLRF   | ADCON1      |            | ; Configure A/D inputs                                   |

| BCF    | STATUS,     | RP0        | ; Select Bank 0                                          |

| MOVL   | W 0xCl      |            | ; RC Clock, A/D is on, Channel 0 is selected             |

| MOVW   | F ADCON0    |            | ;                                                        |

| BSF    | INTCON,     | ADIE       | ; Enable A/D Interrupt                                   |

| BSF    | INTCON,     | GIE        | ; Enable all interrupts                                  |

|        |             |            |                                                          |

| Ensure | that the re | equired sa | ampling time for the selected input channel has elapsed. |

Then the conversion may be started.

;

;;

;

| BSF | ADCON0, GO | ; Start A/D Conversion                              |

|-----|------------|-----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit      |

| :   |            | ; is cleared upon completion of the A/D Conversion. |

# FIGURE 8-2: CONFIGURATION WORD, PIC16C710/711

| CP0 C                      | P0 CI                                      | P0 CP0                                                                           | CP0                                   | CP0     | CP0     | BODEN | CP0     | CP0      | PWRTE    | WDTE   | FOSC1 | FOSC0 | Register:      | CONFIG |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------|---------|-------|---------|----------|----------|--------|-------|-------|----------------|--------|

| bit13                      |                                            | •                                                                                |                                       |         |         |       |         |          |          |        |       | bit0  | Address        | 2007h  |

| bit 13-7<br>5-4:<br>bit 6: | 1 = Co<br>0 = All<br><b>BODE</b><br>1 = BC | Code prote<br>ode protec<br>memory<br><b>N:</b> Brown<br>OR enable<br>OR disable | ction off<br>is code<br>-out Re<br>ed | protec  |         |       | Fh is w | vritable |          |        |       |       |                |        |

| bit 3:                     | 1 = PV                                     | <b>Ē:</b> Power<br>VRT disal<br>VRT enat                                         | bled                                  | er Ena  | ble bit | (1)   |         |          |          |        |       |       |                |        |

| bit 2:                     | 1 = W                                      | : Watchd<br>DT enable<br>DT disabl                                               | ed                                    | er Enab | le bit  |       |         |          |          |        |       |       |                |        |

| bit 1-0:                   | 11 = F<br>10 = F<br>01 = X                 | 1:FOSC0<br>RC oscilla<br>IS oscillat<br>(T oscillat<br>P oscillat                | tor<br>tor<br>tor                     | ator Se | lection | bits  |         |          |          |        |       |       |                |        |

| Note 1:                    | Ensur                                      | e the Pow                                                                        | er-up T                               | imer is | enable  |       | ne Brov | vn-out l | Reset is | enable | d.    |       | value of bit F | PWRTE. |

#### 2: All of the CP0 bits have to be given the same value to enable the code protection scheme listed.

# FIGURE 8-3: CONFIGURATION WORD, PIC16C715

| CP1             | CP0               | CP1                                           | CP0                           | CP1                           | CP0                    | MPEEN                               | BODEN                  | CP1    | CP0   | PWRTE     | WDTE     | FOSC1    | FOSC0      | Register:    | CONFIG |

|-----------------|-------------------|-----------------------------------------------|-------------------------------|-------------------------------|------------------------|-------------------------------------|------------------------|--------|-------|-----------|----------|----------|------------|--------------|--------|

| bit13           |                   |                                               |                               |                               |                        |                                     |                        |        |       |           |          |          | bit0       | Address      | 2007h  |

| bit 13-8<br>5-4 | 4: 11<br>10<br>01 | L = Up                                        | de prot<br>per hal<br>per 3/4 | ection<br>f of pro<br>th of p | off<br>ogram<br>rogran | memory                              | r code pr<br>ry code p |        |       |           |          |          |            |              |        |

| bit 7:          | 1                 | = Mem                                         | ory Pa                        | rity Ch                       | ecking                 | or Enabl<br>g is enat<br>g is disal | oled                   |        |       |           |          |          |            |              |        |

| bit 6:          | 1                 | <b>oden</b> :<br>= Bor<br>= Bor               | enable                        | ed                            | Reset E                | Enable b                            | <sub>it</sub> (1)      |        |       |           |          |          |            |              |        |

| bit 3:          | 1                 | <b>WRTE</b> :<br>= PWF<br>= PWF               | RT disa                       | bled                          | mer Ei                 | nable bit                           | (1)                    |        |       |           |          |          |            |              |        |

| bit 2:          | 1                 | <b>DTE:</b> \<br>= WDT<br>= WDT               | enabl                         | ed                            | ner En                 | able bit                            |                        |        |       |           |          |          |            |              |        |

| bit 1-0         | 11<br>10<br>01    | DSC1:<br>L = RC<br>D = HS<br>L = XT<br>D = LP | oscilla<br>oscilla<br>oscilla | ator<br>itor<br>tor           | llator \$              | Selectior                           | n bits                 |        |       |           |          |          |            |              |        |

| Note 7          |                   |                                               |                               |                               |                        |                                     | cally ena<br>ed anytir |        | •     |           | ,        | 0        | ess of the | value of bit | PWRTE. |

|                 | 2: Al             | l of the                                      | CP1:0                         | CP0 pa                        | airs ha                | ve to be                            | given the              | e same | value | to enable | e the co | de prote | ection sch | eme listed.  |        |

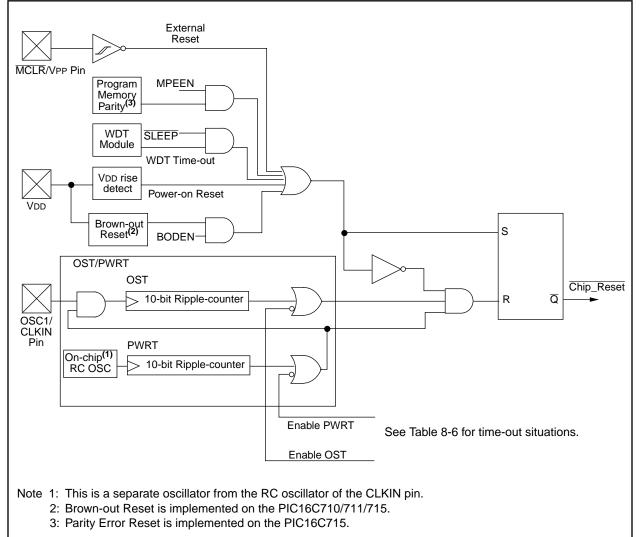

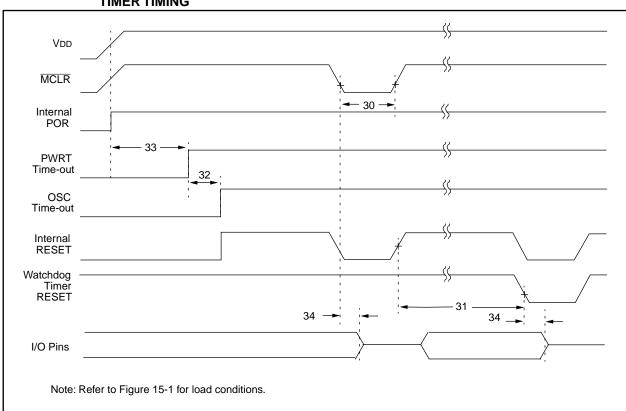

# 8.3 <u>Reset</u>

# Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and

WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

# FIGURE 8-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

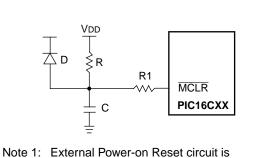

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

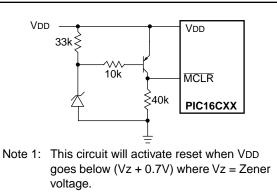

# FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

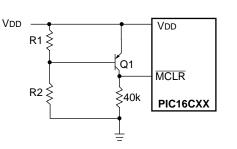

# FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

# 9.0 INSTRUCTION SET SUMMARY

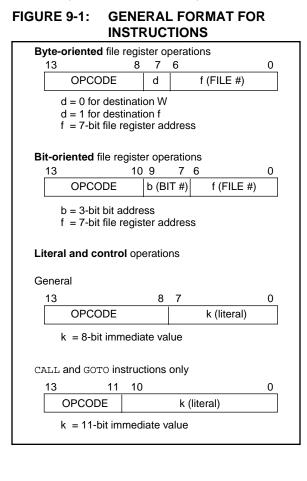

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 9-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 9-2 lists the instructions recognized by the MPASM assembler.

Figure 9-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# TABLE 9-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | Э    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIEI |        | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL AN |        | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| OUDLIN     |        |                              |        |     |        |        |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                      |                                                                               |                                                |                                    |                                                          |                                                  | 、                                                   |                                   |                                      |          |          |            |                                       |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------|-------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----------------------------------|--------------------------------------|----------|----------|------------|---------------------------------------|

|                            |                                                    |                                       |                                                    |                      |                                                                               |                                                |                                    |                                                          |                                                  | 7                                                   | 2                                 |                                      |          |          |            | 7                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                      |                                                                               |                                                | 2                                  |                                                          |                                                  | 7                                                   |                                   | 2                                    |          |          |            |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 2                    |                                                                               |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC17C4X                   | 2                                                  |                                       | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C9XX                  | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          | 7          |                                       |

| PIC16C8X                   | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C7XX                  | 7                                                  | 7                                     | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16C6X                   | 7                                                  | 7                                     | 7                                                  | 2                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16CXXX                  | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 2        |          |            |                                       |

| PIC16C5X                   | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC14000                   | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC12C5XX                  | >                                                  | 7                                     | 7                                                  | >                    | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

|                            | PICMASTER®/<br>PICMASTER-CE<br>In-Circuit Emulator | CEPIC Low-Cost<br>In-Circuit Emulator | MPLAB™<br>Integrated<br>Development<br>Environment | MPLAB™ C<br>compiler | Lo fuzzyTECH <sup>®</sup> .MP<br>Explorer/Edition<br>Fuzzy Logic<br>Dev. Tool | MP-DriveWay™<br>Applications<br>Code Generator | Total Endurance™<br>Software Model | PICSTART <sup>®</sup><br>Lite Ultra Low-Cost<br>Dev. Kit | PICSTART®<br>Plus Low-Cost<br>Universal Dev. Kit | PRO MATE <sup>®</sup> II<br>Universal<br>Programmer | KEELOQ <sup>®</sup><br>Programmer | SEEVAL <sup>®</sup><br>Designers Kit | PICDEM-1 | PICDEM-2 | e PICDEM-3 | KEELOQ <sup>®</sup><br>Evaluation Kit |

# TABLE 10-1: DEVELOPMENT TOOLS FROM MICROCHIP

# 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

#### 1. TppS2ppS

2. TppS

| Т      |                                      |     |              |  |

|--------|--------------------------------------|-----|--------------|--|

| F      | Frequency                            | Т   | Time         |  |

| Lowerc | ase letters (pp) and their meanings: |     |              |  |

| рр     |                                      |     |              |  |

| сс     | CCP1                                 | osc | OSC1         |  |

| ck     | CLKOUT                               | rd  | RD           |  |

| CS     | CS                                   | rw  | RD or WR     |  |

| di     | SDI                                  | sc  | SCK          |  |

| do     | SDO                                  | SS  | SS           |  |

| dt     | Data in                              | tO  | TOCKI        |  |

| io     | I/O port                             | t1  | T1CKI        |  |

| mc     | MCLR                                 | wr  | WR           |  |

| Upperc | case letters and their meanings:     |     |              |  |

| S      |                                      |     |              |  |

| F      | Fall                                 | P   | Period       |  |

| н      | High                                 | R   | Rise         |  |

| I      | Invalid (Hi-impedance)               | V   | Valid        |  |

| L      | Low                                  | Z   | Hi-impedance |  |

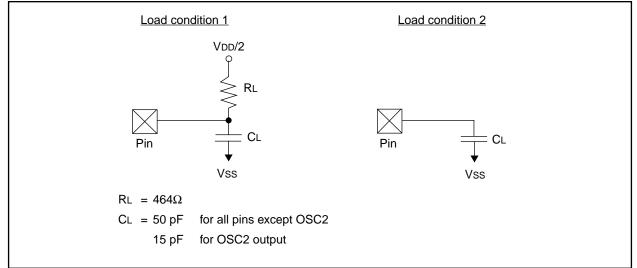

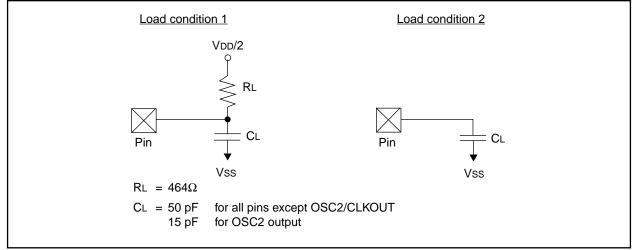

# FIGURE 11-1: LOAD CONDITIONS

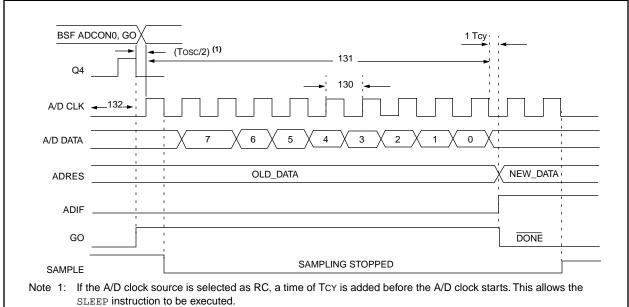

# FIGURE 11-7: A/D CONVERSION TIMING

#### **TABLE 11-7: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                                        |                        | Min    | Тур†    | Мах | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|-------------------------------------------------------|------------------------|--------|---------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                      | PIC16 <b>C</b> 710/711 | 1.6    | _       | _   | μs    | Tosc based, VREF $\ge 3.0V$                                                                                                                                                                                                |

|              |      |                                                       | PIC16LC710/711         | 2.0    | _       | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                                |

|              |      |                                                       | PIC16 <b>C</b> 710/711 | 2.0*   | 4.0     | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                |

|              |      |                                                       | PIC16LC710/711         | 3.0*   | 6.0     | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                |

| 131          | TCNV | Conversion time<br>(not including S/H time). (Note 1) |                        | —      | 9.5     |     | TAD   |                                                                                                                                                                                                                            |

| 132          | TACQ | Acquisition time                                      |                        | Note 2 | 20      | _   | μs    |                                                                                                                                                                                                                            |

|              |      |                                                       |                        | 5*     | _       | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if the<br>"new" input voltage has not changed<br>by more than 1 LSb (i.e., 19.5 mV @<br>5.12V) from the last sampled voltage<br>(as stated on CHOLD). |

| 134          | TGO  | Q4 to AD clock start                                  |                        |        | Tosc/2§ |     | _     | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                           |

| 135          | Tswc | Switching from co                                     | 1.5§                   | _      |         | TAD |       |                                                                                                                                                                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

This specification ensured by design. §

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 7.1 for min conditions.

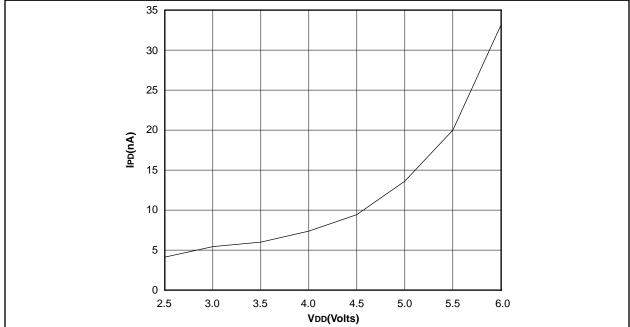

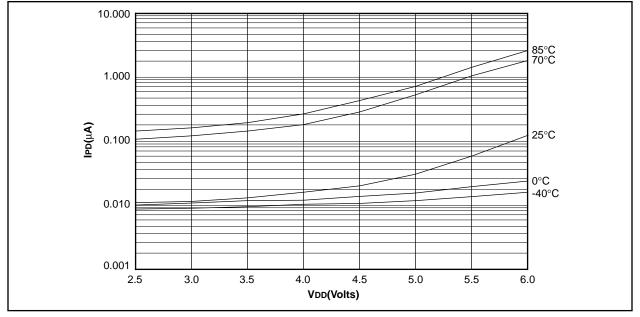

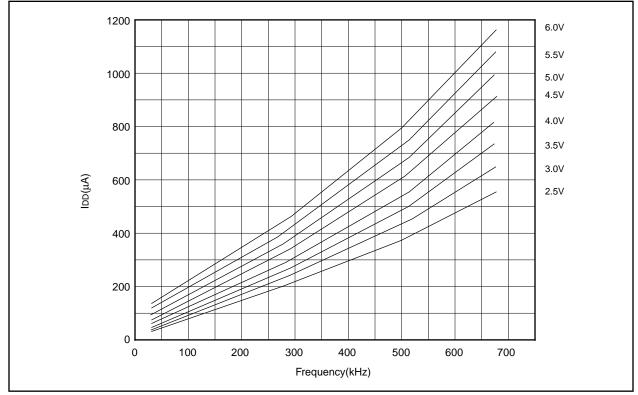

# 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

# FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

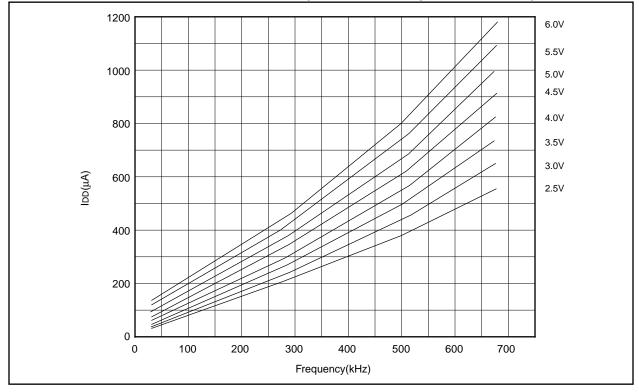

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

# 13.1 DC Characteristics: PIC16C715-04 (Commercial, Industrial, Extended) PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (

| DC CHA                         | RACTERISTICS                                                      | Operating temperature |            |                           |                      | ditions (unless otherwise stated)<br>$D^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended) |                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------|-------------------------------------------------------------------|-----------------------|------------|---------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.                  | Characteristic                                                    | Sym                   | Min        | Тур†                      | Мах                  | Units                                                                                                                                                                                                   | Conditions                                                                                                                                                                                                                                                                                        |  |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd                   | 4.0<br>4.5 | -                         | 5.5<br>5.5           | V<br>V                                                                                                                                                                                                  | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                           |  |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                   | -          | 1.5                       | -                    | V                                                                                                                                                                                                       | Device in SLEEP mode                                                                                                                                                                                                                                                                              |  |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR                  | -          | Vss                       | -                    | V                                                                                                                                                                                                       | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |  |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD                  | 0.05       | -                         | -                    | V/ms                                                                                                                                                                                                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |  |

| D005                           | Brown-out Reset Voltage                                           | Bvdd                  | 3.7        | 4.0                       | 4.3                  | V                                                                                                                                                                                                       | BODEN configuration bit is enabled                                                                                                                                                                                                                                                                |  |

| D010                           | Supply Current (Note 2)                                           | IDD                   | -          | 2.7                       | 5                    | mA .                                                                                                                                                                                                    | XT, RC osc configuration (PIC16C715-04)<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                      |  |

| D013                           |                                                                   |                       | -          | 13.5                      | 30                   | mA                                                                                                                                                                                                      | HS øsc configuration (PIC16C715-20)<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                  |  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ IBOR         | -<         | 300*                      | 500                  | ha `                                                                                                                                                                                                    | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |  |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD <                 | -          | 10,5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                                                                                                                    | $VDD = 4.0V, WDT enabled, -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -0^{\circ}C \text{ to } +70^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +125^{\circ}C$ |  |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | ALBOR                 |            | >300*                     | 500                  | μA                                                                                                                                                                                                      | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 51, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which Vod can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

(The)test conditions for all IDD measurements in active operation mode are:

OSCT = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# 15.2 DC Characteristics: PIC16LC71-04 (Commercial, Industrial)

| DC CHA                | RACTERISTICS                                                     |      | Standard Operating Conditions (unless otherwise stated)OOperating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) |                 |               |                |                                                                                                                                                                         |  |  |

|-----------------------|------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          |                                                                  |      | Min                                                                                                                                                                                         | Тур†            | Max           | Units          | Conditions                                                                                                                                                              |  |  |