Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E-XF

| Betuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 68 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                                |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

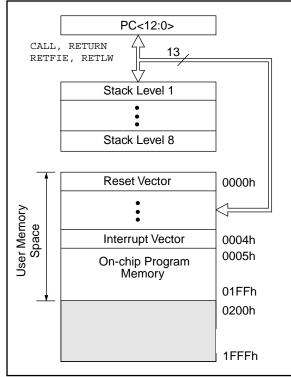

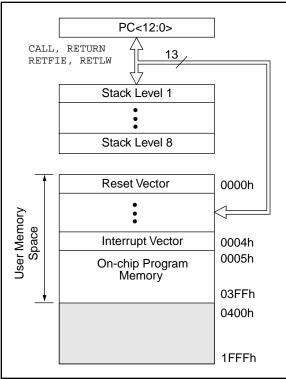

# 4.1 Program Memory Organization

The PIC16C71X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C710 | 512 x 14          | 0000h-01FFh   |

| PIC16C71  | 1K x 14           | 0000h-03FFh   |

| PIC16C711 | 1K x 14           | 0000h-03FFh   |

| PIC16C715 | 2K x 14           | 0000h-07FFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

# FIGURE 4-1: PIC16C710 PROGRAM MEMORY MAP AND STACK

# FIGURE 4-2: PIC16C71/711 PROGRAM MEMORY MAP AND STACK

# FIGURE 4-3: PIC16C715 PROGRAM MEMORY MAP AND STACK

# 4.2 Data Memory Organization

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow \text{Bank } 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

|                     | 1117 \                                                   |                                                                      |                 |  |  |  |  |

|---------------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------|--|--|--|--|

| File<br>Addres      | s                                                        | ,                                                                    | File<br>Address |  |  |  |  |

| 00h                 | INDF <sup>(1)</sup>                                      | INDF <sup>(1)</sup>                                                  | 80h             |  |  |  |  |

| 01h                 | TMR0                                                     | OPTION                                                               | 81h             |  |  |  |  |

| 02h                 | PCL                                                      | PCL                                                                  | 82h             |  |  |  |  |

| 03h                 | 03h STATUS STATUS                                        |                                                                      |                 |  |  |  |  |

| 04h                 | 04h FSR FSR                                              |                                                                      |                 |  |  |  |  |

| 05h                 | PORTA                                                    | TRISA                                                                | 85h             |  |  |  |  |

| 06h                 | PORTB                                                    | TRISB                                                                | 86h             |  |  |  |  |

| 07h                 |                                                          | PCON <sup>(2)</sup>                                                  | 87h             |  |  |  |  |

| 08h                 | ADCON0                                                   | ADCON1                                                               | 88h             |  |  |  |  |

| 09h                 | ADRES                                                    | ADRES                                                                | 89h             |  |  |  |  |

| 0Ah                 | PCLATH                                                   | PCLATH                                                               | 8Ah             |  |  |  |  |

| 0Bh                 | INTCON                                                   | INTCON                                                               | 8Bh             |  |  |  |  |

| 0Ch                 | General<br>Purpose<br>Register                           | General<br>Purpose<br>Register<br>Mapped<br>in Bank 0 <sup>(3)</sup> | 8Ch             |  |  |  |  |

| 2Fh                 |                                                          |                                                                      | AFh             |  |  |  |  |

| 30h                 |                                                          |                                                                      | B0h             |  |  |  |  |

| 3011                |                                                          |                                                                      |                 |  |  |  |  |

| l                   | <                                                        |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

| Ν                   |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      | )               |  |  |  |  |

| 7Fh                 |                                                          |                                                                      | FFh             |  |  |  |  |

| L                   | Bank 0                                                   | Bank 1                                                               | 1               |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

| Note 1:<br>2:<br>3: | 2: The PCON register is not implemented on the PIC16C71. |                                                                      |                 |  |  |  |  |

|                     |                                                          |                                                                      |                 |  |  |  |  |

# 4.2.2.2 OPTION REGISTER

# Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

# FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                                         | R/W-1                                                          | R/W-1      | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                          |  |  |  |  |

|----------|-----------------------------------------------|----------------------------------------------------------------|------------|------------|--------------|------------|-------|--------------------------|--|--|--|--|

| RBPU     | INTEDG                                        | TOCS                                                           | T0SE       | PSA        | PS2          | PS1        | PS0   | R = Readable bit         |  |  |  |  |

| bit7     | · · ·                                         | bit0 W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |            |            |              |            |       |                          |  |  |  |  |

|          |                                               |                                                                |            |            |              |            |       | - n = Value at POR reset |  |  |  |  |

| bit 7:   | RBPU: PC                                      | RTB Pull                                                       | -up Enabl  | le bit     |              |            |       |                          |  |  |  |  |

|          | 1 = PORT                                      |                                                                |            |            |              |            |       |                          |  |  |  |  |

|          | 0 = PORTE                                     | 3 pull-ups                                                     | s are enab | led by ind | ividual port | latch valu | es    |                          |  |  |  |  |

| bit 6:   | INTEDG:                                       | nterrupt E                                                     | Edge Sele  | ct bit     |              |            |       |                          |  |  |  |  |

|          | 1 = Interru                                   | pt on risir                                                    | ng edge of | f RB0/INT  | pin          |            |       |                          |  |  |  |  |

|          | 0 = Interru                                   | pt on falli                                                    | ng edge o  | f RB0/INT  | pin          |            |       |                          |  |  |  |  |

| bit 5:   | TOCS: TM                                      | R0 Clock                                                       | Source S   | elect bit  |              |            |       |                          |  |  |  |  |

|          | 1 = Transition on RA4/T0CKI pin               |                                                                |            |            |              |            |       |                          |  |  |  |  |

|          | 0 = Internal instruction cycle clock (CLKOUT) |                                                                |            |            |              |            |       |                          |  |  |  |  |

| bit 4:   | TOSE: TM                                      |                                                                |            |            |              |            |       |                          |  |  |  |  |

|          |                                               |                                                                |            |            | on RA4/T00   |            |       |                          |  |  |  |  |

|          | 0 = Increm                                    | ent on lo                                                      | w-to-high  | transition | on RA4/T00   | JKI pin    |       |                          |  |  |  |  |

| bit 3:   | PSA: Pres                                     |                                                                | 0          |            |              |            |       |                          |  |  |  |  |

|          | 1 = Presca<br>0 = Presca                      |                                                                |            |            | modulo       |            |       |                          |  |  |  |  |

|          |                                               |                                                                | •          |            | module       |            |       |                          |  |  |  |  |

| bit 2-0: | PS2:PS0:                                      | Prescale                                                       | r Rate Sel | lect bits  |              |            |       |                          |  |  |  |  |

|          | Bit Value                                     | TMR0 R                                                         | ate WD     | Γ Rate     |              |            |       |                          |  |  |  |  |

|          | 000                                           | 1:2                                                            | 1:         |            |              |            |       |                          |  |  |  |  |

|          | 001                                           | 1:4                                                            | 1:         |            |              |            |       |                          |  |  |  |  |

|          | 010<br>011                                    | 1:8                                                            | 1:         |            |              |            |       |                          |  |  |  |  |

|          | 100                                           | 1:16                                                           |            | 16         |              |            |       |                          |  |  |  |  |

|          | 101                                           | 1:64                                                           | . 1:       | 32         |              |            |       |                          |  |  |  |  |

|          | 110                                           | 1 : 12                                                         |            | 64         |              |            |       |                          |  |  |  |  |

|          | 111                                           | 1:25                                                           | 6   1      | 128        |              |            |       |                          |  |  |  |  |

|          |                                               |                                                                |            |            |              |            |       |                          |  |  |  |  |

|          |                                               |                                                                |            |            |              |            |       |                          |  |  |  |  |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

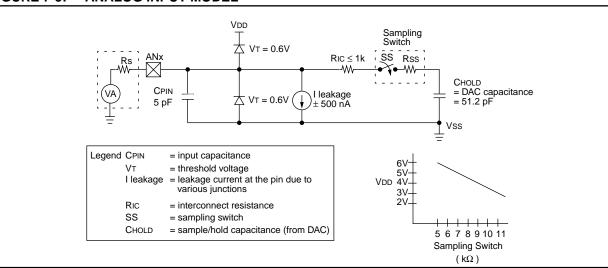

# 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

# EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

# FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

# EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

# TABLE 8-10: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C710/71/711

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C710/711 |

|------------------------------------|-----------------------|--------------------|-----------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x                                |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu                                |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu                                |

| WDT Reset                          | 000h                  | 0000 luuu          | uu                                |

| WDT Wake-up                        | PC + 1                | นนน0 0นนน          | uu                                |

| Brown-out Reset (PIC16C710/711)    | 000h                  | 0001 luuu          | u0                                |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu                                |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

# TABLE 8-11: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C715

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |  |

|------------------------------------|-----------------------|--------------------|------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | u10x             |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uuuu             |  |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | uuuu             |  |

| WDT Reset                          | 000h                  | 0000 luuu          | uuuu             |  |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uuuu             |  |

| Brown-out Reset                    | 000h                  | 0001 luuu          | uuu0             |  |

| Parity Error Reset                 | 000h                  | uuul Ouuu          | u0uu             |  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

# TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

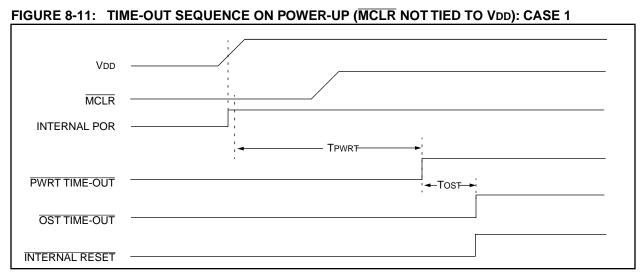

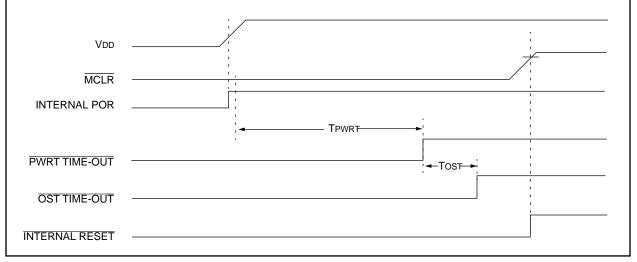

FIGURE 8-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

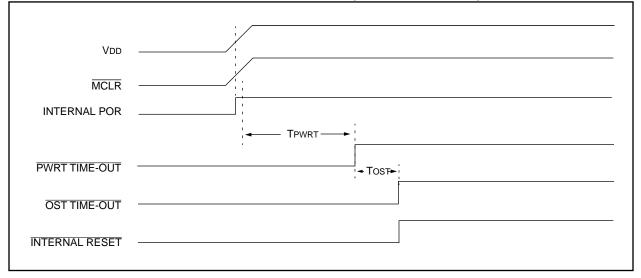

# FIGURE 8-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| FIGURE 8-22: WAKE-UP FROM SLEEP THROUGH INTERRUP |

|--------------------------------------------------|

|--------------------------------------------------|

| CLKOUT(4)                                                                          | ////               | Tost(2)      | //                    | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u> |                  | /           |

|------------------------------------------------------------------------------------|--------------------|--------------|-----------------------|-----------------------------------------------|------------------|-------------|

| · .                                                                                | 1                  | 1 1          |                       |                                               | / IN             | /           |

| INTE flag                                                                          |                    | 1 1          | 1                     | 1 I<br>1 I                                    | 1<br>1           |             |

| (INTCON<1>)                                                                        | <br> <br>          |              | 1<br><del> </del><br> | Interrupt Latency<br>(Note 2)                 |                  |             |

| GIE bit<br>(INTCON<7>)                                                             | <br> <br> <br>     | Processor in | 1<br>1<br>1           |                                               |                  |             |

| STRUCTION FLOW                                                                     | 1<br>1<br>1        | SLEEP        | <br> <br>             | 1 1<br>1 1<br>1 1                             | 1                |             |

| PC X PC                                                                            | PC+1               | PC+2         | V PC+2                | ↓<br>↓ PC + 2 ↓                               | ( <u>0004h</u> ) | 0005h       |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | SLEEP Inst(PC + 1) |              | Inst(PC + 2)          | 1 1<br>1 1<br>1 1                             | Inst(0004h)      | Inst(0005h) |

| Instruction { Inst(PC                                                              | - 1) SLEEP         |              | Inst(PC + 1)          | Dummy cycle                                   | Dummy cycle      | Inst(0004h) |

Δ. CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 8.9 **Program Verification/Code Protection**

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 8.10 **ID** Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

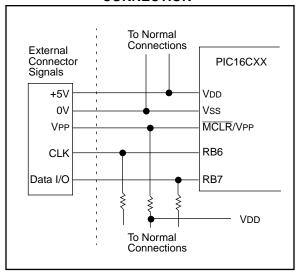

#### 8.11 In-Circuit Serial Programming

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

## FIGURE 8-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# SLEEP

| [ label ]                                                                                                                                                                                                   | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| None                                                                                                                                                                                                        |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                        |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TO, PD                                                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00                                                                                                                                                                                                          | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 8.8 for more details. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                                                           |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                                                           |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                                                                                                                                                          | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                                                                                                                                                      | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SLEEP                                                                                                                                                                                                       |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                                                             | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |

| SUBLW             | Subtract W from Literal    |                    |                                                                            |  |  |  |  |

|-------------------|----------------------------|--------------------|----------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [ label ]                  | SUBL               | N k                                                                        |  |  |  |  |

| Operands:         | $0 \le k \le 255$          |                    |                                                                            |  |  |  |  |

| Operation:        | $k \text{ - } (W) \to (W)$ |                    |                                                                            |  |  |  |  |

| Status Affected:  | C, DC, Z                   |                    |                                                                            |  |  |  |  |

| Encoding:         | 11                         | 110x               | kkkk kkkł                                                                  |  |  |  |  |

| Description:      | ment meth                  | od) from           | ubtracted (2's complet<br>the eight bit literal 'k<br>I in the W register. |  |  |  |  |

| Words:            | 1                          |                    |                                                                            |  |  |  |  |

| Cycles:           | 1                          |                    |                                                                            |  |  |  |  |

| Q Cycle Activity: | Q1                         | Q2                 | Q3 Q4                                                                      |  |  |  |  |

|                   | Decode                     | Read<br>literal 'k | Process Write to data                                                      |  |  |  |  |

| Example 1:        | SUBLW                      | 0x02               |                                                                            |  |  |  |  |

|                   | Before Instruction         |                    |                                                                            |  |  |  |  |

|                   |                            | W =<br>C =<br>Z =  | 1<br>?<br>?                                                                |  |  |  |  |

|                   | After Inst                 | ruction            |                                                                            |  |  |  |  |

|                   |                            | W =<br>C =<br>Z =  | 1<br>1; result is positive<br>0                                            |  |  |  |  |

| Example 2:        | Before In:                 | structior          | n                                                                          |  |  |  |  |

|                   |                            | W =<br>C =<br>Z =  | 2<br>?<br>?                                                                |  |  |  |  |

|                   | After Inst                 | ruction            |                                                                            |  |  |  |  |

|                   |                            | W =<br>C =<br>Z =  | 0<br>1; result is zero<br>1                                                |  |  |  |  |

| Example 3:        | Before In                  | structior          | ı                                                                          |  |  |  |  |

| Example 0.        |                            | W =                | 3                                                                          |  |  |  |  |

| Example 0.        |                            |                    |                                                                            |  |  |  |  |

| Example 0.        |                            | C =<br>Z =         | ?<br>?                                                                     |  |  |  |  |

|                   | After Inst                 | Z =                |                                                                            |  |  |  |  |

|                   | After Inst                 | Z =                |                                                                            |  |  |  |  |

|                   | After Inst                 | Z =<br>ruction     | ?                                                                          |  |  |  |  |

Applicable Devices 710 71 711 715

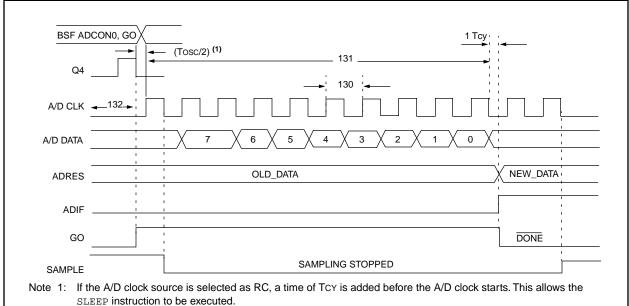

# FIGURE 11-7: A/D CONVERSION TIMING

#### **TABLE 11-7: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym                    | Characteristic                                        |                                 | Min    | Тур†    | Max | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------------------------|-------------------------------------------------------|---------------------------------|--------|---------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | 0 TAD A/D clock period |                                                       | PIC16 <b>C</b> 710/711          | 1.6    | _       | _   | μs    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                               |

|              |                        |                                                       | PIC16LC710/711                  | 2.0    | _       | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                                |

|              |                        |                                                       | PIC16 <b>C</b> 710/711          | 2.0*   | 4.0     | 6.0 | μs    | A/D RC mode                                                                                                                                                                                                                |

|              |                        |                                                       | PIC16LC710/711                  | 3.0*   | 6.0     | 9.0 | μs    | A/D RC mode                                                                                                                                                                                                                |

| 131          | TCNV                   | Conversion time<br>(not including S/H time). (Note 1) |                                 | —      | 9.5     | -   | TAD   |                                                                                                                                                                                                                            |

| 132          | TACQ                   | Acquisition time                                      |                                 | Note 2 | 20      | _   | μs    |                                                                                                                                                                                                                            |

|              |                        |                                                       |                                 | 5*     | _       | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if the<br>"new" input voltage has not changed<br>by more than 1 LSb (i.e., 19.5 mV @<br>5.12V) from the last sampled voltage<br>(as stated on CHOLD). |

| 134          | TGO                    | Q4 to AD clock start                                  |                                 |        | Tosc/2§ |     | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                           |

| 135          | Tswc                   | Switching from co                                     | nvert $\rightarrow$ sample time | 1.5§   | _       |     | TAD   |                                                                                                                                                                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

This specification ensured by design. §

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 7.1 for min conditions.

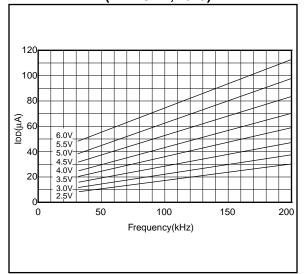

# FIGURE 12-25: TYPICAL IDD vs. FREQUENCY (LP MODE, 25°C)

# Applicable Devices 710 71 711 715

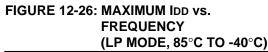

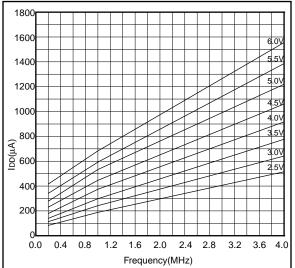

FIGURE 12-27: TYPICAL IDD vs. FREQUENCY (XT MODE, 25°C)

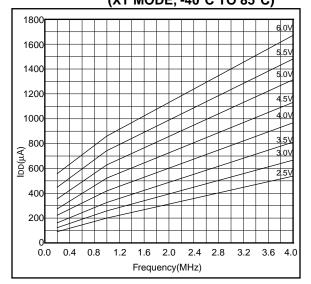

FIGURE 12-28: MAXIMUM IDD vs. FREQUENCY (XT MODE, -40°C TO 85°C)

# Applicable Devices 710 71 711 715

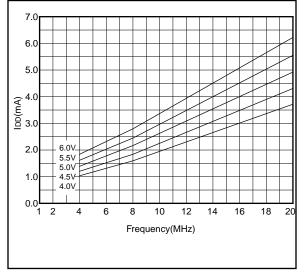

# FIGURE 12-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

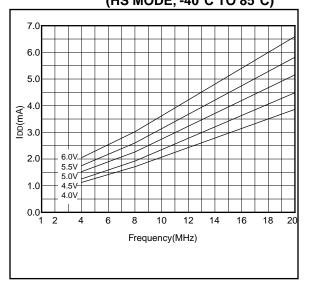

# FIGURE 12-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

# Applicable Devices 710 71 711 715

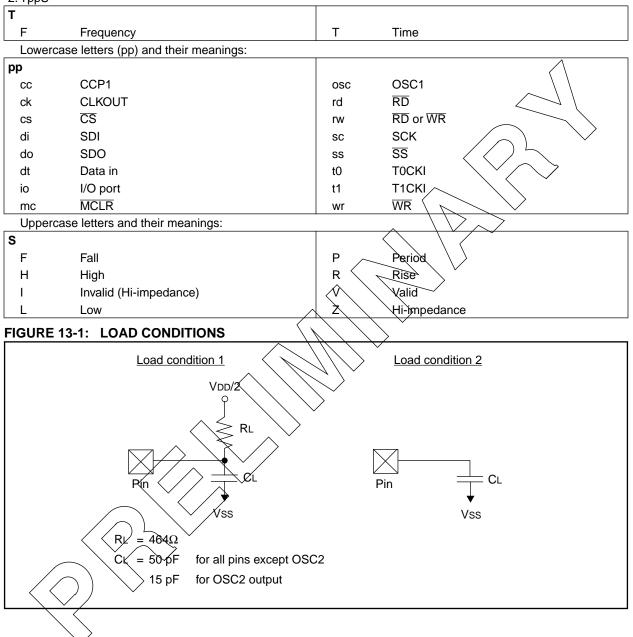

# 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

Applicable Devices 710 71 711 715

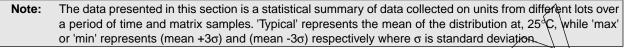

# 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

Applicable Devices 710 71 711 715

# 15.0 ELECTRICAL CHARACTERISTICS FOR PIC16C71

# Absolute Maximum Ratings †

| •                                                                                                                                                |                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Ambient temperature under bias                                                                                                                   | 55 to +125°C         |  |

| Storage temperature                                                                                                                              | 65°C to +150°C       |  |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                               | 0.3V to (VDD + 0.3V) |  |

| Voltage on VDD with respect to Vss                                                                                                               | -0.3 to +7.5V        |  |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                     | 0 to +14V            |  |

| Voltage on RA4 with respect to Vss                                                                                                               | 0 to +14V            |  |

| Total power dissipation (Note 1)                                                                                                                 |                      |  |

| Maximum current out of Vss pin                                                                                                                   | 150 mA               |  |

| Maximum current into VDD pin                                                                                                                     | 100 mA               |  |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                     | ±20 mA               |  |

| Output clamp current, Iok (Vo < 0 or Vo > VDD)                                                                                                   |                      |  |

| Maximum output current sunk by any I/O pin                                                                                                       |                      |  |

| Maximum output current sourced by any I/O pin                                                                                                    | 20 mA                |  |

| Maximum current sunk by PORTA                                                                                                                    | 80 mA                |  |

| Maximum current sourced by PORTA                                                                                                                 | 50 mA                |  |

| Maximum current sunk by PORTB                                                                                                                    |                      |  |

| Maximum current sourced by PORTB                                                                                                                 | 100 mA               |  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD-VOH) x IOH} + $\Sigma$ (VOI x IOL) |                      |  |

| Note 2: Voltage spikes below Vss at the $\overline{MCLR}$ bin inducing currents greater than 80 mA may cause latch-up. Thus                      |                      |  |

**Note 2:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# TABLE 15-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C71-04                                                                                               | PIC16C71-20                                                                                   | PIC16LC71-04                                                                                            | JW Devices                                                                                              |

|-----|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 3.3 mA max. at 5.5V<br>IPD: 14 μA max. at 4V<br>Freq:4 MHz max.                 | VDD: 4.5V to 5.5V<br>IDD: 1.8 mA typ. at 5.5V<br>IPD: 1.0 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 3.0V to 6.0V<br>IDD: 1.4 mA typ. at 3.0V<br>IPD: 0.6 μA typ. at 3V<br>Freq: 4 MHz max.             | VDD: 4.0V to 6.0V<br>IDD: 3.3 mA max. at 5.5V<br>IPD: 14 μA max. at 4V<br>Freq:4 MHz max.               |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 3.3 mA max. at 5.5V<br>IPD: 14 μA max. at 4V<br>Freq: 4 MHz max.                | VDD: 4.5V to 5.5V<br>IDD: 1.8 mA typ. at 5.5V<br>IPD: 1.0 μA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 3.0V to 6.0V<br>IDD: 1.4 mA typ. at 3.0V<br>IPD: 0.6 μA typ. at 3V<br>Freq: 4 MHz max.             | VDD: 4.0V to 6.0V<br>IDD: 3.3 mA max. at 5.5V<br>IPD: 14 μA max. at 4V<br>Freq: 4 MHz max.              |

| нѕ  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.0 μA typ. at 4.5V<br>Freq: 4 MHz max.            | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at 5.5V<br>IPD: 1.0 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use in<br>HS mode                                                                   | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at 5.5V<br>IPD: 1.0 μA typ. at 4.5V<br>Freq: 20 MHz max.           |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 15 μA typ. at 32 kHz,<br>4.0V<br>IPD: 0.6 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use<br>in LP mode                                                         | VDD: 3.0V to 6.0V<br>IDD: 32 μA max. at 32 kHz,<br>3.0V<br>IPD: 9 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 6.0V<br>IDD: 32 μA max. at 32 kHz,<br>3.0V<br>IPD: 9 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

# Applicable Devices 710 71 711 715

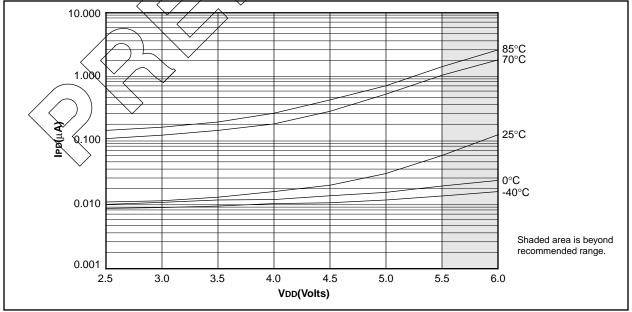

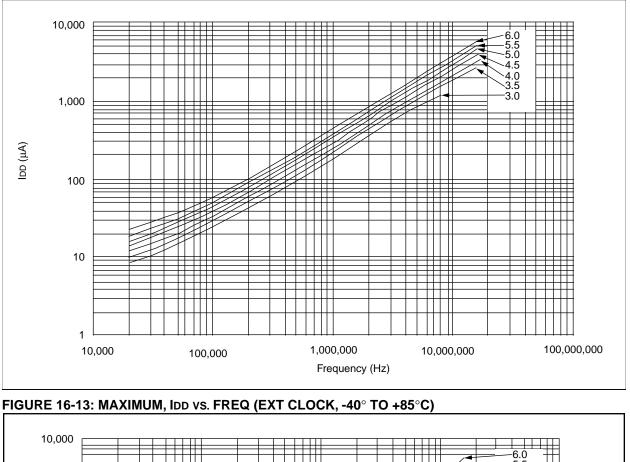

# FIGURE 16-12: TYPICAL IDD vs. FREQ (EXT CLOCK, 25°C)

Data based on matrix samples. See first page of this section for details.

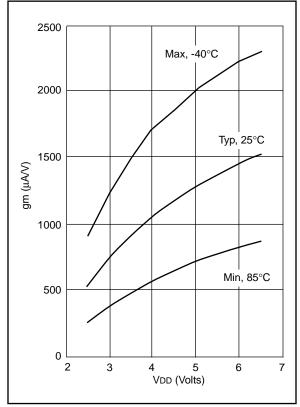

# FIGURE 16-18: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

# **APPENDIX A:**

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (1K now as opposed to 512 before) and register file (68 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

# APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

| Figure 7-3:   | ADCON1 Register, PIC16C710/71/711          |

|---------------|--------------------------------------------|

| 0             | (Address 88h),                             |

|               | PIC16C715 (Address 9Fh)                    |

| Figure 7 4    |                                            |

| Figure 7-4:   | A/D Block Diagram                          |

| Figure 7-5:   | Analog Input Model 40                      |

| Figure 7-6:   | A/D Transfer Function 45                   |

| Figure 7-7:   | Flowchart of A/D Operation 45              |

| Figure 8-1:   | Configuration Word for PIC16C71 47         |

| Figure 8-2:   | Configuration Word, PIC16C710/711 48       |

| Figure 8-3:   | Configuration Word, PIC16C71548            |

| Figure 8-4:   | Crystal/Ceramic Resonator Operation        |

| Figure 0-4.   |                                            |

|               | (HS, XT or LP OSC Configuration)           |

| Figure 8-5:   | External Clock Input Operation             |

|               | (HS, XT or LP OSC Configuration)           |

| Figure 8-6:   | External Parallel Resonant Crystal         |

| -             | Oscillator Circuit                         |

| Figure 8-7:   | External Series Resonant Crystal           |

| rigaro o r.   | Oscillator Circuit                         |

|               |                                            |

| Figure 8-8:   | RC Oscillator Mode                         |

| Figure 8-9:   | Simplified Block Diagram of On-chip        |

|               | Reset Circuit52                            |

| Figure 8-10:  | Brown-out Situations53                     |

| Figure 8-11:  | Time-out Sequence on Power-up              |

| 0             | (MCLR not Tied to VDD): Case 1             |

| Figure 8-12:  | Time-out Sequence on Power-up              |

| rigule 0-12.  |                                            |

|               | (MCLR Not Tied To VDD): Case 2             |

| Figure 8-13:  | Time-out Sequence on Power-up              |

|               | (MCLR Tied to VDD) 59                      |

| Figure 8-14:  | External Power-on Reset Circuit            |

| -             | (for Slow VDD Power-up)60                  |

| Figure 8-15:  | External Brown-out Protection Circuit 1 60 |

| Figure 8-16:  | External Brown-out Protection Circuit 2 60 |

|               |                                            |

| Figure 8-17:  | Interrupt Logic, PIC16C710, 71, 711        |

| Figure 8-18:  | Interrupt Logic, PIC16C71562               |

| Figure 8-19:  | INT Pin Interrupt Timing63                 |

| Figure 8-20:  | Watchdog Timer Block Diagram65             |

| Figure 8-21:  | Summary of Watchdog Timer Registers 65     |

| Figure 8-22:  | Wake-up from Sleep Through Interrupt 67    |

| Figure 8-23:  | Typical In-Circuit Serial Programming      |

| r igure e 20. | Connection                                 |

|               |                                            |

| Figure 9-1:   | General Format for Instructions            |

| Figure 11-1:  | Load Conditions94                          |

| Figure 11-2:  | External Clock Timing95                    |

| Figure 11-3:  | CLKOUT and I/O Timing                      |

| Figure 11-4:  | Reset, Watchdog Timer, Oscillator          |

| 0.            | Start-up Timer and Power-up Timer          |

|               | Timing                                     |

| Figure 11 Fr  |                                            |

| Figure 11-5:  | Brown-out Reset Timing                     |

| Figure 11-6:  | Timer0 External Clock Timings              |

| Figure 11-7:  | A/D Conversion Timing 100                  |

| Figure 12-1:  | Typical IPD vs. VDD                        |

|               | (WDT Disabled, RC Mode) 101                |

| Figure 12-2:  | Maximum IPD vs. VDD                        |

|               | (WDT Disabled, RC Mode) 101                |

| Figure 12-3:  |                                            |

| Figure 12-5.  | Typical IPD vs. VDD @ 25°C                 |

|               | (WDT Enabled, RC Mode) 102                 |

| Figure 12-4:  | Maximum IPD vs. VDD                        |

|               | (WDT Enabled, RC Mode) 102                 |

| Figure 12-5:  | Typical RC Oscillator Frequency            |

| -             | vs. VDD                                    |

| Figure 12-6:  | Typical RC Oscillator Frequency            |

|               | vs. VDD                                    |

|               |                                            |

| Figure 12-7:  | Typical RC Oscillator Frequency            |

|               | vs. VDD                                    |

| Figure 12-8:  | Typical IPD vs. VDD Brown-out Detect       |

|               | Enabled (RC Mode) 103                      |

| Figure 12-9:                   | Maximum IPD vs. VDD Brown-out Detect                              |

|--------------------------------|-------------------------------------------------------------------|

| <b>Figure 10 10</b>            | Enabled (85°C to -40°C, RC Mode) 103                              |

| Figure 12-10:                  | Typical IPD vs. Timer1 Enabled<br>(32 kHz, RC0/RC1 = 33 pF/33 pF, |

|                                | (32 kHz, KC0/RC1 = 33 pr/33 pr,<br>RC Mode)                       |

| Figure 12-11:                  | Maximum IPD vs. Timer1 Enabled                                    |

| ga.o                           | (32  kHz, RC0/RC1 = 33  pF/33  pF,)                               |

|                                | 85°C to -40°C, RC Mode) 103                                       |

| Figure 12-12:                  | Typical IDD vs. Frequency                                         |

|                                | (RC Mode @ 22 pF, 25°C) 104                                       |

| Figure 12-13:                  | Maximum IDD vs. Frequency                                         |

|                                | (RC Mode @ 22 pF, -40°C to 85°C) 104                              |

| Figure 12-14:                  | Typical IDD vs. Frequency                                         |

| Figure 12 15                   | (RC Mode @ 100 pF, 25°C) 105<br>Maximum IDD vs. Frequency         |

| Figure 12-15:                  | (RC Mode @ 100 pF, -40°C to 85°C) 105                             |

| Figure 12-16:                  | Typical IDD vs. Frequency                                         |

| · · g · · · · · · · · ·        | (RC Mode @ 300 pF, 25°C) 106                                      |

| Figure 12-17:                  | Maximum IDD vs. Frequency                                         |

| -                              | (RC Mode @ 300 pF, -40°C to 85°C) 106                             |

| Figure 12-18:                  | Typical IDD vs. Capacitance                                       |

|                                | @ 500 kHz (RC Mode) 107                                           |

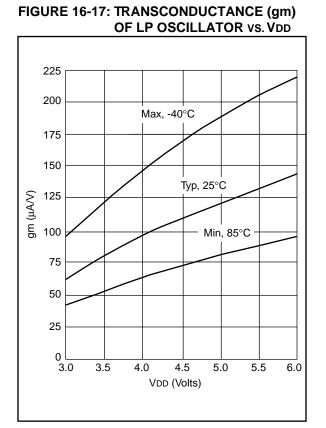

| Figure 12-19:                  | Transconductance(gm) of                                           |

| Figure 40.00                   | HS Oscillator vs. VDD 107                                         |

| Figure 12-20:                  | Transconductance(gm) of<br>LP Oscillator vs. VDD                  |

| Figure 12-21:                  | Transconductance(gm) of                                           |

|                                | XT Oscillator vs. VDD 107                                         |

| Figure 12-22:                  | Typical XTAL Startup Time vs.                                     |

| 0                              | VDD (LP Mode, 25°C) 108                                           |

| Figure 12-23:                  | Typical XTAL Startup Time vs.                                     |

|                                | VDD (HS Mode, 25°C) 108                                           |

| Figure 12-24:                  | Typical XTAL Startup Time vs.                                     |

| E                              | VDD (XT Mode, 25°C) 108                                           |

| Figure 12-25:                  | Typical IDD vs. Frequency<br>(LP Mode, 25°C)                      |

| Figure 12-26:                  | Maximum IDD vs. Frequency                                         |

| 1 iguro 12 20.                 | (LP Mode, 85°C to -40°C) 109                                      |

| Figure 12-27:                  | Typical IDD vs. Frequency                                         |

| 0                              | (XT Mode, 25°C) 109                                               |

| Figure 12-28:                  | Maximum IDD vs. Frequency                                         |

|                                | (XT Mode, -40°C to 85°C) 109                                      |

| Figure 12-29:                  | Typical IDD vs. Frequency                                         |

| <b>F</b> ilment <b>10</b> ,000 | (HS Mode, 25°C) 110                                               |

| Figure 12-30:                  | Maximum IDD vs. Frequency<br>(HS Mode, -40°C to 85°C) 110         |

| Figure 13-1:                   | Load Conditions                                                   |

| Figure 13-2:                   | External Clock Timing                                             |

| Figure 13-3:                   | CLKOUT and I/O Timing 119                                         |

| Figure 13-4:                   | Reset, Watchdog Timer, Oscillator                                 |

|                                | Start-Up Timer, and Power-Up Timer                                |

| <b>F</b> : 10 <b>F</b>         | Timing                                                            |

| Figure 13-5:                   | Brown-out Reset Timing                                            |

| Figure 13-6:<br>Figure 13-7:   | Timer0 Clock Timings                                              |

| Figure 14-1:                   | Typical IPD vs. VDD                                               |

| . iguic 14-1.                  | (WDT Disabled, RC Mode)                                           |

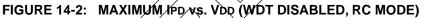

| Figure 14-2:                   | Maximum IPD vs. VDD                                               |