Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | <u>.</u>                                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711t-20-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 PIC16C71X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C71X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C71X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**71. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC71. These devices have EPROM type memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C71X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution. **Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

BCFSTATUS, RP0;Bank 0CLRFTMR0;Clear TMR0 & PrescalerBSFSTATUS, RP0;Bank 1CLRWDT;Clears WDTMOVLWb'xxxxlxxx';Selects new prescale valueMOVWFOPTION\_REG;and assigns the prescaler to the WDTBCFSTATUS, RP0;Bank 0

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT → TIMER0)

| CLRWDT |             | ;Clear WDT and prescaler             |

|--------|-------------|--------------------------------------|

| BSF    | STATUS, RPO | ;Bank 1                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new prescale value and |

| MOVWF  | OPTION_REG  | ;clock source                        |

| BCF    | STATUS, RPO | ;Bank 0                              |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address  | Name   | Bit 7  | Bit 6      | Bit 5   | Bit 4                         |      |      | Value on:<br>POR,<br>BOR | Value on all other resets |           |           |

|----------|--------|--------|------------|---------|-------------------------------|------|------|--------------------------|---------------------------|-----------|-----------|

| 01h      | TMR0   | Timer0 | module's r | egister | gister                        |      |      |                          | xxxx xxxx                 | uuuu uuuu |           |

| 0Bh,8Bh, | INTCON | GIE    | ADIE       | TOIE    | INTE                          | RBIE | TOIF | INTF                     | RBIF                      | 0000 000x | 0000 000u |

| 81h      | OPTION | RBPU   | INTEDG     | T0CS    | TOSE                          | PSA  | PS2  | PS1                      | PS0                       | 1111 1111 | 1111 1111 |

| 85h      | TRISA  | —      | —          | _       | PORTA Data Direction Register |      |      | 1 1111                   | 1 1111                    |           |           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 7.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

#### 7.6 <u>A/D Accuracy/Error</u>

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at <  $\pm$ 1 LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from TOSC, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 7.7 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

#### 7.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | Care must be taken when using the RA0       |

|-------|---------------------------------------------|

|       | pin in A/D conversions due to its proximity |

|       | to the OSC1 pin.                            |

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

#### TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

#### 8.6 <u>Context Saving During Interrupts</u>

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 8-1 stores and restores the STATUS and W registers. The user register, STATUS\_TEMP, must be defined in bank 0.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### EXAMPLE 8-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W |

|----------------|--------------------|----------------------------------------------------------------------------------------|

| SWAPP          | •                  | L                                                                                      |

| MOVWF          | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                         |

| :              |                    |                                                                                        |

| :(ISR)         |                    |                                                                                        |

| :              |                    |                                                                                        |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                                                      |

|                |                    | ;(sets bank to original state)                                                         |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                           |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                           |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                    |

|                |                    |                                                                                        |

| FIGURE 8-22: WAKE-UP FROM SLEEP THROUGH INTERRUP |

|--------------------------------------------------|

|--------------------------------------------------|

| CLKOUT(4)                                                                          | ////               | Tost(2)      | //                    | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u> |                  | /           |

|------------------------------------------------------------------------------------|--------------------|--------------|-----------------------|-----------------------------------------------|------------------|-------------|

| · .                                                                                | 1                  | 1 1          |                       |                                               | / IN             | /           |

| INTE flag                                                                          |                    | 1 1          | 1                     | 1 I<br>1 I                                    | 1<br>1           |             |

| (INTCON<1>)                                                                        | <br> <br>          |              | 1<br><del> </del><br> | Interrupt Latency<br>(Note 2)                 |                  |             |

| GIE bit<br>(INTCON<7>)                                                             | <br> <br> <br>     | Processor in | 1<br>1<br>1           |                                               |                  |             |

| STRUCTION FLOW                                                                     | 1<br>1<br>1        | SLEEP        | <br> <br>             | 1 1<br>1 1<br>1 1                             | 1                |             |

| PC X PC                                                                            | PC+1               | PC+2         | V PC+2                | ↓<br>↓ PC + 2 ↓                               | ( <u>0004h</u> ) | 0005h       |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | SLEEP Inst(PC + 1) |              | Inst(PC + 2)          | 1 1<br>1 1<br>1 1                             | Inst(0004h)      | Inst(0005h) |

| Instruction { Inst(PC                                                              | - 1) SLEEP         |              | Inst(PC + 1)          | Dummy cycle                                   | Dummy cycle      | Inst(0004h) |

Δ. CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 8.9 **Program Verification/Code Protection**

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 8.10 **ID** Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

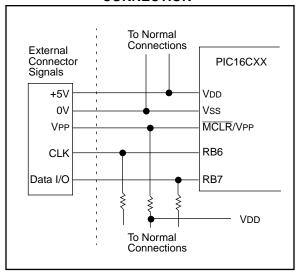

#### 8.11 In-Circuit Serial Programming

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

#### FIGURE 8-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |

|                   | FLAG_REG = 0xC7<br>After Instruction   | If Skip:          | (2nd Cycle)                                                                   |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |

| •                     |  |  |  |  |  |  |  |

|-----------------------|--|--|--|--|--|--|--|

| Before Instruction    |  |  |  |  |  |  |  |

| PC = address HERE     |  |  |  |  |  |  |  |

| After Instruction     |  |  |  |  |  |  |  |

| if $FLAG < 1 > = 0$ , |  |  |  |  |  |  |  |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                                                                     |                 |                       |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|-----------------------|--|--|

| Syntax:           | [ <i>label</i> ] BSF f,b                                                                         |                                                                     |                 |                       |  |  |

| Operands:         | $0 \le f \le 12$ $0 \le b \le 7$                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                 |                       |  |  |

| Operation:        | $1 \rightarrow (f < b >)$                                                                        |                                                                     |                 |                       |  |  |

| Status Affected:  | None                                                                                             |                                                                     |                 |                       |  |  |

| Encoding:         | 01                                                                                               | 01bb                                                                | bfff            | ffff                  |  |  |

| Description:      | Bit 'b' in register 'f' is set.                                                                  |                                                                     |                 |                       |  |  |

| Words:            | 1                                                                                                |                                                                     |                 |                       |  |  |

| Cycles:           | 1                                                                                                |                                                                     |                 |                       |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                                                                  | Q3              | Q4                    |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'                                             | Process<br>data | Write<br>register 'f' |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG REG = 0x8A |                                                                     |                 |                       |  |  |

| BTFSS             | Bit Test f                 | f, Skip if S                                            | Set                       |         | CALL              | Call Sub                              | oroutine                             |                                                          |                                             |

|-------------------|----------------------------|---------------------------------------------------------|---------------------------|---------|-------------------|---------------------------------------|--------------------------------------|----------------------------------------------------------|---------------------------------------------|

| Syntax:           | [ <i>label</i> ] B1        | FSS f,b                                                 |                           |         | Syntax:           | [ label ]                             | [ <i>label</i> ] CALL k              |                                                          |                                             |

| Operands:         | $0 \le f \le 12$           |                                                         |                           |         | Operands:         | $0 \le k \le 2$                       | 047                                  |                                                          |                                             |

|                   | 0 ≤ b < 7                  |                                                         |                           |         | Operation:        | (PC)+ 1-                              | → TOS,                               |                                                          |                                             |

| Operation:        | skip if (f<                | :b>) = 1                                                |                           |         |                   | $k \rightarrow PC <$                  |                                      | 50.40                                                    |                                             |

| Status Affected:  | None                       | i                                                       |                           |         |                   | ,                                     | 1<4:3>) -                            | $\rightarrow$ PC<12                                      | :11>                                        |

| Encoding:         | 01                         | 11bb                                                    | bfff                      | ffff    | Status Affected:  | None                                  |                                      |                                                          |                                             |

| Description:      |                            | register 'f' is                                         |                           | ne next | Encoding:         | 10                                    | 0kkk                                 | kkkk                                                     | kkkk                                        |

|                   | If bit 'b' is<br>discarded | is execute<br>1', then the<br>and a NOF<br>aking this a | next instru<br>is execute | ed      | Description:      | (PC+1) is<br>eleven bit<br>into PC bi | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the state<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |

| Words:            | 1                          |                                                         |                           |         |                   |                                       |                                      | rom PCLA<br>instruction                                  |                                             |

| Cycles:           | 1(2)                       |                                                         |                           |         | Words:            | 1                                     |                                      |                                                          |                                             |

| Q Cycle Activity: | Q1                         | Q2                                                      | Q3                        | Q4      | Cycles:           | 2                                     |                                      |                                                          |                                             |

|                   | Decode                     | Read<br>register 'f'                                    | Process<br>data           | NOP     | Q Cycle Activity: | Q1                                    | Q2                                   | Q3                                                       | Q4                                          |

| If Skip:          | (2nd Cyc                   | :le)                                                    |                           |         | 1st Cycle         | Decode                                | Read<br>literal 'k',                 | Process<br>data                                          | Write to<br>PC                              |

|                   | Q1                         | Q2                                                      | Q3                        | Q4      | 1                 |                                       | Push PC<br>to Stack                  |                                                          |                                             |

|                   | NOP                        | NOP                                                     | NOP                       | NOP     | 2nd Cycle         | NOP                                   | NOP                                  | NOP                                                      | NOP                                         |

| Example           | HERE<br>FALSE              |                                                         | FLAG,1<br>PROCESS_        | _CODE   | Example           | HERE                                  | CALL                                 | THERE                                                    |                                             |

|                   | TRUE                       | •                                                       |                           |         |                   | Before Ir                             |                                      |                                                          |                                             |

|                   |                            | •                                                       |                           |         |                   | After Ins                             |                                      | Address HE                                               | RE                                          |

|                   | Before In                  | struction                                               |                           |         |                   |                                       | -                                    | ddress TH                                                |                                             |

|                   |                            |                                                         | address H                 | IERE    |                   |                                       | TOS = A                              | Address HE                                               | RE+1                                        |

|                   | After Inst                 | ruction<br>if FLAG<1>                                   | - 0                       |         |                   |                                       |                                      |                                                          |                                             |

|                   |                            | -                                                       | > = 0,<br>address F≠      | ALSE    |                   |                                       |                                      |                                                          |                                             |

|                   |                            | if FLAG<1><br>PC =                                      | ,                         |         |                   |                                       |                                      |                                                          |                                             |

|                   |                            | FU = 1                                                  | address TF                | KUE     |                   |                                       |                                      |                                                          |                                             |

| INCFSZ            | Increme                                                                                                                                                                                                                                                                                                           | nt f, Skip                         | o if O          |               |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|---------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | INCFSZ                             | f,d             |               |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | $0 \le f \le 127$<br>$d \in [0,1]$ |                 |               |  |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (dest), s                          | kip if resu     | ult = 0       |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              | None                               |                 |               |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                               | dfff            | ffff          |  |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                                    |                 |               |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                                    |                 |               |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                                    |                 |               |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                                 | Q3              | Q4            |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                                                                            | Read<br>register<br>'f'            | Process<br>data | Write to dest |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                                          | le)                                |                 | •             |  |  |  |  |

|                   | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                             | Q3              | Q4            |  |  |  |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                                | NOP             | NOP           |  |  |  |  |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •                                                                                                                                                                                                                                                                     |                                    |                 |               |  |  |  |  |

|                   | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if $CNT= 0$ ,<br>PC = address CONTINUE<br>if $CNT \neq 0$ ,<br>PC = address HERE + 1                                                                                                                                             |                                    |                 |               |  |  |  |  |

| IORLW             |                 |                     | eral with                                  |               |

|-------------------|-----------------|---------------------|--------------------------------------------|---------------|

| Syntax:           | [ label ]       | IORLW               | К                                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                                            |               |

| Operation:        | (W) .OR.        | $k \rightarrow (W)$ | )                                          |               |

| Status Affected:  | Z               |                     |                                            |               |

| Encoding:         | 11              | 1000                | kkkk                                       | kkkk          |

| Description:      | OR'ed wit       | h the eigh          | W register<br>t bit literal<br>ne W regist | 'k'. The      |

| Words:            | 1               |                     |                                            |               |

| Cycles:           | 1               |                     |                                            |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                                         | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data                            | Write to<br>W |

| Example           | IORLW           | 0x35                |                                            |               |

|                   | Before In       |                     | 1                                          |               |

|                   |                 | W =                 | 0x9A                                       |               |

|                   | After Inst      |                     |                                            |               |

|                   |                 | W =                 | 0xBF                                       |               |

#### SLEEP

| [ label ]                                                                                                                                                              | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| None                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| TO, PD                                                                                                                                                                 |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 00                                                                                                                                                                     | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Q1                                                                                                                                                                     | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Decode                                                                                                                                                                 | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SLEEP                                                                                                                                                                  |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                        | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |  |  |

| SUBLW             | Subtract              | W from             | Literal                                                                    |  |

|-------------------|-----------------------|--------------------|----------------------------------------------------------------------------|--|

| Syntax:           | [ label ]             | SUBL               | N k                                                                        |  |

| Operands:         | $0 \le k \le 25$      | 55                 |                                                                            |  |

| Operation:        | k - (W) $\rightarrow$ | • (W)              |                                                                            |  |

| Status Affected:  | C, DC, Z              |                    |                                                                            |  |

| Encoding:         | 11                    | 110x               | kkkk kkkł                                                                  |  |

| Description:      | ment meth             | od) from           | ubtracted (2's complet<br>the eight bit literal 'k<br>I in the W register. |  |

| Words:            | 1                     |                    |                                                                            |  |

| Cycles:           | 1                     |                    |                                                                            |  |

| Q Cycle Activity: | Q1                    | Q2                 | Q3 Q4                                                                      |  |

|                   | Decode                | Read<br>literal 'k | Process Write to data                                                      |  |

| Example 1:        | SUBLW                 | 0x02               |                                                                            |  |

|                   | Before Instruction    |                    |                                                                            |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>?<br>?                                                                |  |

|                   | After Inst            | ruction            |                                                                            |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>1; result is positive<br>0                                            |  |

| Example 2:        | Before In:            | structior          | n                                                                          |  |

|                   |                       | W =<br>C =<br>Z =  | 2<br>?<br>?                                                                |  |

|                   | After Inst            | ruction            |                                                                            |  |

|                   |                       | W =<br>C =<br>Z =  | 0<br>1; result is zero<br>1                                                |  |

| Example 3:        | Before In             | structior          | ı                                                                          |  |

| Example 0.        |                       | W =                | 3                                                                          |  |

| Example 0.        |                       |                    |                                                                            |  |

| Example 0.        |                       | C =<br>Z =         | ?<br>?                                                                     |  |

|                   | After Inst            | Z =                |                                                                            |  |

|                   | After Inst            | Z =                |                                                                            |  |

|                   | After Inst            | Z =<br>ruction     | ?                                                                          |  |

### 10.0 DEVELOPMENT SUPPORT

#### 10.1 <u>Development Tools</u>

The PICmicro<sup>™</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

#### 10.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 10.3 ICEPIC: Low-Cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

|         |                                            | Standa             | rd Operat | ting  | Conditio | ons (un  | less otherwise stated)                                                  |

|---------|--------------------------------------------|--------------------|-----------|-------|----------|----------|-------------------------------------------------------------------------|

|         |                                            | Operati            | ng temper | atur  |          | ,<br>≤ T | $A \leq +70^{\circ}C$ (commercial)                                      |

|         |                                            |                    | •         |       | -40°0    |          | A ≤ +85°C (industrial)                                                  |

| DC CHAP | RACTERISTICS                               |                    |           |       | -40°0    | C ≤T     | $A \leq +125^{\circ}C$ (extended)                                       |

|         |                                            | Operati<br>Section |           | e Vde | range a  | s descr  | ibed in DC spec Section 11.1 and                                        |

| Param   | Characteristic                             | Sym                | Min       | Тур   | Max      | Units    | Conditions                                                              |

| No.     |                                            | - C.J              |           | t     | max      | 0        |                                                                         |

|         | Output Low Voltage                         |                    |           | -     |          |          |                                                                         |

| D080    | I/O ports                                  | Vol                | -         | -     | 0.6      | V        | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                             |

| D080A   |                                            |                    | -         | -     | 0.6      | V        | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

| D083    | OSC2/CLKOUT (RC osc config)                |                    | -         | -     | 0.6      | V        | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |

| D083A   |                                            |                    | -         | -     | 0.6      | V        | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

|         | Output High Voltage                        |                    |           |       |          |          |                                                                         |

| D090    | I/O ports (Note 3)                         | Vон                | Vdd - 0.7 | -     | -        | V        | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

| D090A   |                                            |                    | Vdd - 0.7 | -     | -        | V        | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D092    | OSC2/CLKOUT (RC osc config)                |                    | Vdd - 0.7 | -     | -        | V        | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D092A   |                                            |                    | Vdd - 0.7 | -     | -        | V        | ІОН = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D130*   | Open-Drain High Voltage                    | Vod                | -         | -     | 14       | V        | RA4 pin                                                                 |

|         | Capacitive Loading Specs on<br>Output Pins |                    |           |       |          |          |                                                                         |

| D100    | OSC2 pin                                   | Cosc2              | -         | -     | 15       | pF       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101    | All I/O pins and OSC2 (in RC mode)         | Сю                 | -         | -     | 50       | pF       |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

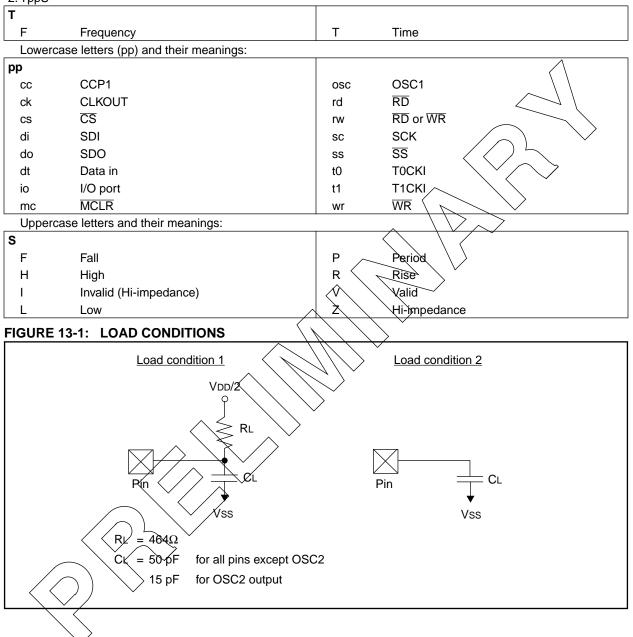

#### 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

#### 1. TppS2ppS

2. TppS

| <u></u> |                                      |     |              |  |

|---------|--------------------------------------|-----|--------------|--|

| Т       |                                      |     |              |  |

| F       | Frequency                            | Т   | Time         |  |

| Lowerc  | ase letters (pp) and their meanings: |     |              |  |

| рр      |                                      |     |              |  |

| сс      | CCP1                                 | osc | OSC1         |  |

| ck      | CLKOUT                               | rd  | RD           |  |

| CS      | CS                                   | rw  | RD or WR     |  |

| di      | SDI                                  | sc  | SCK          |  |

| do      | SDO                                  | SS  | SS           |  |

| dt      | Data in                              | tO  | TOCKI        |  |

| io      | I/O port                             | t1  | T1CKI        |  |

| mc      | MCLR                                 | wr  | WR           |  |

| Upperc  | case letters and their meanings:     |     |              |  |

| S       |                                      |     |              |  |

| F       | Fall                                 | P   | Period       |  |

| н       | High                                 | R   | Rise         |  |

| I       | Invalid (Hi-impedance)               | V   | Valid        |  |

| L       | Low                                  | Z   | Hi-impedance |  |

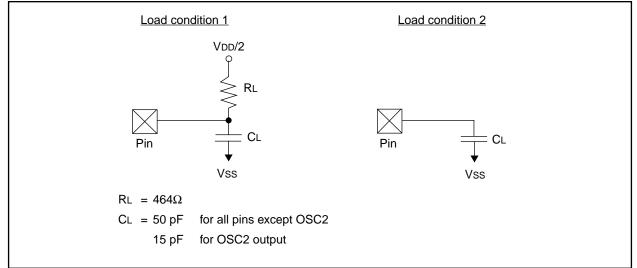

#### FIGURE 11-1: LOAD CONDITIONS

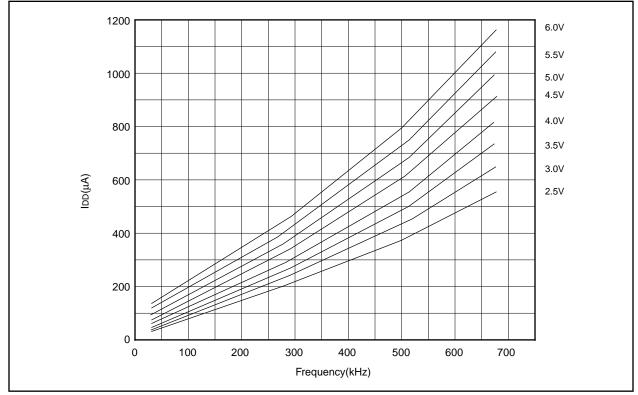

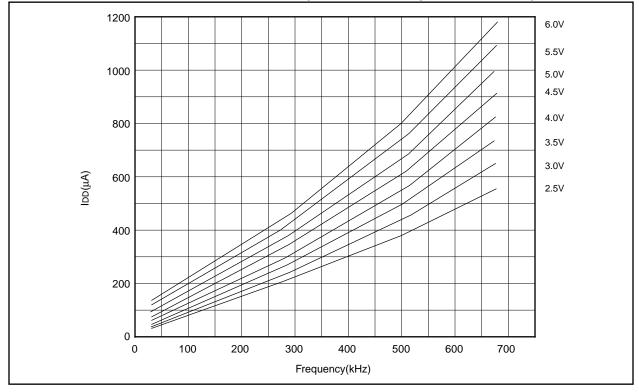

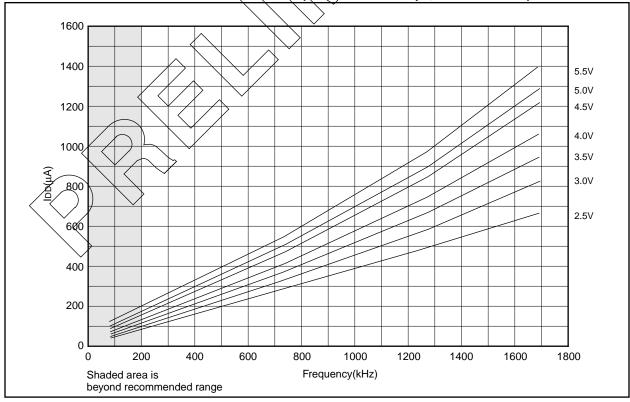

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

# 13.1 DC Characteristics: PIC16C715-04 (Commercial, Industrial, Extended) PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (

| DC CHARACTERISTICS             |                                                                   |               |            | lard Op<br>ating ter      |                      | ture (               | ditions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)                                                                                           |