Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 68 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                     |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c711t-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

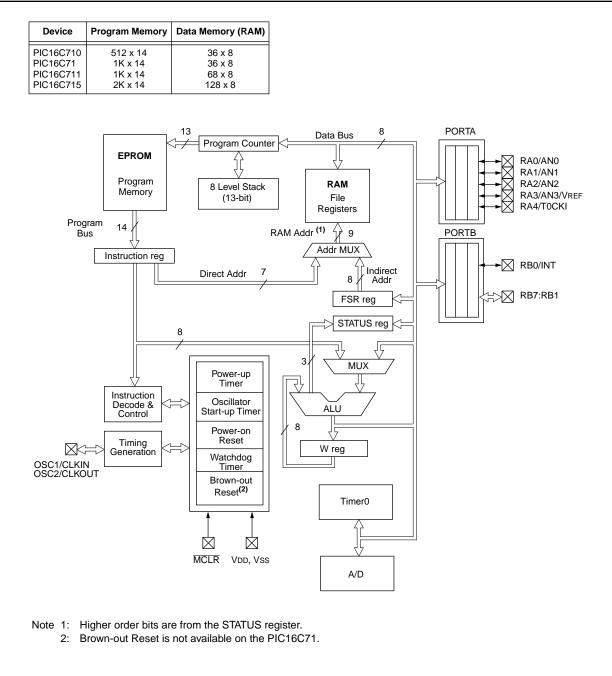

#### FIGURE 3-1: PIC16C71X BLOCK DIAGRAM

| TABLE              | 4-2:   | PIC16C7            | '15 SPEC           | CIAL FUI      | NCTION       | REGIST         | ER SUMI          | MARY          |           |                               |                                     |

|--------------------|--------|--------------------|--------------------|---------------|--------------|----------------|------------------|---------------|-----------|-------------------------------|-------------------------------------|

| Address            | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4        | Bit 3          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR, PER | Value on all<br>other resets<br>(3) |

| Bank 0             |        | -                  |                    |               |              |                |                  |               |           | -                             |                                     |

| 00h <sup>(1)</sup> | INDF   | Addressing         | this location      | uses conten   | ts of FSR to | address data   | a memory (ne     | ot a physical | register) | 0000 0000                     | 0000 0000                           |

| 01h                | TMR0   | Timer0 mod         | dule's registe     | r             |              |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 02h <sup>(1)</sup> | PCL    | Program Co         | ounter's (PC)      | Least Signif  | icant Byte   |                |                  |               |           | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO           | PD             | Z                | DC            | С         | 0001 1xxx                     | 000q quuu                           |

| 04h <sup>(1)</sup> | FSR    | Indirect data      | a memory ad        | dress pointe  | er           |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 05h                | PORTA  | _                  | _                  | _             | PORTA Dat    | a Latch whe    | n written: PO    | RTA pins wh   | en read   | x 0000                        | u 0000                              |

| 06h                | PORTB  | PORTB Dat          | ta Latch whe       | n written: PC | RTB pins w   | hen read       |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 07h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 08h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 09h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Ah <b>(1,2)</b>   | PCLATH | _                  | _                  | _             | Write Buffe  | r for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                        | 0 0000                              |

| 0Bh <sup>(1)</sup> | INTCON | GIE                | PEIE               | TOIE          | INTE         | RBIE           | TOIF             | INTF          | RBIF      | 0000 000x                     | 0000 000u                           |

| 0Ch                | PIR1   | _                  | ADIF               | _             | _            | _              | _                | _             | _         | -0                            | -0                                  |

| 0Dh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Eh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Fh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 10h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 11h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 12h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 13h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 14h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 15h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 16h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 17h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 18h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 19h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Ah                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | —                                   |

| 1Bh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Ch                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Dh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Eh                | ADRES  | A/D Result         | Register           |               |              |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 1Fh                | ADCON0 | ADCS1              | ADCS0              | CHS2          | CHS1         | CHS0           | GO/DONE          | _             | ADON      | 0000 00-0                     | 0000 00-0                           |

|                    |        |                    |                    |               |              |                |                  |               |           |                               |                                     |

TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

#### 4.2.2.2 OPTION REGISTER

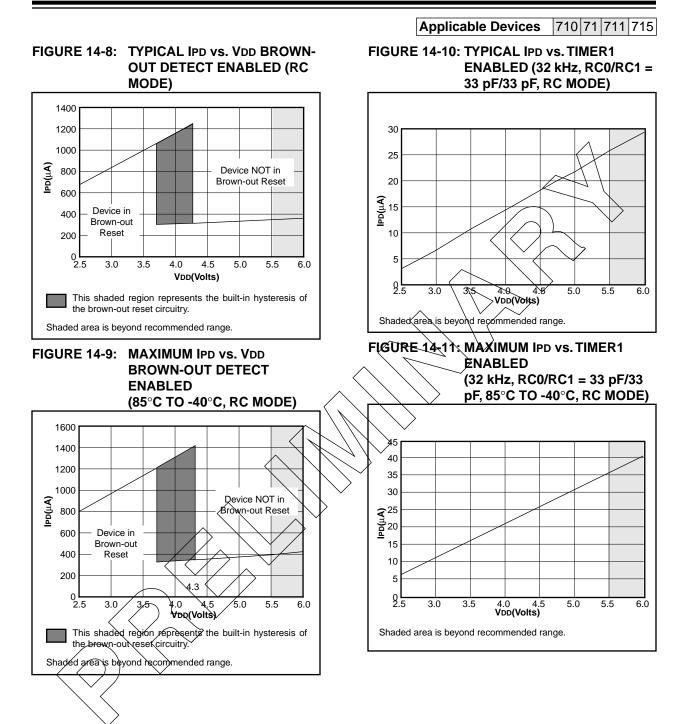

# Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

#### FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                    | R/W-1       | R/W-1       | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                                                           |

|----------|--------------------------|-------------|-------------|------------|--------------|------------|-------|-----------------------------------------------------------|

| RBPU     | INTEDG                   | TOCS        | T0SE        | PSA        | PS2          | PS1        | PS0   | R = Readable bit                                          |

| bit7     | · · ·                    |             |             |            |              |            | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

|          |                          |             |             |            |              |            |       | - n = Value at POR reset                                  |

| bit 7:   | RBPU: PC                 | RTB Pull    | -up Enabl   | le bit     |              |            |       |                                                           |

|          | 1 = PORT                 |             |             |            |              |            |       |                                                           |

|          | 0 = PORTE                | 3 pull-ups  | s are enab  | led by ind | ividual port | latch valu | es    |                                                           |

| bit 6:   | INTEDG:                  | nterrupt E  | Edge Sele   | ct bit     |              |            |       |                                                           |

|          | 1 = Interru              | pt on risir | ng edge of  | f RB0/INT  | pin          |            |       |                                                           |

|          | 0 = Interru              | pt on falli | ng edge o   | f RB0/INT  | pin          |            |       |                                                           |

| bit 5:   | TOCS: TM                 | R0 Clock    | Source S    | elect bit  |              |            |       |                                                           |

|          | 1 = Transit              |             |             |            |              |            |       |                                                           |

|          | 0 = Interna              | al instruct | ion cycle ( | clock (CLk | (OUT)        |            |       |                                                           |

| bit 4:   | TOSE: TM                 |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            | on RA4/T00   |            |       |                                                           |

|          | 0 = Increm               | ent on lo   | w-to-high   | transition | on RA4/T00   | JKI pin    |       |                                                           |

| bit 3:   | PSA: Pres                |             | 0           |            |              |            |       |                                                           |

|          | 1 = Presca<br>0 = Presca |             |             |            | modulo       |            |       |                                                           |

|          |                          |             | •           |            | module       |            |       |                                                           |

| bit 2-0: | PS2:PS0:                 | Prescale    | r Rate Sel  | lect bits  |              |            |       |                                                           |

|          | Bit Value                | TMR0 R      | ate WD      | Γ Rate     |              |            |       |                                                           |

|          | 000                      | 1:2         | 1:          |            |              |            |       |                                                           |

|          | 001                      | 1:4         | 1:          |            |              |            |       |                                                           |

|          | 010<br>011               | 1:8         | 1:          |            |              |            |       |                                                           |

|          | 100                      | 1:16        |             | 16         |              |            |       |                                                           |

|          | 101                      | 1:64        | . 1:        | 32         |              |            |       |                                                           |

|          | 110                      | 1 : 12      |             | 64         |              |            |       |                                                           |

|          | 111                      | 1:25        | 6   1       | 128        |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

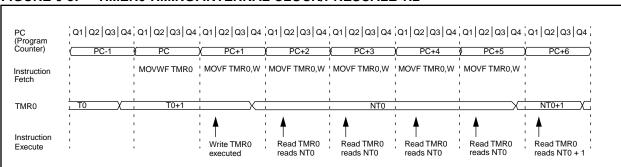

# FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

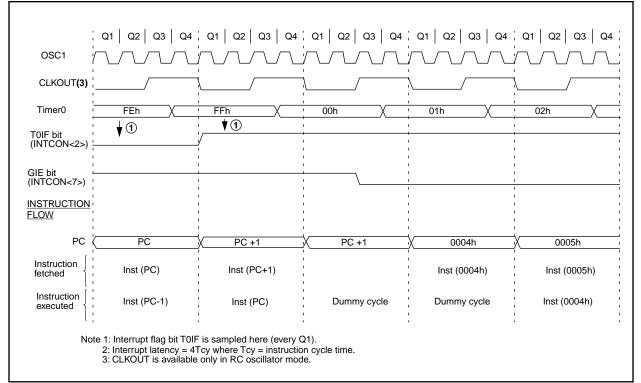

## FIGURE 6-4: TIMER0 INTERRUPT TIMING

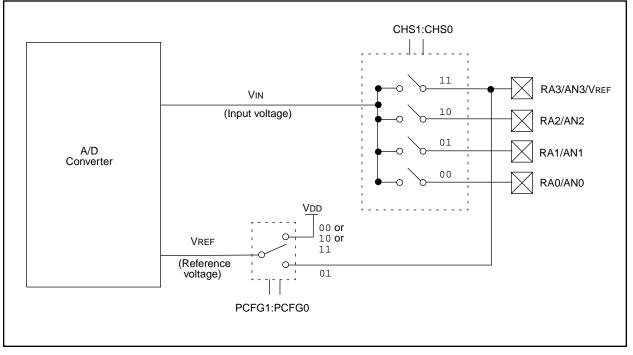

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 7-4.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 7.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- Set GIE bit

- 3. Wait the required acquisition time.

2. Configure A/D interrupt (if desired):

4. Start conversion:

Clear ADIF bit

Set ADIE bit

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 7-4: A/D BLOCK DIAGRAM

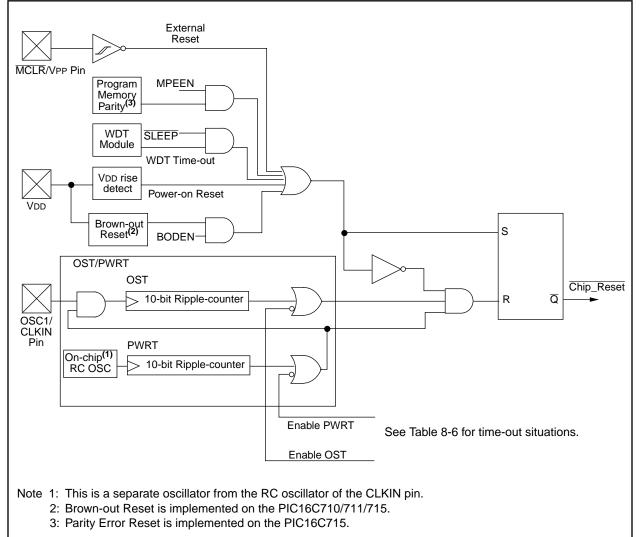

### 8.3 <u>Reset</u>

# Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and

WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

### FIGURE 8-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 8.4.5 TIME-OUT SEQUENCE

#### Applicable Devices 710 71 711 715

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

#### 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

#### Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

#### 8.4.7 PARITY ERROR RESET (PER)

#### Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

#### TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

#### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power            | r-up      | Brown out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

| Register | Power-on Reset,<br>Brown-out Reset<br>Parity Error Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|----------|----------------------------------------------------------|--------------------------|------------------------------------|

| W        | XXXX XXXX                                                | นนนน นนนน                | นนนน นนนน                          |

| INDF     | N/A                                                      | N/A                      | N/A                                |

| TMR0     | xxxx xxxx                                                | uuuu uuuu                | uuuu uuuu                          |

| PCL      | 0000 0000                                                | 0000 0000                | PC + 1(2)                          |

| STATUS   | 0001 1xxx                                                | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR      | xxxx xxxx                                                | uuuu uuuu                | uuuu uuuu                          |

| PORTA    | x 0000                                                   | u 0000                   | u uuuu                             |

| PORTB    | XXXX XXXX                                                | uuuu uuuu                | uuuu uuuu                          |

| PCLATH   | 0 0000                                                   | 0 0000                   | u uuuu                             |

| INTCON   | 0000 000x                                                | 0000 000u                | uuuu uuuu(1)                       |

| PIR1     | -0                                                       | -0                       | _ <sub>u</sub> _(1)                |

| ADCON0   | 0000 00-0                                                | 0000 00-0                | uuuu uu-u                          |

| OPTION   | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| TRISA    | 1 1111                                                   | 1 1111                   | u uuuu                             |

| TRISB    | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| PIE1     | -0                                                       | -0                       | -u                                 |

| PCON     | वेर्वेवे                                                 | luu                      | luu                                |

| ADCON1   | 00                                                       | 00                       |                                    |

### TABLE 8-13: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C715

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-11 for reset value for specific condition.

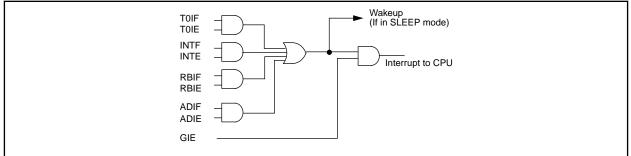

## FIGURE 8-17: INTERRUPT LOGIC, PIC16C710, 71, 711

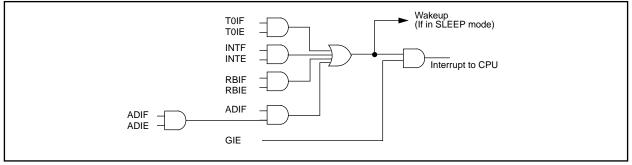

### FIGURE 8-18: INTERRUPT LOGIC, PIC16C715

#### 8.6 <u>Context Saving During Interrupts</u>

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 8-1 stores and restores the STATUS and W registers. The user register, STATUS\_TEMP, must be defined in bank 0.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### EXAMPLE 8-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W |

|----------------|--------------------|----------------------------------------------------------------------------------------|

| SWAPP          | •                  | L                                                                                      |

| MOVWF          | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                         |

| :              |                    |                                                                                        |

| :(ISR)         |                    |                                                                                        |

| :              |                    |                                                                                        |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                                                      |

|                |                    | ;(sets bank to original state)                                                         |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                           |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                           |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                    |

|                |                    |                                                                                        |

| FIGURE 8-22: WAKE-UP FROM SLEEP THROUGH INTERRUP |

|--------------------------------------------------|

|--------------------------------------------------|

| CLKOUT(4)                                                                          | ////               | (            | //                    | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u> |                  | /           |

|------------------------------------------------------------------------------------|--------------------|--------------|-----------------------|-----------------------------------------------|------------------|-------------|

| · .                                                                                | 1                  | 1 1          |                       |                                               | / IN             | /           |

| INTE flag                                                                          |                    | 1 1          | 1                     | 1 I<br>1 I                                    | 1<br>1           |             |

| (INTCON<1>)                                                                        | <br> <br>          |              | 1<br><del> </del><br> | Interrupt Latency<br>(Note 2)                 |                  |             |

| GIE bit<br>(INTCON<7>)                                                             | <br> <br> <br>     | Processor in | 1<br>1<br>1           |                                               |                  |             |

| STRUCTION FLOW                                                                     | 1<br>1<br>1        | SLEEP        | <br> <br>             | 1 1<br>1 1<br>1 1                             | 1                |             |

| PC X PC                                                                            | PC+1               | PC+2         | /<br>/X PC+2          | ↓<br>↓ PC + 2 ↓                               | ( <u>0004h</u> ) | 0005h       |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | SLEEP Inst(PC + 1) |              | Inst(PC + 2)          | 1 1<br>1 1<br>1 1                             | Inst(0004h)      | Inst(0005h) |

| Instruction { Inst(PC                                                              | - 1) SLEEP         |              | Inst(PC + 1)          | Dummy cycle                                   | Dummy cycle      | Inst(0004h) |

Δ. CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 8.9 **Program Verification/Code Protection**

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 8.10 **ID** Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

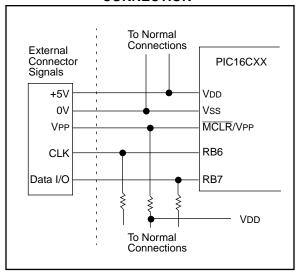

#### 8.11 In-Circuit Serial Programming

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

#### FIGURE 8-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| GOTO              | Unconditional Branch                                                                                                                                                                          |                     |                 |                |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                     | GOTO                | k               |                |  |  |  |

| Operands:         | $0 \le k \le 20$                                                                                                                                                                              | 047                 |                 |                |  |  |  |

| Operation:        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |                     |                 |                |  |  |  |

| Status Affected:  | None                                                                                                                                                                                          |                     |                 |                |  |  |  |

| Encoding:         | 10                                                                                                                                                                                            | 1kkk                | kkkk            | kkkk           |  |  |  |

| Description:      | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                 |                |  |  |  |

| Words:            | 1                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Cycles:           | 2                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                            | Q2                  | Q3              | Q4             |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                        | Read<br>literal 'k' | Process<br>data | Write to<br>PC |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                           | NOP                 | NOP             | NOP            |  |  |  |

| Example           | GOTO THERE<br>After Instruction<br>PC = Address THERE                                                                                                                                         |                     |                 |                |  |  |  |

| INCF              | Increment f                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] INCF f,d                                                                                                                                           |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                  |

| Operation:        | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:  | Z                                                                                                                                                                   |

| Encoding:         | 00 1010 dfff ffff                                                                                                                                                   |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:            | 1                                                                                                                                                                   |

| Cycles:           | 1                                                                                                                                                                   |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                         |

|                   | Decode Read register data Write to dest                                                                                                                             |

| Example           | INCF CNT, 1                                                                                                                                                         |

|                   | Before Instruction<br>CNT = 0xFF<br>Z = 0                                                                                                                           |

|                   | After Instruction                                                                                                                                                   |

|                   | $\begin{array}{rcl} CNT &=& 0x00 \\ Z &=& 1 \end{array}$                                                                                                            |

| NOP               | No Operation |       |      |      |  |  |  |

|-------------------|--------------|-------|------|------|--|--|--|

| Syntax:           | [ label ]    | NOP   |      |      |  |  |  |

| Operands:         | None         |       |      |      |  |  |  |

| Operation:        | No opera     | ition |      |      |  |  |  |

| Status Affected:  | None         |       |      |      |  |  |  |

| Encoding:         | 00           | 0000  | 0xx0 | 0000 |  |  |  |

| Description:      | No operat    | ion.  |      |      |  |  |  |

| Words:            | 1            |       |      |      |  |  |  |

| Cycles:           | 1            |       |      |      |  |  |  |

| Q Cycle Activity: | Q1           | Q2    | Q3   | Q4   |  |  |  |

|                   | Decode       | NOP   | NOP  | NOP  |  |  |  |

| Example           | NOP          | •     |      |      |  |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                      |        |                    |                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|

| Syntax:           | [ label ]                                                                                                                                                                  | RETFIE |                    |                    |

| Operands:         | None                                                                                                                                                                       |        |                    |                    |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                      | PC,    |                    |                    |

| Status Affected:  | None                                                                                                                                                                       |        |                    |                    |

| Encoding:         | 00                                                                                                                                                                         | 0000   | 0000               | 1001               |

| Monda             | and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |        |                    |                    |

| Words:            | 1                                                                                                                                                                          |        |                    |                    |

| Cycles:           | 2                                                                                                                                                                          |        |                    |                    |

| Q Cycle Activity: | Q1                                                                                                                                                                         | Q2     | Q3                 | Q4                 |

| 1st Cycle         | Decode                                                                                                                                                                     | NOP    | Set the<br>GIE bit | Pop from the Stack |

| 2nd Cycle         | NOP                                                                                                                                                                        | NOP    | NOP                | NOP                |

| Example           | RETFIE                                                                                                                                                                     |        |                    |                    |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                                                                                                                                                                           | tion Reg | gister   |      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|

| Syntax:          | [ label ]                                                                                                                                                                                                                                          | OPTION   | ١        |      |

| Operands:        | None                                                                                                                                                                                                                                               |          |          |      |

| Operation:       | $(W)\toOF$                                                                                                                                                                                                                                         | PTION    |          |      |

| Status Affected: | None                                                                                                                                                                                                                                               |          |          |      |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000     | 0110     | 0010 |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |          |          |      |

| Words:           | 1                                                                                                                                                                                                                                                  |          |          |      |

| Cycles:          | 1                                                                                                                                                                                                                                                  |          |          |      |

| Example          |                                                                                                                                                                                                                                                    |          |          |      |

|                  | To mainta<br>with futur<br>not use th                                                                                                                                                                                                              | re PIC16 | CXX prod |      |

# Applicable Devices 710 71 711 715

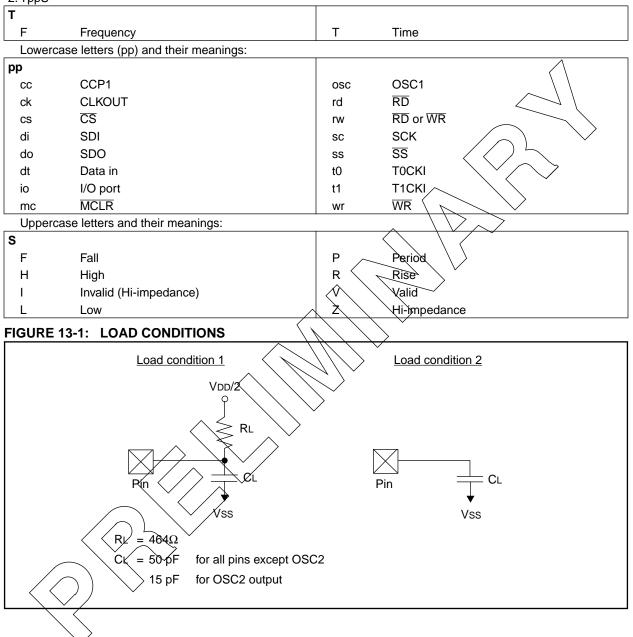

### 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

# Applicable Devices 710 71 711 715

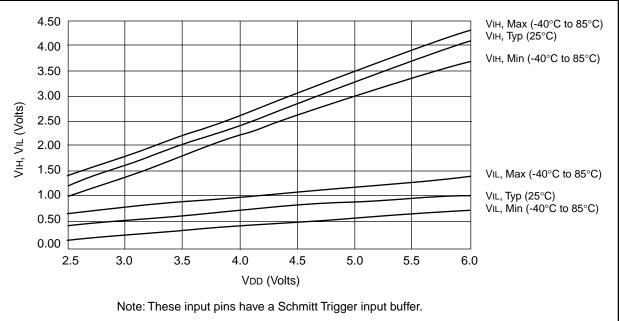

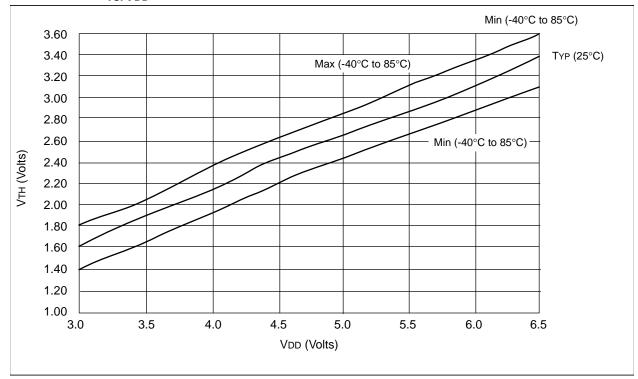

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) VS. VDD

#### FIGURE 16-11: VTH (INPUT THRESHOLD VOLTAGE) OF OSC1 INPUT (IN XT, HS, AND LP MODES) VS. VDD

# 17.0 PACKAGING INFORMATION

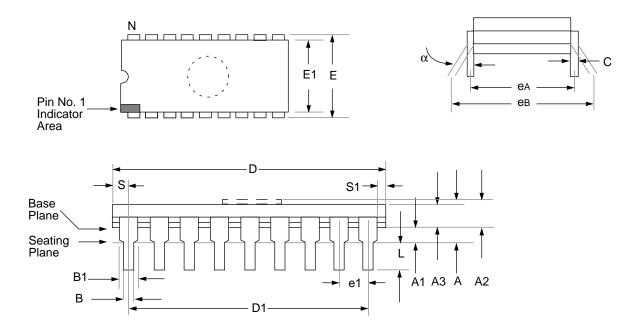

# 17.1 <u>18-Lead Ceramic CERDIP Dual In-line with Window (300 mil) (JW)</u>

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |        |             |           |            |        |           |  |

|--------------------------------------------------|--------|-------------|-----------|------------|--------|-----------|--|

|                                                  |        | Millimeters |           |            | Inches |           |  |

| Symbol                                           | Min    | Мах         | Notes     | Min        | Мах    | Notes     |  |

| α                                                | 0°     | 10°         |           | <b>0</b> ° | 10°    |           |  |

| А                                                |        | 5.080       |           |            | 0.200  |           |  |

| A1                                               | 0.381  | 1.7780      |           | 0.015      | 0.070  |           |  |

| A2                                               | 3.810  | 4.699       |           | 0.150      | 0.185  |           |  |

| A3                                               | 3.810  | 4.445       |           | 0.150      | 0.175  |           |  |

| В                                                | 0.355  | 0.585       |           | 0.014      | 0.023  |           |  |

| B1                                               | 1.270  | 1.651       | Typical   | 0.050      | 0.065  | Typical   |  |

| С                                                | 0.203  | 0.381       | Typical   | 0.008      | 0.015  | Typical   |  |

| D                                                | 22.352 | 23.622      |           | 0.880      | 0.930  |           |  |

| D1                                               | 20.320 | 20.320      | Reference | 0.800      | 0.800  | Reference |  |

| E                                                | 7.620  | 8.382       |           | 0.300      | 0.330  |           |  |

| E1                                               | 5.588  | 7.874       |           | 0.220      | 0.310  |           |  |

| e1                                               | 2.540  | 2.540       | Reference | 0.100      | 0.100  | Reference |  |

| eA                                               | 7.366  | 8.128       | Typical   | 0.290      | 0.320  | Typical   |  |

| eB                                               | 7.620  | 10.160      |           | 0.300      | 0.400  |           |  |

| L                                                | 3.175  | 3.810       |           | 0.125      | 0.150  |           |  |

| N                                                | 18     | 18          |           | 18         | 18     |           |  |

| S                                                | 0.508  | 1.397       |           | 0.020      | 0.055  |           |  |

| S1                                               | 0.381  | 1.270       |           | 0.015      | 0.050  |           |  |

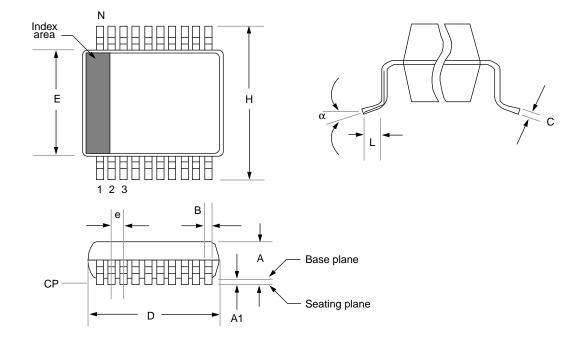

#### 17.4 20-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

|        | Package Group: Plastic SSOP |             |           |       |        |           |  |

|--------|-----------------------------|-------------|-----------|-------|--------|-----------|--|

|        |                             | Millimeters |           |       | Inches |           |  |

| Symbol | Min                         | Max         | Notes     | Min   | Max    | Notes     |  |

| α      | 0°                          | 8°          |           | 0°    | 8°     |           |  |

| А      | 1.730                       | 1.990       |           | 0.068 | 0.078  |           |  |

| A1     | 0.050                       | 0.210       |           | 0.002 | 0.008  |           |  |

| В      | 0.250                       | 0.380       |           | 0.010 | 0.015  |           |  |

| С      | 0.130                       | 0.220       |           | 0.005 | 0.009  |           |  |

| D      | 7.070                       | 7.330       |           | 0.278 | 0.289  |           |  |

| E      | 5.200                       | 5.380       |           | 0.205 | 0.212  |           |  |

| е      | 0.650                       | 0.650       | Reference | 0.026 | 0.026  | Reference |  |

| Н      | 7.650                       | 7.900       |           | 0.301 | 0.311  |           |  |

| L      | 0.550                       | 0.950       |           | 0.022 | 0.037  |           |  |

| N      | 20                          | 20          |           | 20    | 20     |           |  |

| CP     | -                           | 0.102       |           | -     | 0.004  |           |  |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

- 2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

- 3: This outline conforms to JEDEC MS-026.

### 17.5 Package Marking Information

18-Lead CERDIP Windowed

#### 20-Lead SSOP

Example

## Example

### Example

### Example

| Legend: | MMM<br>XXX<br>AA<br>BB<br>C<br>D1<br>E | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calender year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.<br>Mask revision number for microcontroller<br>Assembly code of the plant or country of origin in which<br>part was assembled. |

|---------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | line, it will                          | ent the full Microchip part number cannot be marked on one<br>be carried over to the next line thus limiting the number of<br>characters for customer specific information.                                                                                                                                                                                                                                                 |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

| RA2/AN2                                                                | a                                     |

|------------------------------------------------------------------------|---------------------------------------|

|                                                                        |                                       |

| RA3/AN3/VREF                                                           | -                                     |

| RA4/T0CKI                                                              | 9                                     |

| RB0/INT                                                                | 9                                     |

| RB1                                                                    | -                                     |

|                                                                        | -                                     |

| RB2                                                                    | 9                                     |

| RB3                                                                    | 9                                     |

| RB4                                                                    |                                       |

|                                                                        | -                                     |

| RB5                                                                    | 9                                     |

| RB6                                                                    | 9                                     |

| RB7                                                                    | a                                     |

|                                                                        | -                                     |

| VDD                                                                    |                                       |

| Vss                                                                    | 9                                     |

| Pinout Descriptions                                                    |                                       |

| PIC16C71                                                               | 0                                     |

|                                                                        |                                       |

| PIC16C710                                                              | 9                                     |

| PIC16C711                                                              | 9                                     |

| PIC16C715                                                              | -                                     |

|                                                                        |                                       |

| PIR1 Register                                                          | 21                                    |

| POP                                                                    | 23                                    |

| POR                                                                    | 53 54                                 |

|                                                                        |                                       |

| Oscillator Start-up Timer (OST)                                        | 47, 53                                |

| Power Control Register (PCON)                                          | 54                                    |

| Power-on Reset (POR)                                                   | 3 57 58                               |

|                                                                        | 47 50                                 |

| Power-up Timer (PWRT)                                                  |                                       |

| Time-out Sequence                                                      | 54                                    |

| Time-out Sequence on Power-up                                          | 59                                    |

| TO                                                                     |                                       |

|                                                                        |                                       |

| POR bit                                                                | 22, 54                                |

| Port RB Interrupt                                                      | 63                                    |

| PORTA                                                                  |                                       |

|                                                                        |                                       |

| PORTA Register 1                                                       | 4, 15, 25                             |

| PORTB                                                                  | 57. 58                                |

| PORTB Register1                                                        | ,                                     |

|                                                                        |                                       |

| Power-down Mode (SLEEP)                                                |                                       |

| Prescaler, Switching Between Timer0 and WDT                            | 35                                    |

| PRO MATE <sup>®</sup> II Universal Programmer                          | 85                                    |

|                                                                        |                                       |

| Program Branches                                                       |                                       |

| Program Memory                                                         |                                       |

| Paging                                                                 | 23                                    |

| Program Memory Maps                                                    |                                       |

|                                                                        |                                       |

| PIC16C71                                                               | 11                                    |

| PIC16C710                                                              | 11                                    |

| PIC16C711                                                              | 11                                    |

|                                                                        |                                       |

| PIC16C715                                                              |                                       |

| Program Verification                                                   | 67                                    |

| PS0 bit                                                                |                                       |

| PS1 bit                                                                | -                                     |

|                                                                        |                                       |

| PS2 bit                                                                |                                       |

| PSA bit                                                                | 18                                    |

| PUSH                                                                   | 23                                    |

|                                                                        |                                       |

| PWRT                                                                   |                                       |

| Power-up Timer (PWRT)                                                  | 53                                    |

| PWRTE bit                                                              | 47 48                                 |

|                                                                        | ,                                     |

| R                                                                      |                                       |

|                                                                        |                                       |

| RBIE bit                                                               |                                       |

|                                                                        |                                       |

| KDIF DIL                                                               |                                       |

| RBIF bit1                                                              | 9, 27, 63                             |

| RBPU bit                                                               | 9, 27, 63<br>18                       |

|                                                                        | 9, 27, 63<br>18                       |

| RBPU bit                                                               | 9, 27, 63<br>18<br>54                 |

| RBPU bit<br>RC<br>RC Oscillator                                        | 9, 27, 63<br>18<br>54<br>51, 54       |

| RBPU bit          RC          RC Oscillator          Read-Modify-Write | 9, 27, 63<br>18<br>54<br>51, 54<br>30 |

| RBPU bit<br>RC<br>RC Oscillator                                        | 9, 27, 63<br>18<br>54<br>51, 54<br>30 |

| RBPU bit          RC          RC Oscillator          Read-Modify-Write | 9, 27, 63<br>18<br>54<br>51, 54<br>30 |

| <b>DIO100711</b>                         | 10     |

|------------------------------------------|--------|

| PIC16C711                                |        |

| PIC16C715                                | 13     |

| Reset Conditions                         | 56     |

| Summary                                  |        |

| Reset                                    | 47, 52 |

| Reset Conditions for Special Registers . |        |

| RP0 bit                                  | 12, 17 |

| RP1 bit                                  | 17     |

# S

|            | Evaluation and Programming System   | n87           |  |  |

|------------|-------------------------------------|---------------|--|--|

| Services   |                                     |               |  |  |

|            | ime-Programmable (OTP) Devices .    |               |  |  |

|            | -Turnaround-Production (QTP) Devic  |               |  |  |

|            | ized Quick-Turnaround Production (S |               |  |  |

|            | es                                  |               |  |  |

|            |                                     |               |  |  |

|            | imulator (MPLAB™ SIM)               |               |  |  |

|            | atures of the CPU                   | 47            |  |  |

|            | nction Registers                    |               |  |  |

| PIC16      | SC71                                | 14            |  |  |

| PIC16      | 6C710                               | 14            |  |  |

| PIC16      | 6C711                               | 14            |  |  |

| Special Fu | nction Registers, Section           | 14            |  |  |

|            |                                     |               |  |  |

|            | ows                                 |               |  |  |

|            | flow                                |               |  |  |

|            | egister                             |               |  |  |

| 01/1001    |                                     |               |  |  |

| Т          |                                     |               |  |  |

| TOCS hit   |                                     | 18            |  |  |

|            |                                     |               |  |  |

|            |                                     |               |  |  |

|            |                                     |               |  |  |

|            |                                     | 41            |  |  |

| Timer0     |                                     |               |  |  |

|            | ;                                   | 57, 58        |  |  |

| Timers     |                                     |               |  |  |

| Timer      |                                     |               |  |  |

| E          | Block Diagram                       | 31            |  |  |

| E          | External Clock                      |               |  |  |

| E          | External Clock Timing               | 33            |  |  |

|            | ncrement Delay                      |               |  |  |

|            | nterrupt                            |               |  |  |

|            | nterrupt Timing                     |               |  |  |

|            | Prescaler                           |               |  |  |

|            | Prescaler Block Diagram             |               |  |  |

|            | Section                             |               |  |  |

|            |                                     |               |  |  |

|            | Switching Prescaler Assignment      |               |  |  |

|            | Synchronization                     |               |  |  |

|            |                                     |               |  |  |

|            | TOIF                                |               |  |  |

|            | Timing                              |               |  |  |

|            | MR0 Interrupt                       | 63            |  |  |

| Timing Dia | •                                   |               |  |  |

| A/D C      | onversion                           | 100, 124, 146 |  |  |

| Brown      | n-out Reset                         | 53, 97        |  |  |

| CLKO       | UT and I/O                          | 96, 119, 142  |  |  |

| Exterr     | nal Clock Timing                    | 95, 118, 141  |  |  |

|            | r-up Timer                          |               |  |  |

|            |                                     |               |  |  |

|            | up Timer                            | ,             |  |  |

|            | out Sequence                        |               |  |  |

|            |                                     |               |  |  |

| Timer      | 0                                   | 50, 121, 144  |  |  |

| i imer     | 0 Interrupt Timing                  |               |  |  |

|            | 0 with External Clock               |               |  |  |

|            | -up from SLEEP through Interrupt    |               |  |  |

| Watch      | ndog Timer                          | 97, 143       |  |  |

Maps