Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 PIC16C71X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C71X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C71X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**71. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC71. These devices have EPROM type memory and operate over an extended voltage range.

### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C71X.

### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

| TABLE              | 4-2:   | PIC16C7            | '15 SPEC           | CIAL FUI      | NCTION       | REGIST         | ER SUMI          | MARY          |           |                               |                                     |

|--------------------|--------|--------------------|--------------------|---------------|--------------|----------------|------------------|---------------|-----------|-------------------------------|-------------------------------------|

| Address            | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4        | Bit 3          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR, PER | Value on all<br>other resets<br>(3) |

| Bank 0             |        | -                  |                    |               |              |                |                  |               |           | -                             |                                     |

| 00h <sup>(1)</sup> | INDF   | Addressing         | this location      | uses conten   | ts of FSR to | address data   | a memory (ne     | ot a physical | register) | 0000 0000                     | 0000 0000                           |

| 01h                | TMR0   | Timer0 mod         | dule's registe     | r             |              |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 02h <sup>(1)</sup> | PCL    | Program Co         | ounter's (PC)      | Least Signif  | icant Byte   |                |                  |               |           | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO           | PD             | Z                | DC            | С         | 0001 1xxx                     | 000q quuu                           |

| 04h <sup>(1)</sup> | FSR    | Indirect data      | a memory ad        | dress pointe  | er           |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 05h                | PORTA  | _                  | _                  | _             | PORTA Dat    | a Latch whe    | n written: PO    | RTA pins wh   | en read   | x 0000                        | u 0000                              |

| 06h                | PORTB  | PORTB Dat          | ta Latch whe       | n written: PC | RTB pins w   | hen read       |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 07h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 08h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 09h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Ah <b>(1,2)</b>   | PCLATH | _                  | _                  | _             | Write Buffe  | r for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                        | 0 0000                              |

| 0Bh <sup>(1)</sup> | INTCON | GIE                | PEIE               | TOIE          | INTE         | RBIE           | TOIF             | INTF          | RBIF      | 0000 000x                     | 0000 000u                           |

| 0Ch                | PIR1   | _                  | ADIF               | _             | _            | _              | _                | _             | _         | -0                            | -0                                  |

| 0Dh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Eh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 0Fh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 10h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 11h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 12h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 13h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 14h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 15h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 16h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 17h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 18h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 19h                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Ah                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | —                                   |

| 1Bh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Ch                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Dh                | _      | Unimpleme          | nted               |               |              |                |                  |               |           | _                             | _                                   |

| 1Eh                | ADRES  | A/D Result         | Register           |               |              |                |                  |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 1Fh                | ADCON0 | ADCS1              | ADCS0              | CHS2          | CHS1         | CHS0           | GO/DONE          | —             | ADON      | 0000 00-0                     | 0000 00-0                           |

|                    |        |                    |                    |               |              |                |                  |               |           |                               |                                     |

TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

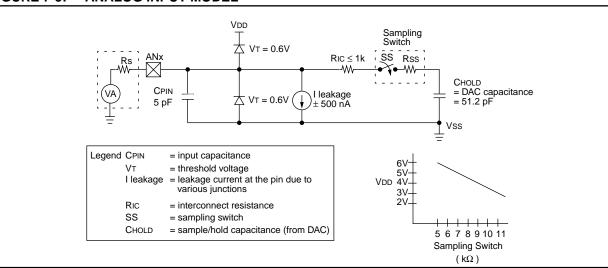

### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

### EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

### FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

### EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

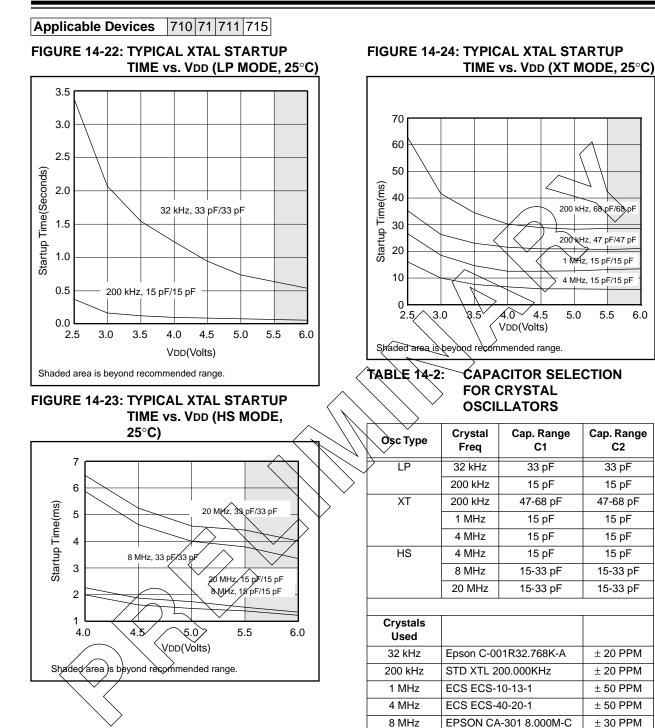

### 8.2 <u>Oscillator Configurations</u>

### 8.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

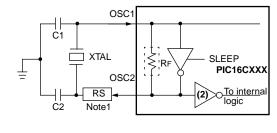

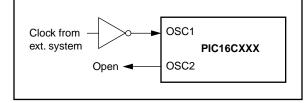

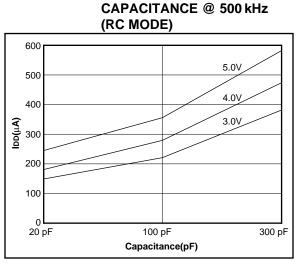

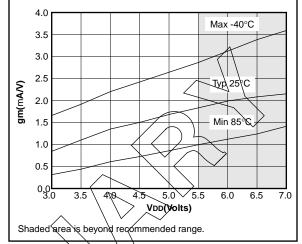

## 8.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-4). The PIC16CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 8-5).

### FIGURE 8-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

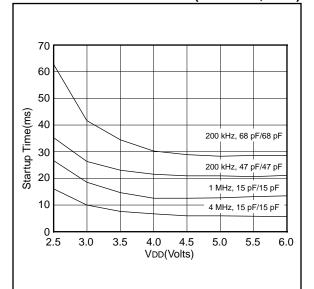

See Table 8-1 and Table 8-1 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: The buffer is on the OSC2 pin.

### FIGURE 8-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

## TABLE 8-1: CERAMIC RESONATORS, PIC16C71

| Ranges Tested:                         |                                                       |                                         |                                         |  |  |  |

|----------------------------------------|-------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode                                   | Freq                                                  | OSC1                                    | OSC2                                    |  |  |  |

| ХТ                                     | 455 kHz<br>2.0 MHz<br>4.0 MHz                         | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                     | 8.0 MHz<br>16.0 MHz                                   | 15 - 68 pF<br>10 - 47 pF                | 15 - 68 pF<br>10 - 47 pF                |  |  |  |

|                                        | se values are for<br>es at bottom of page             |                                         | nce only. See                           |  |  |  |

| Resonator                              | s Used:                                               |                                         |                                         |  |  |  |

| 455 kHz                                | Panasonic EF                                          | D-A455K04B                              | ± 0.3%                                  |  |  |  |

| 2.0 MHz                                | Murata Erie CS                                        | SA2.00MG                                | ± 0.5%                                  |  |  |  |

| 4.0 MHz                                | .0 MHz Murata Erie CSA4.00MG ± 0.5%                   |                                         |                                         |  |  |  |

| 8.0 MHz                                | Murata Erie CSA8.00MT ± 0.5%                          |                                         |                                         |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ± 0.5% |                                                       |                                         |                                         |  |  |  |

| All reso                               | All resonators used did not have built-in capacitors. |                                         |                                         |  |  |  |

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16C71

| Mode                                                                    | Freq    | OSC1        | OSC2        |  |  |

|-------------------------------------------------------------------------|---------|-------------|-------------|--|--|

| LP                                                                      | 32 kHz  | 33 - 68 pF  | 33 - 68 pF  |  |  |

|                                                                         | 200 kHz | 15 - 47 pF  | 15 - 47 pF  |  |  |

| XT                                                                      | 100 kHz | 47 - 100 pF | 47 - 100 pF |  |  |

|                                                                         | 500 kHz | 20 - 68 pF  | 20 - 68 pF  |  |  |

|                                                                         | 1 MHz   | 15 - 68 pF  | 15 - 68 pF  |  |  |

|                                                                         | 2 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |  |

|                                                                         | 4 MHz   | 15 - 33 pF  | 15 - 33 pF  |  |  |

| HS                                                                      | 8 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |  |

|                                                                         | 20 MHz  | 15 - 47 pF  | 15 - 47 pF  |  |  |

| These values are for design guidance only. See notes at bottom of page. |         |             |             |  |  |

### 8.4.5 TIME-OUT SEQUENCE

### Applicable Devices 710 71 711 715

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

### 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

### Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

### 8.4.7 PARITY ERROR RESET (PER)

### Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

### TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power-up         |           | Brown out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

### 9.1 Instruction Descriptions

|                   |                                                                                                                                 | •                   | _               |               |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|

| ADDLW             | Add Lite                                                                                                                        | ral and \           | N               |               |  |  |

| Syntax:           | [ <i>label</i> ] Al                                                                                                             | DDLW                | k               |               |  |  |

| Operands:         | $0 \le k \le 25$                                                                                                                | 55                  |                 |               |  |  |

| Operation:        | $(W) + k \to (W)$                                                                                                               |                     |                 |               |  |  |

| Status Affected:  | C, DC, Z                                                                                                                        |                     |                 |               |  |  |

| Encoding:         | 11                                                                                                                              | 111x                | kkkk            | kkkk          |  |  |

| Description:      | The conter<br>added to the result is play                                                                                       | ne eight b          | it literal 'k'  | and the       |  |  |

| Words:            | 1                                                                                                                               |                     |                 |               |  |  |

| Cycles:           | 1                                                                                                                               |                     |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                                                                              | Q2                  | Q3              | Q4            |  |  |

|                   | Decode                                                                                                                          | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |

| Example:          | ADDLW $0x15$<br>Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                 |                     |                 |               |  |  |

| ADDWF             | Add W a                                                                                                                         | nd f                |                 |               |  |  |

| Syntax:           | [ <i>label</i> ] Al                                                                                                             | DDWF                | f,d             |               |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$                                                       | 7                   |                 |               |  |  |

| Operation:        | (W) + (f) -                                                                                                                     | ightarrow (dest)    |                 |               |  |  |

| Status Affected:  | C, DC, Z                                                                                                                        |                     |                 |               |  |  |

| Encoding:         | 00 0111 dfff ffff                                                                                                               |                     |                 |               |  |  |

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the |                     |                 |               |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff             |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|------------------|--|--|

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                         |                 |                  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4               |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to<br>Dest |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0x17<br>0xC2    |                  |  |  |

|                   | After Inst                                                                                                                                                                |                         | 0               |                  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                  |  |  |

| ANDLW             | AND Lite                           | eral with                | w               |               |  |  |  |

|-------------------|------------------------------------|--------------------------|-----------------|---------------|--|--|--|

| Syntax:           | [ <i>label</i> ] A                 | [ <i>label</i> ] ANDLW k |                 |               |  |  |  |

| Operands:         | $0 \le k \le 2$                    | $0 \le k \le 255$        |                 |               |  |  |  |

| Operation:        | (W) .AND. (k) $\rightarrow$ (W)    |                          |                 |               |  |  |  |

| Status Affected:  | Z                                  |                          |                 |               |  |  |  |

| Encoding:         | 11                                 | 1001                     | kkkk            | kkkk          |  |  |  |

| Description:      | The conte<br>AND'ed wiresult is pl | ith the eig              | ht bit litera   | 'k'.The       |  |  |  |

| Words:            | 1                                  |                          |                 |               |  |  |  |

| Cycles:           | 1                                  |                          |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                 | Q2                       | Q3              | Q4            |  |  |  |

|                   | Decode                             | Read<br>literal "k"      | Process<br>data | Write to<br>W |  |  |  |

| Example           | ANDLW                              | 0x5F                     |                 |               |  |  |  |

|                   | Before In                          | struction                | 0xA3            |               |  |  |  |

|                   | After Inst                         | •• –                     | UXAU            |               |  |  |  |

|                   |                                    | = W                      | 0x03            |               |  |  |  |

|                   |                                    |                          |                 |               |  |  |  |

| ANDWF             | AND W v                                                               | vith f                     |                                              |                  |  |  |  |

|-------------------|-----------------------------------------------------------------------|----------------------------|----------------------------------------------|------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                    | [ <i>label</i> ] ANDWF f,d |                                              |                  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                    |                            |                                              |                  |  |  |  |

| Operation:        | (W) .ANE                                                              | D. (f) $\rightarrow$ (c    | dest)                                        |                  |  |  |  |

| Status Affected:  | Z                                                                     |                            |                                              |                  |  |  |  |

| Encoding:         | 00                                                                    | 0101                       | dfff                                         | ffff             |  |  |  |

| Description:      | 'd' is 0 the                                                          | result is a 'd' is 1 the   | with regist<br>stored in th<br>e result is s | ie W             |  |  |  |

| Words:            | 1                                                                     |                            |                                              |                  |  |  |  |

| Cycles:           | 1                                                                     |                            |                                              |                  |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                         | Q3                                           | Q4               |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f'    | Process<br>data                              | Write to<br>Dest |  |  |  |

| Example           | ANDWF                                                                 | FSR,                       | 1                                            |                  |  |  |  |

|                   | Before In                                                             |                            |                                              |                  |  |  |  |

|                   | W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02 |                            |                                              |                  |  |  |  |

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |

|                   | FLAG_REG = 0xC7<br>If Skig             | If Skip:          | (2nd Cycle)                                                                   |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |

| •                     |      |

|-----------------------|------|

| Before Instruction    |      |

| PC = address          | HERE |

| After Instruction     |      |

| if $FLAG < 1 > = 0$ , |      |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                           |                          |                 |                       |  |  |

|-------------------|---------------------------------------------------------------------|--------------------------|-----------------|-----------------------|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                 | [ <i>label</i> ] BSF f,b |                 |                       |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                          |                 |                       |  |  |

| Operation:        | $1 \rightarrow (f < b)$                                             | >)                       |                 |                       |  |  |

| Status Affected:  | None                                                                |                          |                 |                       |  |  |

| Encoding:         | 01 01bb bfff ffff                                                   |                          |                 |                       |  |  |

| Description:      | Bit 'b' in register 'f' is set.                                     |                          |                 |                       |  |  |

| Words:            | 1                                                                   |                          |                 |                       |  |  |

| Cycles:           | 1                                                                   |                          |                 |                       |  |  |

| Q Cycle Activity: | Q1                                                                  | Q2                       | Q3              | Q4                    |  |  |

|                   | Decode                                                              | Read<br>register<br>'f'  | Process<br>data | Write<br>register 'f' |  |  |

| Example           | After Inst                                                          | FLAG_RE                  |                 |                       |  |  |

| GOTO                                                          | Unconditional Branch                                                                                                                                                                          |                     |                 |                |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|--|--|--|

| Syntax:                                                       | [ label ]                                                                                                                                                                                     | GOTO                | k               |                |  |  |  |

| Operands:                                                     | $0 \le k \le 2047$                                                                                                                                                                            |                     |                 |                |  |  |  |

| Operation:                                                    | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |                     |                 |                |  |  |  |

| Status Affected:                                              | None                                                                                                                                                                                          |                     |                 |                |  |  |  |

| Encoding:                                                     | 10 1kkk kkkk kk                                                                                                                                                                               |                     |                 |                |  |  |  |

| Description:                                                  | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                 |                |  |  |  |

| Words:                                                        | 1                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Cycles:                                                       | 2                                                                                                                                                                                             |                     |                 |                |  |  |  |

| Q Cycle Activity:                                             | Q1                                                                                                                                                                                            | Q2                  | Q3              | Q4             |  |  |  |

| 1st Cycle                                                     | Decode                                                                                                                                                                                        | Read<br>literal 'k' | Process<br>data | Write to<br>PC |  |  |  |

| 2nd Cycle                                                     | NOP                                                                                                                                                                                           | NOP                 | NOP             | NOP            |  |  |  |

| Example GOTO THERE<br>After Instruction<br>PC = Address THERE |                                                                                                                                                                                               |                     |                 |                |  |  |  |

| INCF              | Increment f                                                                                                                                                         |               |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

| Syntax:           | [label] INCF f,d                                                                                                                                                    |               |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                   |               |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |               |  |  |  |

| Status Affected:  | Z                                                                                                                                                                   |               |  |  |  |

| Encoding:         | 00 1010 dfff                                                                                                                                                        | ffff          |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |               |  |  |  |

| Words:            | 1                                                                                                                                                                   |               |  |  |  |

| Cycles:           | 1                                                                                                                                                                   |               |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3                                                                                                                                                            | Q4            |  |  |  |

|                   | Decode Read register data                                                                                                                                           | Write to dest |  |  |  |

| Example           | INCF CNT, 1                                                                                                                                                         |               |  |  |  |

|                   | Before Instruction<br>CNT = 0<br>Z = 0                                                                                                                              | ٢F            |  |  |  |

|                   | After Instruction                                                                                                                                                   |               |  |  |  |

|                   | $\begin{array}{rcl} CNT &=& 0;\\ Z &=& 1 \end{array}$                                                                                                               | <00           |  |  |  |

| INCFSZ            | Increme                                                                                                                                                                                                                                                                                                           | nt f, Skip                                       | o if O          |               |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|---------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | INCFSZ                                           | f,d             |               |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | $0 \le f \le 127$<br>$d \in [0,1]$               |                 |               |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (f) + 1 $\rightarrow$ (dest), skip if result = 0 |                 |               |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              |                                                  |                 |               |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                                             | dfff            | ffff          |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                                                  |                 |               |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                                                  |                 |               |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                                                  |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                                               | Q3              | Q4            |  |  |  |

|                   | Decode Read<br>register<br>'f'                                                                                                                                                                                                                                                                                    |                                                  | Process<br>data | Write to dest |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                                          | le)                                              |                 | •             |  |  |  |

|                   | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                                           | Q3              | Q4            |  |  |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                                              | NOP             | NOP           |  |  |  |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •                                                                                                                                                                                                                                                                     |                                                  |                 |               |  |  |  |

|                   | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONT<br>if CNT≠ 0,<br>PC = address HERE                                                                                                                                                               |                                                  |                 |               |  |  |  |

| IORLW             |                   |                     | eral with                                  |               |  |

|-------------------|-------------------|---------------------|--------------------------------------------|---------------|--|

| Syntax:           | [ label ]         | IORLW               | К                                          |               |  |

| Operands:         | $0 \le k \le 2$   | 55                  |                                            |               |  |

| Operation:        | (W) .OR.          | $k \rightarrow (W)$ | )                                          |               |  |

| Status Affected:  | Z                 |                     |                                            |               |  |

| Encoding:         | 11                | 1000                | kkkk                                       | kkkk          |  |

| Description:      | OR'ed wit         | h the eigh          | W register<br>t bit literal<br>ne W regist | 'k'. The      |  |

| Words:            | 1                 |                     |                                            |               |  |

| Cycles:           | 1                 |                     |                                            |               |  |

| Q Cycle Activity: | Q1                | Q2                  | Q3                                         | Q4            |  |

|                   | Decode            | Read<br>literal 'k' | Process<br>data                            | Write to<br>W |  |

| Example           | IORLW             | 0x35                |                                            |               |  |

|                   | Before In         |                     | 1                                          |               |  |

|                   |                   | W =                 | 0x9A                                       |               |  |

|                   | After Instruction |                     |                                            |               |  |

|                   |                   | W =                 | 0xBF                                       |               |  |

| NOP               | No Operation |      |      |      |  |  |  |

|-------------------|--------------|------|------|------|--|--|--|

| Syntax:           | [ label ]    | NOP  |      |      |  |  |  |

| Operands:         | None         |      |      |      |  |  |  |

| Operation:        | No operation |      |      |      |  |  |  |

| Status Affected:  | None         |      |      |      |  |  |  |

| Encoding:         | 00           | 0000 | 0xx0 | 0000 |  |  |  |

| Description:      | No operat    | ion. |      |      |  |  |  |

| Words:            | 1            |      |      |      |  |  |  |

| Cycles:           | 1            |      |      |      |  |  |  |

| Q Cycle Activity: | Q1           | Q2   | Q3   | Q4   |  |  |  |

|                   | Decode       | NOP  | NOP  | NOP  |  |  |  |

| Example           | NOP          |      |      |      |  |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                                                               |        |                    |                    |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                           | RETFIE |                    |                    |  |  |

| Operands:         | None                                                                                                                                                                                                                |        |                    |                    |  |  |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                                                               | PC,    |                    |                    |  |  |

| Status Affected:  | None                                                                                                                                                                                                                |        |                    |                    |  |  |

| Encoding:         | 00 0000 0000 1001                                                                                                                                                                                                   |        |                    |                    |  |  |

| Monda             | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |        |                    |                    |  |  |

| Words:            | 1                                                                                                                                                                                                                   |        |                    |                    |  |  |

| Cycles:           | 2                                                                                                                                                                                                                   |        |                    |                    |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                  | Q2     | Q3                 | Q4                 |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                                              | NOP    | Set the<br>GIE bit | Pop from the Stack |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                                                 | NOP    | NOP                | NOP                |  |  |

| Example           | RETFIE                                                                                                                                                                                                              |        |                    |                    |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                                                                                                                                                                          | tion Reg | gister |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                         | OPTION   | ٧      |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                              |          |        |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                          |          |        |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                              |          |        |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                 |          |        |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it |          |        |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                 |          |        |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                 |          |        |  |  |  |

| Example          |                                                                                                                                                                                                                                                   |          |        |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                |          |        |  |  |  |

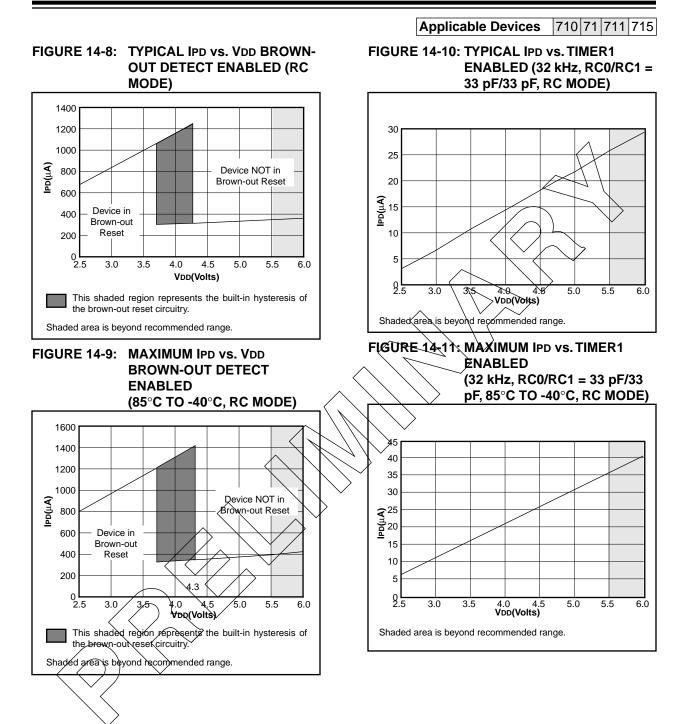

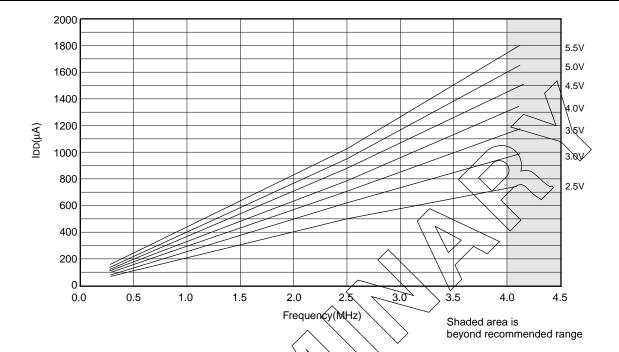

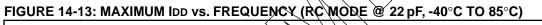

#### Applicable Devices 710 71 711 715

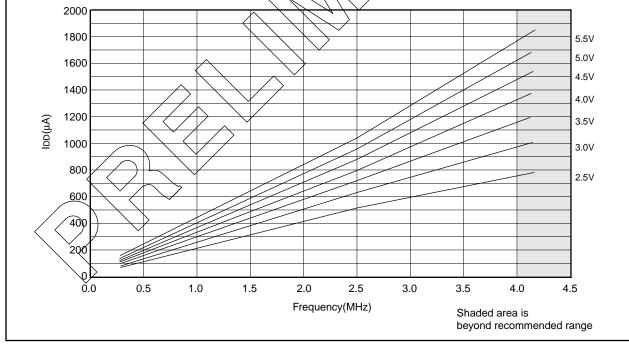

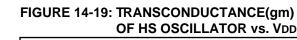

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHAF                        | RACTERISTICS                                                      |               |             | ard Ope<br>ing tem       |                    | ire 0°(<br>-4        | itions (unless otherwise stated)C $\leq$ TA $\leq$ +70°C (commercial)0°C $\leq$ TA $\leq$ +85°C (industrial)0°C $\leq$ TA $\leq$ +125°C (extended)                                                                                |

|--------------------------------|-------------------------------------------------------------------|---------------|-------------|--------------------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym           | Min         | Тур†                     | Max                | Units                | Conditions                                                                                                                                                                                                                        |

| D001                           | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0  | -                        | 6.0<br>6.0         | V<br>V               | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -           | 1.5                      | -                  | V                    |                                                                                                                                                                                                                                   |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -           | Vss                      | -                  | V                    | See section on Power-on Reset for details                                                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | Svdd          | 0.05        | -                        | -                  | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                         |

| D005                           | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7         | 4.0                      | 4.3                | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                |

| D010                           | Supply Current<br>(Note 2)                                        | IDD           | -           | 2.0                      | 3.8                | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                     |

| D010A                          |                                                                   |               | -           | 22.5                     | 48                 | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                   |

| D015                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -           | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9<br>0.9 | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |

| D023                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -           | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.