Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C71X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C710 | 512 x 14          | 36 x 8      |

| PIC16C71  | 1K x 14           | 36 x 8      |

| PIC16C711 | 1K x 14           | 68 x 8      |

| PIC16C715 | 2K x 14           | 128 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

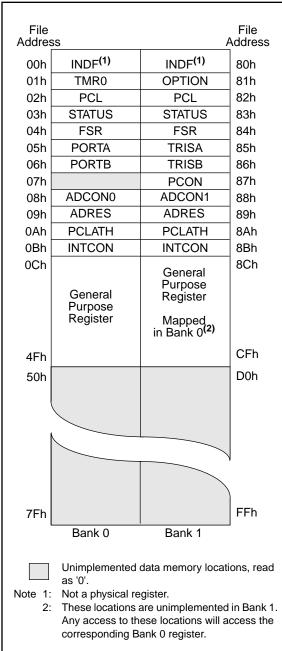

# 4.2 Data Memory Organization

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow \text{Bank } 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

|                                                                                                                                                                                                                                                                                                                         | 1117 \                         |                                                                      |                 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|-----------------|--|--|

| File<br>Addres                                                                                                                                                                                                                                                                                                          | s                              | ,                                                                    | File<br>Address |  |  |

| 00h                                                                                                                                                                                                                                                                                                                     | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>                                                  | 80h             |  |  |

| 01h                                                                                                                                                                                                                                                                                                                     | TMR0                           | OPTION                                                               | 81h             |  |  |

| 02h                                                                                                                                                                                                                                                                                                                     | PCL                            | PCL                                                                  | 82h             |  |  |

| 03h                                                                                                                                                                                                                                                                                                                     | STATUS                         | STATUS                                                               | 83h             |  |  |

| 04h                                                                                                                                                                                                                                                                                                                     | FSR                            | FSR                                                                  | 84h             |  |  |

| 05h                                                                                                                                                                                                                                                                                                                     | PORTA                          | TRISA                                                                | 85h             |  |  |

| 06h                                                                                                                                                                                                                                                                                                                     | PORTB                          | TRISB                                                                | 86h             |  |  |

| 07h                                                                                                                                                                                                                                                                                                                     |                                | PCON <sup>(2)</sup>                                                  | 87h             |  |  |

| 08h                                                                                                                                                                                                                                                                                                                     | ADCON0                         | ADCON1                                                               | 88h             |  |  |

| 09h                                                                                                                                                                                                                                                                                                                     | ADRES                          | ADRES                                                                | 89h             |  |  |

| 0Ah                                                                                                                                                                                                                                                                                                                     | PCLATH                         | PCLATH                                                               | 8Ah             |  |  |

| 0Bh                                                                                                                                                                                                                                                                                                                     | INTCON                         | INTCON                                                               | 8Bh             |  |  |

| 0Ch                                                                                                                                                                                                                                                                                                                     | General<br>Purpose<br>Register | General<br>Purpose<br>Register<br>Mapped<br>in Bank 0 <sup>(3)</sup> | 8Ch             |  |  |

| 2Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | AFh             |  |  |

| 30h                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | B0h             |  |  |

| 3011                                                                                                                                                                                                                                                                                                                    |                                |                                                                      |                 |  |  |

| l                                                                                                                                                                                                                                                                                                                       | <                              |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

| Ν                                                                                                                                                                                                                                                                                                                       |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      | )               |  |  |

| 7Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | FFh             |  |  |

| L                                                                                                                                                                                                                                                                                                                       | Bank 0                         | Bank 1                                                               | 1               |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>Note 1: Not a physical register.</li> <li>2: The PCON register is not implemented on the PIC16C71.</li> <li>3: These locations are unimplemented in Bank 1. Any access to these locations will access the corresponding Bank 0 register.</li> </ul> |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

# FIGURE 4-5: PIC16C711 REGISTER FILE MAP

# FIGURE 4-6: PIC16C715 REGISTER FILE MAP

| File<br>Address | 3                                                                                        |                                | File<br>Address |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------|--------------------------------|-----------------|--|--|--|--|--|

| 00h             | INDF <sup>(1)</sup>                                                                      | INDF <sup>(1)</sup>            | 80h             |  |  |  |  |  |

| 01h             | TMR0                                                                                     | OPTION                         | 81h             |  |  |  |  |  |

| 02h             | PCL                                                                                      | PCL                            | 82h             |  |  |  |  |  |

| 03h             | STATUS                                                                                   | STATUS                         | 83h             |  |  |  |  |  |

| 04h             | FSR                                                                                      | FSR                            |                 |  |  |  |  |  |

| 05h             | PORTA                                                                                    | TRISA                          |                 |  |  |  |  |  |

| 06h             | PORTB                                                                                    | TRISB                          |                 |  |  |  |  |  |

| 07h             |                                                                                          |                                | 87h             |  |  |  |  |  |

| 08h             |                                                                                          |                                |                 |  |  |  |  |  |

| 09h             |                                                                                          |                                |                 |  |  |  |  |  |

| 0Ah             | PCLATH                                                                                   | PCLATH                         | 8Ah             |  |  |  |  |  |

| 0Bh             | INTCON                                                                                   | INTCON                         | 8Bh             |  |  |  |  |  |

| 0Ch             | PIR1                                                                                     | PIE1                           | 8Ch             |  |  |  |  |  |

| 0Dh             |                                                                                          |                                | 8Dh             |  |  |  |  |  |

| 0Eh             |                                                                                          | PCON                           | 8Eh             |  |  |  |  |  |

| 0Fh             |                                                                                          |                                | 8Fh             |  |  |  |  |  |

| 10h             |                                                                                          |                                | 90h             |  |  |  |  |  |

| 11h             |                                                                                          |                                | 91h             |  |  |  |  |  |

| 12h             |                                                                                          |                                |                 |  |  |  |  |  |

| 13h             |                                                                                          |                                | 93h             |  |  |  |  |  |

| 14h             |                                                                                          |                                | 94h             |  |  |  |  |  |

| 15h             |                                                                                          |                                | 95h             |  |  |  |  |  |

| 16h             |                                                                                          |                                | 96h             |  |  |  |  |  |

| 17h             |                                                                                          |                                |                 |  |  |  |  |  |

| 18h             |                                                                                          |                                | 98h             |  |  |  |  |  |

| 19h             |                                                                                          |                                | 99h             |  |  |  |  |  |

| 1Ah             |                                                                                          |                                | 9Ah             |  |  |  |  |  |

| 1Bh             |                                                                                          |                                | 9Bh             |  |  |  |  |  |

| 1Ch             |                                                                                          |                                | 9Ch             |  |  |  |  |  |

| 1Dh             |                                                                                          |                                | 9Dh             |  |  |  |  |  |

| 1Eh             | ADRES                                                                                    |                                | 9Eh             |  |  |  |  |  |

| 1Fh             | ADCON0                                                                                   | ADCON1                         | 9Fh             |  |  |  |  |  |

| 20h             | General<br>Purpose<br>Register                                                           | General<br>Purpose<br>Register | A0h             |  |  |  |  |  |

|                 | rtogiotor                                                                                |                                | BFh             |  |  |  |  |  |

|                 |                                                                                          |                                | C0h             |  |  |  |  |  |

|                 |                                                                                          |                                |                 |  |  |  |  |  |

| l               |                                                                                          |                                |                 |  |  |  |  |  |

|                 |                                                                                          |                                |                 |  |  |  |  |  |

| 7Fh             | Deels                                                                                    | Denk 1                         | _ FFh           |  |  |  |  |  |

|                 | Bank 0 Bank 1                                                                            |                                |                 |  |  |  |  |  |

| e a             | Unimplemented data memory locations, read<br>as '0'.<br>Note 1: Not a physical register. |                                |                 |  |  |  |  |  |

|                 |                                                                                          |                                |                 |  |  |  |  |  |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name                                                                                                | Bit 7                                 | Bit 6              | Bit 5         | Bit 4                                                    | Bit 3         | Bit 2            | Bit 1       | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(1) |

|----------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|---------------|----------------------------------------------------------|---------------|------------------|-------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |                                                                                                     |                                       |                    |               | •                                                        | •             |                  |             |           |                          |                                     |

| 00h <sup>(3)</sup>   | INDF Addressing this location uses contents of FSR to address data memory (not a physical register) |                                       |                    |               |                                                          |               |                  |             | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0                                                                                                | Timer0 mod                            | lule's register    | r             |                                                          |               |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(3)</sup>   | PCL                                                                                                 | Program Co                            | ounter's (PC)      | Least Signif  | icant Byte                                               |               |                  |             |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(3)</sup>   | STATUS                                                                                              | IRP <sup>(5)</sup>                    | RP1 <sup>(5)</sup> | RP0           | TO                                                       | PD            | Z                | DC          | с         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(3)</sup>   | FSR                                                                                                 | Indirect data                         | a memory ad        | dress pointe  | r                                                        |               |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA                                                                                               | —                                     | —                  | —             | PORTA Dat                                                | a Latch whe   | n written: PO    | RTA pins wh | en read   | x 0000                   | u 0000                              |

| 06h                  | PORTB                                                                                               | PORTB Dat                             | a Latch whe        | n written: PC | DRTB pins wł                                             | nen read      |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | —                                                                                                   | Unimpleme                             | nted               |               |                                                          |               |                  |             |           | —                        | —                                   |

| 08h                  | ADCON0                                                                                              | ADCS1                                 | ADCS0              | (6)           | CHS1                                                     | CHS0          | GO/DONE          | ADIF        | ADON      | 00-0 0000                | 00-0 0000                           |

| 09h <sup>(3)</sup>   | ADRES                                                                                               | RES A/D Result Register               |                    |               |                                                          |               |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 0Ah <sup>(2,3)</sup> | PCLATH                                                                                              | _                                     | —                  | _             | Write Buffer for the upper 5 bits of the Program Counter |               |                  |             |           | 0 0000                   | 0 0000                              |

| 0Bh <b>(3)</b>       | INTCON                                                                                              | GIE                                   | ADIE               | TOIE          | INTE                                                     | RBIE          | TOIF             | INTF        | RBIF      | 0000 000x                | 0000 000u                           |

| Bank 1               |                                                                                                     |                                       |                    |               |                                                          |               |                  |             |           |                          |                                     |

| 80h <sup>(3)</sup>   | INDF Addressing this location uses contents of FSR to address data memory (not a physical register) |                                       |                    |               |                                                          |               |                  | register)   | 0000 0000 | 0000 0000                |                                     |

| 81h                  | OPTION                                                                                              | RBPU                                  | INTEDG             | TOCS          | TOSE                                                     | PSA           | PS2              | PS1         | PS0       | 1111 1111                | 1111 1111                           |

| 82h <sup>(3)</sup>   | PCL                                                                                                 | Program Co                            | ounter's (PC)      | Least Signif  | icant Byte                                               |               |                  |             |           | 0000 0000                | 0000 0000                           |

| 83h <sup>(3)</sup>   | STATUS                                                                                              | IRP <sup>(5)</sup>                    | RP1 <sup>(5)</sup> | RP0           | TO                                                       | PD            | z                | DC          | с         | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(3)</sup>   | FSR                                                                                                 | Indirect data                         | a memory ad        | dress pointe  | er                                                       |               |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA                                                                                               | —                                     | —                  | —             | PORTA Dat                                                | a Direction F | Register         |             |           | 1 1111                   | 1 1111                              |

| 86h                  | TRISB                                                                                               | PORTB Data Direction Control Register |                    |               |                                                          |               |                  |             |           | 1111 1111                | 1111 1111                           |

| 87h <sup>(4)</sup>   | PCON                                                                                                | —                                     | —                  | —             | _                                                        | —             | _                | POR         | BOR       | dd                       | uu                                  |

| 88h                  | ADCON1                                                                                              | —                                     | —                  | _             | _                                                        | _             | —                | PCFG1       | PCFG0     | 00                       | 00                                  |

| 89h <sup>(3)</sup>   | ADRES                                                                                               | RES A/D Result Register               |                    |               |                                                          |               |                  |             |           | xxxx xxxx                | uuuu uuuu                           |

| 8Ah <sup>(2,3)</sup> | PCLATH                                                                                              | _                                     | —                  | —             | Write Buffer                                             | for the uppe  | er 5 bits of the | e Program C | ounter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(3)</sup>   | INTCON                                                                                              | GIE                                   | ADIE               | TOIE          | INTE                                                     | RBIE          | TOIF             | INTF        | RBIF      | 0000 000x                | 0000 000u                           |

# TABLE 4-1: PIC16C710/71/711 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: These registers can be addressed from either bank.

4: The PCON register is not physically implemented in the PIC16C71, read as '0'.

5: The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear.

6: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

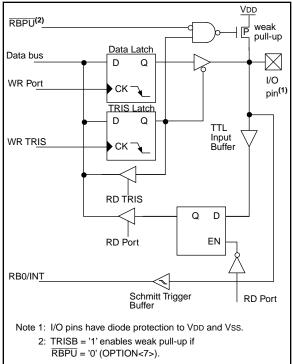

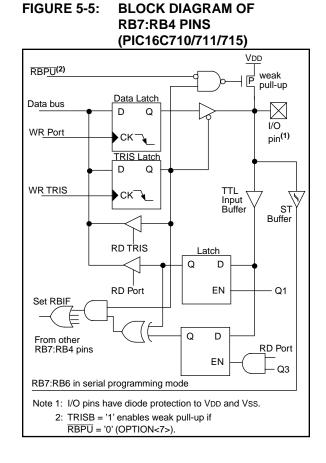

# 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

# EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, RPC | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPC | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

# FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

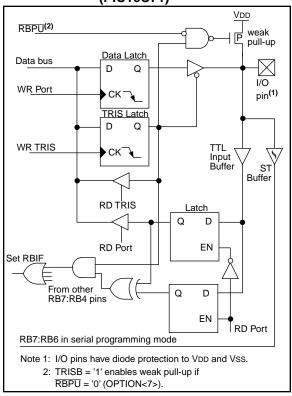

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

| Note: | For the PIC16C71                                 |

|-------|--------------------------------------------------|

|       | if a change on the I/O pin should occur          |

|       | when the read operation is being executed        |

|       | (start of the Q2 cycle), then interrupt flag bit |

|       | RBIF may not get set.                            |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

# FIGURE 5-4: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C71)

# TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

| Address   | Name   | Bit 7                         | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------------------------------|--------|-------|-------|-------|-----------|-----------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7                           | RB6    | RB5   | RB4   | RB3   | RB2       | RB1       | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB Data Direction Register |        |       |       |       | 1111 1111 | 1111 1111 |       |                          |                           |

| 81h, 181h | OPTION | RBPU                          | INTEDG | TOCS  | TOSE  | PSA   | PS2       | PS1       | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 8.4.5 TIME-OUT SEQUENCE

# Applicable Devices 710 71 711 715

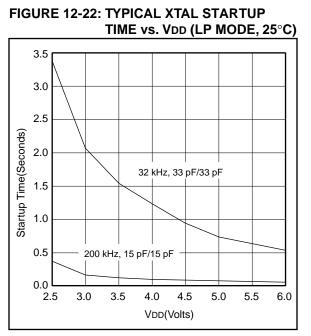

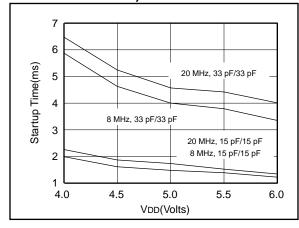

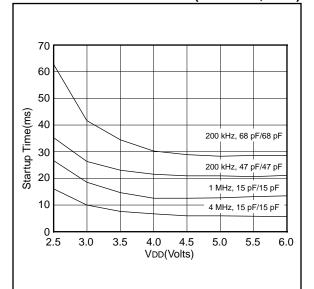

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

#### 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

# Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

#### 8.4.7 PARITY ERROR RESET (PER)

#### Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

#### TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

#### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power-up         |           | Brown out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

# 9.1 Instruction Descriptions

|                   |                                                                | •                                                                                                                       | _            |         |  |  |  |  |  |

|-------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------|---------|--|--|--|--|--|

| ADDLW             | Add Lite                                                       | ral and \                                                                                                               | N            |         |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] ADDLW k                                       |                                                                                                                         |              |         |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                              |                                                                                                                         |              |         |  |  |  |  |  |

| Operation:        | $(W) + k \to (W)$                                              |                                                                                                                         |              |         |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                       |                                                                                                                         |              |         |  |  |  |  |  |

| Encoding:         | 11                                                             | 111x                                                                                                                    | kkkk         | kkkk    |  |  |  |  |  |

| Description:      | added to th                                                    | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |              |         |  |  |  |  |  |

| Words:            | 1                                                              |                                                                                                                         |              |         |  |  |  |  |  |

| Cycles:           | 1                                                              |                                                                                                                         |              |         |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                             | Q2                                                                                                                      | Q3           | Q4      |  |  |  |  |  |

|                   | Decode Read Process W<br>literal 'k' data                      |                                                                                                                         |              |         |  |  |  |  |  |

| Example:          | After Inst                                                     | W =                                                                                                                     | 0x10<br>0x25 |         |  |  |  |  |  |

| ADDWF             | Add W a                                                        | nd f                                                                                                                    |              |         |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] Al                                            | DDWF                                                                                                                    | f,d          |         |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                                                                                                                       |              |         |  |  |  |  |  |

| Operation:        | (W) + (f) -                                                    | ightarrow (dest)                                                                                                        |              |         |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                       |                                                                                                                         |              |         |  |  |  |  |  |

| Encoding:         | 00                                                             | 0111                                                                                                                    | dfff         | ffff    |  |  |  |  |  |

| Description:      | Add the co<br>with regist<br>stored in th                      | er 'f'. If 'd'                                                                                                          | is 0 the re  | sult is |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff             |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|------------------|--|--|--|--|--|--|--|

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                         |                 |                  |  |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                  |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                  |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4               |  |  |  |  |  |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to<br>Dest |  |  |  |  |  |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                  |  |  |  |  |  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                  |  |  |  |  |  |  |  |

|                   | W = 0x17<br>FSR = 0xC2                                                                                                                                                    |                         |                 |                  |  |  |  |  |  |  |  |

|                   | After Inst                                                                                                                                                                |                         | 0               |                  |  |  |  |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                  |  |  |  |  |  |  |  |

| ANDLW             | AND Lite                           | eral with              | w               |               |  |  |  |  |  |  |

|-------------------|------------------------------------|------------------------|-----------------|---------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] ANDLW k           |                        |                 |               |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                  |                        |                 |               |  |  |  |  |  |  |

| Operation:        | (W) .ANE                           | D. (k) $\rightarrow$ ( | W)              |               |  |  |  |  |  |  |

| Status Affected:  | Z                                  |                        |                 |               |  |  |  |  |  |  |

| Encoding:         | 11                                 | 1001                   | kkkk            | kkkk          |  |  |  |  |  |  |

| Description:      | The conte<br>AND'ed wiresult is pl | ith the eig            | ht bit litera   | 'k'.The       |  |  |  |  |  |  |

| Words:            | 1                                  |                        |                 |               |  |  |  |  |  |  |

| Cycles:           | 1                                  |                        |                 |               |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                 | Q2                     | Q3              | Q4            |  |  |  |  |  |  |

|                   | Decode                             | Read<br>literal "k"    | Process<br>data | Write to<br>W |  |  |  |  |  |  |

| Example           | ANDLW                              | 0x5F                   |                 |               |  |  |  |  |  |  |

|                   | Before In                          | struction              | 0xA3            |               |  |  |  |  |  |  |

|                   | After Instruction                  |                        |                 |               |  |  |  |  |  |  |

|                   |                                    | = W                    | 0x03            |               |  |  |  |  |  |  |

|                   |                                    |                        |                 |               |  |  |  |  |  |  |

| ANDWF             | AND W v                                                                                     | vith f                   |                                              |                  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------|------------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                          | NDWF                     | f,d                                          |                  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[ 0,1 \right] \end{array}$                |                          |                                              |                  |  |  |  |  |  |

| Operation:        | (W) .ANE                                                                                    | D. (f) $\rightarrow$ (c  | dest)                                        |                  |  |  |  |  |  |

| Status Affected:  | Z                                                                                           |                          |                                              |                  |  |  |  |  |  |

| Encoding:         | 00                                                                                          | 0101                     | dfff                                         | ffff             |  |  |  |  |  |

| Description:      | 'd' is 0 the                                                                                | result is a 'd' is 1 the | with regist<br>stored in th<br>e result is s | ie W             |  |  |  |  |  |

| Words:            | 1                                                                                           |                          |                                              |                  |  |  |  |  |  |

| Cycles:           | 1                                                                                           |                          |                                              |                  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                          | Q2                       | Q3                                           | Q4               |  |  |  |  |  |

|                   | Decode                                                                                      | Read<br>register<br>'f'  | Process<br>data                              | Write to<br>Dest |  |  |  |  |  |

| Example           | ANDWF                                                                                       | FSR,                     | 1                                            |                  |  |  |  |  |  |

|                   | Before In                                                                                   |                          |                                              |                  |  |  |  |  |  |

|                   | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02 |                          |                                              |                  |  |  |  |  |  |

| BTFSS             | Bit Test f                 | f, Skip if S                                            | Set                       |         | CALL              | Call Sub                              | oroutine                             |                                                        |                                             |  |  |

|-------------------|----------------------------|---------------------------------------------------------|---------------------------|---------|-------------------|---------------------------------------|--------------------------------------|--------------------------------------------------------|---------------------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] B1        | FSS f,b                                                 |                           |         | Syntax:           | [ label ]                             | [ <i>label</i> ] CALL k              |                                                        |                                             |  |  |

| Operands:         | $0 \le f \le 12$           |                                                         |                           |         | Operands:         | $0 \le k \le 2047$                    |                                      |                                                        |                                             |  |  |

|                   | 0 ≤ b < 7                  |                                                         |                           |         | Operation:        | (PC)+ 1 $\rightarrow$ TOS,            |                                      |                                                        |                                             |  |  |

| Operation:        | skip if (f<                | ip if (f <b>) = 1</b>                                   |                           |         |                   | $k \rightarrow PC <$                  |                                      | 50.40                                                  |                                             |  |  |

| Status Affected:  | None                       | i                                                       |                           |         |                   | ,                                     | 1<4:3>) -                            | $\rightarrow$ PC<12                                    | :11>                                        |  |  |

| Encoding:         | 01                         | 11bb                                                    | bfff                      | ffff    | Status Affected:  | None                                  |                                      |                                                        |                                             |  |  |

| Description:      |                            | register 'f' is                                         |                           | ne next | Encoding:         | 10                                    | 0kkk                                 | kkkk                                                   | kkkk                                        |  |  |

|                   | If bit 'b' is<br>discarded | is execute<br>1', then the<br>and a NOF<br>aking this a | next instru<br>is execute | ed      | Description:      | (PC+1) is<br>eleven bit<br>into PC bi | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the sta<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |  |  |

| Words:            | 1                          |                                                         |                           |         |                   |                                       |                                      | rom PCLA<br>instruction                                |                                             |  |  |

| Cycles:           | 1(2)                       |                                                         |                           |         | Words:            | 1                                     |                                      |                                                        |                                             |  |  |

| Q Cycle Activity: | Q1                         | Q2                                                      | Q3                        | Q4      | Cycles:           | 2                                     |                                      |                                                        |                                             |  |  |

|                   | Decode                     | Read<br>register 'f'                                    | Process<br>data           | NOP     | Q Cycle Activity: | Q1                                    | Q2                                   | Q3                                                     | Q4                                          |  |  |

| If Skip:          | (2nd Cyc                   | :le)                                                    |                           |         | 1st Cycle         | Decode                                | Read<br>literal 'k',                 | Process<br>data                                        | Write to<br>PC                              |  |  |

|                   | Q1                         | Q2                                                      | Q3                        | Q4      | 1                 |                                       | Push PC<br>to Stack                  |                                                        |                                             |  |  |

|                   | NOP                        | NOP                                                     | NOP                       | NOP     | 2nd Cycle         | NOP                                   | NOP                                  | NOP                                                    | NOP                                         |  |  |

| Example           | HERE<br>FALSE              |                                                         | FLAG,1<br>PROCESS_        | _CODE   | Example           | HERE                                  | CALL                                 | THERE                                                  |                                             |  |  |

|                   | TRUE                       | •                                                       |                           |         |                   | Before Ir                             |                                      |                                                        |                                             |  |  |

|                   |                            | •                                                       |                           |         |                   | After Ins                             |                                      | Address HE                                             | RE                                          |  |  |

|                   | Before In                  | struction                                               |                           |         |                   |                                       | -                                    | ddress TH                                              |                                             |  |  |

|                   |                            |                                                         | address H                 | IERE    |                   |                                       | TOS = A                              | Address HE                                             | RE+1                                        |  |  |

|                   | After Inst                 | ruction<br>if FLAG<1>                                   | - 0                       |         |                   |                                       |                                      |                                                        |                                             |  |  |

|                   |                            | -                                                       | > = 0,<br>address F≠      | ALSE    |                   |                                       |                                      |                                                        |                                             |  |  |

|                   |                            | if FLAG<1><br>PC =                                      | ,                         |         |                   |                                       |                                      |                                                        |                                             |  |  |

|                   |                            | FU = 1                                                  | address TF                | KUE     |                   |                                       |                                      |                                                        |                                             |  |  |

# PIC16C71X

| Applica | ble Devices 710 71 711 715                      |                                                |                                                          |                                                    |                                                                            |                                                                      |                                                             |

|---------|-------------------------------------------------|------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|

| 11.3    |                                                 | 1-04<br>0-10<br>1-10<br>0-20<br>1-20<br>'10-04 | (Comme<br>(Comme<br>(Comme<br>(Comme<br>(Comme<br>(Comme | ercia<br>ercia<br>ercia<br>ercia<br>ercia<br>ercia | II, Indus<br>II, Indus<br>II, Indus<br>II, Indus<br>II, Indus<br>II, Indus | trial, E<br>trial, E<br>trial, E<br>trial, E<br>trial, E<br>trial, E | Extended)<br>Extended)<br>Extended)<br>Extended)            |

|         |                                                 |                                                |                                                          |                                                    |                                                                            |                                                                      | less otherwise stated)                                      |

|         |                                                 | Operati                                        | ng tempe                                                 | ratur                                              |                                                                            |                                                                      | $A \le +70^{\circ}C$ (commercial)                           |

| DC CHA  | RACTERISTICS                                    |                                                |                                                          |                                                    | -40°C<br>-40°C                                                             |                                                                      | A ≤ +85°C (industrial)<br>A ≤ +125°C (extended)             |

|         |                                                 | Operati                                        | na voltaa                                                | e Vdi                                              |                                                                            |                                                                      | ribed in DC spec Section 11.1 and                           |

|         |                                                 | Section                                        |                                                          |                                                    | <b>J</b>                                                                   |                                                                      |                                                             |

| Param   | Characteristic                                  | Sym                                            | Min                                                      | Тур                                                | Max                                                                        | Units                                                                | Conditions                                                  |