Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

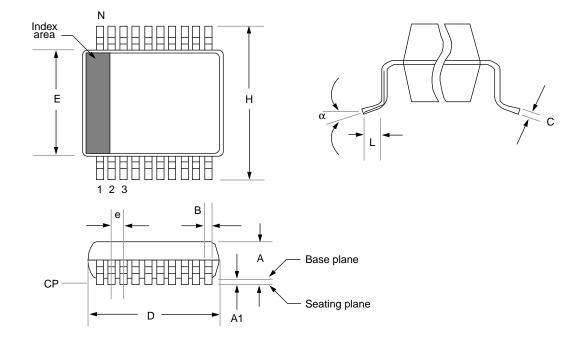

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

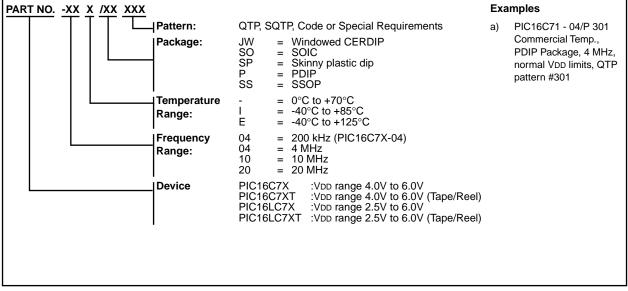

## 2.0 PIC16C71X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C71X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C71X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**71. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC71. These devices have EPROM type memory and operate over an extended voltage range.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C71X.

## 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

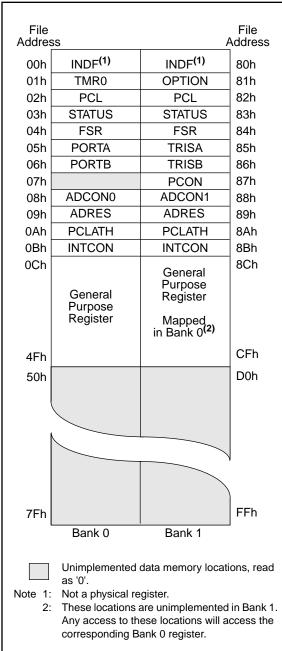

## FIGURE 4-5: PIC16C711 REGISTER FILE MAP

## FIGURE 4-6: PIC16C715 REGISTER FILE MAP

| File<br>Address | 3                                                    |                                | File<br>Address |

|-----------------|------------------------------------------------------|--------------------------------|-----------------|

| 00h             | INDF <sup>(1)</sup>                                  | INDF <sup>(1)</sup>            | 80h             |

| 01h             | TMR0                                                 | OPTION                         | 81h             |

| 02h             | PCL                                                  | PCL                            | 82h             |

| 03h             | STATUS                                               | STATUS                         | 83h             |

| 04h             | FSR                                                  | FSR                            |                 |

| 05h             | PORTA                                                | TRISA                          |                 |

| 06h             | PORTB                                                | TRISB                          |                 |

| 07h             |                                                      |                                | 87h             |

| 08h             |                                                      |                                |                 |

| 09h             |                                                      |                                |                 |

| 0Ah             | PCLATH                                               | PCLATH                         | 8Ah             |

| 0Bh             | INTCON                                               | INTCON                         | 8Bh             |

| 0Ch             | PIR1                                                 | PIE1                           | 8Ch             |

| 0Dh             |                                                      |                                | 8Dh             |

| 0Eh             |                                                      | PCON                           | 8Eh             |

| 0Fh             |                                                      |                                | 8Fh             |

| 10h             |                                                      |                                | 90h             |

| 11h             |                                                      |                                | 91h             |

| 12h             |                                                      |                                |                 |

| 13h             |                                                      |                                | 93h             |

| 14h             |                                                      |                                | 94h             |

| 15h             |                                                      |                                | 95h             |

| 16h             |                                                      |                                | 96h             |

| 17h             |                                                      |                                |                 |

| 18h             |                                                      |                                | 98h             |

| 19h             |                                                      |                                | 99h             |

| 1Ah             |                                                      |                                | 9Ah             |

| 1Bh             |                                                      |                                | 9Bh             |

| 1Ch             |                                                      |                                | 9Ch             |

| 1Dh             |                                                      |                                | 9Dh             |

| 1Eh             | ADRES                                                |                                | 9Eh             |

| 1Fh             | ADCON0                                               | ADCON1                         | 9Fh             |

| 20h             | General<br>Purpose<br>Register                       | General<br>Purpose<br>Register | A0h             |

|                 | rtogiotor                                            |                                | BFh             |

|                 |                                                      |                                | C0h             |

|                 |                                                      |                                |                 |

| l               |                                                      |                                |                 |

|                 |                                                      |                                |                 |

| 7Fh             | Deels                                                | Bank 1                         | _ FFh           |

|                 | Bank 0                                               | Bank 1                         |                 |

| e a             | Jnimplemented dat<br>as '0'.<br>Not a physical regis | -                              | ns, read        |

|                 |                                                      |                                |                 |

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

## TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

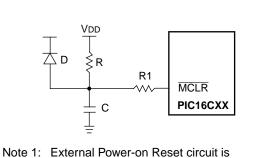

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

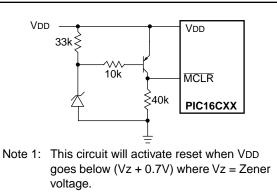

## FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

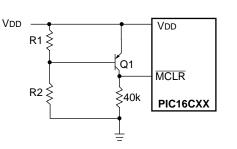

- 3: Resistors should be adjusted for the characteristics of the transistor.

## FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

## 8.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

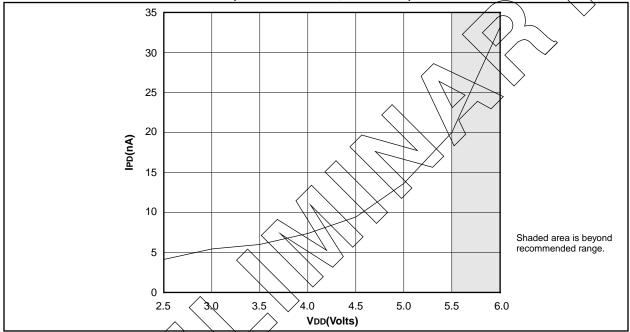

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 8.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. A/D conversion (when A/D clock source is RC).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the subset (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 8.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

NOTES:

## PIC16C71X

| IORWF             | Inclusive                                                                 | e OR W v                    | with f                      |                  |  |

|-------------------|---------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------|--|

| Syntax:           | [ label ]                                                                 | IORWF                       | f,d                         |                  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$ | 27                          |                             |                  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ (dest)                                         |                             |                             |                  |  |

| Status Affected:  | Z                                                                         | Z                           |                             |                  |  |

| Encoding:         | 00                                                                        | 0100                        | dfff                        | ffff             |  |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>the W regi<br>placed bac                | is 0 the re<br>ster. If 'd' | esult is pla<br>is 1 the re | ced in           |  |

| Words:            | 1                                                                         |                             |                             |                  |  |

| Cycles:           | 1                                                                         |                             |                             |                  |  |

| Q Cycle Activity: | Q1                                                                        | Q2                          | Q3                          | Q4               |  |

|                   | Decode                                                                    | Read<br>register<br>'f'     | Process<br>data             | Write to<br>dest |  |

| Example           | IORWF                                                                     |                             | RESULT,                     | 0                |  |

|                   |                                                                           | struction<br>RESULT<br>W    |                             | -                |  |

|                   | After Inst                                                                |                             |                             | 3                |  |

| MOVLW             | Move Lite                           | eral to V           | v               |               |

|-------------------|-------------------------------------|---------------------|-----------------|---------------|

| Syntax:           | [ label ]                           | MOVLW               | / k             |               |

| Operands:         | $0 \le k \le 25$                    | 55                  |                 |               |

| Operation:        | $k \to (W)$                         |                     |                 |               |

| Status Affected:  | None                                |                     |                 |               |

| Encoding:         | 11                                  | 00xx                | kkkk            | kkkk          |

| Description:      | The eight the register. The as 0's. |                     |                 |               |

| Words:            | 1                                   |                     |                 |               |

| Cycles:           | 1                                   |                     |                 |               |

| Q Cycle Activity: | Q1                                  | Q2                  | Q3              | Q4            |

|                   | Decode                              | Read<br>literal 'k' | Process<br>data | Write to<br>W |

| Example           | MOVLW                               | 0x5A                |                 |               |

|                   | After Inst                          | ruction<br>W =      | 0x5A            |               |

| Move f                                                                    |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [label] MOVF f,d                                                          |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$ | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| (f) $\rightarrow$ (des                                                    | st)                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Z                                                                         |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00 1000 dfff ffff                                                         |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| a destinati<br>tus of d. lf<br>ister. lf d =<br>register f it             | on depen<br>d = 0, des<br>1, the de<br>self. d = 1                                                                                                                                                                                                                                            | dant upon<br>stination is<br>stination is<br>is useful t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | the sta-<br>W reg-<br>s file<br>to test a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1                                                                         |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                         |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                        | Q2                                                                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                    | Read<br>register<br>'f'                                                                                                                                                                                                                                                                       | Process<br>data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Write to<br>dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1                                                                         | ruction<br>W = valu                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | egister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                           | $\begin{bmatrix}  abel  \\ 0 \le f \le 12 \\ d \in [0,1] \\ (f) \to (des Z \\ \hline 00 \\ \hline Decode \\ a destinati \\ tus of d. If \\ ister. If d = \\ register f it \\ file registe \\ affected. \\ 1 \\ 1 \\ \hline Q1 \\ \hline Decode \\ \hline MOVF \\ After Inst \\ \end{bmatrix}$ | $\begin{bmatrix} label \\ \end{bmatrix} MOVF$ $0 \le f \le 127$ $d \in [0,1]$ $(f) \rightarrow (dest)$ $Z$ $\boxed{00} 1000$ The contents of reg<br>a destination depention tus of d. If d = 0, destination depentions of the second state o | $\begin{bmatrix} label \end{bmatrix} \text{ MOVF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (f) \rightarrow (dest) \\ Z \\ \hline 00 & 1000 & dfff \\ \hline The contents of register f is m a destination dependant upon tus of d. If d = 0, destination is ister. If d = 1, the destination is register f itself. d = 1 is useful to file register since status flag Z affected. 1 \\ 1 \\ Q1 & Q2 & Q3 \\ \hline Decode & Read & Process \\ data \\ \hline MOVF & FSR, 0 \\ \hline After Instruction \\ W = value in FSR register \\ \end{bmatrix}$ |  |

| MOVWF             | Move W                | to f                    |                  |                       |

|-------------------|-----------------------|-------------------------|------------------|-----------------------|

| Syntax:           | [ label ]             | MOVW                    | = f              |                       |

| Operands:         | $0 \le f \le 12$      | 27                      |                  |                       |

| Operation:        | $(W) \rightarrow (f)$ |                         |                  |                       |

| Status Affected:  | None                  |                         |                  |                       |

| Encoding:         | 00                    | 0000                    | lfff             | ffff                  |

| Description:      | Move data<br>'f'.     | from W r                | egister to       | register              |

| Words:            | 1                     |                         |                  |                       |

| Cycles:           | 1                     |                         |                  |                       |

| Q Cycle Activity: | Q1                    | Q2                      | Q3               | Q4                    |

|                   | Decode                | Read<br>register<br>'f' | Process<br>data  | Write<br>register 'f' |

| Example           | MOVWF                 | OPTIC                   | N_REG            |                       |

|                   | Before In             |                         |                  | _                     |

|                   |                       | OPTION<br>W             | = 0xFF<br>= 0x4F |                       |

|                   | After Inst            | ••                      | - 0741           |                       |

|                   |                       | OPTION                  |                  |                       |

|                   |                       | W                       | = 0x4F           | -                     |

| NOP               | No Oper   | ation |      |      |

|-------------------|-----------|-------|------|------|

| Syntax:           | [ label ] | NOP   |      |      |

| Operands:         | None      |       |      |      |

| Operation:        | No opera  | ition |      |      |

| Status Affected:  | None      |       |      |      |

| Encoding:         | 00        | 0000  | 0xx0 | 0000 |

| Description:      | No operat | ion.  |      |      |

| Words:            | 1         |       |      |      |

| Cycles:           | 1         |       |      |      |

| Q Cycle Activity: | Q1        | Q2    | Q3   | Q4   |

|                   | Decode    | NOP   | NOP  | NOP  |

| Example           | NOP       |       |      |      |

| RETFIE            | Return fi                                                          | rom Inte                              | rrupt                   |                     |

|-------------------|--------------------------------------------------------------------|---------------------------------------|-------------------------|---------------------|

| Syntax:           | [ label ]                                                          | RETFIE                                |                         |                     |

| Operands:         | None                                                               |                                       |                         |                     |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$              | PC,                                   |                         |                     |

| Status Affected:  | None                                                               |                                       |                         |                     |

| Encoding:         | 00                                                                 | 0000                                  | 0000                    | 1001                |

| Monda             | and Top of<br>the PC. Int<br>ting Globa<br>(INTCON-<br>instruction | errupts a<br>I Interrupt<br>7>). This | re enabled<br>Enable bi | l by set-<br>t, GIE |

| Words:            | 1                                                                  |                                       |                         |                     |

| Cycles:           | 2                                                                  |                                       |                         |                     |

| Q Cycle Activity: | Q1                                                                 | Q2                                    | Q3                      | Q4                  |

| 1st Cycle         | Decode                                                             | NOP                                   | Set the<br>GIE bit      | Pop from the Stack  |

| 2nd Cycle         | NOP                                                                | NOP                                   | NOP                     | NOP                 |

| Example           | RETFIE                                                             |                                       |                         |                     |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                           | tion Reg                                       | gister                                               |                                         |  |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|--|

| Syntax:          | [ label ]                                                                                          | OPTION                                         | ٧                                                    |                                         |  |

| Operands:        | None                                                                                               |                                                |                                                      |                                         |  |

| Operation:       | $(W)\toOF$                                                                                         | PTION                                          |                                                      |                                         |  |

| Status Affected: | None                                                                                               |                                                |                                                      |                                         |  |

| Encoding:        | 00 0000 0110 0010                                                                                  |                                                |                                                      |                                         |  |

| Description:     | The conter<br>loaded in the<br>instruction<br>patibility with<br>Since OPT<br>register, the<br>it. | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |  |

| Words:           | 1                                                                                                  |                                                |                                                      |                                         |  |

| Cycles:          | 1                                                                                                  |                                                |                                                      |                                         |  |

| Example          |                                                                                                    |                                                |                                                      |                                         |  |

|                  | To mainta<br>with futur<br>not use th                                                              | re PIC16                                       | CXX prod                                             |                                         |  |

# PIC16C71X

## SLEEP

| [ label ]                                                       | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| None                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | ,                                                                                                                                                                                                                                                 | ller,                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                        |

| TO, PD                                                          |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |