Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715-20-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

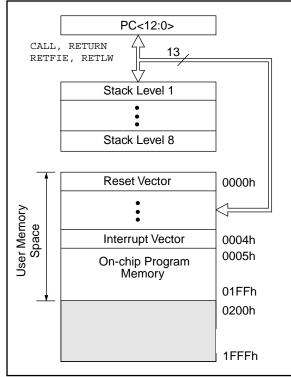

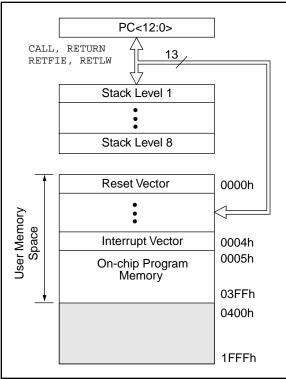

## 4.0 MEMORY ORGANIZATION

#### 4.1 Program Memory Organization

The PIC16C71X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C710 | 512 x 14          | 0000h-01FFh   |

| PIC16C71  | 1K x 14           | 0000h-03FFh   |

| PIC16C711 | 1K x 14           | 0000h-03FFh   |

| PIC16C715 | 2K x 14           | 0000h-07FFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC16C710 PROGRAM MEMORY MAP AND STACK

### FIGURE 4-2: PIC16C71/711 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-3: PIC16C715 PROGRAM MEMORY MAP AND STACK

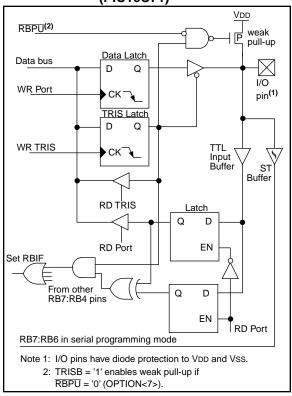

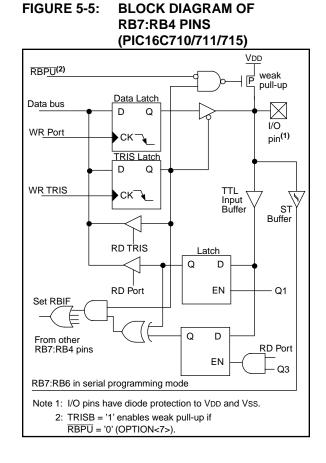

#### FIGURE 5-4: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C71)

#### TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

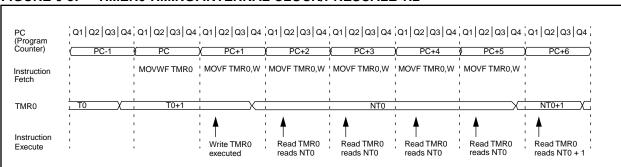

### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

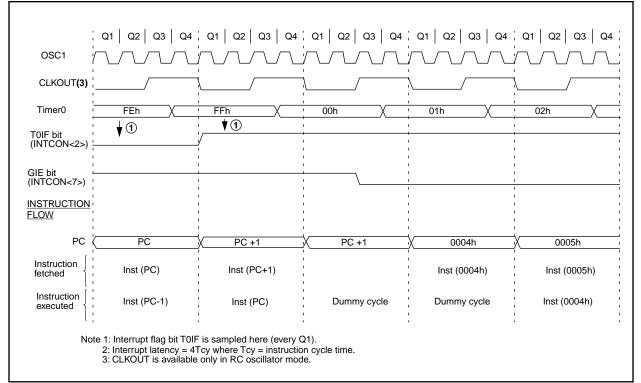

### FIGURE 6-4: TIMER0 INTERRUPT TIMING

#### FIGURE 8-2: CONFIGURATION WORD, PIC16C710/711

| CP0 C                      | P0 CI                                      | P0 CP0                                                                           | CP0                                   | CP0     | CP0     | BODEN | CP0     | CP0      | PWRTE    | WDTE   | FOSC1 | FOSC0 | Register:      | CONFIG |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------|---------|-------|---------|----------|----------|--------|-------|-------|----------------|--------|

| bit13                      |                                            | 1                                                                                |                                       |         |         |       |         |          |          |        |       | bit0  | Address        | 2007h  |

| bit 13-7<br>5-4:<br>bit 6: | 1 = Co<br>0 = All<br><b>BODE</b><br>1 = BC | Code prote<br>ode protec<br>memory<br><b>N:</b> Brown<br>OR enable<br>OR disable | ction off<br>is code<br>-out Re<br>ed | protec  |         |       | Fh is w | vritable |          |        |       |       |                |        |

| bit 3:                     | 1 = PV                                     | <b>Ē:</b> Power<br>VRT disal<br>VRT enat                                         | bled                                  | er Ena  | ble bit | (1)   |         |          |          |        |       |       |                |        |

| bit 2:                     | 1 = W                                      | : Watchd<br>DT enable<br>DT disabl                                               | ed                                    | er Enab | le bit  |       |         |          |          |        |       |       |                |        |

| bit 1-0:                   | 11 = F<br>10 = F<br>01 = X                 | 1:FOSC0<br>RC oscilla<br>IS oscillat<br>(T oscillat<br>P oscillat                | tor<br>tor<br>tor                     | ator Se | lection | bits  |         |          |          |        |       |       |                |        |

| Note 1:                    | Ensur                                      | e the Pow                                                                        | er-up T                               | imer is | enable  |       | ne Brov | vn-out l | Reset is | enable | d.    |       | value of bit F | PWRTE. |

#### 2: All of the CP0 bits have to be given the same value to enable the code protection scheme listed.

#### FIGURE 8-3: CONFIGURATION WORD, PIC16C715

| CP1             | CP0               | CP1                                           | CP0                           | CP1                           | CP0                    | MPEEN                               | BODEN                  | CP1    | CP0   | PWRTE     | WDTE     | FOSC1    | FOSC0      | Register:    | CONFIG |

|-----------------|-------------------|-----------------------------------------------|-------------------------------|-------------------------------|------------------------|-------------------------------------|------------------------|--------|-------|-----------|----------|----------|------------|--------------|--------|

| bit13           |                   |                                               |                               |                               |                        |                                     |                        |        |       |           |          |          | bit0       | Address      | 2007h  |

| bit 13-8<br>5-4 | 4: 11<br>10<br>01 | L = Up                                        | de prot<br>per hal<br>per 3/4 | ection<br>f of pro<br>th of p | off<br>ogram<br>rogran | memory                              | r code pr<br>ry code p |        |       |           |          |          |            |              |        |

| bit 7:          | 1                 | = Mem                                         | ory Pa                        | rity Ch                       | ecking                 | or Enabl<br>g is enat<br>g is disal | oled                   |        |       |           |          |          |            |              |        |

| bit 6:          | 1                 | <b>oden</b> :<br>= Bor<br>= Bor               | enable                        | ed                            | Reset E                | Enable b                            | <sub>it</sub> (1)      |        |       |           |          |          |            |              |        |

| bit 3:          | 1                 | <b>WRTE</b> :<br>= PWF<br>= PWF               | RT disa                       | bled                          | mer Ei                 | nable bit                           | (1)                    |        |       |           |          |          |            |              |        |

| bit 2:          | 1                 | <b>DTE:</b> \<br>= WDT<br>= WDT               | enabl                         | ed                            | ner En                 | able bit                            |                        |        |       |           |          |          |            |              |        |

| bit 1-0         | 11<br>10<br>01    | DSC1:<br>L = RC<br>D = HS<br>L = XT<br>D = LP | oscilla<br>oscilla<br>oscilla | ator<br>itor<br>tor           | llator \$              | Selectior                           | n bits                 |        |       |           |          |          |            |              |        |

| Note 7          |                   |                                               |                               |                               |                        |                                     | cally ena<br>ed anytir |        | •     |           | ,        | 0        | ess of the | value of bit | PWRTE. |

|                 | 2: Al             | l of the                                      | CP1:0                         | CP0 pa                        | airs ha                | ve to be                            | given the              | e same | value | to enable | e the co | de prote | ection sch | eme listed.  |        |

#### 8.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST), and Brown-out Reset</u> (BOR)

#### 8.4.1 POWER-ON RESET (POR)

### Applicable Devices 710 71 711 715

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

8.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

8.4.3 OSCILLATOR START-UP TIMER (OST)

### Applicable Devices 710 71 711 715

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

8.4.4 BROWN-OUT RESET (BOR)

#### Applicable Devices 710 71 711 715

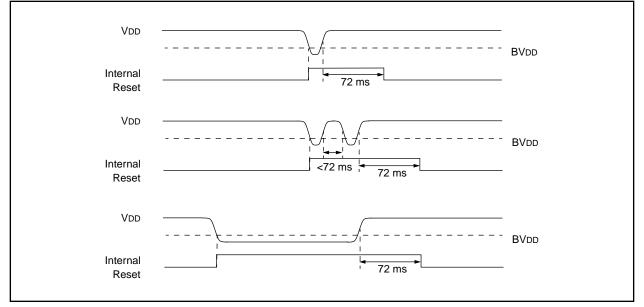

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 8-10 shows typical brown-out situations.

#### FIGURE 8-10: BROWN-OUT SITUATIONS

| BTFSS             | Bit Test f                 | f, Skip if S                                            | Set                       |         | CALL              | Call Sub                                                        | oroutine                             |                                                          |                                             |

|-------------------|----------------------------|---------------------------------------------------------|---------------------------|---------|-------------------|-----------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|---------------------------------------------|

| Syntax:           | [ <i>label</i> ] B1        | FSS f,b                                                 |                           |         | Syntax:           | [ label ]                                                       | CALL                                 | <                                                        |                                             |

| Operands:         | $0 \le f \le 12$           |                                                         |                           |         | Operands:         | $0 \le k \le 2$                                                 | 047                                  |                                                          |                                             |

|                   | 0 ≤ b < 7                  |                                                         |                           |         | Operation:        | : (PC)+ 1 $\rightarrow$ TOS,                                    |                                      |                                                          |                                             |

| Operation:        | skip if (f<                | :b>) = 1                                                |                           |         |                   | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12$ |                                      |                                                          |                                             |

| Status Affected:  | None                       | i                                                       |                           |         |                   | ,                                                               | 1<4:3>) -                            | $\rightarrow$ PC<12                                      | :11>                                        |

| Encoding:         | 01                         | 11bb                                                    | bfff                      | ffff    | Status Affected:  | None                                                            |                                      |                                                          |                                             |

| Description:      |                            | register 'f' is                                         |                           | ne next | Encoding:         | 10                                                              | 0kkk                                 | kkkk                                                     | kkkk                                        |

|                   | If bit 'b' is<br>discarded | is execute<br>1', then the<br>and a NOF<br>aking this a | next instru<br>is execute | ed      | Description:      | (PC+1) is<br>eleven bit<br>into PC bi                           | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the state<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |

| Words:            | 1                          |                                                         |                           |         |                   |                                                                 |                                      | rom PCLA<br>instruction                                  |                                             |

| Cycles:           | 1(2)                       |                                                         |                           |         | Words:            | 1                                                               |                                      |                                                          |                                             |

| Q Cycle Activity: | Q1                         | Q2                                                      | Q3                        | Q4      | Cycles:           | 2                                                               |                                      |                                                          |                                             |

|                   | Decode                     | Read<br>register 'f'                                    | Process<br>data           | NOP     | Q Cycle Activity: | Q1                                                              | Q2                                   | Q3                                                       | Q4                                          |

| If Skip:          | (2nd Cyc                   | :le)                                                    | 1st Cyc                   |         | 1st Cycle         | Decode                                                          | Read<br>literal 'k',                 | Process<br>data                                          | Write to<br>PC                              |

|                   | Q1                         | Q2                                                      | Q3                        | Q4      | 1                 |                                                                 | Push PC<br>to Stack                  |                                                          |                                             |

|                   | NOP                        | NOP                                                     | NOP                       | NOP     | 2nd Cycle         | NOP                                                             | NOP                                  | NOP                                                      | NOP                                         |

| Example           | HERE<br>FALSE              |                                                         | FLAG,1<br>PROCESS_        | _CODE   | Example           | HERE                                                            | CALL                                 | THERE                                                    |                                             |

|                   | TRUE                       | •                                                       |                           |         |                   | Before Ir                                                       |                                      |                                                          |                                             |

|                   |                            | •                                                       |                           |         |                   | After Ins                                                       |                                      | Address HE                                               | RE                                          |

|                   | Before In                  | struction                                               |                           |         |                   |                                                                 | -                                    | ddress TH                                                |                                             |

|                   |                            |                                                         | address H                 | IERE    |                   |                                                                 | TOS = A                              | Address HE                                               | RE+1                                        |

|                   | After Inst                 | ruction<br>if FLAG<1>                                   | - 0                       |         |                   |                                                                 |                                      |                                                          |                                             |

|                   |                            | -                                                       | > = 0,<br>address F≠      | ALSE    |                   |                                                                 |                                      |                                                          |                                             |

|                   |                            | if FLAG<1><br>PC =                                      | ,                         |         |                   |                                                                 |                                      |                                                          |                                             |

|                   |                            | FU = 1                                                  | address TF                | KUE     |                   |                                                                 |                                      |                                                          |                                             |

| XORLW             | Exclusive OR Literal with W |                                           |                 |               |  |  |  |  |  |  |  |

|-------------------|-----------------------------|-------------------------------------------|-----------------|---------------|--|--|--|--|--|--|--|

| Syntax:           | [label]                     | XORL                                      | V k             |               |  |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$             | 255                                       |                 |               |  |  |  |  |  |  |  |

| Operation:        | (W) .XO                     | $R.k \rightarrow (N)$                     | N)              |               |  |  |  |  |  |  |  |

| Status Affected:  | Z                           |                                           |                 |               |  |  |  |  |  |  |  |

| Encoding:         | 11                          | 1010                                      | kkkk            | kkkk          |  |  |  |  |  |  |  |

| Description:      | XOR'ed v                    | ents of the<br>vith the ei<br>t is placed | ght bit lite    | ral 'k'.      |  |  |  |  |  |  |  |

| Words:            | 1                           |                                           |                 |               |  |  |  |  |  |  |  |

| Cycles:           | 1                           |                                           |                 |               |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                          | Q2                                        | Q3              | Q4            |  |  |  |  |  |  |  |

|                   | Decode                      | Read<br>literal 'k'                       | Process<br>data | Write to<br>W |  |  |  |  |  |  |  |

| Example:          | XORLW                       | 0xAF                                      |                 |               |  |  |  |  |  |  |  |

|                   | Before I                    | nstructio                                 | n               |               |  |  |  |  |  |  |  |

|                   |                             | W =                                       | 0xB5            |               |  |  |  |  |  |  |  |

|                   | After Ins                   | truction                                  |                 |               |  |  |  |  |  |  |  |

|                   |                             | W =                                       | 0x1A            |               |  |  |  |  |  |  |  |

|                   |                             |                                           |                 |               |  |  |  |  |  |  |  |

| XORWF             | Exclusiv                                                         | e OR W                   | with f                         |                     |

|-------------------|------------------------------------------------------------------|--------------------------|--------------------------------|---------------------|

| Syntax:           | [label]                                                          | XORWF                    | f,d                            |                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                       |                                |                     |

| Operation:        | (W) .XOF                                                         | $R.\left(f\right)\to($   | dest)                          |                     |

| Status Affected:  | Z                                                                |                          |                                |                     |

| Encoding:         | 00                                                               | 0110                     | dfff                           | ffff                |

| Description:      | Exclusive<br>register wi<br>result is st<br>is 1 the res         | th registe<br>ored in th | r 'f'. If 'd' is<br>e W regist | o the<br>er. If 'd' |

| Words:            | 1                                                                |                          |                                |                     |

| Cycles:           | 1                                                                |                          |                                |                     |

| Q Cycle Activity: | Q1                                                               | Q2                       | Q3                             | Q4                  |

|                   | Decode                                                           | Read<br>register<br>'f'  | Process<br>data                | Write to<br>dest    |

| Example           | XORWF                                                            | REG                      | 1                              |                     |

|                   | Before In                                                        | struction                | 1                              |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | AF<br>B5            |

|                   | After Inst                                                       | ruction                  |                                |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | 1A<br>B5            |

#### 10.6 <u>PICDEM-1 Low-Cost PIC16/17</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 10.7 <u>PICDEM-2 Low-Cost PIC16CXX</u> Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

#### 10.8 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 10.9 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 10.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHAF                        | RACTERISTICS                                                      |               | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended) |                          |                    |                      |                                                                                                                                                                                                                                   |  |  |

|--------------------------------|-------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                   | Characteristic                                                    | Sym           | Min                                                                                                                                                                                                                                               | Тур†                     | Max                | Units                | Conditions                                                                                                                                                                                                                        |  |  |

| D001                           | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0                                                                                                                                                                                                                                        | -                        | 6.0<br>6.0         | V<br>V               | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                            |  |  |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -                                                                                                                                                                                                                                                 | 1.5                      | -                  | V                    |                                                                                                                                                                                                                                   |  |  |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -                                                                                                                                                                                                                                                 | Vss                      | -                  | V                    | See section on Power-on Reset for details                                                                                                                                                                                         |  |  |

| D004*                          | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | Svdd          | 0.05                                                                                                                                                                                                                                              | -                        | -                  | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                         |  |  |

| D005                           | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7                                                                                                                                                                                                                                               | 4.0                      | 4.3                | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                |  |  |

| D010                           | Supply Current<br>(Note 2)                                        | IDD           | -                                                                                                                                                                                                                                                 | 2.0                      | 3.8                | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                     |  |  |

| D010A                          |                                                                   |               | -                                                                                                                                                                                                                                                 | 22.5                     | 48                 | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                   |  |  |

| D015                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -                                                                                                                                                                                                                                                 | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |  |  |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>-                                                                                                                                                                                                                                       | 7.5<br>0.9<br>0.9<br>0.9 | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |  |  |

| D023                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -                                                                                                                                                                                                                                                 | 300*                     | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

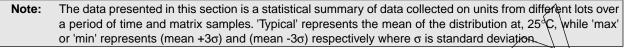

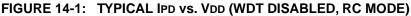

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

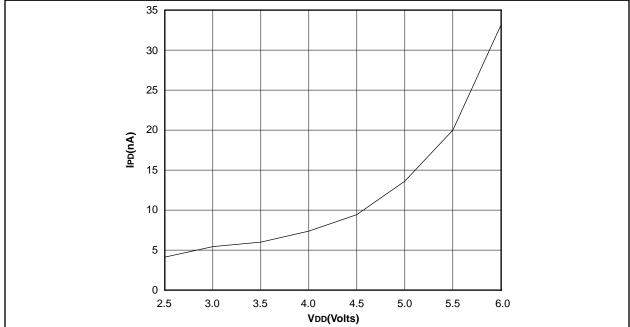

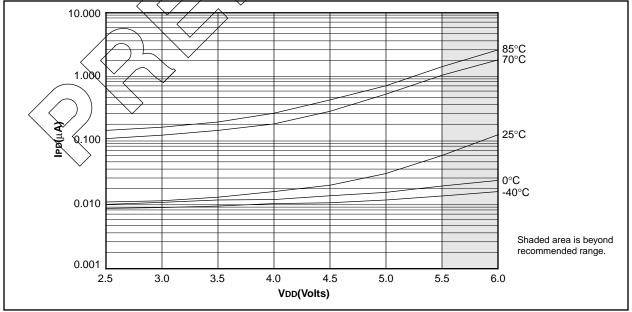

#### FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

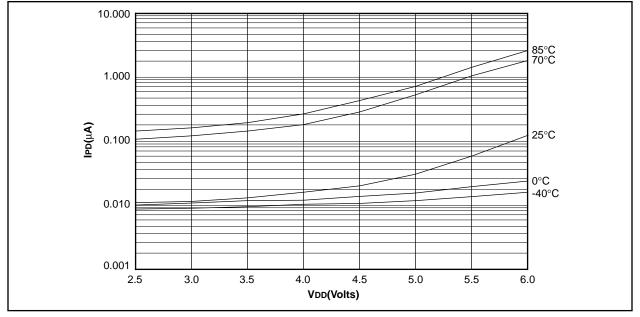

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

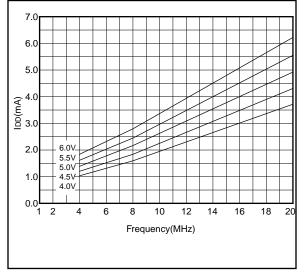

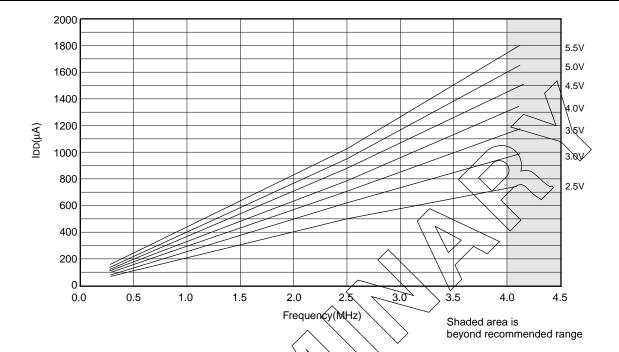

#### FIGURE 12-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

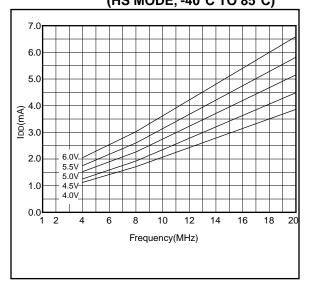

#### FIGURE 12-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

# Applicable Devices71071711715

| DC CHAI      | RACTERISTICS                               | Operati<br>Operati | ng tempe  | ratur<br>e VDI | e 0°C<br>-40°<br>-40° | ⊆<br>C ≤<br>C ≤ | nless otherwise stated)<br>TA ≤ +70°C (commercial)<br>TA ≤ +85°C (industrial)<br>TA ≤ +125°C (extended)<br>cribed in DC spec Section 13.1 |

|--------------|--------------------------------------------|--------------------|-----------|----------------|-----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                             | Sym                | Min       | Тур            | Max                   | Units           | Conditions                                                                                                                                |

| NO.          | Output High Voltage                        |                    |           | 1              |                       |                 |                                                                                                                                           |

| D090         | I/O ports (Note 3)                         | Vон                | Vdd - 0.7 | -              | -                     | V               | ІОН = -3.0 mA, VDp =\4.5V,<br>-40°С to +85°С                                                                                              |

| D090A        |                                            |                    | Vdd - 0.7 | -              | -                     | V               | IOH = -2.5  mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                            |

| D092         | OSC2/CLKOUT (RC osc config)                |                    | Vdd - 0.7 | -              | -                     | V               | IOH = -1.3  mA,  VDD = 4.5  V,<br>-40% to +85%                                                                                            |

| D092A        |                                            |                    | Vdd - 0.7 | -              | -                     | V               | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                             |

|              | Capacitive Loading Specs on<br>Output Pins |                    |           |                |                       |                 |                                                                                                                                           |

| D100         | OSC2 pin                                   | Cosc2              | -         | -              | 15                    | ₽₹              | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1.                                                                   |

| D101         | All I/O pins and OSC2 (in RC mode)         | Сю                 | -         | <              | 50                    | PF              | $\bigvee$                                                                                                                                 |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin:

# 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

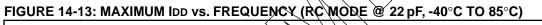

### FIGURE 14-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

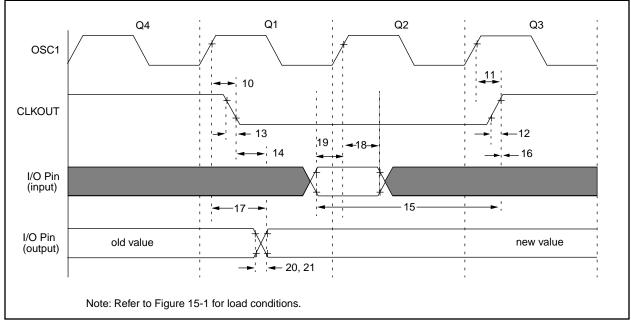

#### FIGURE 15-3: CLKOUT AND I/O TIMING

| TABLE 15-3: CLKOUT AND I/O TIMING REQUIREMENTS | TABLE 15-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|------------------------------------------------|-------------|-------------------------------------------|

|------------------------------------------------|-------------|-------------------------------------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                     | Min | Тур†        | Мах      | Units  | Conditions |

|------------------|----------|---------------------------------------------------|---------------------|-----|-------------|----------|--------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                     | _   | 15          | 30       | ns     | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                     | —   | 15          | 30       | ns     | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  | CLKOUT rise time    |     |             | 15       | ns     | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  |                     | —   | 5           | 15       | ns     | Note 1     |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out vali              | —                   | —   | 0.5Tcy + 20 | ns       | Note 1 |            |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | 0.25Tcy + 25        | —   |             | ns       | Note 1 |            |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | 0                   | —   |             | ns       | Note 1 |            |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                     |     | _           | 80 - 100 | ns     |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 71   | 100 | —           | _        | ns     |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 71  | 200 | —           | _        | ns     |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time) | 0   | —           | -        | ns     |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 71   | —   | 10          | 25       | ns     |            |

|                  |          |                                                   | PIC16 <b>LC</b> 71  | —   | —           | 60       | ns     |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 71   | —   | 10          | 25       | ns     |            |

|                  |          |                                                   | PIC16 <b>LC</b> 71  | —   | —           | 60       | ns     |            |

| 22††*            | Tinp     | INT pin high or low time                          |                     | 20  | —           |          | ns     |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | n or low time       | 20  | —           | _        | ns     |            |

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

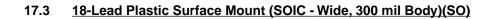

|        | Package Group: Plastic SOIC (SO) |        |           |        |            |           |

|--------|----------------------------------|--------|-----------|--------|------------|-----------|

|        | Millimeters                      |        |           | Inches |            |           |

| Symbol | Min                              | Max    | Notes     | Min    | Мах        | Notes     |

| α      | 0°                               | 8°     |           | 0°     | <b>8</b> ° |           |

| А      | 2.362                            | 2.642  |           | 0.093  | 0.104      |           |

| A1     | 0.101                            | 0.300  |           | 0.004  | 0.012      |           |

| В      | 0.355                            | 0.483  |           | 0.014  | 0.019      |           |

| С      | 0.241                            | 0.318  |           | 0.009  | 0.013      |           |

| D      | 11.353                           | 11.735 |           | 0.447  | 0.462      |           |

| E      | 7.416                            | 7.595  |           | 0.292  | 0.299      |           |

| е      | 1.270                            | 1.270  | Reference | 0.050  | 0.050      | Reference |

| Н      | 10.007                           | 10.643 |           | 0.394  | 0.419      |           |

| h      | 0.381                            | 0.762  |           | 0.015  | 0.030      |           |

| L      | 0.406                            | 1.143  |           | 0.016  | 0.045      |           |

| Ν      | 18                               | 18     |           | 18     | 18         |           |

| CP     | _                                | 0.102  |           | _      | 0.004      |           |

| Figure 7-3:   | ADCON1 Register, PIC16C710/71/711          |

|---------------|--------------------------------------------|

| 0             | (Address 88h),                             |

|               | PIC16C715 (Address 9Fh)                    |

| Figure 7 4    |                                            |

| Figure 7-4:   | A/D Block Diagram                          |

| Figure 7-5:   | Analog Input Model 40                      |

| Figure 7-6:   | A/D Transfer Function 45                   |

| Figure 7-7:   | Flowchart of A/D Operation 45              |

| Figure 8-1:   | Configuration Word for PIC16C71 47         |

| Figure 8-2:   | Configuration Word, PIC16C710/711 48       |

| Figure 8-3:   | Configuration Word, PIC16C71548            |

| Figure 8-4:   | Crystal/Ceramic Resonator Operation        |

| Figure 0-4.   |                                            |

|               | (HS, XT or LP OSC Configuration)           |

| Figure 8-5:   | External Clock Input Operation             |

|               | (HS, XT or LP OSC Configuration)           |

| Figure 8-6:   | External Parallel Resonant Crystal         |

| -             | Oscillator Circuit                         |

| Figure 8-7:   | External Series Resonant Crystal           |

| rigaro o r.   | Oscillator Circuit                         |

|               |                                            |

| Figure 8-8:   | RC Oscillator Mode                         |

| Figure 8-9:   | Simplified Block Diagram of On-chip        |

|               | Reset Circuit52                            |

| Figure 8-10:  | Brown-out Situations53                     |

| Figure 8-11:  | Time-out Sequence on Power-up              |

| 0             | (MCLR not Tied to VDD): Case 1             |

| Figure 8-12:  | Time-out Sequence on Power-up              |

| rigule 0-12.  |                                            |

|               | (MCLR Not Tied To VDD): Case 259           |

| Figure 8-13:  | Time-out Sequence on Power-up              |

|               | (MCLR Tied to VDD) 59                      |

| Figure 8-14:  | External Power-on Reset Circuit            |

| -             | (for Slow VDD Power-up)60                  |

| Figure 8-15:  | External Brown-out Protection Circuit 1 60 |

| Figure 8-16:  | External Brown-out Protection Circuit 2 60 |

|               |                                            |

| Figure 8-17:  | Interrupt Logic, PIC16C710, 71, 711        |

| Figure 8-18:  | Interrupt Logic, PIC16C71562               |

| Figure 8-19:  | INT Pin Interrupt Timing63                 |

| Figure 8-20:  | Watchdog Timer Block Diagram65             |

| Figure 8-21:  | Summary of Watchdog Timer Registers 65     |

| Figure 8-22:  | Wake-up from Sleep Through Interrupt 67    |

| Figure 8-23:  | Typical In-Circuit Serial Programming      |

| r igure e 20. | Connection                                 |

|               |                                            |

| Figure 9-1:   | General Format for Instructions            |

| Figure 11-1:  | Load Conditions94                          |

| Figure 11-2:  | External Clock Timing95                    |

| Figure 11-3:  | CLKOUT and I/O Timing                      |

| Figure 11-4:  | Reset, Watchdog Timer, Oscillator          |

| 0.            | Start-up Timer and Power-up Timer          |

|               | Timing                                     |

| Figure 11 Fr  |                                            |

| Figure 11-5:  | Brown-out Reset Timing                     |

| Figure 11-6:  | Timer0 External Clock Timings              |

| Figure 11-7:  | A/D Conversion Timing 100                  |

| Figure 12-1:  | Typical IPD vs. VDD                        |

|               | (WDT Disabled, RC Mode) 101                |

| Figure 12-2:  | Maximum IPD vs. VDD                        |

|               | (WDT Disabled, RC Mode) 101                |

| Figure 12-3:  |                                            |

| Figure 12-5.  | Typical IPD vs. VDD @ 25°C                 |

|               | (WDT Enabled, RC Mode) 102                 |

| Figure 12-4:  | Maximum IPD vs. VDD                        |

|               | (WDT Enabled, RC Mode) 102                 |

| Figure 12-5:  | Typical RC Oscillator Frequency            |

| -             | vs. VDD                                    |

| Figure 12-6:  | Typical RC Oscillator Frequency            |

|               | vs. VDD                                    |

|               |                                            |

| Figure 12-7:  | Typical RC Oscillator Frequency            |

|               | vs. VDD                                    |

| Figure 12-8:  | Typical IPD vs. VDD Brown-out Detect       |

|               | Enabled (RC Mode) 103                      |

| Figure 12-9:                   | Maximum IPD vs. VDD Brown-out Detect                              |

|--------------------------------|-------------------------------------------------------------------|

| <b>Figure 10 10</b>            | Enabled (85°C to -40°C, RC Mode) 103                              |

| Figure 12-10:                  | Typical IPD vs. Timer1 Enabled<br>(32 kHz, RC0/RC1 = 33 pF/33 pF, |

|                                | (32 kHz, KC0/RC1 = 33 pr/33 pr,<br>RC Mode)                       |

| Figure 12-11:                  | Maximum IPD vs. Timer1 Enabled                                    |

| ga.o                           | (32  kHz, RC0/RC1 = 33  pF/33  pF,)                               |

|                                | 85°C to -40°C, RC Mode) 103                                       |

| Figure 12-12:                  | Typical IDD vs. Frequency                                         |

|                                | (RC Mode @ 22 pF, 25°C) 104                                       |

| Figure 12-13:                  | Maximum IDD vs. Frequency                                         |

|                                | (RC Mode @ 22 pF, -40°C to 85°C) 104                              |

| Figure 12-14:                  | Typical IDD vs. Frequency                                         |

| Figure 12 15                   | (RC Mode @ 100 pF, 25°C) 105<br>Maximum IDD vs. Frequency         |

| Figure 12-15:                  | (RC Mode @ 100 pF, -40°C to 85°C) 105                             |

| Figure 12-16:                  | Typical IDD vs. Frequency                                         |

| · · g · · · · · · · · ·        | (RC Mode @ 300 pF, 25°C) 106                                      |

| Figure 12-17:                  | Maximum IDD vs. Frequency                                         |

| -                              | (RC Mode @ 300 pF, -40°C to 85°C) 106                             |

| Figure 12-18:                  | Typical IDD vs. Capacitance                                       |

|                                | @ 500 kHz (RC Mode) 107                                           |

| Figure 12-19:                  | Transconductance(gm) of                                           |

| Figure 40.00                   | HS Oscillator vs. VDD 107                                         |

| Figure 12-20:                  | Transconductance(gm) of<br>LP Oscillator vs. VDD                  |

| Figure 12-21:                  | Transconductance(gm) of                                           |

|                                | XT Oscillator vs. VDD 107                                         |

| Figure 12-22:                  | Typical XTAL Startup Time vs.                                     |

| 0                              | VDD (LP Mode, 25°C) 108                                           |

| Figure 12-23:                  | Typical XTAL Startup Time vs.                                     |

|                                | VDD (HS Mode, 25°C) 108                                           |

| Figure 12-24:                  | Typical XTAL Startup Time vs.                                     |

| E                              | VDD (XT Mode, 25°C) 108                                           |

| Figure 12-25:                  | Typical IDD vs. Frequency<br>(LP Mode, 25°C)                      |

| Figure 12-26:                  | Maximum IDD vs. Frequency                                         |

| 1 iguro 12 20.                 | (LP Mode, 85°C to -40°C) 109                                      |

| Figure 12-27:                  | Typical IDD vs. Frequency                                         |

| 0                              | (XT Mode, 25°C) 109                                               |

| Figure 12-28:                  | Maximum IDD vs. Frequency                                         |

|                                | (XT Mode, -40°C to 85°C) 109                                      |

| Figure 12-29:                  | Typical IDD vs. Frequency                                         |

| <b>F</b> ilment <b>10</b> ,000 | (HS Mode, 25°C) 110                                               |

| Figure 12-30:                  | Maximum IDD vs. Frequency<br>(HS Mode, -40°C to 85°C) 110         |

| Figure 13-1:                   | Load Conditions                                                   |

| Figure 13-2:                   | External Clock Timing                                             |

| Figure 13-3:                   | CLKOUT and I/O Timing 119                                         |

| Figure 13-4:                   | Reset, Watchdog Timer, Oscillator                                 |

|                                | Start-Up Timer, and Power-Up Timer                                |

| <b>F</b> : 10 <b>F</b>         | Timing                                                            |

| Figure 13-5:                   | Brown-out Reset Timing                                            |

| Figure 13-6:<br>Figure 13-7:   | Timer0 Clock Timings                                              |

| Figure 14-1:                   | Typical IPD vs. VDD                                               |

| . iguic 14-1.                  | (WDT Disabled, RC Mode)                                           |

| Figure 14-2:                   | Maximum IPD vs. VDD                                               |

| č                              | (WDT Disabled, RC Mode) 125                                       |

| Figure 14-3:                   | Typical IPD vs. VDD @ 25°C                                        |

|                                | (WDT Enabled, RC Mode) 126                                        |

| Figure 14-4:                   | Maximum IPD vs. VDD                                               |

| Figure 14 5                    | (WDT Enabled, RC Mode) 126                                        |

| Figure 14-5:                   | Typical RC Oscillator Frequency vs.<br>VDD                        |

|                                | v 00 120                                                          |

|                                |                                                                   |

| Figure 14-6:  | Typical RC Oscillator Frequency vs.                                                              |

|---------------|--------------------------------------------------------------------------------------------------|

| riguio i i o. | VDD126                                                                                           |

| Figure 14-7:  | Typical RC Oscillator Frequency vs.<br>VDD126                                                    |

| Figure 14-8:  | Typical IPD vs. VDD Brown-out Detect<br>Enabled (RC Mode)127                                     |

| Figure 14-9:  | Maximum IPD vs. VDD Brown-out Detect<br>Enabled                                                  |

| Figure 14-10: | (85°C to -40°C, RC Mode)                                                                         |

| Figure 14-11: | Maximum IPD vs. Timer1 Enabled<br>(32 kHz, RC0/RC1 = 33 pF/33 pF,                                |

| Figure 14-12: | 85°C to -40°C, RC Mode)                                                                          |

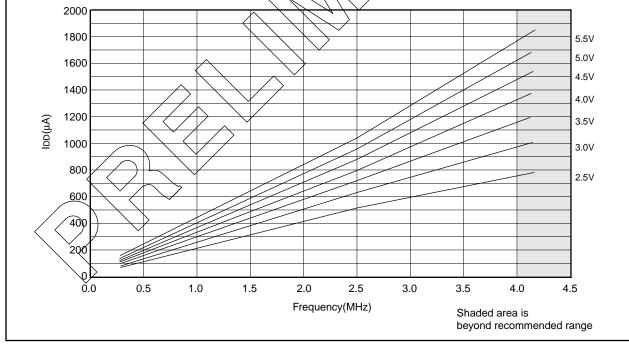

| Figure 14-13: | (RC Mode @ 22 pF, 25 C) 128<br>Maximum IDD vs. Frequency<br>(RC Mode @ 22 pF, -40°C to 85°C) 128 |

| Figure 14-14: | (RC Mode @ 22 pF, -40 C to 85 C) 128<br>Typical IDD vs. Frequency<br>(RC Mode @ 100 pF, 25°C)    |

| Figure 14-15: | Maximum IDD vs. Frequency<br>(RC Mode @ 100 pF, -40°C to 85°C) 129                               |

| Figure 14-16: | Typical IDD vs. Frequency<br>(RC Mode @ 300 pF, 25°C)                                            |

| Figure 14-17: | Maximum IDD vs. Frequency<br>(RC Mode @ 300 pF, -40°C to 85°C) 130                               |

| Figure 14-18: | Typical IDD vs. Capacitance @ 500 kHz<br>(RC Mode)131                                            |

| Figure 14-19: | Transconductance(gm) of<br>HS Oscillator vs. VDD131                                              |

| Figure 14-20: | Transconductance(gm) of<br>LP Oscillator vs. VDD131                                              |

| Figure 14-21: | Transconductance(gm) of<br>XT Oscillator vs. VDD131                                              |

| Figure 14-22: | Typical XTAL Startup Time vs.<br>VDD (LP Mode, 25°C)132                                          |

| Figure 14-23: | Typical XTAL Startup Time vs.<br>VDD (HS Mode, 25°C)132                                          |

| Figure 14-24: | Typical XTAL Startup Time vs.<br>VDD (XT Mode, 25°C)132                                          |

| Figure 14-25: | Typical IDD vs. Frequency<br>(LP Mode, 25°C)133                                                  |

| Figure 14-26: | Maximum IDD vs. Frequency<br>(LP Mode, 85°C to -40°C)                                            |

| Figure 14-27: | Typical IDD vs. Frequency<br>(XT Mode, 25°C)133                                                  |

| Figure 14-28: | Maximum IDD vs. Frequency<br>(XT Mode, -40°C to 85°C)133                                         |

| Figure 14-29: | Typical IDD vs. Frequency<br>(HS Mode, 25°C)134                                                  |

| Figure 14-30: | Maximum IDD vs. Frequency<br>(HS Mode, -40°C to 85°C)134                                         |

| Figure 15-1:  | Load Conditions140                                                                               |

| Figure 15-2:  | External Clock Timing141                                                                         |

| Figure 15-3:  | CLKOUT and I/O Timing142                                                                         |

| Figure 15-4:  | Reset, Watchdog Timer, Oscillator<br>Start-up Timer and Power-up Timer                           |

| Figure 45 5   | Timing                                                                                           |

| Figure 15-5:  | Timer0 External Clock Timings                                                                    |

| Figure 15-6:  | A/D Conversion Timing146                                                                         |

| Figure 16-1:  | Typical RC Oscillator Frequency vs.                                                              |

| Figure 16-2:  | Temperature                                                                                      |

| Figure 10.0   | VDD147                                                                                           |

| Figure 16-3:  | Typical RC Oscillator Frequency vs.<br>VDD147                                                    |

| Figure 16-4:   | Typical RC Oscillator Frequency vs.<br>VDD                     |

|----------------|----------------------------------------------------------------|

| Figure 16-5:   | Typical lpd vs. VDD Watchdog Timer<br>Disabled 25°C148         |

| Figure 16-6:   | Typical Ipd vs. VDD Watchdog Timer<br>Enabled 25°C 148         |

| Figure 16-7:   | Maximum Ipd vs. VDD Watchdog<br>Disabled149                    |

| Figure 16-8:   | Maximum Ipd vs. VDD Watchdog<br>Enabled149                     |

| Figure 16-9:   | Vth (Input Threshold Voltage) of<br>I/O Pins vs. VDD149        |

| Figure 16-10:  | VIH, VIL of MCLR, TOCKI and OSC1<br>(in RC Mode) vs. VDD       |

| Figure 16-11:  | Vтн (Input Threshold Voltage)<br>of OSC1 Input (in XT, HS, and |

|                | LP Modes) vs. VDD 150                                          |

| Figure 16-12:  | Typical IDD vs. Freq (Ext Clock, 25°C) 151                     |

| Figure 16-13:  | Maximum, IDD vs. Freq (Ext Clock,<br>-40° to +85°C)151         |

| Figure 16-14:  | Maximum IDD vs. Freq with A/D Off                              |

|                | (Ext Clock, -55° to +125°C) 152                                |

| Figure 16-15:  | WDT Timer Time-out Period vs. VDD 152                          |

| Figure 16-16:  | Transconductance (gm) of                                       |

| E: 10.17       | HS Oscillator vs. VDD 152                                      |

| Figure 16-17:  | Transconductance (gm) of<br>LP Oscillator vs. VDD              |

| Figure 16-18:  | Transconductance (gm) of                                       |

| . igure te tet | XT Oscillator vs. VDD 153                                      |

| Figure 16-19:  | IOH vs. VOH, VDD = 3V 153                                      |

| Figure 16-20:  | IOH vs. VOH, VDD = 5V 153                                      |

| Figure 16-21:  | IOL vs. VOL, VDD = 3V                                          |

| Figure 16-22:  | IOL vs. VOL, VDD = 5V 154                                      |

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:  | Technical Publications Manager                                                           | Total Pages Sent                                  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| RE:  | : Reader Response                                                                        |                                                   |  |  |  |  |  |

| Fror | m: Name                                                                                  |                                                   |  |  |  |  |  |

|      | Company                                                                                  |                                                   |  |  |  |  |  |

|      |                                                                                          |                                                   |  |  |  |  |  |

|      |                                                                                          |                                                   |  |  |  |  |  |

| A    | Telephone: ()       -       FAX: ()       -         A       i       -                    |                                                   |  |  |  |  |  |

|      | Application (optional):                                                                  |                                                   |  |  |  |  |  |

| Wou  | uld you like a reply?YN                                                                  |                                                   |  |  |  |  |  |

| Dev  | Device: PIC16C71X Literature Number: DS30272A                                            |                                                   |  |  |  |  |  |

| Que  | estions:                                                                                 |                                                   |  |  |  |  |  |

| 1    | What are the best features of this docum                                                 | ent?                                              |  |  |  |  |  |

| 1.   |                                                                                          | GIU:                                              |  |  |  |  |  |

|      |                                                                                          |                                                   |  |  |  |  |  |

| 2.   | . How does this document meet your hardware and software development needs?              |                                                   |  |  |  |  |  |

|      |                                                                                          |                                                   |  |  |  |  |  |