Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Betano                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715-20e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

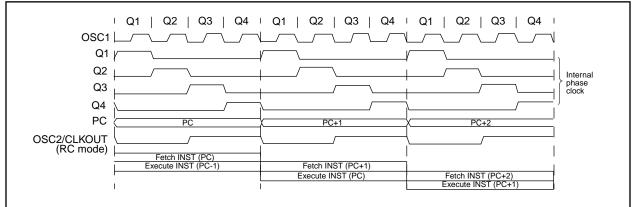

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

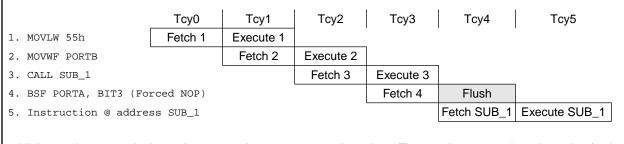

# 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

# 4.2 Data Memory Organization

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow \text{Bank } 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

|                                                                                                                                                                                                                                                                                                                         | 1117 \                         |                                                                      |                 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|-----------------|--|--|

| File<br>Addres                                                                                                                                                                                                                                                                                                          | s                              | ,                                                                    | File<br>Address |  |  |

| 00h                                                                                                                                                                                                                                                                                                                     | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>                                                  | 80h             |  |  |

| 01h                                                                                                                                                                                                                                                                                                                     | TMR0                           | OPTION                                                               | 81h             |  |  |

| 02h                                                                                                                                                                                                                                                                                                                     | PCL                            | PCL                                                                  | 82h             |  |  |

| 03h                                                                                                                                                                                                                                                                                                                     | STATUS                         | STATUS                                                               | 83h             |  |  |

| 04h                                                                                                                                                                                                                                                                                                                     | FSR                            | FSR                                                                  | 84h             |  |  |

| 05h                                                                                                                                                                                                                                                                                                                     | PORTA                          | TRISA                                                                | 85h             |  |  |

| 06h                                                                                                                                                                                                                                                                                                                     | PORTB                          | TRISB                                                                | 86h             |  |  |

| 07h                                                                                                                                                                                                                                                                                                                     |                                | PCON <sup>(2)</sup>                                                  | 87h             |  |  |

| 08h                                                                                                                                                                                                                                                                                                                     | ADCON0                         | ADCON1                                                               | 88h             |  |  |

| 09h                                                                                                                                                                                                                                                                                                                     | ADRES                          | ADRES                                                                | 89h             |  |  |

| 0Ah                                                                                                                                                                                                                                                                                                                     | PCLATH                         | PCLATH                                                               | 8Ah             |  |  |

| 0Bh                                                                                                                                                                                                                                                                                                                     | INTCON                         | INTCON                                                               | 8Bh             |  |  |

| 0Ch                                                                                                                                                                                                                                                                                                                     | General<br>Purpose<br>Register | General<br>Purpose<br>Register<br>Mapped<br>in Bank 0 <sup>(3)</sup> | 8Ch             |  |  |

| 2Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | AFh             |  |  |

| 30h                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | B0h             |  |  |

| 3011                                                                                                                                                                                                                                                                                                                    |                                |                                                                      |                 |  |  |

| l                                                                                                                                                                                                                                                                                                                       | <                              |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

| Ν                                                                                                                                                                                                                                                                                                                       |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      | )               |  |  |

| 7Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | FFh             |  |  |

| L                                                                                                                                                                                                                                                                                                                       | Bank 0                         | Bank 1                                                               | 1               |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>Note 1: Not a physical register.</li> <li>2: The PCON register is not implemented on the PIC16C71.</li> <li>3: These locations are unimplemented in Bank 1. Any access to these locations will access the corresponding Bank 0 register.</li> </ul> |                                |                                                                      |                 |  |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |  |

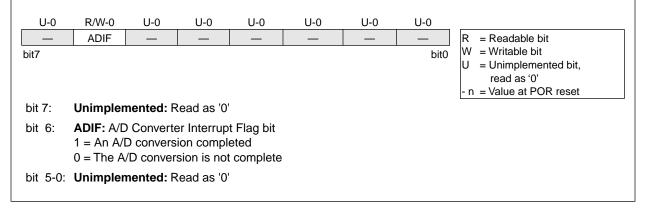

# 4.2.2.5 PIR1 REGISTER

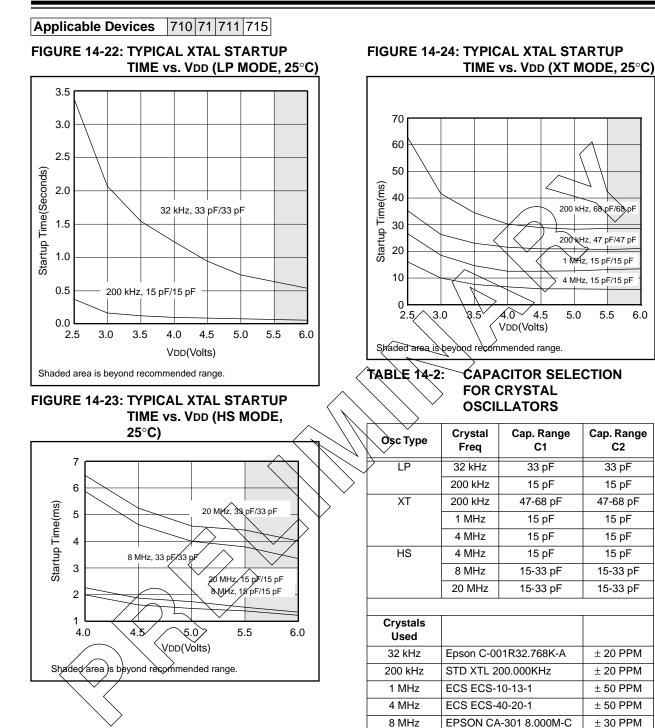

# Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

# 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Applicable Devices 710 71 711 715

The analog-to-digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 7-1 and Figure 7-2, controls the operation of the A/D module. The ADCON1 register, shown in Figure 7-3 configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0<br>ADCS1 | R/W-0<br>ADCS0                                                                                                                                            | U-0                         | R/W-0<br>CHS1 | R/W-0<br>CHS0 | R/W-0<br>GO/DONE                   | R/W-0<br>ADIF | R/W-0<br>ADON | R = Readable bit                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|---------------|------------------------------------|---------------|---------------|--------------------------------------------------------------------------------------|

| bit7           | ADCSU                                                                                                                                                     |                             | CHST          | CHSU          | GO/DONE                            | ADIF          | bit0          | W = Writable bit<br>U = Unimplemented<br>bit, read as '0'<br>- n =Value at POR reset |

| bit 7-6:       | 00 = Fos<br>01 = Fos<br>10 = Fos                                                                                                                          | c/8                         |               |               |                                    |               |               |                                                                                      |

| bit 5:         | Unimple                                                                                                                                                   | <b>nented:</b> Re           | ad as '0'.    |               |                                    |               |               |                                                                                      |

| bit 4-3:       | CHS1:CHS0: Analog Channel Select bits<br>00 = channel 0, (RA0/AN0)<br>01 = channel 1, (RA1/AN1)<br>10 = channel 2, (RA2/AN2)<br>11 = channel 3, (RA3/AN3) |                             |               |               |                                    |               |               |                                                                                      |

| bit 2:         | GO/DON                                                                                                                                                    | E: A/D Con                  | version Sta   | atus bit      |                                    |               |               |                                                                                      |

|                |                                                                                                                                                           | onversion ir<br>onversion r |               |               | is bit starts th<br>bit is automat |               |               | are when the A/D conver-                                                             |

|                | ADIF: A/D Conversion Complete Interrupt Flag bit<br>1 = conversion is complete (must be cleared in software)<br>0 = conversion is not complete            |                             |               |               |                                    |               |               |                                                                                      |

|                |                                                                                                                                                           | onverter mo                 | •             | •             | consumes no                        | operating o   | current       |                                                                                      |

| Note 1:        |                                                                                                                                                           | DCON0 is a nented, read     |               | Purpose R     | /W bit for the                     | PIC16C71      | 0/711 only. I | For the PIC16C71, this bit is                                                        |

# FIGURE 7-1: ADCON0 REGISTER (ADDRESS 08h), PIC16C710/71/711

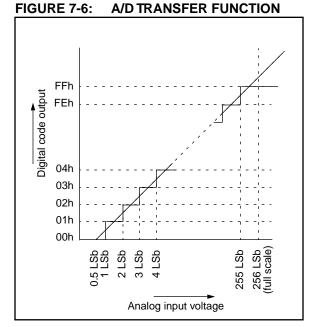

# 7.9 <u>Transfer Function</u>

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is Analog VREF/256 (Figure 7-6).

# 7.10 <u>References</u>

A very good reference for understanding A/D converters is the "Analog-Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

ADON = 0Yes ADON = 0 No Acquire Selected Channel Yes GO = 0? No Start of A/D onversion Delaye Instruction Cycle Yes A/D Clock = RC? /es SLEEP Finish Conversior Inst uction GO = 0 ADIF = 1 No No Yes Abort Conversion Yes Wake-up From Sleep inish Conversio Device in SLEEP? Wait 2 TAD GO = 0ADIF = 0 GO = 0 ADIF = 1 No No SLEEP Power-down A/D Finish Conversion Stay in Sleep Power-down A/D Wait 2 TAD GO = 0 ADIF = 1 Wait 2 TAD

FIGURE 7-7: FLOWCHART OF A/D OPERATION

# 8.4.5 TIME-OUT SEQUENCE

# Applicable Devices 710 71 711 715

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

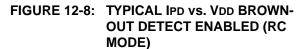

## 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

# Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

# 8.4.7 PARITY ERROR RESET (PER)

# Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

# TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power-up         |           | Brown out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

# **PIC16C71X**

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] C                                                    | LRF f                   |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$                                                      | 7                       |                 |                       |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | I                       |                 |                       |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | G_REG           |                       |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |                         |                 |                       |  |  |  |

|                   | $FLAG\_REG = 0x00$ $Z = 1$                                            |                         |                 |                       |  |  |  |

| CLRW                                                                | Clear W                                                                                                                                                    |                                                          |                                                           |                                                                               |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|

| Syntax:                                                             | [ label ]                                                                                                                                                  | CLRW                                                     |                                                           |                                                                               |

| Operands:                                                           | None                                                                                                                                                       |                                                          |                                                           |                                                                               |

| Operation:                                                          | $00h \rightarrow (V 1 \rightarrow Z$                                                                                                                       | V)                                                       |                                                           |                                                                               |

| Status Affected:                                                    | Z                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Encoding:                                                           | 00                                                                                                                                                         | 0001                                                     | 0xxx                                                      | xxxx                                                                          |

| Description:                                                        | W register set.                                                                                                                                            | is cleare                                                | d. Zero bit                                               | (Z) is                                                                        |

| Words:                                                              | 1                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Cycles:                                                             | 1                                                                                                                                                          |                                                          |                                                           |                                                                               |

| Q Cycle Activity:                                                   | Q1                                                                                                                                                         | Q2                                                       | Q3                                                        | Q4                                                                            |

|                                                                     | Decode                                                                                                                                                     | NOP                                                      | Process<br>data                                           | Write to<br>W                                                                 |

| Example                                                             | CLRW                                                                                                                                                       |                                                          |                                                           |                                                                               |

|                                                                     | Before In                                                                                                                                                  | struction                                                | 1                                                         |                                                                               |

|                                                                     |                                                                                                                                                            | W =                                                      | 0x5A                                                      |                                                                               |

|                                                                     | After Inst                                                                                                                                                 |                                                          |                                                           |                                                                               |

|                                                                     |                                                                                                                                                            | W =<br>Z =                                               | 0x00<br>1                                                 |                                                                               |

|                                                                     |                                                                                                                                                            | -                                                        | •                                                         |                                                                               |

| CLRWDT                                                              | Clear Wa                                                                                                                                                   | tchdog                                                   | Timer                                                     |                                                                               |

| Syntax:                                                             | [ label ]                                                                                                                                                  | CLRWD                                                    | Т                                                         |                                                                               |

| Operands:                                                           | None                                                                                                                                                       |                                                          |                                                           |                                                                               |

| Operation:                                                          | $00h \rightarrow W$                                                                                                                                        |                                                          |                                                           |                                                                               |

|                                                                     | $0 \rightarrow WDT \\ 1 \rightarrow \overline{TO}$                                                                                                         | r presca                                                 | ler,                                                      |                                                                               |

|                                                                     | $1 \rightarrow \overline{PD}$                                                                                                                              |                                                          |                                                           |                                                                               |

|                                                                     |                                                                                                                                                            |                                                          |                                                           |                                                                               |

| Status Affected:                                                    | TO, PD                                                                                                                                                     |                                                          |                                                           |                                                                               |

| Status Affected:<br>Encoding:                                       | <b>TO</b> , <b>PD</b>                                                                                                                                      | 0000                                                     | 0110                                                      | 0100                                                                          |

| Encoding:                                                           | 00<br>CLRWDT in                                                                                                                                            | struction                                                | resets the                                                | Watch-                                                                        |

|                                                                     | 00                                                                                                                                                         | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:                                                           | 00<br>CLRWDT in<br>dog Timer<br>of the WD                                                                                                                  | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:                                           | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.                                                                                                      | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:<br>Words:                                 | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1                                                                                                 | struction<br>It also re                                  | resets the<br>sets the pi                                 | Watch-<br>rescaler                                                            |

| Encoding:<br>Description:<br>Words:<br>Cycles:                      | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1                                                                                            | Instruction<br>It also re<br>T. Status I                 | resets the<br>set <u>s</u> the pr<br>bits TO and          | Watch-<br>re <u>sca</u> ler<br>d PD                                           |

| Encoding:<br>Description:<br>Words:<br>Cycles:                      | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1                                                                                | Istruction<br>It also re<br>T. Status I                  | resets the<br>sets the pl<br>pits TO and<br>Q3<br>Process | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1<br>Decode                                                                       | Q2                                                       | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer<br>of the WD<br>are set.<br>1<br>1<br>2<br>4<br>2<br>1<br>2<br>2<br>2<br>2<br>CLRWDT<br>Before In                             | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT                              |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>0<br>2<br>1<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2 | Q2<br>NOP<br>Struction<br>WDT cou                        | Q3<br>Process<br>data                                     | Watch-<br>re <u>sc</u> aler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter          |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0<br>2<br>0 | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou<br>WDT pres | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00<br>0 |

| Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | 00<br>CLRWDT in<br>dog Timer,<br>of the WD<br>are set.<br>1<br>1<br>2<br>Q1<br>Decode<br>CLRWDT<br>Before In<br>After Inst                                 | Q2<br>NOP<br>Struction<br>WDT cou<br>WDT cou             | Q3<br>Process<br>data                                     | Watch-<br>rescaler<br>d PD<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00      |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                           | Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                     |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                        |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                            |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

|                   |                                                                                                                                                                                                             |                   |                                                                                                                                                                                                              |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                            |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                            |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                  |

|                   | Decode Read Process Write to data dest                                                                                                                                                                      |                   | Decode Read register data Virite to dest                                                                                                                                                                     |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                   |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                         |

#### 11.2 PIC16LC710-04 (Commercial, Industrial, Extended) DC Characteristics: PIC16LC711-04 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS             |                                                                   |               |             | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended) |                    |                      |                                                                                                                                                                                                                                   |  |  |

|--------------------------------|-------------------------------------------------------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                   | Characteristic                                                    | Sym           | Min         | Тур†                                                                                                                                                                                                                                              | Max                | Units                | Conditions                                                                                                                                                                                                                        |  |  |

| D001                           | Supply Voltage<br>Commercial/Industrial<br>Extended               | Vdd<br>Vdd    | 2.5<br>3.0  | -                                                                                                                                                                                                                                                 | 6.0<br>6.0         | V<br>V               | LP, XT, RC osc configuration (DC - 4 MHz)<br>LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                            |  |  |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -           | 1.5                                                                                                                                                                                                                                               | -                  | V                    |                                                                                                                                                                                                                                   |  |  |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -           | Vss                                                                                                                                                                                                                                               | -                  | V                    | See section on Power-on Reset for details                                                                                                                                                                                         |  |  |

| D004*                          | VDD rise rate to ensure<br>internal Power-on<br>Reset<br>signal   | Svdd          | 0.05        | -                                                                                                                                                                                                                                                 | -                  | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                         |  |  |

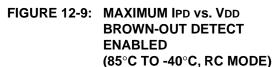

| D005                           | Brown-out Reset<br>Voltage                                        | Bvdd          | 3.7         | 4.0                                                                                                                                                                                                                                               | 4.3                | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                |  |  |

| D010                           | Supply Current<br>(Note 2)                                        | IDD           | -           | 2.0                                                                                                                                                                                                                                               | 3.8                | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                     |  |  |

| D010A                          |                                                                   |               | -           | 22.5                                                                                                                                                                                                                                              | 48                 | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                   |  |  |

| D015                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ IBOR | -           | 300*                                                                                                                                                                                                                                              | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |  |  |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9<br>0.9                                                                                                                                                                                                                          | 30<br>5<br>5<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |  |  |

| D023                           | Brown-out Reset<br>Current (Note 5)                               | $\Delta$ Ibor | -           | 300*                                                                                                                                                                                                                                              | 500                | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                            |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only † and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

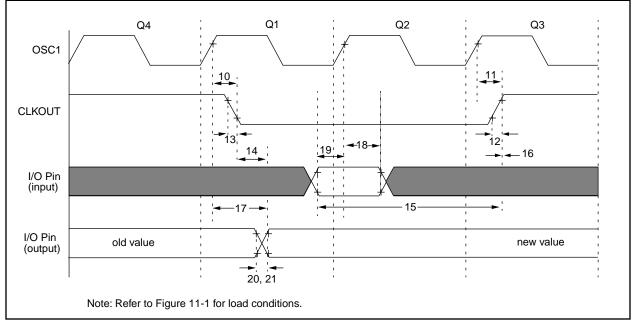

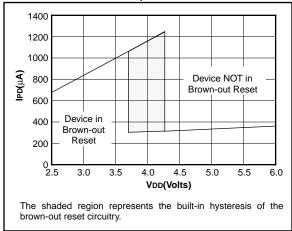

# FIGURE 11-3: CLKOUT AND I/O TIMING

# TABLE 11-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min                    | Тур†         | Мах | Units       | Conditions |        |

|------------------|----------|------------------------------------------------------------------|------------------------|--------------|-----|-------------|------------|--------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                                                 |                        | _            | 15  | 30          | ns         | Note 1 |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                                                 |                        |              | 15  | 30          | ns         | Note 1 |

| 12*              | TckR     | CLKOUT rise time                                                 |                        | —            | 5   | 15          | ns         | Note 1 |

| 13*              | TckF     | CLKOUT fall time                                                 |                        |              | 5   | 15          | ns         | Note 1 |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out valid                            | d                      | _            | —   | 0.5Tcy + 20 | ns         | Note 1 |

| 15*              | TioV2ckH | Port in valid before CLKOL                                       | T ↑                    | 0.25Tcy + 25 | —   | _           | ns         | Note 1 |

| 16*              | TckH2iol | Port in hold after CLKOUT                                        | $\uparrow$             | 0            | —   |             | ns         | Note 1 |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid                |                        | _            | _   | 80 - 100    | ns         |        |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to<br>Port input invalid (I/O in ho | ld time)               | TBD          | _   | _           | ns         |        |

| 19*              | TioV2osH | Port input valid to OSC11                                        | (I/O in setup time)    | TBD          | —   | _           | ns         |        |

| 20*              | TioR     | Port output rise time                                            | PIC16 <b>C</b> 710/711 | _            | 10  | 25          | ns         |        |

|                  |          |                                                                  | PIC16LC710/711         | _            | —   | 60          | ns         |        |

| 21*              | TioF     | Port output fall time                                            | PIC16 <b>C</b> 710/711 | _            | 10  | 25          | ns         |        |

|                  |          |                                                                  | PIC16LC710/711         | —            | —   | 60          | ns         |        |

| 22††*            | Tinp     | INT pin high or low time                                         |                        | 20           | —   | _           | ns         |        |

| 23††*            | Trbp     | RB7:RB4 change INT high                                          | or low time            | 20           | —   | _           | ns         |        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

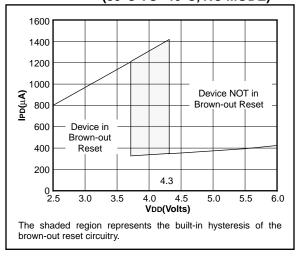

# FIGURE 12-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

Applicable Devices 710 71 711 715

# TABLE 12-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average      |        |  |

|--------|------|--------------|--------|--|

| Cext   | Rext | Fosc @ 5V, 2 | 25°C   |  |

| 22 pF  | 5k   | 4.12 MHz     | ± 1.4% |  |

|        | 10k  | 2.35 MHz     | ± 1.4% |  |

|        | 100k | 268 kHz      | ± 1.1% |  |

| 100 pF | 3.3k | 1.80 MHz     | ± 1.0% |  |

|        | 5k   | 1.27 MHz     | ± 1.0% |  |

|        | 10k  | 688 kHz      | ± 1.2% |  |

|        | 100k | 77.2 kHz     | ± 1.0% |  |

| 300 pF | 3.3k | 707 kHz      | ± 1.4% |  |

|        | 5k   | 501 kHz      | ± 1.2% |  |

|        | 10k  | 269 kHz      | ± 1.6% |  |

|        | 100k | 28.3 kHz     | ± 1.1% |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

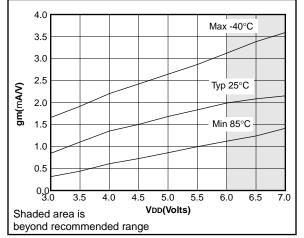

# FIGURE 12-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

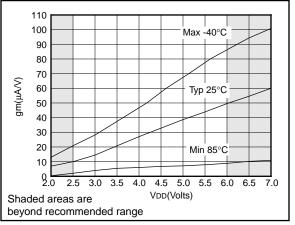

# FIGURE 12-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

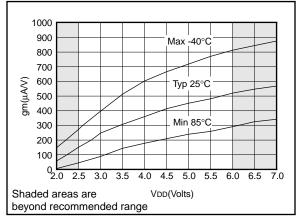

# FIGURE 12-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

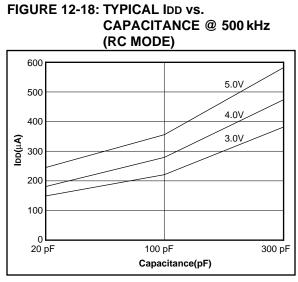

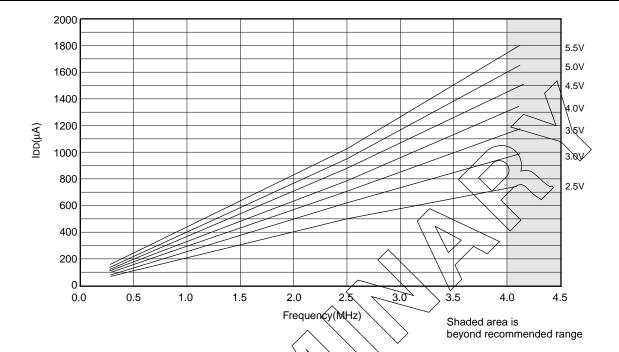

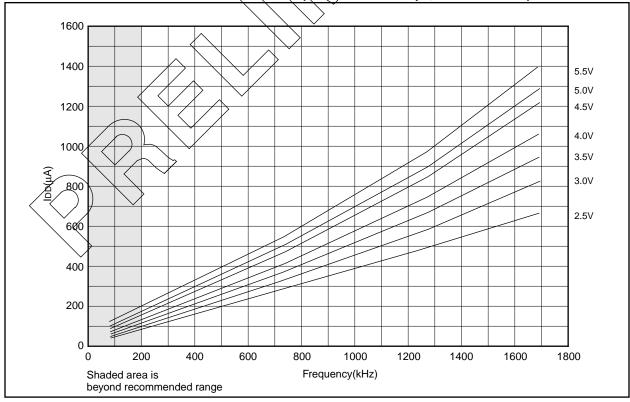

# FIGURE 14-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

# PIC16C71X

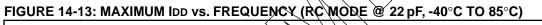

# Applicable Devices 710 71 711 715

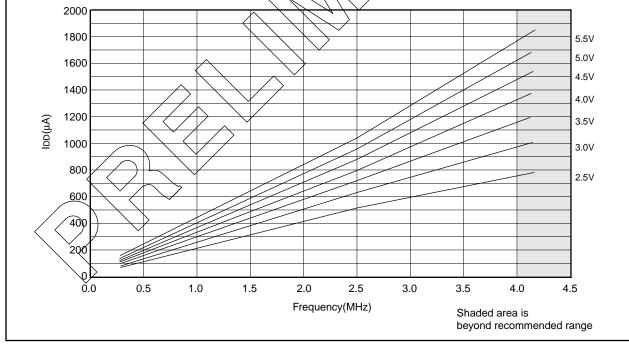

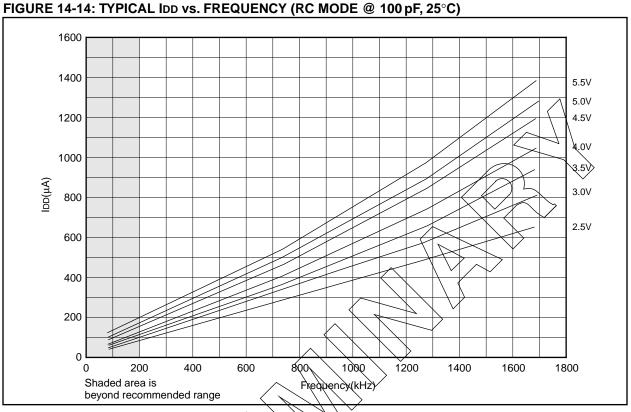

FIGURE 14-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

20 MHz

DS30272A-page 132

± 30 PPM

EPSON CA-301 20.000M-C

6.0

# 15.2 DC Characteristics: PIC16LC71-04 (Commercial, Industrial)

|                       |                                                                  |      |      |                 |               |                | $C \leq TA \leq +70^{\circ}C$ (commercial)                                                                                                                                                                           |

|-----------------------|------------------------------------------------------------------|------|------|-----------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym  | Min  | Тур†            | Max           | Units          | Conditions                                                                                                                                                                                                           |

| D001                  | Supply Voltage                                                   | Vdd  | 3.0  | -               | 6.0           | V              | XT, RC, and LP osc configuration                                                                                                                                                                                     |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -    | 1.5             | -             | V              |                                                                                                                                                                                                                      |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -    | Vss             | -             | V              | See section on Power-on Reset for details                                                                                                                                                                            |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD | 0.05 | -               | -             | V/ms           | See section on Power-on Reset for details                                                                                                                                                                            |

| D010                  | Supply Current (Note 2)                                          | IDD  | -    | 1.4             | 2.5           | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                        |

| D010A                 |                                                                  |      | -    | 15              | 32            | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                      |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3)                                   | IPD  | -    | 5<br>0.6<br>0.6 | 20<br>9<br>12 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 3.0V, WDT \text{ disabled, } 0^{\circ}C \text{ to } +70^{\circ}C$ $VDD = 3.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +85^{\circ}C$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

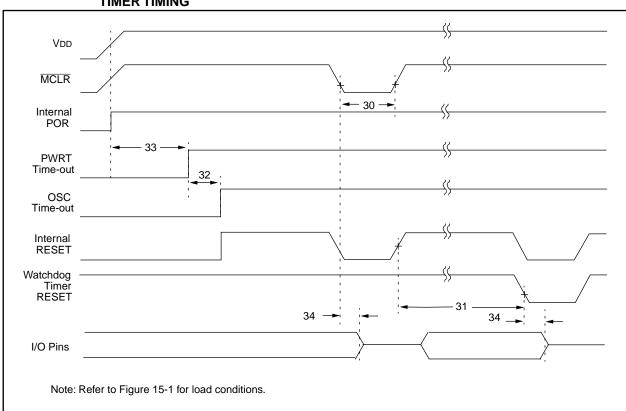

# FIGURE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 15-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†      | Мах  | Units | Conditions               |

|------------------|-------|--------------------------------------------------|-----|-----------|------|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 200 | —         | _    | ns    | VDD = 5V, -40°C to +85°C |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*  | 18        | 33*  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | _   | 1024 Tosc | -    | —     | Tosc = OSC1 period       |

| 33               | Tpwrt | Power-up Timer Period                            | 28* | 72        | 132* | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O High Impedance from MCLR<br>Low              | —   | —         | 100  | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

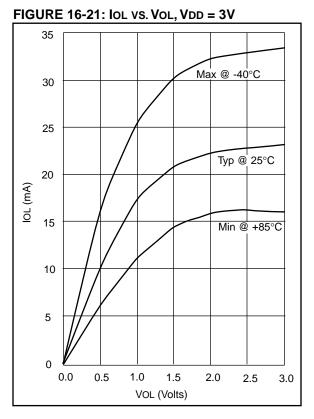

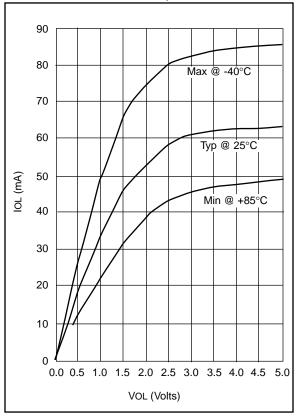

FIGURE 16-22: IOL VS. VOL, VDD = 5V

# **PIC16C71X**

| RA2/AN2                         |                                        | a                                                                                                                          |

|---------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                 |                                        |                                                                                                                            |