Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c715t-20e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

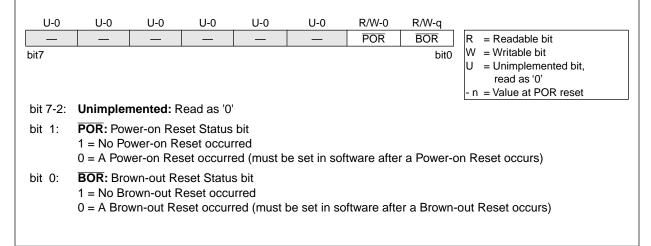

#### 4.2.2.6 PCON REGISTER

#### Applicable Devices71071711715

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset (BOR) condition from a Power-on Reset condition. For the PIC16C715 the PCON register also contains status bits MPEEN and PER. MPEEN reflects the value of the MPEEN bit in the configuration word. PER indicates a parity error reset has occurred. Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### FIGURE 4-12: PCON REGISTER (ADDRESS 8Eh), PIC16C710/711

#### FIGURE 4-13: PCON REGISTER (ADDRESS 8Eh), PIC16C715

| R-U<br>MPEEN | U-0                                                                                                           | U-0       | U-0        | U-0  | R/W-1        | R/W-0       | R/W-q<br>BOR <sup>(1)</sup> | R = Readable bit                                                                      |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|-----------|------------|------|--------------|-------------|-----------------------------|---------------------------------------------------------------------------------------|--|--|--|

| bit7         |                                                                                                               |           |            |      |              |             | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |

| bit 7:       | bit 7: MPEEN: Memory Parity Error Circuitry Status bit<br>Reflects the value of configuration word bit, MPEEN |           |            |      |              |             |                             |                                                                                       |  |  |  |

| bit 6-3:     | Unimplen                                                                                                      | nented: R | ead as '0' |      |              |             |                             |                                                                                       |  |  |  |

| bit 2:       | ·                                                                                                             |           |            |      |              |             |                             |                                                                                       |  |  |  |

| bit 1:       |                                                                                                               |           |            |      |              |             |                             |                                                                                       |  |  |  |

| bit 0:       | <b>BOR:</b> Bro<br>1 = No Bro<br>0 = A Bro                                                                    | own-out R | eset occu  | rred | be set in sc | oftware aft | er a Brown-                 | out Reset occurs)                                                                     |  |  |  |

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

#### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x | 500      |                                                      |

|--------|----------|------------------------------------------------------|

| BSF    | pclath,3 | ;Select page 1 (800h-FFFh)                           |

| BCF    | pclath,4 | ;Only on >4K devices                                 |

| CALL   | SUB1_P1  | ;Call subroutine in                                  |

|        | :        | ;page 1 (800h-FFFh)                                  |

|        | :        |                                                      |

|        | :        |                                                      |

| ORG 0x | 900      |                                                      |

| SUB1_P | 1:       | ;called subroutine                                   |

|        | :        | ;page 1 (800h-FFFh)                                  |

|        | :        |                                                      |

| RETURN |          | ;return to Call subroutine<br>;in page 0 (000h-7FFh) |

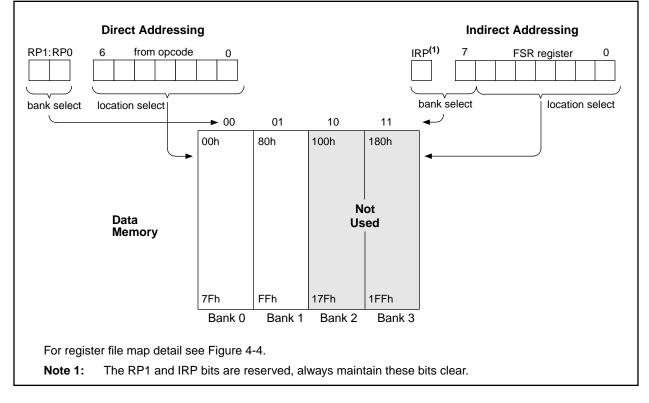

#### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-15. However, IRP is not used in the PIC16C71X devices.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | 0x20<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |                                               |                                                                                                    |

|          | :                     |                                               | ;yes continue                                                                                      |

#### FIGURE 4-15: DIRECT/INDIRECT ADDRESSING

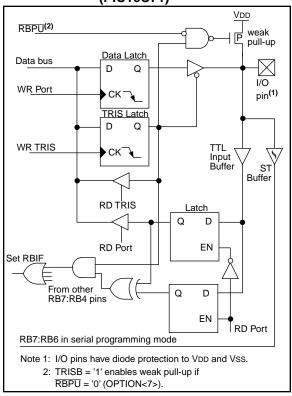

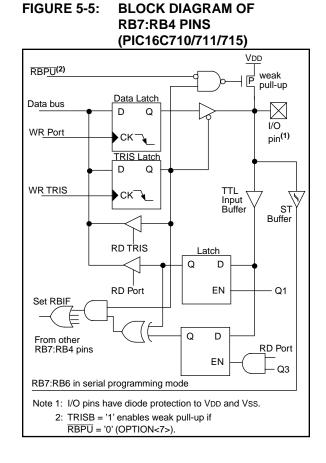

#### FIGURE 5-4: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C71)

#### TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-3 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-3: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

;

| ; |     |        |       |   | PORT | latch | PORT p | ins  |

|---|-----|--------|-------|---|------|-------|--------|------|

| ; |     |        |       |   |      |       |        |      |

|   | BCF | PORTB, | 7     | ; | 01pp | pppp  | llpp j | pppp |

|   | BCF | PORTB, | б     | ; | 10pp | pppp  | 11pp   | pppp |

|   | BSF | STATUS | , RP0 | ; |      |       |        |      |

|   | BCF | TRISB, | 7     | ; | 10pp | pppp  | 11pp g | pppp |

|   | BCF | TRISB, | 6     | ; | 10pp | pppp  | 10pp j | pppp |

|   |     |        |       |   |      |       |        |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

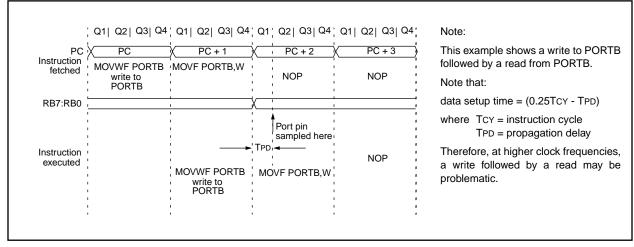

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-6). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-6: SUCCESSIVE I/O OPERATION

### 8.0 SPECIAL FEATURES OF THE CPU

#### Applicable Devices 710 71 711 715

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PER) (PIC16C715)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 8.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 8-1: CONFIGURATION WORD FOR PIC16C71

| bit13     | -   -                                                       | —                                                                                             | —       | _        | _        | —       | —       | CP0      | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|-----------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------|----------|----------|---------|---------|----------|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5: | Unimpler                                                    | nented                                                                                        | : Read  | as '1'   |          |         |         |          |       |      |       |               |                      |                 |

| bit 4:    | <b>CP0:</b> Cod<br>1 = Code<br>0 = All me                   | protect                                                                                       | ion off |          | ed, but  | 00h - 3 | Fh is w | /ritable |       |      |       |               |                      |                 |

| bit 3:    | 1 = Power                                                   | PWRTE: Power-up Timer Enable bit<br>1 = Power-up Timer enabled<br>0 = Power-up Timer disabled |         |          |          |         |         |          |       |      |       |               |                      |                 |

| bit 2:    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                        | enabled                                                                                       | ł       | Enable   | e bit    |         |         |          |       |      |       |               |                      |                 |

| bit 1-0:  | FOSC1:F<br>11 = RC c<br>10 = HS c<br>01 = XT c<br>00 = LP o | oscillato<br>oscillato<br>oscillato                                                           | or<br>r | tor Sele | ection b | vits    |         |          |       |      |       |               |                      |                 |

# 9.1 Instruction Descriptions

|                   |                                                                                 | •                   | _               |               |  |  |  |

|-------------------|---------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|

| ADDLW             | Add Lite                                                                        | ral and \           | N               |               |  |  |  |

| Syntax:           | [ <i>label</i> ] Al                                                             | DDLW                | k               |               |  |  |  |

| Operands:         | $0 \le k \le 25$                                                                | 55                  |                 |               |  |  |  |

| Operation:        | (W) + k –                                                                       | → (W)               |                 |               |  |  |  |

| Status Affected:  | C, DC, Z                                                                        |                     |                 |               |  |  |  |

| Encoding:         | 11                                                                              | 111x                | kkkk            | kkkk          |  |  |  |

| Description:      | The conter<br>added to the<br>result is pla                                     | ne eight b          | it literal 'k'  | and the       |  |  |  |

| Words:            | 1                                                                               |                     |                 |               |  |  |  |

| Cycles:           | 1                                                                               |                     |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                                                              | Q2                  | Q3              | Q4            |  |  |  |

|                   | Decode                                                                          | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |

| Example:          | ADDLW $0x15$<br>Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25 |                     |                 |               |  |  |  |

| ADDWF             | Add W a                                                                         | nd f                |                 |               |  |  |  |

| Syntax:           | [ <i>label</i> ] Al                                                             | DDWF                | f,d             |               |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                  | 7                   |                 |               |  |  |  |

| Operation:        | (W) + (f) -                                                                     | ightarrow (dest)    |                 |               |  |  |  |

| Status Affected:  | C, DC, Z                                                                        |                     |                 |               |  |  |  |

| Encoding:         | 00                                                                              | 0111                | dfff            | ffff          |  |  |  |

| Description:      | Add the co<br>with regist<br>stored in th                                       | er 'f'. If 'd'      | is 0 the re     | sult is       |  |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff             |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|------------------|--|--|--|

| Description:      | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                         |                 |                  |  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                  |  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4               |  |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to<br>Dest |  |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                  |  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0x17<br>0xC2    |                  |  |  |  |

|                   | After Inst                                                                                                                                                                |                         | 0               |                  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                  |  |  |  |

| ANDLW             | AND Lite                                                                                                            | eral with              | w               |               |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|---------------|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                  | NDLW                   | k               |               |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                     | 55                     |                 |               |  |  |

| Operation:        | (W) .ANE                                                                                                            | D. (k) $\rightarrow$ ( | W)              |               |  |  |

| Status Affected:  | Z                                                                                                                   |                        |                 |               |  |  |

| Encoding:         | 11                                                                                                                  | 1001                   | kkkk            | kkkk          |  |  |

| Description:      | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                        |                 |               |  |  |

| Words:            | 1                                                                                                                   |                        |                 |               |  |  |

| Cycles:           | 1                                                                                                                   |                        |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                                                                  | Q2                     | Q3              | Q4            |  |  |

|                   | Decode                                                                                                              | Read<br>literal "k"    | Process<br>data | Write to<br>W |  |  |

| Example           | ANDLW                                                                                                               | 0x5F                   |                 |               |  |  |

|                   | Before In                                                                                                           | struction              | 0xA3            |               |  |  |

|                   | After Inst                                                                                                          | •• –                   | UXAU            |               |  |  |

|                   |                                                                                                                     | = W                    | 0x03            |               |  |  |

|                   |                                                                                                                     |                        |                 |               |  |  |

| ANDWF             | AND W v                        | vith f                                                                                                                                                    |                 |                  |  |  |  |

|-------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] A             | NDWF                                                                                                                                                      | f,d             |                  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$ | .7                                                                                                                                                        |                 |                  |  |  |  |

| Operation:        | (W) .ANE                       | D. (f) $\rightarrow$ (c                                                                                                                                   | dest)           |                  |  |  |  |

| Status Affected:  | Z                              |                                                                                                                                                           |                 |                  |  |  |  |

| Encoding:         | 00                             | 0101                                                                                                                                                      | dfff            | ffff             |  |  |  |

| Description:      | 'd' is 0 the register. If      | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |                 |                  |  |  |  |

| Words:            | 1                              |                                                                                                                                                           |                 |                  |  |  |  |

| Cycles:           | 1                              |                                                                                                                                                           |                 |                  |  |  |  |

| Q Cycle Activity: | Q1                             | Q2                                                                                                                                                        | Q3              | Q4               |  |  |  |

|                   | Decode                         | Read<br>register<br>'f'                                                                                                                                   | Process<br>data | Write to<br>Dest |  |  |  |

| Example           | ANDWF                          | FSR,                                                                                                                                                      | 1               |                  |  |  |  |

|                   | Before In                      |                                                                                                                                                           |                 |                  |  |  |  |

|                   | After Inst                     | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                               |                 |                  |  |  |  |

#### SLEEP

| [ label ]                                                                                                                                                                                                               | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| None                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                    |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| TO, PD                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 00                                                                                                                                                                                                                      | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| The power-down status bit, PD is<br>cleared. Time-out status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Q1                                                                                                                                                                                                                      | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Decode                                                                                                                                                                                                                  | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SLEEP                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                         | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |  |  |

| SUBLW             | Subtract              | W from             | Literal                                                                    |  |  |

|-------------------|-----------------------|--------------------|----------------------------------------------------------------------------|--|--|

| Syntax:           | [ label ]             | SUBL               | N k                                                                        |  |  |

| Operands:         | $0 \le k \le 255$     |                    |                                                                            |  |  |

| Operation:        | k - (W) $\rightarrow$ | • (W)              |                                                                            |  |  |

| Status Affected:  | C, DC, Z              |                    |                                                                            |  |  |

| Encoding:         | 11                    | 110x               | kkkk kkk                                                                   |  |  |

| Description:      | ment meth             | od) from           | ubtracted (2's complet<br>the eight bit literal 'k<br>I in the W register. |  |  |

| Words:            | 1                     |                    |                                                                            |  |  |

| Cycles:           | 1                     |                    |                                                                            |  |  |

| Q Cycle Activity: | Q1                    | Q2                 | Q3 Q4                                                                      |  |  |

|                   | Decode                | Read<br>literal 'k | Process Write to data                                                      |  |  |

| Example 1:        | SUBLW                 | 0x02               |                                                                            |  |  |

|                   | Before In:            | structior          | ı                                                                          |  |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>?<br>?                                                                |  |  |

|                   | After Inst            | ruction            |                                                                            |  |  |

|                   |                       | W =<br>C =<br>Z =  | 1<br>1; result is positive<br>0                                            |  |  |

| Example 2:        | Before In:            | structior          | n                                                                          |  |  |

|                   |                       | W =<br>C =<br>Z =  | 2<br>?<br>?                                                                |  |  |

|                   | After Inst            | ruction            |                                                                            |  |  |

|                   |                       | W =<br>C =<br>Z =  | 0<br>1; result is zero<br>1                                                |  |  |

| Example 3:        | Before In             | structior          | ı                                                                          |  |  |

| Example 0.        |                       | W =                | 3                                                                          |  |  |

| Example 0.        |                       |                    |                                                                            |  |  |

| Example 0.        |                       | C =<br>Z =         | ?<br>?                                                                     |  |  |

|                   | After Inst            | Z =                |                                                                            |  |  |

|                   | After Inst            | Z =                |                                                                            |  |  |

|                   | After Inst            | Z =<br>ruction     | ?                                                                          |  |  |

| Appli | cable Devices | 710 71  | 711 715                                                                                                                                                                                                                                                                                                  |             |

|-------|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 11.1  | DC Character  | istics: | PIC16C710-04 (Commercial, Industrial, Extended<br>PIC16C711-04 (Commercial, Industrial, Extended<br>PIC16C710-10 (Commercial, Industrial, Extended<br>PIC16C711-10 (Commercial, Industrial, Extended<br>PIC16C710-20 (Commercial, Industrial, Extended<br>PIC16C711-20 (Commercial, Industrial, Extended | )<br>)<br>) |

| DC CHARACTERISTICS             |                                                                   |               | Operating temperature 0°C<br>-40°C |                           |                      |                      | ditions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended)                             |

|--------------------------------|-------------------------------------------------------------------|---------------|------------------------------------|---------------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min                                | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                         |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5                         | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -                                  | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                    |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -                                  | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                          |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD          | 0.05                               | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                           | Bvdd          | 3.7                                | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                 |

|                                |                                                                   |               | 3.7                                | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                           | IDD           | -                                  | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                      |

| D013                           |                                                                   |               | -                                  | 13.5                      | 30                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                                  | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD           | -<br>-<br>-<br>-                   | 10.5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 4.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -0^{\circ}C to +70^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 4.0V, WDT disabled, -40^{\circ}C to +125^{\circ}C$ |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ Ibor | -                                  | 300*                      | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDDMCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

#### 1. TppS2ppS

2. TppS

| 2. 1990 |                                       |     |              |  |

|---------|---------------------------------------|-----|--------------|--|

| Т       |                                       |     |              |  |

| F       | Frequency                             | Т   | Time         |  |

| Lowerc  | case letters (pp) and their meanings: |     |              |  |

| рр      |                                       |     |              |  |

| сс      | CCP1                                  | osc | OSC1         |  |

| ck      | CLKOUT                                | rd  | RD           |  |

| cs      | CS                                    | rw  | RD or WR     |  |

| di      | SDI                                   | sc  | SCK          |  |

| do      | SDO                                   | SS  | SS           |  |

| dt      | Data in                               | tO  | TOCKI        |  |

| io      | I/O port                              | t1  | T1CKI        |  |

| mc      | MCLR                                  | wr  | WR           |  |

| Upperc  | case letters and their meanings:      |     |              |  |

| S       |                                       |     |              |  |

| F       | Fall                                  | P   | Period       |  |

| н       | High                                  | R   | Rise         |  |

| I       | Invalid (Hi-impedance)                | V   | Valid        |  |

| L       | Low                                   | Z   | Hi-impedance |  |

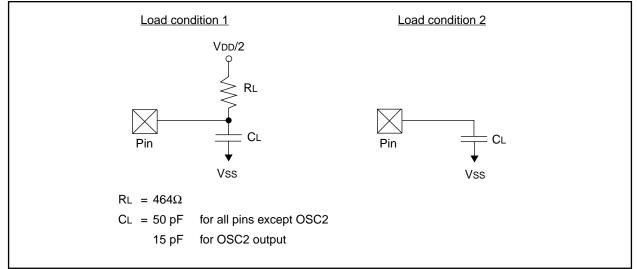

#### FIGURE 11-1: LOAD CONDITIONS

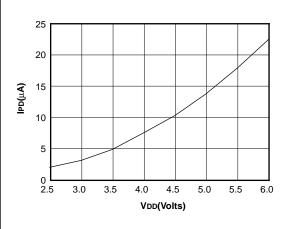

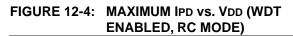

## 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

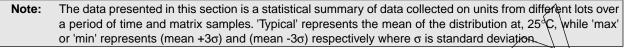

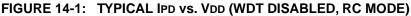

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

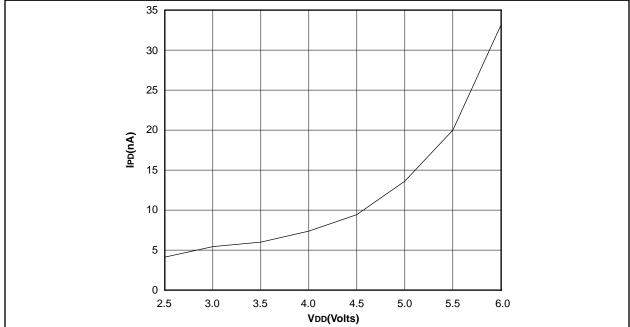

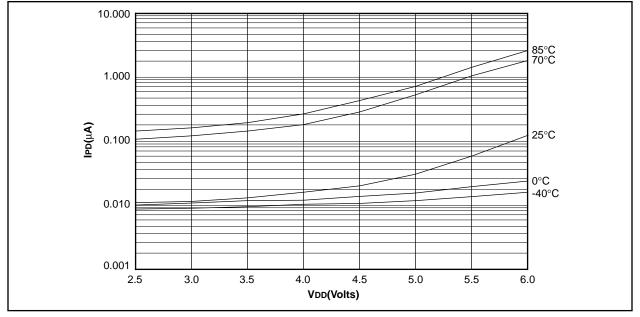

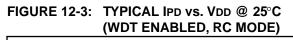

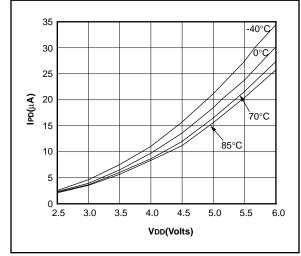

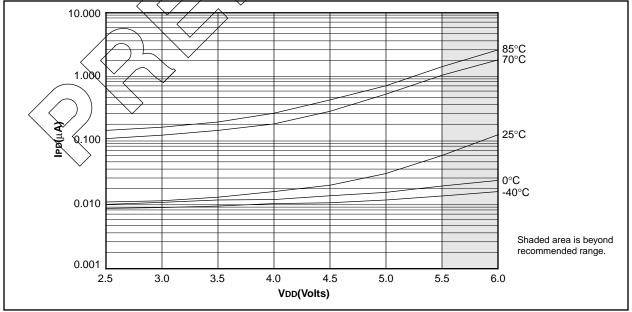

#### FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

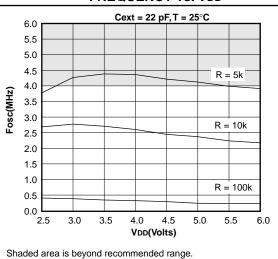

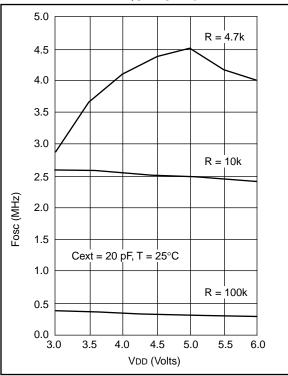

#### FIGURE 12-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

#### FIGURE 12-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

# TABLE 13-6:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C715-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C715-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C715-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Parameter<br>No. | Sym  | Characteristic                                       | Min       | Тур†       | Мах                   | Units                       | Conditions                                           |

|------------------|------|------------------------------------------------------|-----------|------------|-----------------------|-----------------------------|------------------------------------------------------|

|                  | Nr   | Resolution                                           | _         | _          | 8-bits                | _                           | $VREF=VDD,VSS\leqAin\leqVREF$                        |

|                  | Nint | Integral error                                       | _         | _          | less than<br>±1 LSb   | —                           | $VREF = VDD, VSS \le AIN \le VREF$                   |

|                  | Ndif | Differential error                                   | _         | _          | less than<br>±1 LSb   | —                           | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|                  | NFS  | Full scale error                                     | _         |            | less than<br>±1 LSb   | _                           | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|                  | Noff | Offset error                                         | _         | _          | less than<br>±1 LSb   | —                           | VREF = VDØ, VSS ≤ AIN ≤ VREF                         |

|                  | _    | Monotonicity                                         | _         | guaranteed | _                     | _                           | VSS S AIN S VREF                                     |

|                  | Vref | Reference voltage                                    | 2.5V      | _          | Vdd + 0.3             | V                           |                                                      |

|                  | VAIN | Analog input voltage                                 | Vss - 0.3 |            | Vref + 0.3            | V                           |                                                      |

|                  | ZAIN | Recommended<br>impedance of analog<br>voltage source | _         | _          | 10.0                  | kΩ                          |                                                      |

|                  | IAD  | A/D conversion cur-<br>rent (VDD)                    | _         | 180        | $\overline{\langle }$ | <u></u><br>→<br>A<br>→<br>A | Average current consumption when A/D is on. (Note 1) |

|                  | IREF | VREF input current<br>(Note 2)                       | _         |            | 1                     | μA<br>μA                    | During sampling<br>All other times                   |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

# 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

# Applicable Devices 710 71 711 715

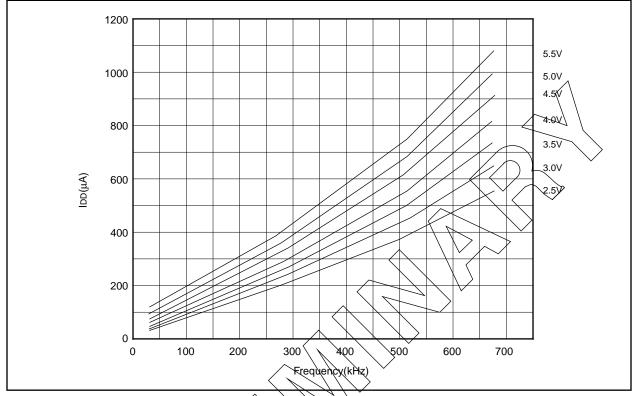

FIGURE 14-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

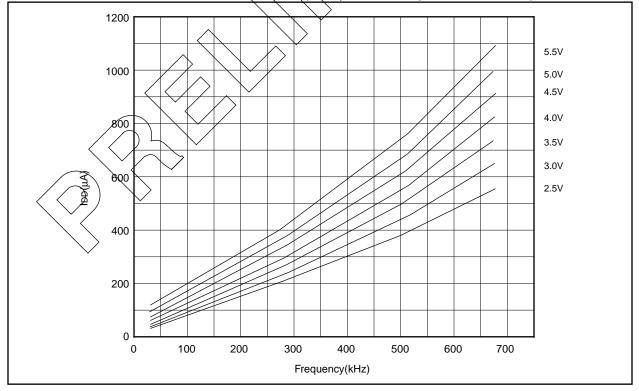

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

## 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C71

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

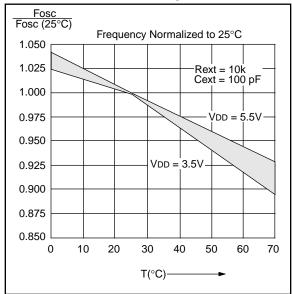

#### FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

Applicable Devices71071711715

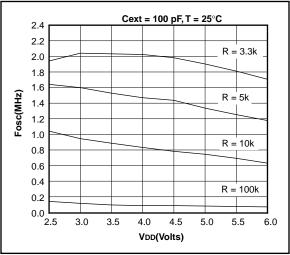

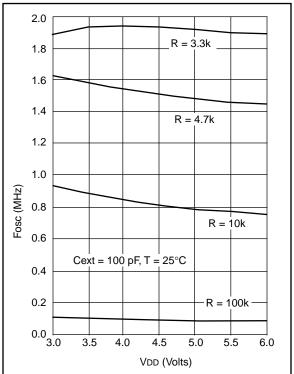

#### FIGURE 16-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

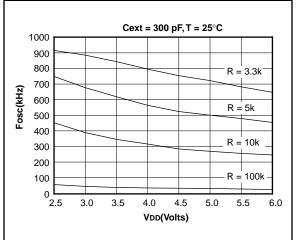

FIGURE 16-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

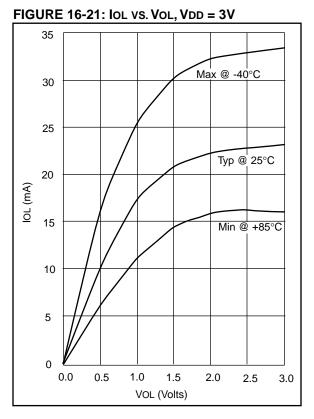

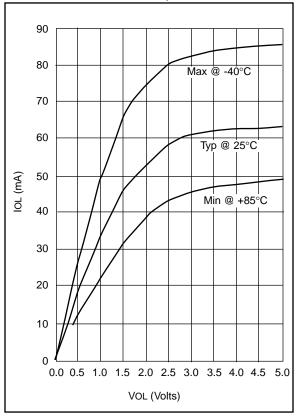

FIGURE 16-22: IOL VS. VOL, VDD = 5V

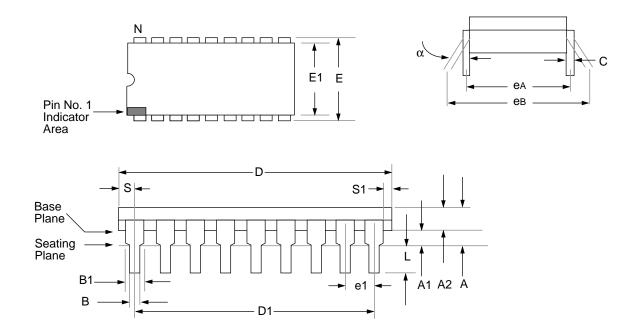

# 17.2 <u>18-Lead Plastic Dual In-line (300 mil) (P)</u>

|        | Package Group: Plastic Dual In-Line (PLA) |             |           |            |        |           |  |

|--------|-------------------------------------------|-------------|-----------|------------|--------|-----------|--|

|        |                                           | Millimeters |           |            | Inches |           |  |

| Symbol | Min                                       | Max         | Notes     | Min        | Max    | Notes     |  |

| α      | 0°                                        | 10°         |           | <b>0</b> ° | 10°    |           |  |

| А      | _                                         | 4.064       |           | _          | 0.160  |           |  |

| A1     | 0.381                                     | _           |           | 0.015      | -      |           |  |

| A2     | 3.048                                     | 3.810       |           | 0.120      | 0.150  |           |  |

| В      | 0.355                                     | 0.559       |           | 0.014      | 0.022  |           |  |

| B1     | 1.524                                     | 1.524       | Reference | 0.060      | 0.060  | Reference |  |

| С      | 0.203                                     | 0.381       | Typical   | 0.008      | 0.015  | Typical   |  |

| D      | 22.479                                    | 23.495      |           | 0.885      | 0.925  |           |  |

| D1     | 20.320                                    | 20.320      | Reference | 0.800      | 0.800  | Reference |  |

| E      | 7.620                                     | 8.255       |           | 0.300      | 0.325  |           |  |

| E1     | 6.096                                     | 7.112       |           | 0.240      | 0.280  |           |  |

| e1     | 2.489                                     | 2.591       | Typical   | 0.098      | 0.102  | Typical   |  |

| eA     | 7.620                                     | 7.620       | Reference | 0.300      | 0.300  | Reference |  |

| eB     | 7.874                                     | 9.906       |           | 0.310      | 0.390  |           |  |

| L      | 3.048                                     | 3.556       |           | 0.120      | 0.140  |           |  |

| N      | 18                                        | 18          |           | 18         | 18     |           |  |

| S      | 0.889                                     | _           |           | 0.035      | -      |           |  |

| S1     | 0.127                                     | _           |           | 0.005      | -      |           |  |

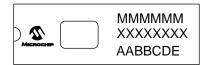

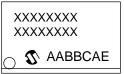

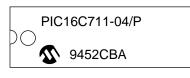

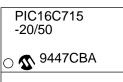

#### 17.5 Package Marking Information

18-Lead CERDIP Windowed

#### 20-Lead SSOP

Example

#### Example

#### Example

#### Example

| Legend: | MMM<br>XXX<br>AA<br>BB<br>C<br>D1<br>E | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calender year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.<br>Mask revision number for microcontroller<br>Assembly code of the plant or country of origin in which<br>part was assembled. |

|---------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | line, it will                          | ent the full Microchip part number cannot be marked on one<br>be carried over to the next line thus limiting the number of<br>characters for customer specific information.                                                                                                                                                                                                                                                 |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

| TO bit           |   |

|------------------|---|

| TOSE bit         |   |

| TRISA Register   |   |

| TRISB Register   |   |

| Two's Complement | 7 |

| U                |   |

| 0                    |   |

|----------------------|---|

| Upward Compatibility |   |

| UV Erasable Devices  | 5 |

#### W

| W Register                   |    |

|------------------------------|----|

| ĂLU                          | 7  |

| Wake-up from SLEEP           |    |

| Watchdog Timer (WDT)         |    |

| WDT                          |    |

| Block Diagram                |    |

| Programming Considerations . | 65 |

| Timeout                      |    |

| WDT Period                   |    |

| WDTE bit                     |    |

| Z                            |    |

| Z bit . |     |   |

|---------|-----|---|

| Zero b  | bit | 7 |

# LIST OF EXAMPLES

| Example 3-1:  | Instruction Pipeline Flow10         |

|---------------|-------------------------------------|

| Example 4-1:  | Call of a Subroutine in Page 1 from |

|               | Page 0 24                           |

| Example 4-2:  | Indirect Addressing 24              |

| Example 5-1:  | Initializing PORTA25                |

| Example 5-2:  | Initializing PORTB27                |

| Example 5-3:  | Read-Modify-Write Instructions      |

|               | on an I/O Port 30                   |

| Example 6-1:  | Changing Prescaler (Timer0→WDT) 35  |

| Example 6-2:  | Changing Prescaler (WDT→Timer0) 35  |

| Equation 7-1: | A/D Minimum Charging Time 40        |

| Example 7-1:  | Calculating the Minimum Required    |

|               | Aquisition Time 40                  |

| Example 7-2:  | A/D Conversion 42                   |

| Example 7-3:  | 4-bit vs. 8-bit Conversion Times 43 |

| Example 8-1:  | Saving STATUS and W Registers       |

|               | in RAM 64                           |

# LIST OF FIGURES

| Figure 3-1:  | PIC16C71X Block Diagram               | 8  |

|--------------|---------------------------------------|----|

| Figure 3-2:  | Clock/Instruction Cycle               |    |

| Figure 4-1:  | PIC16C710 Program Memory Map          |    |

|              | and Stack                             | 11 |

| Figure 4-2:  | PIC16C71/711 Program Memory Map       |    |

| -            | and Stack                             | 11 |

| Figure 4-3:  | PIC16C715 Program Memory Map          |    |

|              | and Stack                             | 11 |

| Figure 4-4:  | PIC16C710/71 Register File Map        | 12 |

| Figure 4-5:  | PIC16C711 Register File Map           | 13 |

| Figure 4-6:  | PIC16C715 Register File Map           |    |

| Figure 4-7:  | Status Register (Address 03h, 83h)    | 17 |

| Figure 4-8:  | OPTION Register (Address 81h, 181h)   | 18 |

| Figure 4-9:  | INTCON Register (Address 0Bh, 8Bh)    | 19 |

| Figure 4-10: | PIE1 Register (Address 8Ch)           | 20 |

| Figure 4-11: | PIR1 Register (Address 0Ch)           | 21 |

| Figure 4-12: | PCON Register (Address 8Eh),          |    |

|              | PIC16C710/711                         | 22 |

| Figure 4-13: | PCON Register (Address 8Eh),          |    |

|              | PIC16C715                             |    |

| Figure 4-14: | Loading of PC In Different Situations | 23 |

| Figure 4-15: | Direct/Indirect Addressing            |    |