Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 36 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc71-04-p |

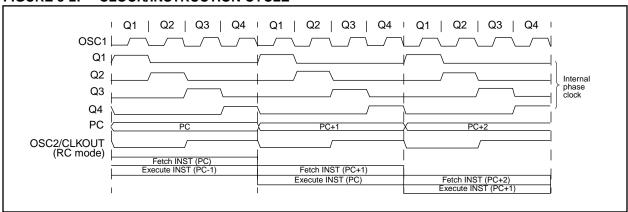

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 <u>Instruction Flow/Pipelining</u>

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

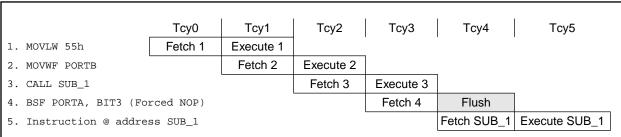

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address              | Name   | Bit 7              | Bit 6              | Bit 5        | Bit 4         | Bit 3          | Bit 2           | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR, PER | Value on all other resets (3) |

|----------------------|--------|--------------------|--------------------|--------------|---------------|----------------|-----------------|-------|-------|-------------------------------|-------------------------------|

| Bank 1               |        |                    |                    |              |               |                |                 |       |       |                               |                               |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location      | 0000 0000    | 0000 0000     |                |                 |       |       |                               |                               |

| 81h                  | OPTION | RBPU               | INTEDG             | T0CS         | T0SE          | PSA            | PS2             | PS1   | PS0   | 1111 1111                     | 1111 1111                     |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)      | Least Signif | ficant Byte   |                |                 |       |       | 0000 0000                     | 0000 0000                     |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0          | TO            | PD             | Z               | DC    | С     | 0001 1xxx                     | 000q quuu                     |

| 84h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ac        | dress pointe | er            |                |                 |       |       | xxxx xxxx                     | uuuu uuuu                     |

| 85h                  | TRISA  | _                  | _                  | PORTA Dat    | a Direction F | Register       |                 |       |       | 11 1111                       | 11 1111                       |

| 86h                  | TRISB  | PORTB Da           | ta Direction F     | Register     |               |                |                 |       |       | 1111 1111                     | 1111 1111                     |

| 87h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 88h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 89h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 8Ah <sup>(1,2)</sup> | PCLATH | _                  | _                  | _            | Write Buffe   | r for the uppe | er 5 bits of th | e PC  |       | 0 0000                        | 0 0000                        |

| 8Bh <sup>(1)</sup>   | INTCON | GIE                | PEIE               | TOIE         | INTE          | RBIE           | TOIF            | INTF  | RBIF  | 0000 000x                     | 0000 000u                     |

| 8Ch                  | PIE1   | _                  | ADIE               | _            | _             | _              | _               | _     | _     | -0                            | -0                            |

| 8Dh                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 8Eh                  | PCON   | MPEEN              | _                  | _            | _             | _              | PER             | POR   | BOR   | u1qq                          | u1uu                          |

| 8Fh                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 90h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 91h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 92h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 93h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 94h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 95h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 96h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 97h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 98h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 99h                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 9Ah                  | _      | Unimpleme          | nted               |              | _             | _              |                 |       |       |                               |                               |

| 9Bh                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 9Ch                  | _      | Unimpleme          | nted               |              | _             | _              |                 |       |       |                               |                               |

| 9Dh                  | _      | Unimplemented      |                    |              |               |                |                 |       |       |                               | _                             |

| 9Eh                  | _      | Unimpleme          | nted               |              |               |                |                 |       |       | _                             | _                             |

| 9Fh                  | ADCON1 | _                  | _                  | _            | _             | _              | _               | PCFG1 | PCFG0 | 00                            | 00                            |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

#### 4.2.2.2 OPTION REGISTER

710 71 711 715 Applicable Devices

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

#### FIGURE 4-8: **OPTION REGISTER (ADDRESS 81h, 181h)**

| R/   | W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------|-----|--------|-------|-------|-------|-------|-------|-------|

| RE   | 3PU | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit7 |     |        |       |       |       |       |       | bit0  |

= Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

- bit 7: RBPU: PORTB Pull-up Enable bit

- 1 = PORTB pull-ups are disabled

- 0 = PORTB pull-ups are enabled by individual port latch values

- INTEDG: Interrupt Edge Select bit bit 6:

- 1 = Interrupt on rising edge of RB0/INT pin

- 0 = Interrupt on falling edge of RB0/INT pin

- bit 5: T0CS: TMR0 Clock Source Select bit

- 1 = Transition on RA4/T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- T0SE: TMR0 Source Edge Select bit bit 4:

- 1 = Increment on high-to-low transition on RA4/T0CKI pin

- 0 = Increment on low-to-high transition on RA4/T0CKI pin

- bit 3: PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0: PS2:PS0: Prescaler Rate Select bits

| Bit Value                              | TMR0 Rate                                 | WDT Rate                         |

|----------------------------------------|-------------------------------------------|----------------------------------|

| 000<br>001<br>010<br>011<br>100<br>101 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16 |

| 110<br>111                             | 1 : 128<br>1 : 256                        | 1 : 64<br>1 : 128                |

TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |  |

|--------------|------|--------|-------------------------------------------------|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                    |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                    |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                    |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |  |

|              |      |        | Output is open drain type                       |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | _     | _     | _     | RA4                           | RA3   | RA2   | RA1   | RA0   | x 0000                   | u 0000                    |

| 85h     | TRISA  | _     | _     | _     | PORTA Data Direction Register |       |       |       |       | 1 1111                   | 1 1111                    |

| 9Fh     | ADCON1 | _     | _     | _     | _                             | _     | _     | PCFG1 | PCFG0 | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### 7.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- · Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of:

2.0 us for the PIC16C71

1.6 µs for all other PIC16C71X devices

Table 7-1 and Table 7-2 and show the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 7.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

Note 2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES, PIC16C71

| AD Cloc           | k Source (TAD) | Device Frequency          |                           |                           |                         |                         |  |  |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|-------------------------|-------------------------|--|--|

| Operation         | ADCS1:ADCS0    | 20 MHz                    | 16 MHz                    | 4 MHz                     | 1 MHz                   | 333.33 kHz              |  |  |

| 2Tosc             | 00             | 100 ns <sup>(2)</sup>     | 125 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 2.0 μs                  | 6 μs                    |  |  |

| 8Tosc             | 01             | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 2.0 μs                    | 8.0 μs                  | 24 μs <sup>(3)</sup>    |  |  |

| 32Tosc            | 10             | 1.6 μs <sup>(2)</sup>     | 2.0 μs                    | 8.0 μs                    | 32.0 μs <sup>(3)</sup>  | 96 μs <sup>(3)</sup>    |  |  |

| RC <sup>(5)</sup> | 11             | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The RC source has a typical TAD time of 4 μs.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

TABLE 7-2: TAD vs. DEVICE OPERATING FREQUENCIES, PIC16C710/711, PIC16C715

| AD Clock          | Source (TAD) | Device Frequency          |                           |                           |                         |  |  |

|-------------------|--------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|

| Operation         | ADCS1:ADCS0  | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |

| 2Tosc             | 00           | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |

| 8Tosc             | 01           | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |

| 32Tosc            | 10           | 1.6 µs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |

| RC <sup>(5)</sup> | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The RC source has a typical TAD time of 4 µs.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

TABLE 8-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C71

| TO | PD |                                                         |

|----|----|---------------------------------------------------------|

| 1  | 1  | Power-on Reset                                          |

| 0  | x  | Illegal, TO is set on POR                               |

| х  | 0  | Illegal, PD is set on POR                               |

| 0  | 1  | WDT Reset                                               |

| 0  | 0  | WDT Wake-up                                             |

| u  | u  | MCLR Reset during normal operation                      |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 8-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C710/711

| POR | BOR | TO | PD |                                                         |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | х   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | х   | 0  | х  | legal, TO is set on POR                                 |  |  |  |

| 0   | х   | х  | 0  | egal, PD is set on POR                                  |  |  |  |

| 1   | 0   | х  | х  | Brown-out Reset                                         |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | ICLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

#### TABLE 8-9: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C715

| PER | POR | BOR | TO | PD |                                                         |

|-----|-----|-----|----|----|---------------------------------------------------------|

| 1   | 0   | х   | 1  | 1  | Power-on Reset                                          |

| х   | 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| х   | 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 1   | 0   | x  | х  | Brown-out Reset                                         |

| 1   | 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

| 0   | 1   | 1   | 1  | 1  | Parity Error Reset                                      |

| 0   | 0   | х   | x  | х  | Illegal, PER is set on POR                              |

| 0   | х   | 0   | х  | х  | Illegal, PER is set on BOR                              |

TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000q quuu <sup>(3)</sup> | uuuq quuu(3)                       |

| FSR                 | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu(1)                       |

| ADRES               | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | uuuu uuuu                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | uuuu uuuu                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       | uu                                 |

| ADCON1              | 00                                                | 00                       | uu                                 |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

- 3: See Table 8-10 for reset value for specific condition.

- 4: The PCON register is not implemented on the PIC16C71.

- 5: Brown-out reset is not implemented on the PIC16C71.

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

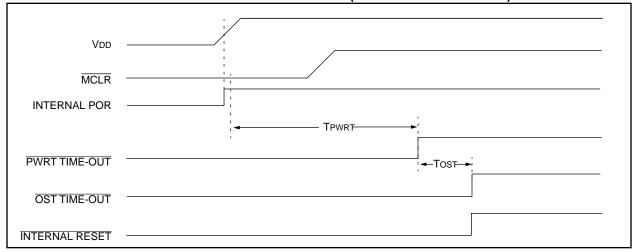

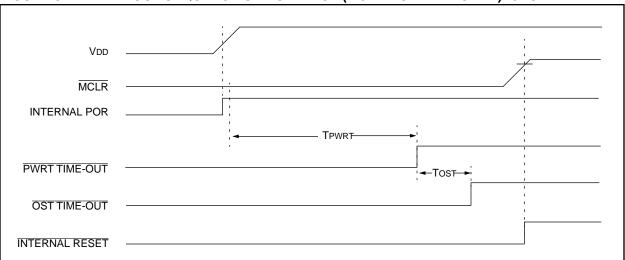

FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

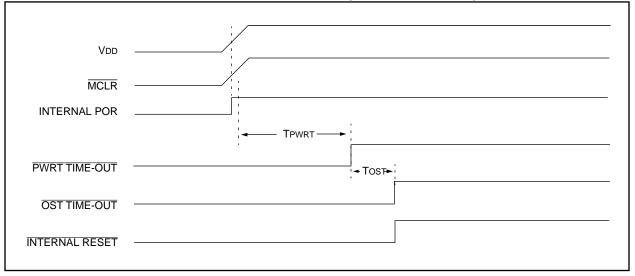

FIGURE 8-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 8-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

DC CHARACTERISTICS

### Applicable Devices 710 71 711 715

11.1 DC Characteristics: PIC16C710-04 (Commercial, Industrial, Extended)

PIC16C711-04 (Commercial, Industrial, Extended)

PIC16C710-10 (Commercial, Industrial, Extended)

PIC16C711-10 (Commercial, Industrial, Extended)

PIC16C710-20 (Commercial, Industrial, Extended) PIC16C711-20 (Commercial, Industrial, Extended)

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +85 $^{\circ}$ C (industrial) -40 $^{\circ}$ C  $\leq$  TA  $\leq$  +125 $^{\circ}$ C (extended)

|                                |                                                            |       |             |                           |                      | -                    | -40°C ≤ TA ≤ +125°C (extended)                                                                                                                                     |

|--------------------------------|------------------------------------------------------------|-------|-------------|---------------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                             | Sym   | Min         | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                         |

| D001<br>D001A                  | Supply Voltage                                             | VDD   | 4.0<br>4.5  | -                         | 6.0<br>5.5           | > >                  | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                     | VDR   | -           | 1.5                       | -                    | <b>V</b>             |                                                                                                                                                                    |

| D003                           | VDD start voltage to ensure internal Power-on Reset signal | VPOR  | -           | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                          |

| D004*                          | VDD rise rate to ensure internal Power-on Reset signal     | SVDD  | 0.05        | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                    | Bvdd  | 3.7         | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                 |

|                                |                                                            |       | 3.7         | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                    | IDD   | -           | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                                                                      |

| D013                           |                                                            |       | -           | 13.5                      | 30                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                  |

| D015                           | Brown-out Reset Current (Note 5)                           | Δlbor | -           | 300*                      | 500                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

| D020<br>D021<br>D021A<br>D021B | Power-down Current (Note 3)                                | IPD   | -<br>-<br>- | 10.5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D023                           | Brown-out Reset Current (Note 5)                           | ΔIBOR | -           | 300*                      | 500                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}$ C  $\leq TA \leq +70^{\circ}$ C (commercial)

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +85 $^{\circ}$ C (industrial)

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +125 $^{\circ}$ C (extended)

Operating voltage VDD range as described in DC spec Section 11.1 and

Section 11.2.

| Param | Characteristic                             | Sym               | Min       | Тур | Max | Units | Conditions                                                                                      |

|-------|--------------------------------------------|-------------------|-----------|-----|-----|-------|-------------------------------------------------------------------------------------------------|

| No.   |                                            |                   |           | †   |     |       |                                                                                                 |

|       | Output Low Voltage                         |                   |           |     |     |       |                                                                                                 |

| D080  | I/O ports                                  | Vol               | -         | -   | 0.6 | V     | IOL = $8.5 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$  |

| D080A |                                            |                   | -         | -   | 0.6 | V     | IOL = $7.0 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ |

| D083  | OSC2/CLKOUT (RC osc config)                |                   | -         | -   | 0.6 | V     | IOL = 1.6 mA, $VDD = 4.5V$ , $-40^{\circ}C$ to $+85^{\circ}C$                                   |

| D083A |                                            |                   | -         | -   | 0.6 | V     | IOL = 1.2 mA, $VDD = 4.5V$ , $-40^{\circ}C$ to $+125^{\circ}C$                                  |

|       | Output High Voltage                        |                   |           |     |     |       |                                                                                                 |

| D090  | I/O ports (Note 3)                         | Vон               | VDD - 0.7 | -   | -   | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                            |

| D090A |                                            |                   | VDD - 0.7 | -   | -   | V     | IOH = $-2.5$ mA, VDD = $4.5$ V, $-40$ °C to $+125$ °C                                           |

| D092  | OSC2/CLKOUT (RC osc config)                |                   | VDD - 0.7 | -   | -   | V     | IOH = -1.3 mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C                                              |

| D092A |                                            |                   | VDD - 0.7 | -   | -   | V     | IOH = $-1.0$ mA, VDD = $4.5$ V, $-40$ °C to $+125$ °C                                           |

| D130* | Open-Drain High Voltage                    | Vod               | -         | -   | 14  | V     | RA4 pin                                                                                         |

|       | Capacitive Loading Specs on<br>Output Pins |                   |           |     |     |       |                                                                                                 |

| D100  | OSC2 pin                                   | Cosc <sub>2</sub> | -         | -   | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1.                               |

| D101  | All I/O pins and OSC2 (in RC mode)         | Cio               | -         | -   | 50  | pF    |                                                                                                 |

<sup>\*</sup> These parameters are characterized but not tested.

DC CHARACTERISTICS

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

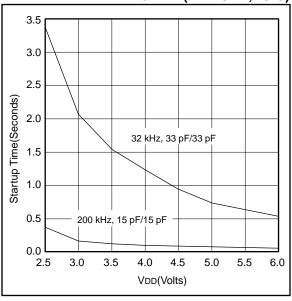

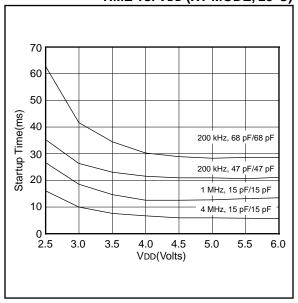

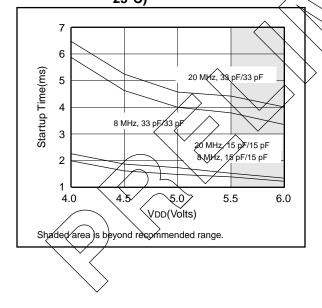

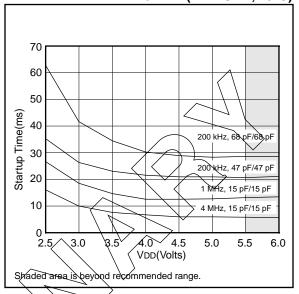

FIGURE 12-22: TYPICAL XTAL STARTUP

TIME vs. Vdd (LP MODE, 25°C)

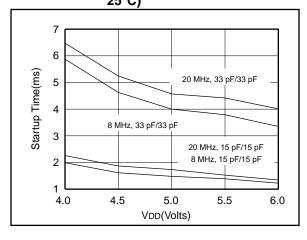

FIGURE 12-23: TYPICAL XTAL STARTUP TIME vs. VdD (HS MODE,  $25^{\circ}$ C)

FIGURE 12-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1      | Cap. Range<br>C2 |  |

|------------------|-----------------|-----------------------|------------------|--|

| LP               | 32 kHz          | 33 pF                 | 33 pF            |  |

|                  | 200 kHz         | 15 pF                 | 15 pF            |  |

| XT               | 200 kHz         | 47-68 pF              | 47-68 pF         |  |

|                  | 1 MHz           | 15 pF                 | 15 pF            |  |

|                  | 4 MHz           | 15 pF                 | 15 pF            |  |

| HS               | 4 MHz           | 15 pF                 | 15 pF            |  |

|                  | 8 MHz           | 15-33 pF              | 15-33 pF         |  |

|                  | 20 MHz          | 15-33 pF              | 15-33 pF         |  |

|                  | •               |                       |                  |  |

| Crystals<br>Used |                 |                       |                  |  |

| 32 kHz           | Epson C-0       | ± 20 PPM              |                  |  |

| 200 kHz          | STD XTL 2       | ± 20 PPM              |                  |  |

| 1 MHz            | ECS ECS-        | ± 50 PPM              |                  |  |

| 4 MHz            | ECS ECS-        | ECS ECS-40-20-1       |                  |  |

| 8 MHz            | EPSON CA        | EPSON CA-301 8.000M-C |                  |  |

| 20 MHz           | EPSON CA        | ± 30 PPM              |                  |  |

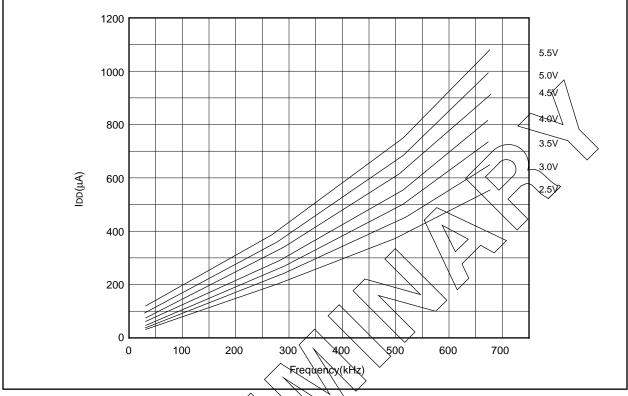

FIGURE 14-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

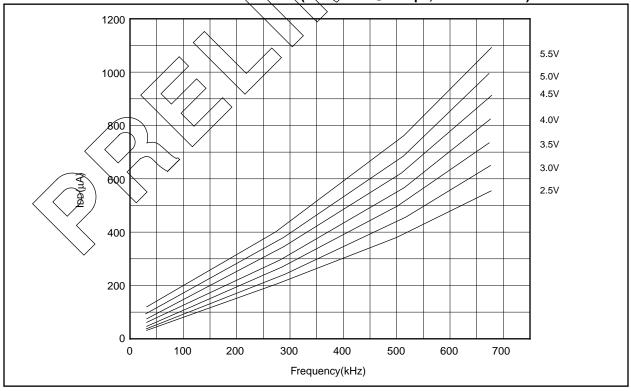

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

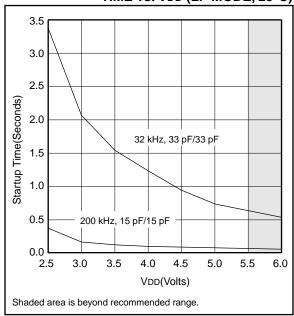

FIGURE 14-22: TYPICAL XTAL STARTUP

TIME vs. Vdd (LP MODE, 25°C)

FIGURE 14-23: TYPICAL XTAL STARTUP TIME vs. Vdd (HS MODE,  $25^{\circ}\text{C}$ )

FIGURE 14-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

TABLE 14-2: CAPACITOR SELECTION

FOR CRYSTAL

OSCILLATORS

| $\rightarrow$    |                 |                       |                  |  |

|------------------|-----------------|-----------------------|------------------|--|

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1      | Cap. Range<br>C2 |  |

| LP               | 32 kHz          | 33 pF                 | 33 pF            |  |

|                  | 200 kHz         | 15 pF                 | 15 pF            |  |

| XT               | 200 kHz         | 47-68 pF              | 47-68 pF         |  |

|                  | 1 MHz           | 15 pF                 | 15 pF            |  |

|                  | 4 MHz           | 15 pF                 | 15 pF            |  |

| HS               | 4 MHz           | 15 pF                 | 15 pF            |  |

|                  | 8 MHz           | 15-33 pF              | 15-33 pF         |  |

|                  | 20 MHz          | 15-33 pF              | 15-33 pF         |  |

|                  | •               |                       |                  |  |

| Crystals<br>Used |                 |                       |                  |  |

| 32 kHz           | Epson C-00      | ± 20 PPM              |                  |  |

| 200 kHz          | STD XTL 2       | ± 20 PPM              |                  |  |

| 1 MHz            | ECS ECS-        | ± 50 PPM              |                  |  |

| 4 MHz            | ECS ECS-4       | ± 50 PPM              |                  |  |

| 8 MHz            | EPSON CA        | EPSON CA-301 8.000M-C |                  |  |

| 20 MHz           | EPSON CA        | ± 30 PPM              |                  |  |

|                  |                 |                       |                  |  |

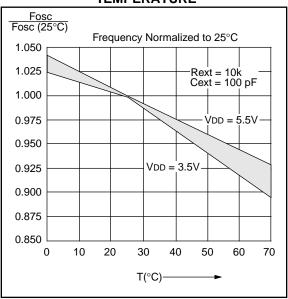

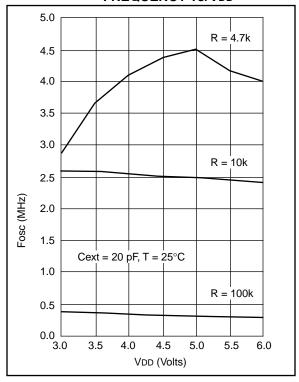

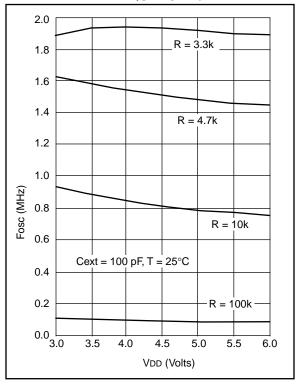

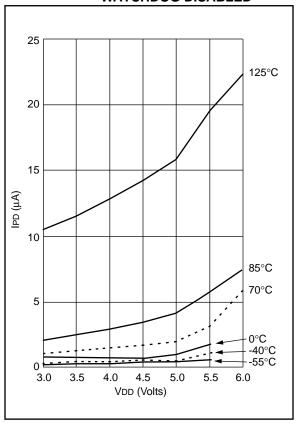

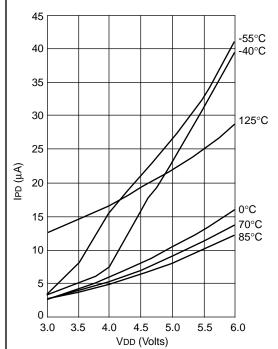

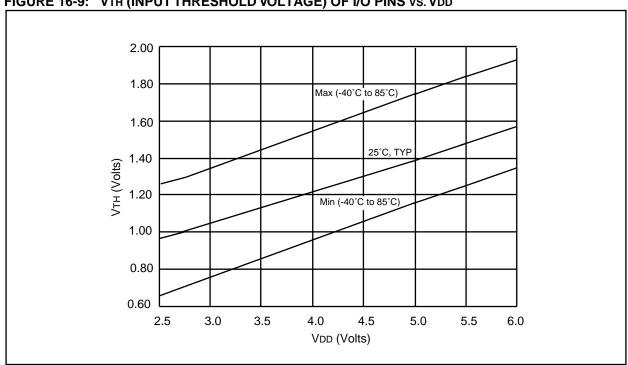

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C71

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

Note: The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs.

TEMPERATURE

### FIGURE 16-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

FIGURE 16-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

FIGURE 16-7: MAXIMUM IPD VS. VDD WATCHDOG DISABLED

FIGURE 16-8: MAXIMUM IPD VS. VDD **WATCHDOG ENABLED**

IPD, with Watchdog Timer enabled, has two components: The leakage current which increases with higher temperature and the operating current of the Watchdog Timer logic which increases with lower temperature. At -40°C, the latter dominates explaining the apparently anomalous behavior.

FIGURE 16-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

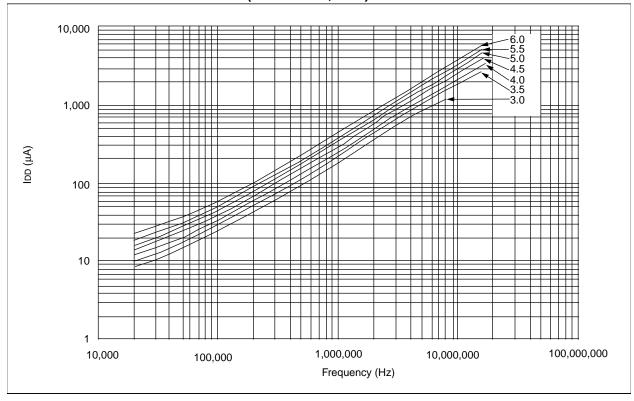

FIGURE 16-12: TYPICAL IDD Vs. FREQ (EXT CLOCK, 25°C)

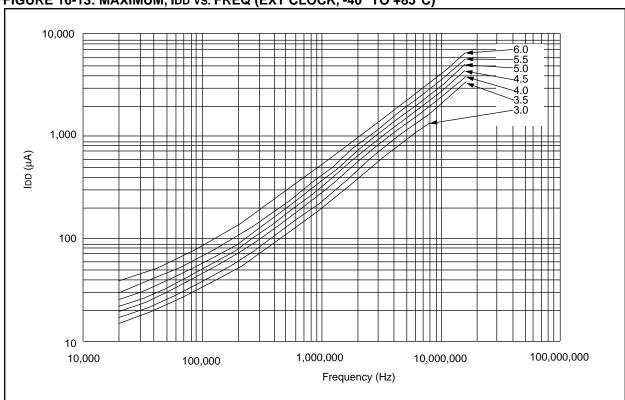

FIGURE 16-13: MAXIMUM, IDD VS. FREQ (EXT CLOCK, -40° TO +85°C)

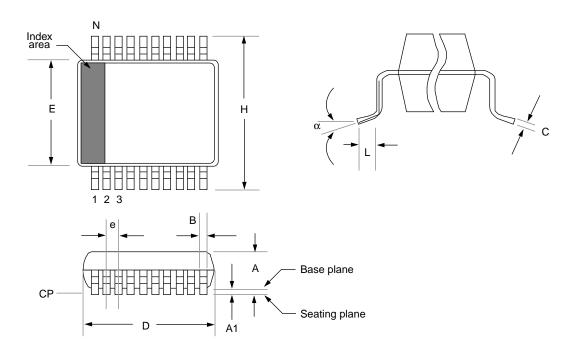

#### 17.4 20-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

|        | Package Group: Plastic SSOP |       |           |       |        |           |  |  |

|--------|-----------------------------|-------|-----------|-------|--------|-----------|--|--|

|        | Millimeters                 |       |           |       | Inches |           |  |  |

| Symbol | Min                         | Max   | Notes     | Min   | Max    | Notes     |  |  |

| α      | 0°                          | 8°    |           | 0°    | 8°     |           |  |  |

| Α      | 1.730                       | 1.990 |           | 0.068 | 0.078  |           |  |  |

| A1     | 0.050                       | 0.210 |           | 0.002 | 0.008  |           |  |  |

| В      | 0.250                       | 0.380 |           | 0.010 | 0.015  |           |  |  |

| С      | 0.130                       | 0.220 |           | 0.005 | 0.009  |           |  |  |

| D      | 7.070                       | 7.330 |           | 0.278 | 0.289  |           |  |  |

| E      | 5.200                       | 5.380 |           | 0.205 | 0.212  |           |  |  |

| е      | 0.650                       | 0.650 | Reference | 0.026 | 0.026  | Reference |  |  |

| Н      | 7.650                       | 7.900 |           | 0.301 | 0.311  |           |  |  |

| L      | 0.550                       | 0.950 |           | 0.022 | 0.037  |           |  |  |

| N      | 20                          | 20    |           | 20    | 20     |           |  |  |

| СР     | -                           | 0.102 |           | -     | 0.004  |           |  |  |

- Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

- 2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

- 3: This outline conforms to JEDEC MS-026.

#### **APPENDIX C: WHAT'S NEW**

Consolidated all pin compatible 18-pin A/D based devices into one data sheet.

#### **APPENDIX D: WHAT'S CHANGED**

- Minor changes, spelling and grammatical changes.

- 2. Low voltage operation on the PIC16LC710/711/715 has been reduced from 3.0V to 2.5V.

- 3. Part numbers of the PIC16C70 and PIC16C71A have changed to PIC16C710 and PIC16C711, respectively.

| 1                                             |        | TMR0 Overflow                                         | 61                 |

|-----------------------------------------------|--------|-------------------------------------------------------|--------------------|

| I/O Ports                                     |        | INTF bit                                              | 19                 |

| PORTA                                         | 25     | IRP bit                                               | 17                 |

| PORTB                                         | _      | 17                                                    |                    |

| Section                                       |        | K                                                     |                    |

|                                               |        | KeeLoq® Evaluation and Programming Tools              | 87                 |

| I/O Programming Considerations                |        |                                                       |                    |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator |        | L                                                     |                    |

| In-Circuit Serial Programming                 |        | Loading of PC                                         | 23                 |

| INDF Register14                               |        | LP                                                    | 54                 |

| Indirect Addressing                           |        |                                                       |                    |

| Instruction Cycle                             |        | M                                                     |                    |

| Instruction Flow/Pipelining                   |        | MCLR                                                  | 52, 56             |

| Instruction Format                            | 69     | Memory                                                |                    |

| Instruction Set                               |        | Data Memory                                           | 12                 |

| ADDLW                                         | 71     | Program Memory                                        |                    |

| ADDWF                                         | 71     | Register File Maps                                    |                    |

| ANDLW                                         | 71     | PIC16C71                                              | 12                 |

| ANDWF                                         | 71     | PIC16C710                                             |                    |

| BCF                                           | 72     | PIC16C711                                             |                    |

| BSF                                           | 72     |                                                       |                    |

| BTFSC                                         |        | PIC16C715                                             |                    |

| BTFSS                                         |        | MP-DriveWay <sup>™</sup> - Application Code Generator |                    |

| CALL                                          | _      | MPEEN bit                                             |                    |

| CLRF                                          | _      | MPLAB™ C                                              | 87                 |

| CLRW                                          |        | MPLAB™ Integrated Development Environment             |                    |

|                                               |        | Software                                              | 86                 |

| CLRWDT                                        |        | 0                                                     |                    |

| COMF                                          |        | O                                                     |                    |

| DECF                                          | _      | OPCODE                                                |                    |

| DECFSZ                                        | -      | OPTION Register                                       | 18                 |

| GOTO                                          |        | Orthogonal                                            | 7                  |

| INCF                                          | 76     | OSC selection                                         | 47                 |

| INCFSZ                                        | 77     | Oscillator                                            |                    |

| IORLW                                         | 77     | HS                                                    | 49. 54             |

| IORWF                                         | 78     | LP                                                    | 49 <sup>°</sup> 54 |

| MOVF                                          | 78     | RC                                                    | 49                 |

| MOVLW                                         | 78     | XT4                                                   | 49.54              |

| MOVWF                                         | 78     | Oscillator Configurations                             | ,                  |

| NOP                                           | 79     | Oscillator Start-up Timer (OST)                       |                    |

| OPTION                                        | 79     |                                                       |                    |

| RETFIE                                        | 79     | P                                                     |                    |

| RETLW                                         | 80     | Packaging                                             |                    |

| RETURN                                        | 80     | 18-Lead CERDIP w/Window                               | 155                |

| RLF                                           | 81     | 18-Lead PDIP                                          |                    |

| RRF                                           | -      | 18-Lead SOIC                                          |                    |

| SLEEP                                         | 00     | 20-Lead SSOP                                          |                    |

| SUBLW                                         | 82     | Paging, Program Memory                                |                    |

| SUBWF                                         |        | PCL Register14, 15,                                   |                    |

| SWAPF                                         |        |                                                       |                    |

| TRIS                                          |        | PCLATH                                                |                    |

|                                               |        | PCLATH Register 14, 15, 7                             | -                  |

| XORLW                                         |        | PCON Register                                         | -                  |

| XORWF                                         |        | PD bit 17, 5                                          | ,                  |

| Section                                       |        | PER bit                                               |                    |

| Summary Table                                 |        | PIC16C71                                              |                    |

| INT Interrupt                                 |        | AC Characteristics                                    |                    |

| INTCON Register                               |        | PICDEM-1 Low-Cost PIC16/17 Demo Board                 | 86                 |

| INTE bit                                      | 19     | PICDEM-2 Low-Cost PIC16CXX Demo Board                 | 86                 |

| INTEDG bit                                    | 18, 63 | PICDEM-3 Low-Cost PIC16CXXX Demo Board                | 86                 |

| Internal Sampling Switch (Rss) Impedence      | 40     | PICMASTER® In-Circuit Emulator                        | 85                 |

| Interrupts                                    | 47     | PICSTART® Plus Entry Level Development System         | 85                 |

| A/D                                           | 61     | PIE1 Register                                         |                    |

| External                                      | 61     | Pin Functions                                         |                    |

| PORTB Change                                  | 61     | MCLR/VPP                                              | <u> </u>           |

| PortB Change                                  |        | OSC1/CLKIN                                            |                    |

| RB7:RB4 Port Change                           |        | OSC2/CLKOUT                                           |                    |

| Section                                       |        | RAO/ANO                                               |                    |

| TMR0                                          |        | RA1/AN1                                               |                    |

|                                               | 50     | TM 11/1 W 1 1                                         |                    |

**NOTES:**