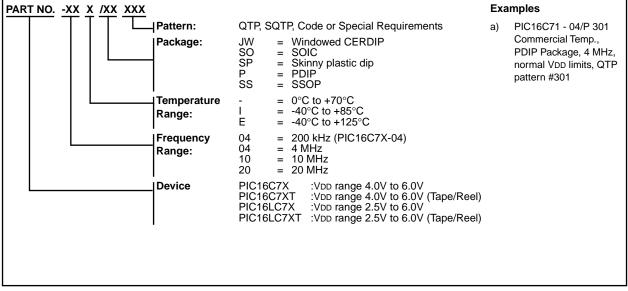

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 36 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc71-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.1 STATUS REGISTER

#### Applicable Devices 710 71 711 715

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| <u>R/W-0</u> | R/W-0                                                                                                                                                                       | R/W-0<br>RP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>R-1</u><br>TO | <u>R-1</u><br>PD | R/W-x<br>Z | R/W-x<br>DC | R/W-x<br>C | R = Readable bit |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------|-------------|------------|------------------|--|--|--|

| IRP<br>bit7  | RP1                                                                                                                                                                         | bit0<br>bit0<br>bit0<br>w = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                  |            |             |            |                  |  |  |  |

| bit 7:       | 1 = Bank                                                                                                                                                                    | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |            |             |            |                  |  |  |  |

| bit 6-5:     | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank                                                                                                                            | <b>RP1:RP0:</b> Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |            |             |            |                  |  |  |  |

| bit 4:       | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                  |            |             |            |                  |  |  |  |

| bit 3:       | <ul> <li>PD: Power-down bit</li> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                  |            |             |            |                  |  |  |  |

| bit 2:       | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                  |            |             |            |                  |  |  |  |

| bit 1:       | 1 = A carr                                                                                                                                                                  | <b>DC:</b> Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |            |             |            |                  |  |  |  |

| bit 0:       | 1 = A carr<br>0 = No ca<br>Note: For                                                                                                                                        | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>D = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the most significant bit of the result occurred</li> <li>D = No carry-out from the most significant bit of the result occurred</li> <li>No carry-out from the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order</li> </ul> |                  |                  |            |             |            |                  |  |  |  |

#### FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h)

#### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |  |

|--------------|------|--------|-------------------------------------------------|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                    |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                    |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                    |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |  |

|              |      |        | Output is open drain type                       |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|--------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | —     | _     | RA4                           | RA3   | RA2   | RA1   | RA0    | x 0000                   | u 0000                    |

| 85h     | TRISA  | —     | —     | _     | PORTA Data Direction Register |       |       |       | 1 1111 | 1 1111                   |                           |

| 9Fh     | ADCON1 | _     | _     | _     | _                             | _     |       | PCFG1 | PCFG0  | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

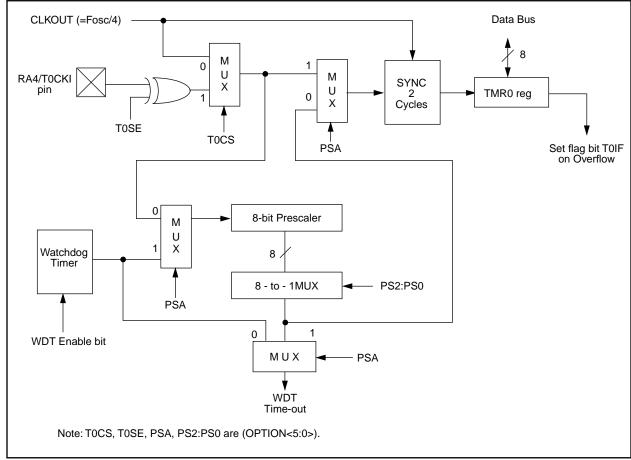

#### 6.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Applicable Devices 710 71 711 715

The analog-to-digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 7-1 and Figure 7-2, controls the operation of the A/D module. The ADCON1 register, shown in Figure 7-3 configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0<br>ADCS1 | R/W-0<br>ADCS0                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0<br>CHS1 | R/W-0<br>CHS0 | R/W-0<br>GO/DONE | R/W-0<br>ADIF | R/W-0<br>ADON | R = Readable bit |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------------------|---------------|---------------|------------------|--|--|--|

| bit7           | ADCSU                                                                                                                                                                                                                         | bito<br>bito<br>bito<br>bito<br>chsi chsi chsi concert<br>bito<br>bito<br>chsi chsi chsi concert<br>bito<br>chsi chsi chsi chsi chsi chi<br>chsi chsi chsi chsi chi<br>chsi chsi chsi chsi chi<br>chsi chi<br>chsi chsi chi<br>chsi chi<br>chi<br>chsi chi<br>chsi chi<br>chi<br>chsi chi<br>chi<br>chsi chi<br>chsi chi<br>chi<br>chi<br>chi<br>chi<br>chi<br>chi<br>chi |               |               |                  |               |               |                  |  |  |  |

| bit 7-6:       | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an RC oscillation)                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

| bit 5:         | Unimple                                                                                                                                                                                                                       | <b>nented:</b> Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ad as '0'.    |               |                  |               |               |                  |  |  |  |

| bit 4-3:       | CHS1:CHS0: Analog Channel Select bits<br>00 = channel 0, (RA0/AN0)<br>01 = channel 1, (RA1/AN1)<br>10 = channel 2, (RA2/AN2)<br>11 = channel 3, (RA3/AN3)                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

| bit 2:         | GO/DONE: A/D Conversion Status bit                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

|                | <u>If ADON = 1</u> :<br>1 = A/D conversion in progress (setting this bit starts the A/D conversion)<br>0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

|                | ADIF: A/D Conversion Complete Interrupt Flag bit<br>1 = conversion is complete (must be cleared in software)<br>0 = conversion is not complete                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

|                | ADON: A/D On bit<br>1 = A/D converter module is operating                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |                  |               |               |                  |  |  |  |

| Note 1:        |                                                                                                                                                                                                                               | 0 = A/D converter module is shutoff and consumes no operating current<br>Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is<br>unimplemented, read as '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |               |                  |               |               |                  |  |  |  |

#### FIGURE 7-1: ADCON0 REGISTER (ADDRESS 08h), PIC16C710/71/711

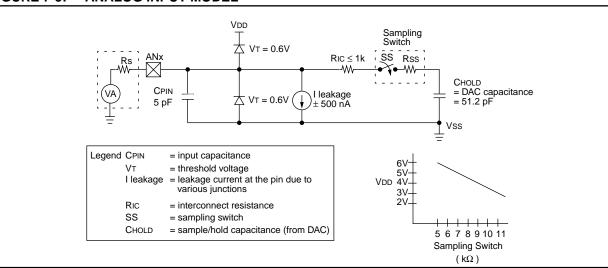

#### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

#### EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

#### FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

# TABLE 8-3:CERAMIC RESONATORS,<br/>PIC16C710/711/715

| Ranges Tested:                                                          |                                                                                                        |                                         |                                         |  |  |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode                                                                    | Freq OSC1 OSC2                                                                                         |                                         |                                         |  |  |  |

| XT                                                                      | 455 kHz<br>2.0 MHz<br>4.0 MHz                                                                          | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                                                      | 8.0 MHz         10 - 68 pF         10 - 68 pF           16.0 MHz         10 - 22 pF         10 - 22 pF |                                         |                                         |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                                                                                        |                                         |                                         |  |  |  |

| Resonator                                                               | Resonators Used:                                                                                       |                                         |                                         |  |  |  |

| 455 kHz                                                                 | Panasonic E                                                                                            | FO-A455K04B                             | ± 0.3%                                  |  |  |  |

| 2.0 MHz                                                                 | Murata Erie (                                                                                          | CSA2.00MG                               | ± 0.5%                                  |  |  |  |

| 4.0 MHz                                                                 | Murata Erie (                                                                                          | CSA4.00MG                               | ± 0.5%                                  |  |  |  |

| 8.0 MHz                                                                 | Murata Erie CSA8.00MT ± 0.5%                                                                           |                                         |                                         |  |  |  |

| 16.0 MHz                                                                | Murata Erie (                                                                                          | CSA16.00MX                              | ± 0.5%                                  |  |  |  |

| All reso                                                                | onators used did                                                                                       | d not have built-in                     | capacitors.                             |  |  |  |

# TABLE 8-4:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR,<br/>PIC16C710/711/715

| Osc Type                                      | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |

|-----------------------------------------------|-----------------|------------------|------------------|--|--|--|--|

| LP                                            | 32 kHz          | 33 pF            | 33 pF            |  |  |  |  |

|                                               | 200 kHz         | 15 pF            | 15 pF            |  |  |  |  |

| XT                                            | 200 kHz         | 47-68 pF         | 47-68 pF         |  |  |  |  |

|                                               | 1 MHz           | 15 pF            | 15 pF            |  |  |  |  |

|                                               | 4 MHz           | 15 pF            | 15 pF            |  |  |  |  |

| HS                                            | 4 MHz           | 15 pF            | 15 pF            |  |  |  |  |

|                                               | 8 MHz           | 15-33 pF         | 15-33 pF         |  |  |  |  |

|                                               | 20 MHz          | 15-33 pF         | 15-33 pF         |  |  |  |  |

| These values are far design guidenes only See |                 |                  |                  |  |  |  |  |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |              |  |  |  |  |

|---------------|------------------------|--------------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM     |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM     |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | $\pm$ 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM     |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM     |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM     |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested table.

2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

| TABLE 8-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C7 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| TO | PD |                                                         |

|----|----|---------------------------------------------------------|

| 1  | 1  | Power-on Reset                                          |

| 0  | x  | Illegal, TO is set on POR                               |

| x  | 0  | Illegal, PD is set on POR                               |

| 0  | 1  | WDT Reset                                               |

| 0  | 0  | WDT Wake-up                                             |

| u  | u  | MCLR Reset during normal operation                      |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 8-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C710/711

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | х  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 8-9: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C715

| PER | POR | BOR | TO | PD |                                                         |

|-----|-----|-----|----|----|---------------------------------------------------------|

| 1   | 0   | х   | 1  | 1  | Power-on Reset                                          |

| x   | 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| x   | 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

| 0   | 1   | 1   | 1  | 1  | Parity Error Reset                                      |

| 0   | 0   | x   | x  | x  | Illegal, PER is set on POR                              |

| 0   | x   | 0   | x  | x  | Illegal, PER is set on BOR                              |

#### TABLE 8-10: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C710/71/711

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C710/711 |  |

|------------------------------------|-----------------------|--------------------|-----------------------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x                                |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu                                |  |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu                                |  |

| WDT Reset                          | 000h                  | 0000 luuu          | uu                                |  |

| WDT Wake-up                        | PC + 1                | นนน0 0นนน          | uu                                |  |

| Brown-out Reset (PIC16C710/711)    | 000h                  | 0001 luuu          | u0                                |  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu                                |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 8-11: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C715

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | u10x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uuuu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | uuuu             |

| WDT Reset                          | 000h                  | 0000 luuu          | uuuu             |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uuuu             |

| Brown-out Reset                    | 000h                  | 0001 luuu          | uuu0             |

| Parity Error Reset                 | 000h                  | uuul Ouuu          | u0uu             |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| RegisterPower-on Reset,Brown-out ResetParity Error Reset |           | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |  |  |

|----------------------------------------------------------|-----------|--------------------------|------------------------------------|--|--|

| W                                                        | XXXX XXXX | นนนน นนนน                | นนนน นนนน                          |  |  |

| INDF                                                     | N/A       | N/A                      | N/A                                |  |  |

| TMR0                                                     | xxxx xxxx | <u>uuuu</u> uuuu         | uuuu uuuu                          |  |  |

| PCL                                                      | 0000 0000 | 0000 0000                | PC + 1(2)                          |  |  |

| STATUS                                                   | 0001 1xxx | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |  |  |

| FSR                                                      | xxxx xxxx | uuuu uuuu                | uuuu uuuu                          |  |  |

| PORTA                                                    | x 0000    | u 0000                   | u uuuu                             |  |  |

| PORTB                                                    | xxxx xxxx | uuuu uuuu                | uuuu uuuu                          |  |  |

| PCLATH                                                   | 0 0000    | 0 0000                   | u uuuu                             |  |  |

| INTCON                                                   | 0000 000x | 0000 000u                | uuuu uuuu <b>(1)</b>               |  |  |

| PIR1                                                     | -0        | -0                       | _ <sub>u</sub> _(1)                |  |  |

| ADCON0                                                   | 0000 00-0 | 0000 00-0                | uuuu uu-u                          |  |  |

| OPTION                                                   | 1111 1111 | 1111 1111                | นนนน นนนน                          |  |  |

| TRISA                                                    | 1 1111    | 1 1111                   | u uuuu                             |  |  |

| TRISB                                                    | 1111 1111 | 1111 1111                | นนนน นนนน                          |  |  |

| PIE1                                                     | -0        | -0uu                     |                                    |  |  |

| PCON                                                     | वेर्वेवे  | luu                      | luu                                |  |  |

| ADCON1                                                   | 00        | 00                       |                                    |  |  |

#### TABLE 8-13: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C715

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-11 for reset value for specific condition.

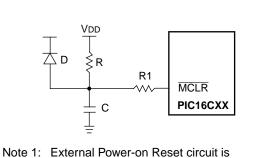

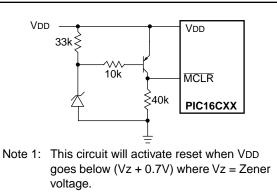

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

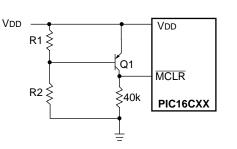

#### FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

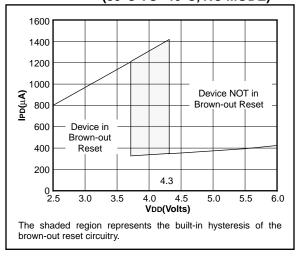

### FIGURE 12-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

Applicable Devices 710 71 711 715

# Applicable Devices 710 71 711 715

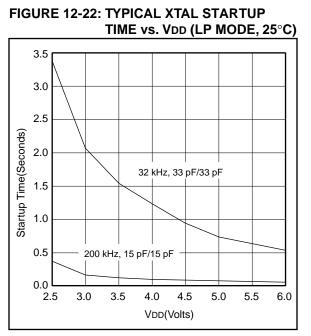

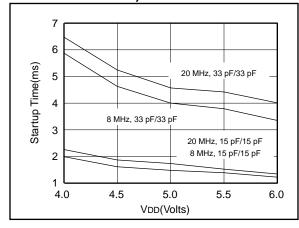

FIGURE 12-23: TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

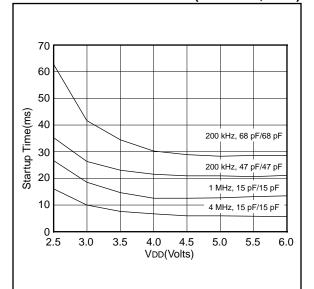

#### FIGURE 12-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

#### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

|                  |                 | <b>A B</b>            | <b>a b</b>       |  |  |  |  |  |

|------------------|-----------------|-----------------------|------------------|--|--|--|--|--|

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1      | Cap. Range<br>C2 |  |  |  |  |  |

| LP               | 32 kHz          | 33 pF                 | 33 pF            |  |  |  |  |  |

|                  | 200 kHz         | 15 pF                 | 15 pF            |  |  |  |  |  |

| ХТ               | 200 kHz         | 47-68 pF              | 47-68 pF         |  |  |  |  |  |

|                  | 1 MHz           | 15 pF                 | 15 pF            |  |  |  |  |  |

|                  | 4 MHz           | 15 pF                 | 15 pF            |  |  |  |  |  |

| HS               | 4 MHz           | 15 pF                 | 15 pF            |  |  |  |  |  |

|                  | 8 MHz           | 15-33 pF              | 15-33 pF         |  |  |  |  |  |

|                  | 20 MHz          | 15-33 pF              | 15-33 pF         |  |  |  |  |  |

|                  | , , ,           |                       |                  |  |  |  |  |  |

| Crystals<br>Used |                 |                       |                  |  |  |  |  |  |

| 32 kHz           | Epson C-00      | Epson C-001R32.768K-A |                  |  |  |  |  |  |

| 200 kHz          | STD XTL 2       | ± 20 PPM              |                  |  |  |  |  |  |

| 1 MHz            | ECS ECS-1       | ± 50 PPM              |                  |  |  |  |  |  |

| 4 MHz            | ECS ECS-4       | ± 50 PPM              |                  |  |  |  |  |  |

| 8 MHz            | EPSON CA        | EPSON CA-301 8.000M-C |                  |  |  |  |  |  |

| 20 MHz           | EPSON CA        | -301 20.000M-C        | ± 30 PPM         |  |  |  |  |  |

# PIC16C71X

Applicable Devices 710 71 711 715

# 13.0 ELECTRICAL CHARACTERISTICS FOR PIC16C715

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Storage temperature                                                                                                                           | 150°C  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                  | 0.3V)  |

| Voltage on VDD with respect to Vss                                                                                                            | +7.5V  |

| Voltage on MCLR with respect to Vss0 to                                                                                                       | +14V   |

| Voltage on RA4 with respect to Vss0 to                                                                                                        | +14V   |

| Total power dissipation (Note 1)                                                                                                              | .1.0W  |

| Maximum current out of Vss pin                                                                                                                | )0 mA  |

| Maximum current into VDD pin                                                                                                                  | 50 mA  |

|                                                                                                                                               | 20 mA  |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)±2                                                                                              | 20 mA  |

| Maximum output current sunk by any I/O pin                                                                                                    | 25 mA  |

|                                                                                                                                               | 201101 |

| Maximum current sunk by PORTA                                                                                                                 | )0 mA  |

| Maximum current sourced by PORTA                                                                                                              | )0 mA  |

| Maximum current sunk by PORTB                                                                                                                 | )0 mA  |

| Maximum current sourced by PORTB                                                                                                              | )0 mA  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Rdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD - VOH) x IOH} + $\Sigma$ (VOI x |        |

| + NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the                                      | ne     |

TNOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### Applicable Devices 710 71 711 715

#### 13.2 DC Characteristics: PIC16LC715-04 (Commercial, Industrial)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)<br>Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial)<br>$-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) |                                                                     |               |      |                   |      |                        |                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------|------|-------------------|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                                                                                                                        | Characteristic                                                      | Sym           | Min  | Тур†              | Max  | Units                  | Conditions                                                                                                                                                                                   |

| D001                                                                                                                                                                                                                | Supply Voltage                                                      | Vdd           | 2.5  | -                 | 5.5  | V                      | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |

| D002*                                                                                                                                                                                                               | RAM Data Retention<br>Voltage (Note 1)                              | Vdr           | -    | 1.5               | -    | V                      | Device in SLEEP mode                                                                                                                                                                         |

| D003                                                                                                                                                                                                                | VDD start voltage to<br>ensure internal<br>Power-on Reset<br>signal | VPOR          | -    | Vss               | -    | V                      | See section on Power-on Reset for details                                                                                                                                                    |

| D004*                                                                                                                                                                                                               | VDD rise rate to<br>ensure internal<br>Power-on Reset<br>signal     | SVDD          | 0.05 | -                 | -    | V/ms                   | See section on Rower-on Reset for details                                                                                                                                                    |

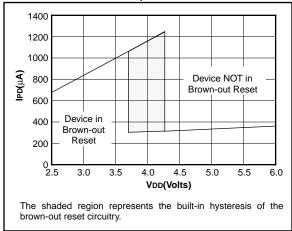

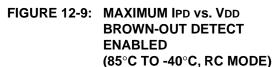

| D005                                                                                                                                                                                                                | Brown-out Reset<br>Voltage                                          | Bvdd          | 3.7  | 4.0               | 4.3  | V                      | BODEN configuration bit is enabled                                                                                                                                                           |

| D010                                                                                                                                                                                                                | Supply Current<br>(Note 2)                                          | IDD           | -    | 2.0               | 3.8  | mA                     | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                |

| D010A                                                                                                                                                                                                               |                                                                     |               | -    | 22.5              | 48   | βıΑ                    | LP osc configuration<br>Fosc = 32 kHz, VDD = $3.0V$ , WDT disabled                                                                                                                           |

| D015                                                                                                                                                                                                                | Brown-out Reset<br>Current (Note 5)                                 | $\Delta$ IBOR | -    | 300*              | 500  | μΑ                     | BOR enabled VDD = 5.0V                                                                                                                                                                       |

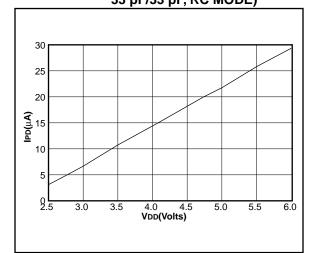

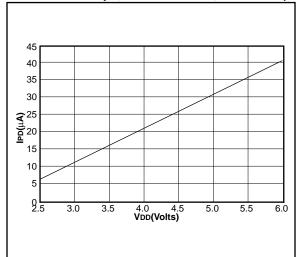

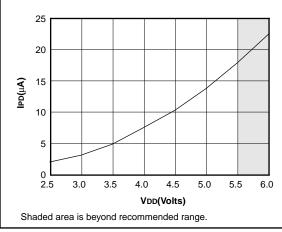

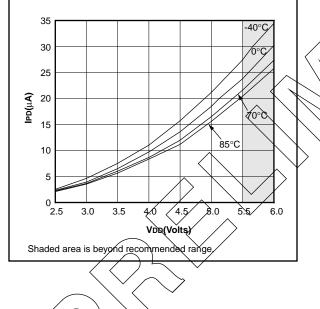

| D020<br>D021<br>D021A                                                                                                                                                                                               | Power-down Current<br>(Note 3)                                      | IPD           |      | 7.5<br>0.9<br>0.9 | 30 5 | μ <b>Α</b><br>μΑ<br>μΑ | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |

| D023                                                                                                                                                                                                                | Brown-out Reset<br>Current (Note 5)                                 |               | -    | 300*              | 500  | μA                     | BOR enabled VDD = 5.0V                                                                                                                                                                       |

These parameters are characterized but pot tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, escillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

ØSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDR; WDT$  enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# Applicable Devices71071711715

| DC CHAI      | RACTERISTICS                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended)Operating voltage VDD range as described in DC spec Section 13.1and Section 13.2. |           |            |     |       |                                                                                                         |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----|-------|---------------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                             | Sym                                                                                                                                                                                                                                                                                                                                | Min       | Typ<br>+   | Max | Units | Conditions                                                                                              |

| NO.          | Output High Voltage                        |                                                                                                                                                                                                                                                                                                                                    |           | 1          |     |       |                                                                                                         |

| D090         | I/O ports (Note 3)                         | Vон                                                                                                                                                                                                                                                                                                                                | Vdd - 0.7 | -          | -   | V     | ІОН = -3.0 mA, VDp =\4.5V,<br>-40°С to +85°С                                                            |

| D090A        |                                            |                                                                                                                                                                                                                                                                                                                                    | Vdd - 0.7 | -          | -   | V     | $IOH = -2.5 \text{ mA}, \text{VDD} = 4.5\text{V}, -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ |

| D092         | OSC2/CLKOUT (RC osc config)                |                                                                                                                                                                                                                                                                                                                                    | Vdd - 0.7 | -          | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С tø +85°С                                                            |

| D092A        |                                            |                                                                                                                                                                                                                                                                                                                                    | Vdd - 0.7 | -          | -   | V     | ION = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                           |