Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 36 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc710-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PIC16C71X FAMILY OF DEVICES

|             |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|-------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|             | EPROM Program Memory (x14 words)                | 512                                 | 1K                  | 1K                                  | 2K                                  | 2K                         | _                          |

| Memory      | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2K                         |

|             | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|             | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| Peripherals | Capture/Compare/PWM<br>Module(s)                | _                                   | _                   | _                                   | _                                   | 1                          | 1                          |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|             | Parallel Slave Port                             | _                                   | _                   | _                                   | _                                   | _                          | _                          |

|             | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|             | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|             | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|             | Voltage Range (Volts)                           | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| Features    | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Brown-out Reset                                 | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

|             |                                                 | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|-------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory (x14 words)                | 4K                          | 4K                                        | 8K                          | 8K                                        |

| oy          | Data Memory (bytes)                             | 192                         | 192                                       | 376                         | 376                                       |

|             | Timer Module(s)                                 | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM<br>Module(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                             | _                           | Yes                                       | _                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                  | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                               | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                        | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                           | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| Features    | In-Circuit Serial Programming                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                 | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                        | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

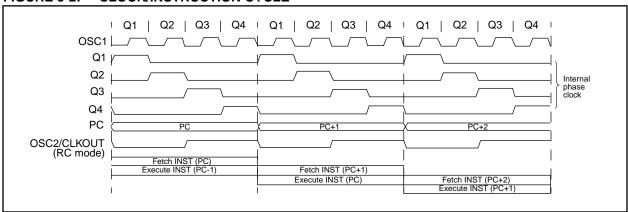

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

### 3.2 <u>Instruction Flow/Pipelining</u>

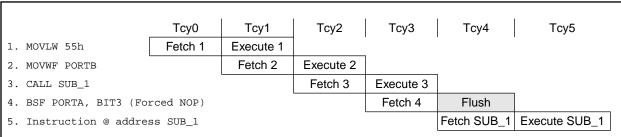

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.2.2.2 OPTION REGISTER

710 71 711 715 Applicable Devices

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

#### FIGURE 4-8: **OPTION REGISTER (ADDRESS 81h, 181h)**

| R/   | W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------|-----|--------|-------|-------|-------|-------|-------|-------|

| RE   | 3PU | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit7 |     |        |       |       |       |       |       | bit0  |

= Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

- bit 7: RBPU: PORTB Pull-up Enable bit

- 1 = PORTB pull-ups are disabled

- 0 = PORTB pull-ups are enabled by individual port latch values

- INTEDG: Interrupt Edge Select bit bit 6:

- 1 = Interrupt on rising edge of RB0/INT pin

- 0 = Interrupt on falling edge of RB0/INT pin

- bit 5: T0CS: TMR0 Clock Source Select bit

- 1 = Transition on RA4/T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- T0SE: TMR0 Source Edge Select bit bit 4:

- 1 = Increment on high-to-low transition on RA4/T0CKI pin

- 0 = Increment on low-to-high transition on RA4/T0CKI pin

- bit 3: PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0: PS2:PS0: Prescaler Rate Select bits

| Bit Value                              | TMR0 Rate                                 | WDT Rate                         |

|----------------------------------------|-------------------------------------------|----------------------------------|

| 000<br>001<br>010<br>011<br>100<br>101 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16 |

| 110<br>111                             | 1 : 128<br>1 : 256                        | 1 : 64<br>1 : 128                |

## FIGURE 8-2: CONFIGURATION WORD, PIC16C710/711

CP0 PWRTE WDTE FOSC1 FOSC0 CP0 CP0 CP0 CP0 CP0 CP0 CP0 BODEN CP0 Register: **CONFIG** Address 2007h bit13 bit 13-7 CP0: Code protection bits (2) 5-4: 1 = Code protection off 0 = All memory is code protected, but 00h - 3Fh is writable **BODEN:** Brown-out Reset Enable bit (1) bit 6: 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0: FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled. 2: All of the CP0 bits have to be given the same value to enable the code protection scheme listed.

### FIGURE 8-3: CONFIGURATION WORD, PIC16C715

CP1 CP1 CP0 CP0 MPEEN BODEN PWRTE | WDTE | FOSC1 | FOSC0 CP0 CP1 CP1 CP0 Register: **CONFIG** Address 2007h hit13 bit0 bit 13-8 CP1:CP0: Code Protection bits (2) 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected 00 = All memory is code protected bit 7: MPEEN: Memory Parity Error Enable 1 = Memory Parity Checking is enabled 0 = Memory Parity Checking is disabled **BODEN:** Brown-out Reset Enable bit (1) bit 6: 1 = BOR enabled 0 = BOR disabled PWRTE: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0: FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled. 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

TABLE 8-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C71

| TO | PD |                                                         |  |  |  |

|----|----|---------------------------------------------------------|--|--|--|

| 1  | 1  | Power-on Reset                                          |  |  |  |

| 0  | x  | llegal, TO is set on POR                                |  |  |  |

| х  | 0  | llegal, $\overline{PD}$ is set on $\overline{POR}$      |  |  |  |

| 0  | 1  | WDT Reset                                               |  |  |  |

| 0  | 0  | WDT Wake-up                                             |  |  |  |

| u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

# TABLE 8-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C710/711

| POR | BOR | TO | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | х   | 1  | 1  | Power-on Reset                                          |  |

| 0   | х   | 0  | х  | llegal, TO is set on POR                                |  |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | х  | х  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | NDT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

# TABLE 8-9: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C715

| PER | POR | BOR | TO | PD |                                                         |

|-----|-----|-----|----|----|---------------------------------------------------------|

| 1   | 0   | х   | 1  | 1  | Power-on Reset                                          |

| х   | 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| х   | 0   | х   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 1   | 0   | x  | х  | Brown-out Reset                                         |

| 1   | 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

| 0   | 1   | 1   | 1  | 1  | Parity Error Reset                                      |

| 0   | 0   | х   | x  | х  | Illegal, PER is set on POR                              |

| 0   | х   | 0   | х  | х  | Illegal, PER is set on BOR                              |

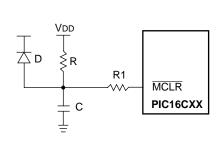

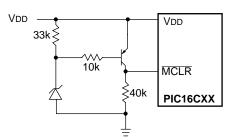

FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- Resistors should be adjusted for the characteristics of the transistor.

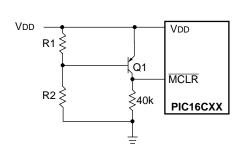

# FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

# 10.6 PICDEM-1 Low-Cost PIC16/17 Demonstration Board

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

# 10.7 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

# 10.8 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include

an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 10.9 MPLAB Integrated Development Environment Software

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- · A full featured editor

- · Three operating modes

- editor

- emulator

- simulator

- · A project manager

- · Customizable tool bar and key mapping

- · A status bar with project information

- Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- · Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 10.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PC-hosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

DC CHARACTERISTICS

# Applicable Devices 710 71 711 715

11.1 DC Characteristics: PIC16C710-04 (Commercial, Industrial, Extended)

PIC16C711-04 (Commercial, Industrial, Extended)

PIC16C710-10 (Commercial, Industrial, Extended)

PIC16C711-10 (Commercial, Industrial, Extended)

PIC16C710-20 (Commercial, Industrial, Extended) PIC16C711-20 (Commercial, Industrial, Extended)

### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +85 $^{\circ}$ C (industrial) -40 $^{\circ}$ C  $\leq$  TA  $\leq$  +125 $^{\circ}$ C (extended)

|                                |                                                            |       |             |                           |                      | -                    | -40°C ≤ TA ≤ +125°C (extended)                                                                                                                                     |

|--------------------------------|------------------------------------------------------------|-------|-------------|---------------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                             | Sym   | Min         | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                         |

| D001<br>D001A                  | Supply Voltage                                             | VDD   | 4.0<br>4.5  | -<br>-                    | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                     | VDR   | -           | 1.5                       | -                    | V                    |                                                                                                                                                                    |

| D003                           | VDD start voltage to ensure internal Power-on Reset signal | VPOR  | -           | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                          |

| D004*                          | VDD rise rate to ensure internal Power-on Reset signal     | SVDD  | 0.05        | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                    | Bvdd  | 3.7         | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                 |

|                                |                                                            |       | 3.7         | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                    | IDD   | -           | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                                                                      |

| D013                           |                                                            |       | -           | 13.5                      | 30                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                  |

| D015                           | Brown-out Reset Current (Note 5)                           | Δlbor | -           | 300*                      | 500                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

| D020<br>D021<br>D021A<br>D021B | Power-down Current (Note 3)                                | IPD   | -<br>-<br>- | 10.5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D023                           | Brown-out Reset Current (Note 5)                           | ΔIBOR | -           | 300*                      | 500                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Applicable Devices 710 71 711 715

# 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 1        |       |   |      |

|----------|-------|---|------|

| F Freque | iency | Т | Time |

Lowercase letters (pp) and their meanings:

| рр |          |     |                                    |

|----|----------|-----|------------------------------------|

| СС | CCP1     | osc | OSC1                               |

| ck | CLKOUT   | rd  | RD                                 |

| cs | CS       | rw  | $\overline{RD}$ or $\overline{WR}$ |

| di | SDI      | sc  | SCK                                |

| do | SDO      | SS  | SS                                 |

| dt | Data in  | t0  | T0CKI                              |

| io | I/O port | t1  | T1CKI                              |

| mc | MCLR     | wr  | WR                                 |

Uppercase letters and their meanings:

| S |                        |   |              |

|---|------------------------|---|--------------|

| F | Fall                   | P | Period       |

| Н | High                   | R | Rise         |

| 1 | Invalid (Hi-impedance) | V | Valid        |

| L | Low                    | Z | Hi-impedance |

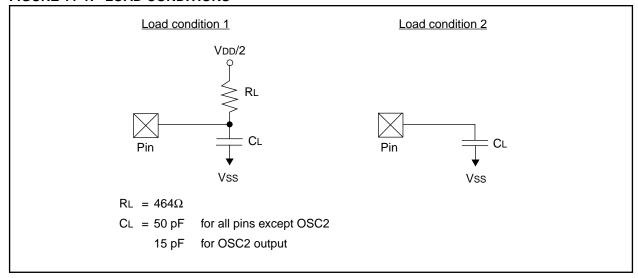

### FIGURE 11-1: LOAD CONDITIONS

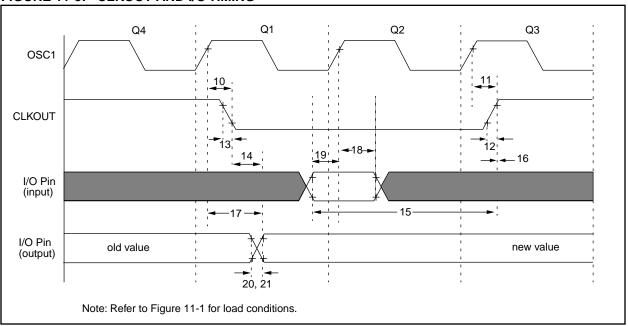

FIGURE 11-3: CLKOUT AND I/O TIMING

TABLE 11-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                               |                         | Min          | Тур† | Max         | Units | Conditions |

|------------------|----------|--------------------------------------------------------------|-------------------------|--------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                                             |                         | _            | 15   | 30          | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                                             |                         | _            | 15   | 30          | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                             |                         | _            | 5    | 15          | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                             |                         | _            | 5    | 15          | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out valid                                   | t                       | _            | _    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOUT ↑                                |                         | 0.25Tcy + 25 | _    | _           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT ↑                                  |                         | 0            | _    | _           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid                        |                         | _            | _    | 80 - 100    | ns    |            |

| 18*              | TosH2ioI | OSC1↑ (Q2 cycle) to<br>Port input invalid (I/O in hold time) |                         | TBD          | _    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC11 (                                  | (I/O in setup time)     | TBD          | _    | _           | ns    |            |

| 20*              | TioR     | Port output rise time                                        | PIC16 <b>C</b> 710/711  | _            | 10   | 25          | ns    |            |

|                  |          |                                                              | PIC16 <b>LC</b> 710/711 | _            | _    | 60          | ns    |            |

| 21*              | TioF     | Port output fall time                                        | PIC16 <b>C</b> 710/711  | _            | 10   | 25          | ns    |            |

|                  |          |                                                              | PIC16 <b>LC</b> 710/711 | _            | _    | 60          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                                     |                         | 20           | _    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                                      | or low time             | 20           | _    | _           | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

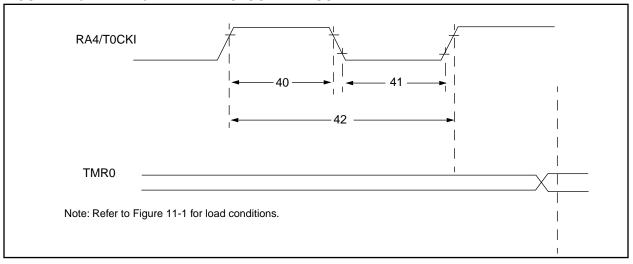

FIGURE 11-6: TIMERO EXTERNAL CLOCK TIMINGS

### TABLE 11-5: TIMERO EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                 |                    | Min                                    | Тур† | Max   | Units | Conditions                      |

|--------------|-----------|--------------------------------|--------------------|----------------------------------------|------|-------|-------|---------------------------------|

| 40           | Tt0H      | T0CKI High Pulse Width         | No Prescaler       | 0.5Tcy + 20*                           | _    | _     | ns    | Must also meet                  |

|              |           |                                | With Prescaler     | 10*                                    | _    | _     | ns    | parameter 42                    |

| 41           | Tt0L      | T0CKI Low Pulse Width          | No Prescaler       | 0.5Tcy + 20*                           | _    | _     | ns    | Must also meet                  |

|              |           |                                | With Prescaler     | 10*                                    | _    | _     | ns    | parameter 42                    |

| 42           | Tt0P      | T0CKI Period                   |                    | Greater of:<br>20 ns or TCY + 40*<br>N | _    | _     | ns    | N = prescale value (2, 4,, 256) |

| 48           | Tcke2tmrl | Delay from external clock edge | to timer increment | 2Tosc                                  | _    | 7Tosc | _     |                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

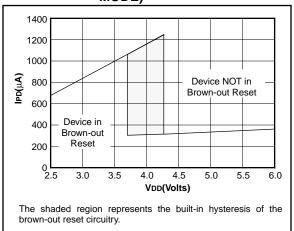

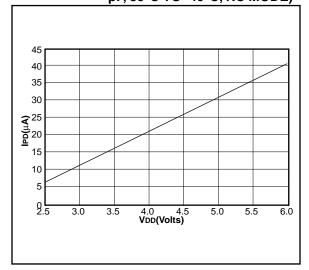

FIGURE 12-8: TYPICAL IPD vs. VDD BROWN-OUT DETECT ENABLED (RC MODE)

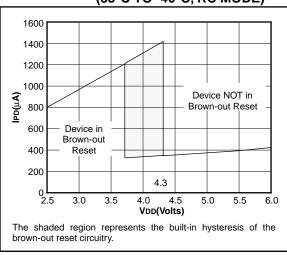

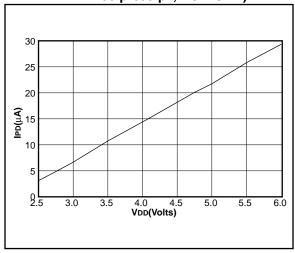

FIGURE 12-9: MAXIMUM IPD vs. VDD

BROWN-OUT DETECT

ENABLED

(85°C TO -40°C, RC MODE)

FIGURE 12-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

FIGURE 12-11: MAXIMUM IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, 85°C TO -40°C, RC MODE)

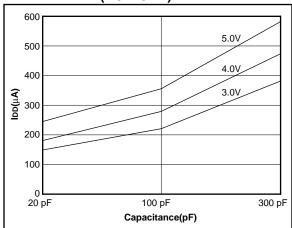

FIGURE 14-18: TYPICAL IDD vs.

CAPACITANCE @ 500 kHz

(RC MODE)

TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average         |        |  |  |  |

|--------|------|-----------------|--------|--|--|--|

| Cext   | Kext | Fosc @ 5V, 25°C |        |  |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |  |

|        | 100k | 268 kHz         | ±1,1%  |  |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ±1.0%  |  |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |  |

|        | 100k | 77.2 kH2        | ± 1.0% |  |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |  |

|        | 5k   | 501 kHz         | ± 1.2% |  |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for VDD = 5V.

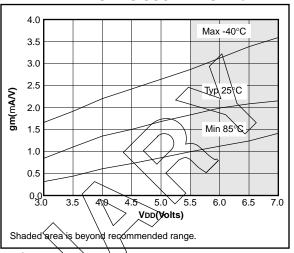

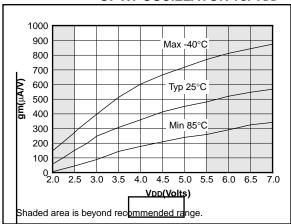

FIGURE 14-19: TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

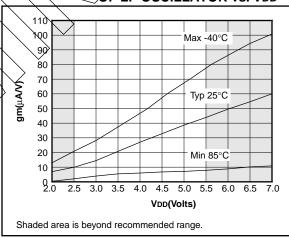

FIGURE 14-20: TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

FIGURE 14-21: TRANSCONDUCTANCE(gm)

OF XT OSCILLATOR vs. VDD

Applicable Devices 710 71 711 715

15.3 DC Characteristics: PIC16C71-04 (Commercial, Industrial)

PIC16C71-20 (Commercial, Industrial) PIC16LC71-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

OOperating temperature  $0^{\circ}C$   $\leq TA \leq +70^{\circ}C$  (commercial)

**DC CHARACTERISTICS**  $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ (industrial)}$

Operating voltage VDD range as described in DC spec Section 15.1

and Section 15.2.

| Param | Characteristic                     | Sym   | Min       | Тур | Max    | Units | Conditions                                          |

|-------|------------------------------------|-------|-----------|-----|--------|-------|-----------------------------------------------------|

| No.   |                                    |       |           | t   |        |       |                                                     |

|       | Input Low Voltage                  |       |           |     |        |       |                                                     |

|       | I/O ports                          | VIL   |           |     |        |       |                                                     |

| D030  | with TTL buffer                    |       | Vss       | -   | 0.15V  | V     | For entire VDD range                                |

| D031  | with Schmitt Trigger buffer        |       | Vss       | -   | 0.8V   | V     | 4.5 ≤ VDD ≤ 5.5V                                    |

| D032  | MCLR, OSC1 (in RC mode)            |       | Vss       | -   | 0.2VDD | V     |                                                     |

| D033  | OSC1 (in XT, HS and LP)            |       | Vss       | -   | 0.3VDD | V     | Note1                                               |

|       | Input High Voltage                 |       |           |     |        |       |                                                     |

|       | I/O ports (Note 4)                 | VIH   |           | -   |        |       |                                                     |

| D040  | with TTL buffer                    |       | 2.0       | -   | Vdd    | V     | 4.5 ≤ VDD ≤ 5.5V                                    |

| D040A |                                    |       | 0.25VDD   | -   | Vdd    |       | For entire VDD range                                |

|       |                                    |       | + 0.8V    |     |        |       |                                                     |

| D041  | with Schmitt Trigger buffer        |       | 0.85VDD   | -   | Vdd    |       | For entire VDD range                                |

| D042  | MCLR, RB0/INT                      |       | 0.85VDD   | -   | Vdd    | V     |                                                     |

| D042A | OSC1 (XT, HS and LP)               |       | 0.7Vdd    | -   | Vdd    | V     | Note1                                               |

| D043  | OSC1 (in RC mode)                  |       | 0.9Vdd    | -   | Vdd    | V     |                                                     |

| D070  | PORTB weak pull-up current         | IPURB | 50        | 250 | †400   | μΑ    | VDD = 5V, VPIN = VSS                                |

|       | Input Leakage Current (Notes 2, 3) |       |           |     |        |       |                                                     |

| D060  | I/O ports                          | lιL   | -         | -   | ±1     | μΑ    | Vss ≤ VPIN ≤ VDD, Pin at hi-<br>impedance           |

| D061  | MCLR, RA4/T0CKI                    |       | -         | -   | ±5     | μΑ    | Vss ≤ Vpin ≤ Vdd                                    |

| D063  | OSC1                               |       | -         | -   | ±5     | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc configuration   |

|       | Output Low Voltage                 |       |           |     |        |       |                                                     |

| D080  | I/O ports                          | Vol   | -         | -   | 0.6    | V     | IOL = $8.5$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C |

| D083  | OSC2/CLKOUT (RC osc config)        |       | -         | -   | 0.6    | V     | IOL = 1.6mA, VDD = 4.5V,<br>-40°C to +85°C          |

|       | Output High Voltage                |       |           |     |        |       |                                                     |

| D090  | I/O ports (Note 3)                 | Vон   | VDD - 0.7 | -   | -      | V     | IOH = -3.0mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D092  | OSC2/CLKOUT (RC osc config)        |       | VDD - 0.7 | -   | -      | V     | IOH = -1.3mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D130* | Open-Drain High Voltage            | Vod   | -         | -   | 14     | V     | RA4 pin                                             |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: PIC16C71 Rev. "Ax" INT pin has a TTL input buffer. PIC16C71 Rev. "Bx" INT pin has a Schmitt Trigger input buffer.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt trigger input. It is not recommended that the PIC16C71 be driven with external clock in RC mode.

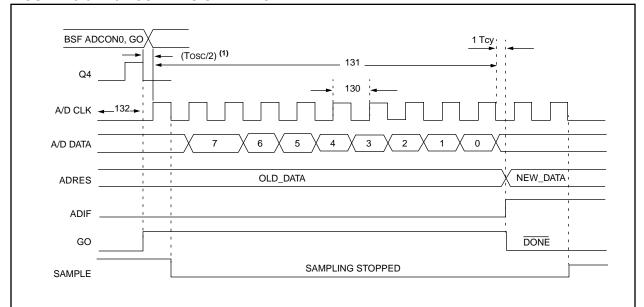

## FIGURE 15-6: A/D CONVERSION TIMING

Note 1: If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

### TABLE 15-7: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                          |                               | Min    | Тур†    | Max | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|-----------------------------------------|-------------------------------|--------|---------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                        | PIC16 <b>C</b> 71             | 2.0    | _       | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                         | PIC16 <b>LC</b> 71            | 2.0    | _       | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                 |

|              |      |                                         | PIC16 <b>C</b> 71             | 2.0    | 4.0     | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                 |

|              |      |                                         | PIC16 <b>LC</b> 71            | 3.0    | 6.0     | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not including S/H time | ne) (Note 1)                  | _      | 9.5     | _   | TAD   |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                        |                               | Note 2 | 20      | _   | μs    |                                                                                                                                                                                                             |

|              |      |                                         |                               | 5*     | _       | _   | μѕ    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 19.5 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | Tgo  | Q4 to A/D clock start                   |                               | _      | Tosc/2§ | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

| 135          | Tswc | Switching from conve                    | $ert \rightarrow sample time$ | 1.5§   | _       | _   | TAD   |                                                                                                                                                                                                             |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

These specifications ensured by design.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>2:</sup> See Section 7.1 for min conditions.

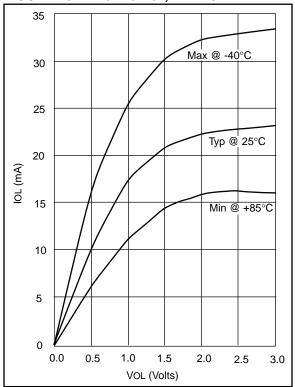

FIGURE 16-21: IOL VS. VOL, VDD = 3V

FIGURE 16-22: IOL VS. VOL, VDD = 5V

Data based on matrix samples. See first page of this section for details.

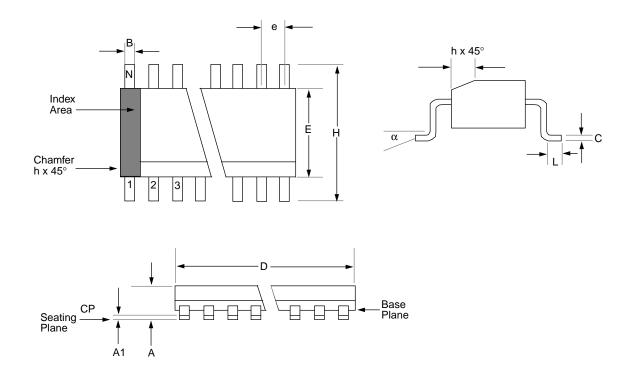

# 17.3 18-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body)(SO)

|        | Package Group: Plastic SOIC (SO) |             |           |        |       |           |  |  |  |

|--------|----------------------------------|-------------|-----------|--------|-------|-----------|--|--|--|

|        |                                  | Millimeters |           | Inches |       |           |  |  |  |

| Symbol | Min                              | Max         | Notes     | Min    | Max   | Notes     |  |  |  |

| α      | 0°                               | 8°          |           | 0°     | 8°    |           |  |  |  |

| Α      | 2.362                            | 2.642       |           | 0.093  | 0.104 |           |  |  |  |

| A1     | 0.101                            | 0.300       |           | 0.004  | 0.012 |           |  |  |  |

| В      | 0.355                            | 0.483       |           | 0.014  | 0.019 |           |  |  |  |

| С      | 0.241                            | 0.318       |           | 0.009  | 0.013 |           |  |  |  |

| D      | 11.353                           | 11.735      |           | 0.447  | 0.462 |           |  |  |  |

| E      | 7.416                            | 7.595       |           | 0.292  | 0.299 |           |  |  |  |

| е      | 1.270                            | 1.270       | Reference | 0.050  | 0.050 | Reference |  |  |  |

| Н      | 10.007                           | 10.643      |           | 0.394  | 0.419 |           |  |  |  |

| h      | 0.381                            | 0.762       |           | 0.015  | 0.030 |           |  |  |  |

| L      | 0.406                            | 1.143       |           | 0.016  | 0.045 |           |  |  |  |

| N      | 18                               | 18          |           | 18     | 18    |           |  |  |  |

| CP     | _                                | 0.102       |           | _      | 0.004 |           |  |  |  |

### **APPENDIX C: WHAT'S NEW**

Consolidated all pin compatible 18-pin A/D based devices into one data sheet.

# **APPENDIX D: WHAT'S CHANGED**

- Minor changes, spelling and grammatical changes.

- 2. Low voltage operation on the PIC16LC710/711/715 has been reduced from 3.0V to 2.5V.

- 3. Part numbers of the PIC16C70 and PIC16C71A have changed to PIC16C710 and PIC16C711, respectively.

| 1                                             |        | TMR0 Overflow                                         | 61     |

|-----------------------------------------------|--------|-------------------------------------------------------|--------|

| I/O Ports                                     |        | INTF bit                                              | 19     |

| PORTA                                         | 25     | IRP bit                                               | 17     |

| PORTB                                         | _      | <b>V</b>                                              |        |

| Section                                       |        | K                                                     |        |

|                                               |        | KeeLoq® Evaluation and Programming Tools              | 87     |

| I/O Programming Considerations                |        |                                                       |        |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator |        | L                                                     |        |

| In-Circuit Serial Programming                 |        | Loading of PC                                         | 23     |

| INDF Register14                               |        | LP                                                    | 54     |

| Indirect Addressing                           |        |                                                       |        |

| Instruction Cycle                             |        | M                                                     |        |

| Instruction Flow/Pipelining                   | 10     | MCLR5                                                 | 52. 56 |

| Instruction Format                            | 69     | Memory                                                | ,      |

| Instruction Set                               |        | Data Memory                                           | 12     |

| ADDLW                                         | 71     | Program Memory                                        |        |

| ADDWF                                         | 71     | Register File Maps                                    |        |

| ANDLW                                         | 71     | PIC16C71                                              | 12     |

| ANDWF                                         | 71     | PIC16C71                                              |        |

| BCF                                           | 72     | PIC16C711                                             |        |

| BSF                                           | 72     |                                                       |        |

| BTFSC                                         |        | PIC16C715                                             |        |

| BTFSS                                         |        | MP-DriveWay <sup>™</sup> - Application Code Generator |        |

| CALL                                          | _      | MPEEN bit                                             |        |

| CLRF                                          | -      | MPLAB™ C                                              | 87     |

| CLRW                                          |        | MPLAB™ Integrated Development Environment             |        |

|                                               |        | Software                                              | 86     |

| CLRWDT                                        |        | 0                                                     |        |

| COMF                                          |        | O .                                                   |        |

| DECF                                          | _      | OPCODE                                                |        |

| DECFSZ                                        | -      | OPTION Register                                       | 18     |

| GOTO                                          |        | Orthogonal                                            | 7      |

| INCF                                          | 76     | OSC selection                                         | 47     |

| INCFSZ                                        | 77     | Oscillator                                            |        |

| IORLW                                         | 77     | HS4                                                   | 49. 54 |

| IORWF                                         | 78     | LP4                                                   | 49. 54 |

| MOVF                                          | 78     | RC                                                    | 49     |

| MOVLW                                         | 78     | XT4                                                   | 49. 54 |

| MOVWF                                         | 78     | Oscillator Configurations                             | ,      |

| NOP                                           | 79     | Oscillator Start-up Timer (OST)                       |        |

| OPTION                                        | 79     |                                                       | 00     |

| RETFIE                                        | 79     | Р                                                     |        |

| RETLW                                         | 80     | Packaging                                             |        |

| RETURN                                        | 80     | 18-Lead CERDIP w/Window                               | 155    |

| RLF                                           | 81     | 18-Lead PDIP                                          |        |

| RRF                                           | -      | 18-Lead SOIC                                          |        |

| SLEEP                                         | 00     | 20-Lead SSOP                                          |        |

| SUBLW                                         | 82     |                                                       |        |

| SUBWF                                         |        | Paging, Program Memory                                |        |

| SWAPF                                         |        | PCL Register                                          |        |

|                                               |        | PCLATH5                                               |        |

| TRIS                                          |        | PCLATH Register 14, 15, 1                             | -      |

| XORLW                                         |        | PCON Register2                                        | -      |

| XORWF                                         |        | PD bit 17, 5                                          |        |

| Section                                       |        | PER bit                                               | 22     |

| Summary Table                                 | 70     | PIC16C71                                              | 147    |

| INT Interrupt                                 |        | AC Characteristics                                    | 147    |

| INTCON Register                               | 19     | PICDEM-1 Low-Cost PIC16/17 Demo Board                 | 86     |

| INTE bit                                      | 19     | PICDEM-2 Low-Cost PIC16CXX Demo Board                 | 86     |

| INTEDG bit                                    | 18, 63 | PICDEM-3 Low-Cost PIC16CXXX Demo Board                | 86     |

| Internal Sampling Switch (Rss) Impedence      | 40     | PICMASTER® In-Circuit Emulator                        | 85     |

| Interrupts                                    |        | PICSTART® Plus Entry Level Development System         |        |

| A/D                                           |        | PIE1 Register                                         |        |

| External                                      |        | Pin Functions                                         | 0      |

| PORTB Change                                  |        | MCLR/VPP                                              | o.     |

| PortB Change                                  |        | OSC1/CLKIN                                            |        |

| RB7:RB4 Port Change                           |        | OSC2/CLKOUT                                           |        |

| Section                                       |        | RAO/ANO                                               |        |

| TMR0                                          |        |                                                       |        |

| ( WILLY                                       |        | RA1/AN1                                               | 9      |

| RA2/AN2                                    | 9              | PIC16C711                                    | 13        |

|--------------------------------------------|----------------|----------------------------------------------|-----------|

| RA3/AN3/VREF                               | 9              | PIC16C715                                    |           |

| RA4/T0CKI                                  |                | Reset Conditions                             |           |

| RB0/INT                                    |                | Summary                                      |           |

| RB1                                        |                | Reset                                        |           |

| RB2                                        |                | Reset Conditions for Special Registers       |           |

| RB3                                        |                | RP0 bit                                      |           |

| RB4                                        |                | RP1 bit                                      |           |

|                                            |                | KFT DIL                                      | 17        |

| RB5                                        | -              | S                                            |           |

| RB6                                        | -              | CEEVAL® Evaluation and Programming System    | 07        |

| RB7                                        |                | SEEVAL® Evaluation and Programming System    | 01        |

| VDD                                        | -              | Services                                     | _         |

| Vss                                        | 9              | One-Time-Programmable (OTP) Devices          | 5         |

| Pinout Descriptions                        |                | Quick-Turnaround-Production (QTP) Devices    |           |

| PIC16C71                                   |                | Serialized Quick-Turnaround Production (SQTP | ,         |

| PIC16C710                                  |                | Devices                                      |           |

| PIC16C711                                  |                | SLEEP                                        | ,         |

| PIC16C715                                  |                | Software Simulator (MPLAB™ SIM)              |           |

| PIR1 Register                              |                | Special Features of the CPU                  | 47        |

| POP                                        | 23             | Special Function Registers                   |           |

| POR                                        | ,              | PIC16C71                                     |           |

| Oscillator Start-up Timer (OST)            | ,              | PIC16C710                                    |           |

| Power Control Register (PCON)              | 54             | PIC16C711                                    |           |

| Power-on Reset (POR)                       | 47, 53, 57, 58 | Special Function Registers, Section          | 14        |

| Power-up Timer (PWRT)                      | 47, 53         | Stack                                        | 23        |

| Time-out Sequence                          | 54             | Overflows                                    | 23        |

| Time-out Sequence on Power-up              | 59             | Underflow                                    | 23        |

| TO                                         |                | STATUS Register                              | 17        |

| OR bit                                     |                | -                                            |           |

| Port RB Interrupt                          |                | Т                                            |           |

| PORTA                                      |                | T0CS bit                                     | 18        |

| PORTA Register                             | ·              | T0IE bit                                     | 19        |

| PORTB                                      |                | T0IF bit                                     | 19        |

| PORTB Register                             |                | TAD                                          | 41        |

| Power-down Mode (SLEEP)                    |                | Timer0                                       |           |

| Prescaler, Switching Between Timer0 and WD |                | RTCC                                         | 57, 58    |

| PRO MATE® II Universal Programmer          |                | Timers                                       |           |

| Program Branches                           |                | Timer0                                       |           |

| Program Memory                             |                | Block Diagram                                | 31        |

| Paging                                     | 23             | External Clock                               |           |

| Program Memory Maps                        | 20             | External Clock Timing                        |           |

| PIC16C71                                   | 11             | Increment Delay                              |           |

| PIC16C71                                   |                | Interrupt                                    |           |

| PIC16C711                                  |                | Interrupt Timing                             |           |

| PIC16C715                                  |                | Prescaler                                    |           |

| Program Verification                       |                | Prescaler Block Diagram                      | 34        |

|                                            |                | Section                                      |           |

| PS0 bit<br>PS1 bit                         |                | Switching Prescaler Assignment               |           |

| PS2 bit                                    |                | Synchronization                              |           |

|                                            | _              | TOCKI                                        |           |

| PSA bit                                    | _              | TOIF                                         |           |

| PUSH                                       | 23             | Timing                                       |           |

| PWRT                                       |                | TMR0 Interrupt                               |           |

| Power-up Timer (PWRT)                      |                |                                              | 03        |

| PWRTE bit                                  | 47, 48         | Timing Diagrams                              | 104 146   |

| R                                          |                | A/D Conversion                               |           |

| · <del>-</del>                             |                | Brown-out Reset                              | -         |

| RBIE bit                                   |                | CLKOUT and I/O                               |           |

| RBIF bit                                   | · ·            | External Clock Timing                        |           |

| RBPU bit                                   |                | Power-up Timer                               |           |

| RC                                         |                | Reset                                        |           |

| RC Oscillator                              |                | Start-up Timer                               |           |

| Read-Modify-Write                          | 30             | Time-out Sequence                            |           |

| Register File                              | 12             | Timer0 31, 98,                               |           |

| Registers                                  |                | Timer0 Interrupt Timing                      |           |

| Maps                                       |                | Timer0 with External Clock                   |           |

| PIC16C71                                   | 12             | Wake-up from SLEEP through Interrupt         |           |

| PIC16C710                                  | 12             | Watchdog Timer                               | . 97, 143 |

|                                            |                |                                              |           |