Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 36 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc710t-04-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

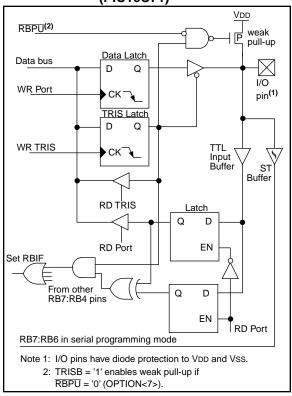

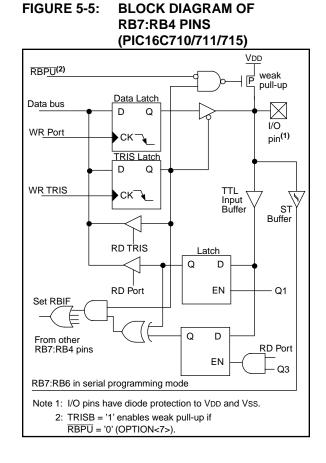

#### FIGURE 5-4: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C71)

#### TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

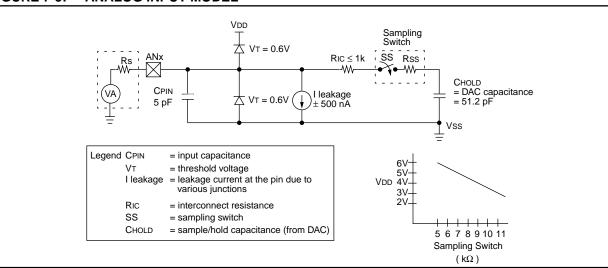

#### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

#### EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

#### FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

#### 7.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 7-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 20 MHz and 16 MHz (The A/D clock is programmed for 32TOSC), and assumes that immediately after 6TAD, the A/D clock is programmed for 2TOSC.

The 2Tosc violates the minimum TAD time since the last 4-bits will not be converted to correct values.

| EXAMPLE 7-3: | 4-BIT vs. 8-BIT CONVERSION TIMES |

|--------------|----------------------------------|

| $\mathbf{L}$ |                                  |

|                                 | - (1)                      | Resolution |         |  |

|---------------------------------|----------------------------|------------|---------|--|

|                                 | Freq. (MHz) <sup>(1)</sup> | 4-bit      | 8-bit   |  |

| TAD                             | 20                         | 1.6 μs     | 1.6 μs  |  |

|                                 | 16                         | 2.0 μs     | 2.0 μs  |  |

| Tosc                            | 20                         | 50 ns      | 50 ns   |  |

|                                 | 16                         | 62.5 ns    | 62.5 ns |  |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 20                         | 10 μs      | 16 μs   |  |

|                                 | 16                         | 12.5 μs    | 20 µs   |  |

Note 1: The PIC16C71 has a minimum TAD time of 2.0 µs.

All other PIC16C71X devices have a minimum TAD time of 1.6  $\mu$ s.

#### 8.4.5 TIME-OUT SEQUENCE

#### Applicable Devices 710 71 711 715

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 8-11, Figure 8-12, and Figure 8-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 8-12). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 8-10 and Table 8-11 show the reset conditions for some special function registers, while Table 8-12 and Table 8-13 show the reset conditions for all the registers.

#### 8.4.6 POWER CONTROL/STATUS REGISTER (PCON)

#### Applicable Devices71071711715

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word). Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

For the PIC16C715, bit2 is  $\overline{\text{PER}}$  (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

For the PIC16C715, bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset of interrupt.

#### 8.4.7 PARITY ERROR RESET (PER)

#### Applicable Devices 710 71 711 715

The PIC16C715 has on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit 2 in the PCON register is cleared (logic '0'). This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure in Program Memory. This flag can only be set (logic '1') by software.

The parity array is user selectable during programming. Bit 7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity. If left unprogrammed (read as '1'), parity is enabled.

#### TABLE 8-5:TIME-OUT IN VARIOUS SITUATIONS, PIC16C71

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | —                  |           |

#### TABLE 8-6:TIME-OUT IN VARIOUS SITUATIONS, PIC16C710/711/715

| Oscillator Configuration | Power            | Power-up  |                  | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            | _         | 72 ms            | _                  |

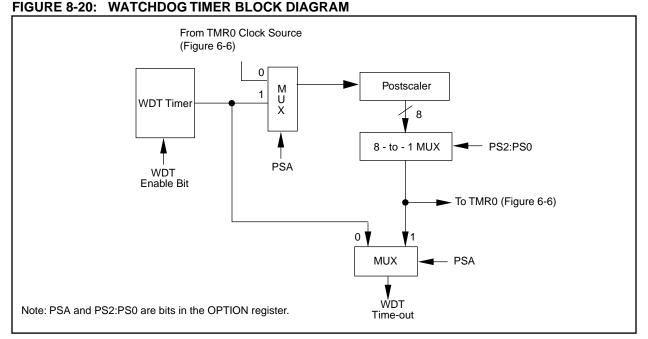

#### 8.7 <u>Watchdog Timer (WDT)</u>

#### Applicable Devices 710 71 711 715

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 8.1).

#### 8.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 8.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 8-21: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 8-1, Figure 8-2 and Figure 8-3 for operation of these bits.

#### © 1997 Microchip Technology Inc.

| SUBWF             | Subtract                                                          | W from f                     |                                   |               |

|-------------------|-------------------------------------------------------------------|------------------------------|-----------------------------------|---------------|

| Syntax:           | [ label ]                                                         | SUBWF                        | f,d                               |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ | 7                            |                                   |               |

| Operation:        | (f) - (W) –                                                       | → (dest)                     |                                   |               |

| Status Affected:  | C, DC, Z                                                          |                              |                                   |               |

| Encoding:         | 00                                                                | 0010                         | dfff                              | ffff          |

| Description:      | Subtract (2<br>ister from r<br>stored in th<br>result is sto      | egister 'f'. I<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the |

| Words:            | 1                                                                 |                              |                                   |               |

| Cycles:           | 1                                                                 |                              |                                   |               |

| Q Cycle Activity: | Q1                                                                | Q2                           | Q3                                | Q4            |

|                   | Decode                                                            | Read                         | Process                           | Write to      |

|                   |                                                                   | register 'f'                 | data                              | dest          |

| Example 1:        | SUBWF                                                             | reg1,1                       |                                   |               |

|                   | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 3                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?                                 |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 1                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>1; result is                 | positive      |

|                   | Z                                                                 | =                            | 0                                 | poolito       |

| Example 2:        | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 2                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?<br>?                            |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 0                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | C<br>Z                                                            | =                            | 1; result is                      | zero          |

| Example 3:        | Eefore Ins                                                        | _                            | 1                                 |               |

|                   | REG1                                                              | -                            | 1                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | С                                                                 | =                            | ?                                 |               |

|                   | Z<br>After Instr                                                  | =                            | ?                                 |               |

|                   |                                                                   |                              |                                   |               |

|                   | REG1<br>W                                                         | =                            | 0xFF<br>2                         |               |

|                   | С                                                                 | =                            | 0; result is                      | negative      |

|                   | Z                                                                 | =                            | 0                                 |               |

| SWAPF             | Swap Ni                                                                                                                                                                 | bbles in                                    | f               |                  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------|------------------|--|--|--|--|

| Syntax:           | [label] SWAPF f,d                                                                                                                                                       |                                             |                 |                  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                          | 0 ≤ f ≤ 127<br>d ∈ [0,1]                    |                 |                  |  |  |  |  |

| Operation:        |                                                                                                                                                                         | $\rightarrow$ (dest<) $\rightarrow$ (dest<) |                 |                  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                    |                                             |                 |                  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                      | 1110                                        | dfff            | ffff             |  |  |  |  |

| Description:      | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0 the<br>result is placed in W register. If 'd' is 1<br>the result is placed in register 'f'. |                                             |                 |                  |  |  |  |  |

| Words:            | 1                                                                                                                                                                       |                                             |                 |                  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                       |                                             |                 |                  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                      | Q2                                          | Q3              | Q4               |  |  |  |  |

|                   | Decode                                                                                                                                                                  | Read<br>register 'f'                        | Process<br>data | Write to<br>dest |  |  |  |  |

| Example           | SWAPF                                                                                                                                                                   | REG,                                        | 0               |                  |  |  |  |  |

|                   | Before In                                                                                                                                                               | struction                                   |                 |                  |  |  |  |  |

|                   |                                                                                                                                                                         | REG1                                        | = 0xA           | 45               |  |  |  |  |

|                   | After Inst                                                                                                                                                              | ruction                                     |                 |                  |  |  |  |  |

|                   |                                                                                                                                                                         | REG1<br>W                                   | = 0x4<br>= 0x5  |                  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                                   |

| Example          |                                                                                                                                                                                     |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |

|                  |                                                                                                                                                                                     |

# PIC16C71X

| XORLW             | Exclusi           | ve OR Li                                  | iteral wit      | h W           |  |

|-------------------|-------------------|-------------------------------------------|-----------------|---------------|--|

| Syntax:           | [label]           | XORL                                      | V k             |               |  |

| Operands:         | $0 \le k \le 2$   | 255                                       |                 |               |  |

| Operation:        | (W) .XO           | $R.k \rightarrow (N)$                     | N)              |               |  |

| Status Affected:  | Z                 |                                           |                 |               |  |

| Encoding:         | 11                | 1010                                      | kkkk            | kkkk          |  |

| Description:      | XOR'ed v          | ents of the<br>vith the ei<br>t is placed | ght bit lite    | ral 'k'.      |  |

| Words:            | 1                 |                                           |                 |               |  |

| Cycles:           | 1                 |                                           |                 |               |  |

| Q Cycle Activity: | Q1                | Q2                                        | Q3              | Q4            |  |

|                   | Decode            | Read<br>literal 'k'                       | Process<br>data | Write to<br>W |  |

| Example:          | XORLW             | 0xAF                                      |                 |               |  |

|                   | Before I          | Before Instruction                        |                 |               |  |

|                   |                   | W =                                       | 0xB5            |               |  |

|                   | After Instruction |                                           |                 |               |  |

|                   |                   | W =                                       | 0x1A            |               |  |

|                   |                   |                                           |                 |               |  |

| XORWF             | Exclusiv                                                         | e OR W                   | with f                         |                     |

|-------------------|------------------------------------------------------------------|--------------------------|--------------------------------|---------------------|

| Syntax:           | [label]                                                          | XORWF                    | f,d                            |                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                       |                                |                     |

| Operation:        | (W) .XOF                                                         | $R.\left(f\right)\to($   | dest)                          |                     |

| Status Affected:  | Z                                                                |                          |                                |                     |

| Encoding:         | 00                                                               | 0110                     | dfff                           | ffff                |

| Description:      | Exclusive<br>register wi<br>result is st<br>is 1 the res         | th registe<br>ored in th | r 'f'. If 'd' is<br>e W regist | o the<br>er. If 'd' |

| Words:            | 1                                                                |                          |                                |                     |

| Cycles:           | 1                                                                |                          |                                |                     |

| Q Cycle Activity: | Q1                                                               | Q2                       | Q3                             | Q4                  |

|                   | Decode                                                           | Read<br>register<br>'f'  | Process<br>data                | Write to<br>dest    |

| Example           | XORWF                                                            | REG                      | 1                              |                     |

|                   | Before In                                                        | struction                | 1                              |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | AF<br>B5            |

|                   | After Inst                                                       | ruction                  |                                |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | 1A<br>B5            |

#### 10.6 <u>PICDEM-1 Low-Cost PIC16/17</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 10.7 <u>PICDEM-2 Low-Cost PIC16CXX</u> Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

#### 10.8 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 10.9 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 10.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

#### Applicable Devices 710 71 711 715

# TABLE 11-6:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C710/711-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Param<br>No. | Sym  | Characteristic                                 | Min       | Тур†       | Мах        | Units | Conditions                                                                                              |

|--------------|------|------------------------------------------------|-----------|------------|------------|-------|---------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                     | —         | _          | 8-bits     | bit   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A02          | EABS | Absolute error                                 | —         | —          | <±1        | LSb   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A03          | EIL  | Integral linearity error                       | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A04          | Edl  | Differential linearity error                   | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A05          | Efs  | Full scale error                               | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A06          | EOFF | Offset error                                   | _         | _          | <±1        | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A10          | —    | Monotonicity                                   | _         | guaranteed | -          | —     | $VSS \leq VAIN \leq VREF$                                                                               |

| A20          | Vref | Reference voltage                              | 2.5V      | _          | Vdd + 0.3  | V     |                                                                                                         |

| A25          | VAIN | Analog input voltage                           | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                         |

| A30          | ZAIN | Recommended impedance of analog voltage source | _         | _          | 10.0       | kΩ    |                                                                                                         |

| A40          | IAD  | A/D conversion current (VDD)                   | _         | 180        | _          | μA    | Average current consumption when A/D is on. (Note 1)                                                    |

| A50          | IREF | VREF input current (Note 2)                    | 10        | _          | 1000       | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN.<br>To charge CHOLD see Section 7.1. |

|              |      |                                                | —         |            | 10         | μA    | During A/D Conversion cycle                                                                             |

These parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

Applicable Devices 710 71 711 715

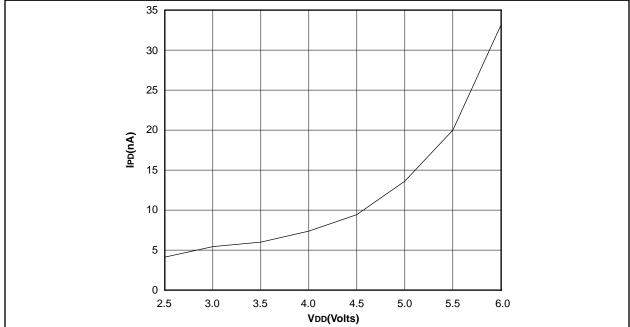

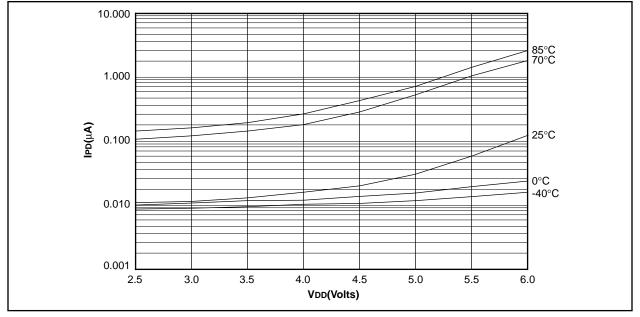

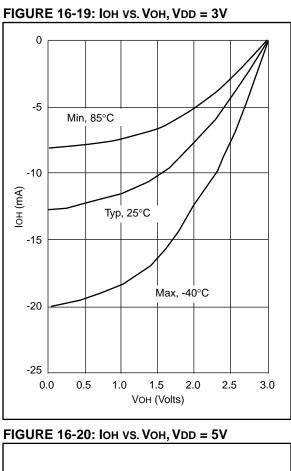

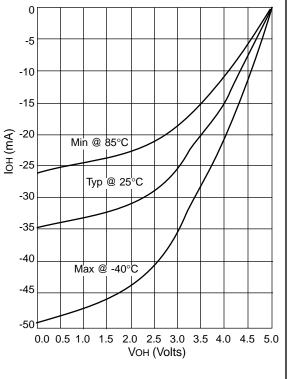

## 12.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C710 AND PIC16C711

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at,  $25^{\circ}$ C, while 'max' or 'min' represents (mean +3 $\sigma$ ) and (mean -3 $\sigma$ ) respectively where  $\sigma$  is standard deviation.

#### FIGURE 12-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 12-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

# PIC16C71X

Applicable Devices 710 71 711 715

## 13.0 ELECTRICAL CHARACTERISTICS FOR PIC16C715

#### Absolute Maximum Ratings †

|                                                                                                                    | Δ                    |

|--------------------------------------------------------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                                                                     |                      |

| Storage temperature                                                                                                |                      |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                       | 0.3∀ to (VDR + 0.3V) |

| Voltage on VDD with respect to Vss                                                                                 | ð tø +7.5V           |

| Voltage on MCLR with respect to Vss                                                                                | 0 to +14V            |

| Voltage on RA4 with respect to Vss                                                                                 | 0 to +14V            |

| Total power dissipation (Note 1)                                                                                   |                      |

| Maximum current out of Vss pin                                                                                     |                      |

| Maximum current into VDD pin                                                                                       | 250 mA               |

| Input clamp current, Iικ (VI < 0 or VI > VDD)                                                                      | ±20 mA               |

| Output clamp current, Ioк (Vo < 0 or Vo > Vbb)                                                                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                                                                         | 25 mA                |

| Maximum output current sourced by any I/O pin                                                                      |                      |

| Maximum current sunk by PORTA                                                                                      | 200 mA               |

| Maximum current sourced by PORTA                                                                                   | 200 mA               |

| Maximum current sunk by PORTB                                                                                      | 200 mA               |

| Maximum current sourced by PORTB.                                                                                  | 200 mA               |

| <b>Note 1:</b> Power dissipation is calculated as follows: Rdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD - VC |                      |

| † NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause perma                             | anent damage to the  |

TNOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### Applicable Devices 710 71 711 715

| 13.3 I | PIC16C71<br>PIC16C71<br>PIC16LC7   | 5-10<br>5-20<br>15-04 | (Comme<br>(Comme<br>(Comme | rcia<br>rcia<br>ercia   | il, Indus<br>il, Indus<br>il, Indus | strial,<br>strial,<br>strial)) |                                                     |

|--------|------------------------------------|-----------------------|----------------------------|-------------------------|-------------------------------------|--------------------------------|-----------------------------------------------------|

|        |                                    |                       |                            |                         |                                     |                                | nless otherwise stated)<br>TA ≤ +70°C (commercial)  |

|        |                                    | Operati               | ng tempe                   | alur                    | e 0°C<br>-40°                       |                                | TA $\leq$ +85°C (industrial)                        |

| DC CHA | RACTERISTICS                       |                       |                            |                         | -40°                                |                                | $TA \le +125^{\circ}C$ (extended)                   |

|        |                                    | Operati               | na voltaa                  | e Vd                    |                                     |                                | cribed in DC spec Section 13.1                      |

|        |                                    |                       | ction 13.2                 |                         |                                     |                                |                                                     |

| Param  | Characteristic                     | Sym                   | Min                        | Тур                     | Max                                 | Units                          | Conditions                                          |

| No.    |                                    | -                     |                            | t                       |                                     |                                |                                                     |

|        | Input Low Voltage                  |                       |                            |                         |                                     |                                |                                                     |

|        | I/O ports                          | VIL                   |                            |                         |                                     |                                |                                                     |

| D030   | with TTL buffer                    |                       | Vss                        | -                       | 0.5V                                | V                              |                                                     |

| D031   | with Schmitt Trigger buffer        |                       | Vss                        | -                       | 0.2VDD                              | v                              |                                                     |

| D032   | MCLR, RA4/T0CKI,OSC1               |                       | Vss                        | -                       | 0.2VDD                              | v                              | $ $ $\backslash$ $\langle$ $\checkmark$             |

|        | (in RC mode)                       |                       |                            |                         | 0.2100                              |                                |                                                     |

| D033   | OSC1 (in XT, HS and LP)            |                       | Vss                        | -                       | 0.3Vdd                              | 7 v/                           | Note1                                               |

|        | Input High Voltage                 |                       |                            |                         |                                     |                                | $\checkmark$                                        |

|        | I/O ports                          | Vін                   |                            | -                       | $\langle \setminus$                 |                                |                                                     |

| D040   | with TTL buffer                    |                       | 2.0                        | $\sim$                  | VDD                                 | ∕ v \                          | $4.5 \leq VDD \leq 5.5V$                            |

| D040A  |                                    |                       | 0.8Vdd                     | $\langle \cdot \rangle$ | VDD                                 | $\mathcal{N}$                  | For VDD > 5.5V or VDD < 4.5V                        |

| D041   | with Schmitt Trigger buffer        |                       | 0.8V0D                     |                         | VBD                                 | $\sim$                         | For entire VDD range                                |

| D042   | MCLR, RA4/T0CKI RB0/INT            |                       | 0.8VDD                     | $\searrow$              | Vpp \                               | V                              |                                                     |

| D042A  | OSC1 (XT, HS and LP)               |                       | 0,7VQD                     | <u>\-</u> `             | VDD                                 | V                              | Note1                                               |

| D043   | OSC1 (in RC mode)                  | ~                     | Q.9VDD                     |                         |                                     | V                              |                                                     |

| D070   | PORTB weak pull-up current         | PURB                  | 50                         | 25,0                    | 400                                 | μA                             | VDD = 5V, VPIN = VSS                                |

|        | Input Leakage Current (Notes 2, 3) | $\nearrow$            |                            | $\checkmark$            |                                     |                                |                                                     |

| D060   | I/O ports                          |                       |                            | -                       | ±1                                  | μA                             | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance |

| D061   | MCLR, RA4/T0CKI                    | $\langle \rangle$     | · -                        | -                       | ±5                                  | μA                             | $Vss \le VPIN \le VDD$                              |

| D063   | OSC1                               | $\sim$                | -                          | -                       | ±5                                  | μA                             | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and L            |

|        | $ \land \land \land \land \land$   | $\langle \rangle$     |                            |                         |                                     |                                | osc configuration                                   |

|        | Output Low Voltage                 |                       |                            |                         |                                     |                                |                                                     |

| D080   | I/O ports                          | Vol                   | -                          | -                       | 0.6                                 | V                              | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D080A  |                                    |                       | -                          | -                       | 0.6                                 |                                | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C        |

| D083   | OSC2/CLKOUT (RC osc config)        |                       | -                          | -                       | 0.6                                 | V                              | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D083A  | $(h) \rightarrow (h)$              |                       | -                          | -                       | 0.6                                 | V                              | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C        |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

# Applicable Devices71071711715

| DC CHARACTERISTICS |                                            |       | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ (extended)Operating voltage VDD range as described in DC spec Section 13.1and Section 13.2. |            |     |       |                                                                                                         |  |

|--------------------|--------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------|---------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Characteristic                             | Sym   | Min                                                                                                                                                                                                                                                                                                                                | Typ<br>+   | Max | Units | Conditions                                                                                              |  |

| NO.                | Output High Voltage                        |       |                                                                                                                                                                                                                                                                                                                                    | 1          |     |       |                                                                                                         |  |

| D090               | I/O ports (Note 3)                         | Vон   | Vdd - 0.7                                                                                                                                                                                                                                                                                                                          | -          | -   | V     | ІОН = -3.0 mA, VDp =\4.5V,<br>-40°С to +85°С                                                            |  |

| D090A              |                                            |       | Vdd - 0.7                                                                                                                                                                                                                                                                                                                          | -          | -   | V     | $IOH = -2.5 \text{ mA}, \text{VDD} = 4.5\text{V}, -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ |  |

| D092               | OSC2/CLKOUT (RC osc config)                |       | Vdd - 0.7                                                                                                                                                                                                                                                                                                                          | -          | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С tø +85°С                                                            |  |

| D092A              |                                            |       | Vdd - 0.7                                                                                                                                                                                                                                                                                                                          | -          | -   | V     | ION = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                           |  |

|                    | Capacitive Loading Specs on<br>Output Pins |       |                                                                                                                                                                                                                                                                                                                                    |            |     |       |                                                                                                         |  |

| D100               | OSC2 pin                                   | Cosc2 | -                                                                                                                                                                                                                                                                                                                                  | -          | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1.                                 |  |

| D101               | All I/O pins and OSC2 (in RC mode)         | Сю    | -                                                                                                                                                                                                                                                                                                                                  | <b>\</b> - | 50  | PF    | $\bigvee$                                                                                               |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin:

#### Applicable Devices 710 71 711 715

#### TABLE 13-7: A/D CONVERTER CHARACTERISTICS: PIC16LC715-04 (COMMERCIAL, INDUSTRIAL)

| Parameter<br>No. | Sym  | Characteristic                                         | Min       | Тур†       | Max                                   | Units     | Conditions                                           |

|------------------|------|--------------------------------------------------------|-----------|------------|---------------------------------------|-----------|------------------------------------------------------|

|                  | NR   | Resolution                                             | _         | —          | 8-bits                                | —         | $VREF = VDD,  VSS \le AIN \le VREF$                  |

|                  | Nint | Integral error                                         | _         |            | less than<br>±1 LSb                   | _         | $VREF = VDD,  VSS \le AIN \le VREF$                  |

|                  | Ndif | Differential error                                     | —         | —          | less than<br>±1 LSb                   | _         | $VREF = VDD, VSS \le AIN \le VREF$                   |

|                  | NFS  | Full scale error                                       | —         | —          | less than<br>±1 LSb                   | _         | $VREF = VDD, VSS \leq AIN \leq VREF$                 |

|                  | NOFF | Offset error                                           | —         |            | less than<br>±1 LSb                   | _         | VREF = VDD, VSS ≤ AIN ≤ VREF                         |

|                  |      | Monotonicity                                           | _         | guaranteed | _                                     | —         | VSS & AKT S VREF                                     |

|                  | Vref | Reference voltage                                      | 2.5V      | _          | Vdd + 0.3                             | V         |                                                      |

|                  | VAIN | Analog input voltage                                   | Vss - 0.3 | —          | Vref + 0.3                            | V         |                                                      |

|                  | ZAIN | Recommended<br>impedance of ana-<br>log voltage source | —         | _          | 10.0                                  | KΩ        |                                                      |

|                  | IAD  | A/D conversion cur-<br>rent (VDD)                      | _         | 90         | $\sim$                                | μÀ        | Average current consumption when A/D is on. (Note 1) |

|                  | IREF | VREF input current<br>(Note 2)                         | _         | - ~        | A A A A A A A A A A A A A A A A A A A | hnA<br>μA | During sampling<br>All other times                   |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

# PIC16C71X

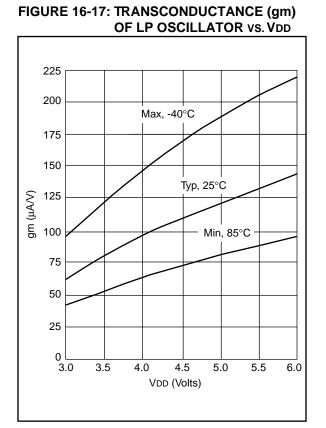

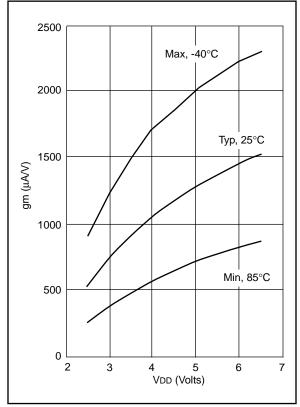

#### FIGURE 16-18: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

NOTES:

# **PIC16C71X**

| RA2/AN2                                                                | a                                     |

|------------------------------------------------------------------------|---------------------------------------|

|                                                                        |                                       |

| RA3/AN3/VREF                                                           | -                                     |

| RA4/T0CKI                                                              | 9                                     |

| RB0/INT                                                                | 9                                     |

| RB1                                                                    | -                                     |

|                                                                        | -                                     |

| RB2                                                                    | 9                                     |

| RB3                                                                    | 9                                     |

| RB4                                                                    |                                       |

|                                                                        | -                                     |

| RB5                                                                    | 9                                     |

| RB6                                                                    | 9                                     |

| RB7                                                                    | a                                     |

|                                                                        | -                                     |

| VDD                                                                    |                                       |

| Vss                                                                    | 9                                     |

| Pinout Descriptions                                                    |                                       |

| PIC16C71                                                               | 0                                     |

|                                                                        |                                       |

| PIC16C710                                                              | 9                                     |

| PIC16C711                                                              | 9                                     |

| PIC16C715                                                              | -                                     |

|                                                                        |                                       |

| PIR1 Register                                                          | 21                                    |

| POP                                                                    | 23                                    |

| POR                                                                    | 53 54                                 |

|                                                                        |                                       |

| Oscillator Start-up Timer (OST)                                        | 47, 53                                |

| Power Control Register (PCON)                                          | 54                                    |

| Power-on Reset (POR)                                                   | 3 57 58                               |

|                                                                        | 47 50                                 |

| Power-up Timer (PWRT)                                                  |                                       |

| Time-out Sequence                                                      | 54                                    |

| Time-out Sequence on Power-up                                          | 59                                    |

| TO                                                                     |                                       |

|                                                                        |                                       |

| POR bit                                                                | 22, 54                                |

| Port RB Interrupt                                                      | 63                                    |

| PORTA                                                                  |                                       |

|                                                                        |                                       |

| PORTA Register 1                                                       | 4, 15, 25                             |

| PORTB                                                                  | 57. 58                                |

| PORTB Register1                                                        | ,                                     |

|                                                                        |                                       |

| Power-down Mode (SLEEP)                                                |                                       |

| Prescaler, Switching Between Timer0 and WDT                            | 35                                    |

| PRO MATE <sup>®</sup> II Universal Programmer                          | 85                                    |

|                                                                        |                                       |

| Program Branches                                                       |                                       |

| Program Memory                                                         |                                       |

| Paging                                                                 | 23                                    |

| Program Memory Maps                                                    |                                       |

|                                                                        |                                       |

| PIC16C71                                                               | 11                                    |

| PIC16C710                                                              | 11                                    |

| PIC16C711                                                              | 11                                    |

|                                                                        |                                       |

| PIC16C715                                                              |                                       |

| Program Verification                                                   | 67                                    |

| PS0 bit                                                                |                                       |

| PS1 bit                                                                | -                                     |

|                                                                        |                                       |

| PS2 bit                                                                |                                       |

| PSA bit                                                                | 18                                    |

| PUSH                                                                   | 23                                    |