Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 36 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc710t-04-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | General Description                                                     |      |

|-------|-------------------------------------------------------------------------|------|

| 2.0   | PIC16C71X Device Varieties                                              | 5    |

| 3.0   | Architectural Overview                                                  |      |

| 4.0   | Memory Organization                                                     | . 11 |

| 5.0   | I/O Ports                                                               | . 25 |

| 6.0   | Timer0 Module                                                           | . 31 |

| 7.0   | Analog-to-Digital Converter (A/D) Module                                | . 37 |

| 8.0   | Special Features of the CPU                                             | . 47 |

| 9.0   | Instruction Set Summary                                                 | . 69 |

| 10.0  | Development Support                                                     | . 85 |

| 11.0  | Electrical Characteristics for PIC16C710 and PIC16C711                  |      |

| 12.0  | DC and AC Characteristics Graphs and Tables for PIC16C710 and PIC16C711 | 101  |

| 13.0  | Electrical Characteristics for PIC16C715                                |      |

| 14.0  | DC and AC Characteristics Graphs and Tables for PIC16C715               |      |

| 15.0  | Electrical Characteristics for PIC16C71                                 | 135  |

| 16.0  | DC and AC Characteristics Graphs and Tables for PIC16C71                | 147  |

| 17.0  | Packaging Information                                                   | 155  |

| Appen | dix A:                                                                  | 161  |

|       | dix B: Compatibility                                                    |      |

| Appen | dix C: What's New                                                       | 162  |

|       | dix D: What's Changed                                                   |      |

|       | -                                                                       |      |

| PIC16 | C71X Product Identification System                                      | 173  |

|       | ·                                                                       |      |

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

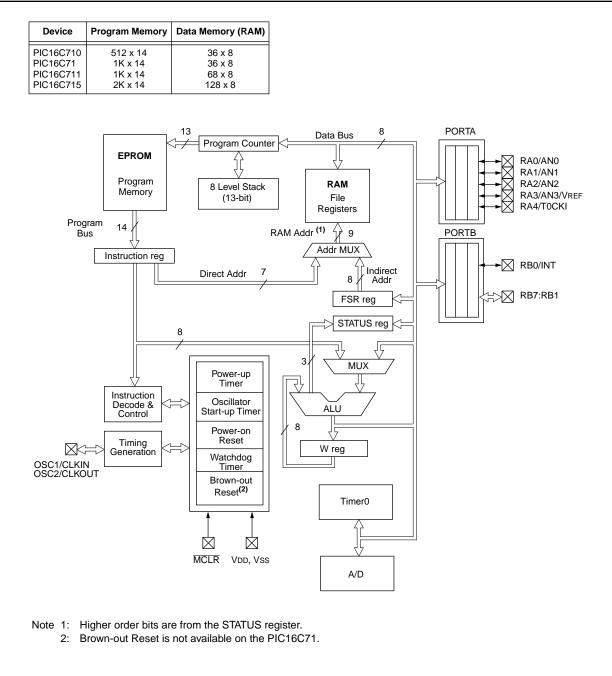

#### FIGURE 3-1: PIC16C71X BLOCK DIAGRAM

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name   | Bit 7                                                                                                    | Bit 6              | Bit 5         | Bit 4        | Bit 3                                                          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(1) |

|----------------------|--------|----------------------------------------------------------------------------------------------------------|--------------------|---------------|--------------|----------------------------------------------------------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |        |                                                                                                          |                    |               | •            | •                                                              |                  |               |           |                          |                                     |

| 00h <sup>(3)</sup>   | INDF   | Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 |                    |               |              |                                                                |                  |               |           |                          | 0000 0000                           |

| 01h                  | TMR0   | Timer0 mod                                                                                               | lule's register    | r             |              |                                                                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(3)</sup>   | PCL    | Program Co                                                                                               | ounter's (PC)      | Least Signif  | icant Byte   |                                                                |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(3)</sup>   | STATUS | IRP <sup>(5)</sup>                                                                                       | RP1 <sup>(5)</sup> | RP0           | TO           | PD                                                             | Z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(3)</sup>   | FSR    | Indirect data                                                                                            | a memory ad        | dress pointe  | r            |                                                                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA  | _                                                                                                        | —                  | —             | PORTA Dat    | a Latch whe                                                    | n written: PO    | RTA pins wh   | en read   | x 0000                   | u 0000                              |

| 06h                  | PORTB  | PORTB Dat                                                                                                | a Latch whe        | n written: PC | DRTB pins wł | nen read                                                       |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | —      | Unimpleme                                                                                                | nted               |               |              |                                                                |                  |               |           | —                        | —                                   |

| 08h                  | ADCON0 | ADCS1                                                                                                    | ADCS0              | (6)           | CHS1         | CHS0                                                           | GO/DONE          | ADIF          | ADON      | 00-0 0000                | 00-0 0000                           |

| 09h <sup>(3)</sup>   | ADRES  | A/D Result                                                                                               | Register           |               |              |                                                                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Ah <sup>(2,3)</sup> | PCLATH | _                                                                                                        | —                  | _             | Write Buffer | for the uppe                                                   | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <b>(3)</b>       | INTCON | GIE                                                                                                      | ADIE               | TOIE          | INTE         | RBIE                                                           | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| Bank 1               |        |                                                                                                          |                    |               |              |                                                                |                  |               |           |                          |                                     |

| 80h <sup>(3)</sup>   | INDF   | Addressing                                                                                               | this location      | uses conten   | ts of FSR to | address dat                                                    | a memory (no     | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION | RBPU                                                                                                     | INTEDG             | TOCS          | TOSE         | PSA                                                            | PS2              | PS1           | PS0       | 1111 1111                | 1111 1111                           |

| 82h <sup>(3)</sup>   | PCL    | Program Co                                                                                               | ounter's (PC)      | Least Signif  | icant Byte   |                                                                |                  |               |           | 0000 0000                | 0000 0000                           |

| 83h <sup>(3)</sup>   | STATUS | IRP <sup>(5)</sup>                                                                                       | RP1 <sup>(5)</sup> | RP0           | TO           | PD                                                             | z                | DC            | с         | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(3)</sup>   | FSR    | Indirect data                                                                                            | a memory ad        | dress pointe  | er           |                                                                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA  | —                                                                                                        | —                  | —             | PORTA Dat    | a Direction F                                                  | Register         |               |           | 1 1111                   | 1 1111                              |

| 86h                  | TRISB  | PORTB Data Direction Control Register 1111 1111                                                          |                    |               |              |                                                                |                  |               | 1111 1111 |                          |                                     |

| 87h <sup>(4)</sup>   | PCON   | —                                                                                                        | —                  | —             | _            | —                                                              | _                | POR           | BOR       | dd                       | uu                                  |

| 88h                  | ADCON1 | —                                                                                                        | —                  | _             | _            | _                                                              | —                | PCFG1         | PCFG0     | 00                       | 00                                  |

| 89h <sup>(3)</sup>   | ADRES  | A/D Result Register xxxx x                                                                               |                    |               |              |                                                                |                  |               | uuuu uuuu |                          |                                     |

| 8Ah <sup>(2,3)</sup> | PCLATH | _                                                                                                        | —                  | —             | Write Buffer | Write Buffer for the upper 5 bits of the Program Counter0 0000 |                  |               |           |                          | 0 0000                              |

| 8Bh <sup>(3)</sup>   | INTCON | GIE                                                                                                      | ADIE               | TOIE          | INTE         | RBIE                                                           | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

#### TABLE 4-1: PIC16C710/71/711 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: These registers can be addressed from either bank.

4: The PCON register is not physically implemented in the PIC16C71, read as '0'.

5: The IRP and RP1 bits are reserved on the PIC16C710/71/711, always maintain these bits clear.

6: Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

### 5.0 I/O PORTS

### Applicable Devices 710 71 711 715

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

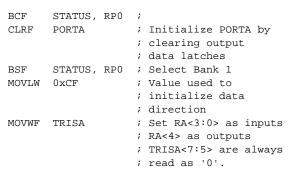

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 5-1: INITIALIZING PORTA

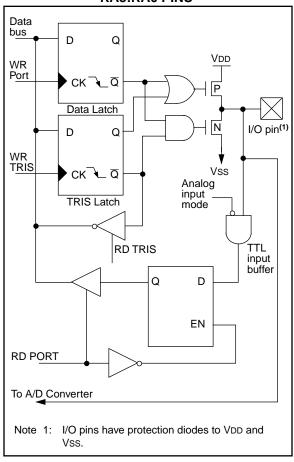

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 PINS

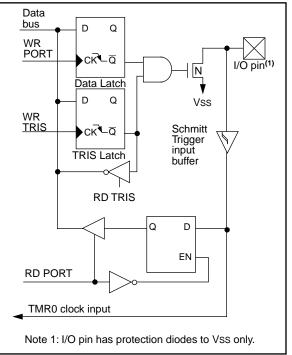

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

| Address   | Name   | Bit 7 | Bit 6                                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------|---------------------------------------------------|-------|-------|-------|-------|-----------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7   | RB6                                               | RB5   | RB4   | RB3   | RB2   | RB1       | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB | PORTB Data Direction Register 1111 1111 1111 1111 |       |       |       |       | 1111 1111 |       |                          |                           |

| 81h, 181h | OPTION | RBPU  | INTEDG                                            | TOCS  | TOSE  | PSA   | PS2   | PS1       | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 8.2 <u>Oscillator Configurations</u>

#### 8.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

## 8.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

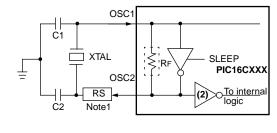

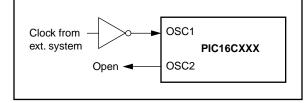

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-4). The PIC16CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 8-5).

#### FIGURE 8-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 8-1 and Table 8-1 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: The buffer is on the OSC2 pin.

#### FIGURE 8-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 8-1: CERAMIC RESONATORS, PIC16C71

| Ranges Tested:                                                          |                               |                                         |                                         |  |  |  |

|-------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode                                                                    | Freq                          | OSC1                                    | OSC2                                    |  |  |  |

| ХТ                                                                      | 455 kHz<br>2.0 MHz<br>4.0 MHz | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                                                      | 8.0 MHz<br>16.0 MHz           | 15 - 68 pF<br>10 - 47 pF                | 15 - 68 pF<br>10 - 47 pF                |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                               |                                         |                                         |  |  |  |

| Resonator                                                               | s Used:                       |                                         |                                         |  |  |  |

| 455 kHz                                                                 | Panasonic EFO-A455K04B ± 0.3% |                                         |                                         |  |  |  |

| 2.0 MHz                                                                 | Murata Erie CS                | Murata Erie CSA2.00MG ± 0.5%            |                                         |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5%  |                                         |                                         |  |  |  |

| 8.0 MHz                                                                 | Murata Erie CSA8.00MT ± 0.5%  |                                         |                                         |  |  |  |

| 16.0 MHz                                                                | Murata Erie CSA16.00MX ± 0.5% |                                         |                                         |  |  |  |

| All resonators used did not have built-in capacitors.                   |                               |                                         |                                         |  |  |  |

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16C71

| Mode                                                                    | Freq    | OSC1        | OSC2        |  |

|-------------------------------------------------------------------------|---------|-------------|-------------|--|

| LP                                                                      | 32 kHz  | 33 - 68 pF  | 33 - 68 pF  |  |

|                                                                         | 200 kHz | 15 - 47 pF  | 15 - 47 pF  |  |

| XT                                                                      | 100 kHz | 47 - 100 pF | 47 - 100 pF |  |

|                                                                         | 500 kHz | 20 - 68 pF  | 20 - 68 pF  |  |

|                                                                         | 1 MHz   | 15 - 68 pF  | 15 - 68 pF  |  |

|                                                                         | 2 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |

|                                                                         | 4 MHz   | 15 - 33 pF  | 15 - 33 pF  |  |

| HS                                                                      | 8 MHz   | 15 - 47 pF  | 15 - 47 pF  |  |

|                                                                         | 20 MHz  | 15 - 47 pF  | 15 - 47 pF  |  |

| These values are for design guidance only. See notes at bottom of page. |         |             |             |  |

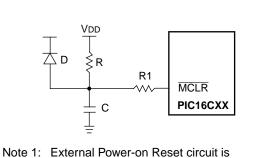

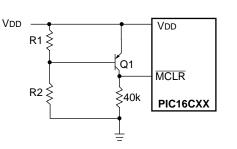

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

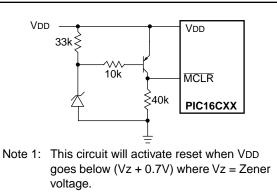

#### FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

### FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### 8.5 Interrupts

### Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |  |  |  |  |

|-------------------------------------------------------|--|--|--|--|

| External interrupt RB0/INT                            |  |  |  |  |

| TMR0 overflow interrupt                               |  |  |  |  |

| PORTB change interrupts (pins RB7:RB4)                |  |  |  |  |

| A/D Interrupt                                         |  |  |  |  |

| The interrupt control register (INTCON) records indi- |  |  |  |  |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~    |                  |                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No   | l<br>r<br>C<br>F | For the PIC16C71<br>If an interrupt occurs while the Global Inter-<br>rupt Enable (GIE) bit is being cleared, the<br>GIE bit may unintentionally be re-enabled<br>by the user's Interrupt Service Routine (the<br>RETFIE instruction). The events that<br>would cause this to occur are: |  |  |  |  |  |

|      | 1                | . An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                                               |  |  |  |  |  |

|      | 2                | 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.                                                                                                                                                                                              |  |  |  |  |  |

|      | 3                | 3. The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts.                 |  |  |  |  |  |

|      |                  | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                                               |  |  |  |  |  |

| LOOP | BCF              | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                                          |  |  |  |  |  |

|      |                  | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                                            |  |  |  |  |  |

|      | GOTO             | LOOP ; NO, try again                                                                                                                                                                                                                                                                     |  |  |  |  |  |

:

Yes, continue

with program

flow

#### 8.6 <u>Context Saving During Interrupts</u>

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 8-1 stores and restores the STATUS and W registers. The user register, STATUS\_TEMP, must be defined in bank 0.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### EXAMPLE 8-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W |

|----------------|--------------------|----------------------------------------------------------------------------------------|

| SWAPP          | •                  | L                                                                                      |

| MOVWF          | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                         |

| :              |                    |                                                                                        |

| :(ISR)         |                    |                                                                                        |

| :              |                    |                                                                                        |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                                                      |

|                |                    | ;(sets bank to original state)                                                         |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                           |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                           |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                    |

|                |                    |                                                                                        |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                         |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [label] RLF f,d                                                                                                                                                                                             | Syntax:           | [label] RRF f,d                                                                                                                                                                                                                                                      |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                          | Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                             |  |  |  |  |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                                                                                |  |  |  |  |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.                                                         |  |  |  |  |

|                   |                                                                                                                                                                                                             |                   |                                                                                                                                                                                                                                                                      |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                                                                                    |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                          |  |  |  |  |

|                   | Decode Read register data Write to dest                                                                                                                                                                     |                   | Decode Read register 'f' Vite to dest                                                                                                                                                                                                                                |  |  |  |  |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                                                                           |  |  |  |  |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | Before Instruction       REG1       =       1110       0110         C       =       0       -         After Instruction       -       -       -         REG1       =       1110       0110         W       =       0111       0011         C       =       0       - |  |  |  |  |

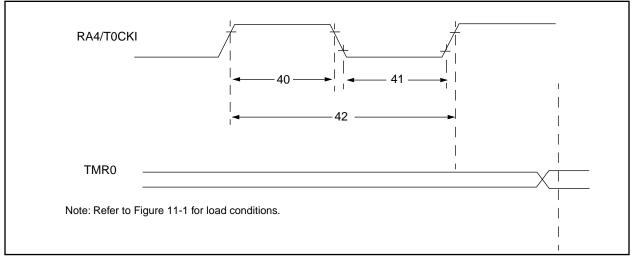

#### FIGURE 11-6: TIMER0 EXTERNAL CLOCK TIMINGS

#### TABLE 11-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                | Min                                            | Тур†         | Max   | Units | Conditions                         |                |

|--------------|-----------|-------------------------------|------------------------------------------------|--------------|-------|-------|------------------------------------|----------------|

| 40           | Tt0H      | T0CKI High Pulse Width        | No Prescaler                                   | 0.5Tcy + 20* | —     |       | ns                                 | Must also meet |

|              |           |                               | With Prescaler                                 | 10*          | —     | _     | ns                                 | parameter 42   |

| 41           | Tt0L      | T0CKI Low Pulse Width         | No Prescaler                                   | 0.5TCY + 20* | —     | _     | ns                                 | Must also meet |

|              |           |                               | With Prescaler                                 | 10*          | —     | _     | ns                                 | parameter 42   |

| 42           | Tt0P      | T0CKI Period                  | Greater of:<br>20 ns or <u>Tcy + 40</u> *<br>N | _            | _     | ns    | N = prescale value<br>(2, 4,, 256) |                |

| 48           | Tcke2tmrl | Delay from external clock edg | 2Tosc                                          | —            | 7Tosc | —     |                                    |                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C71X

### Applicable Devices 710 71 711 715

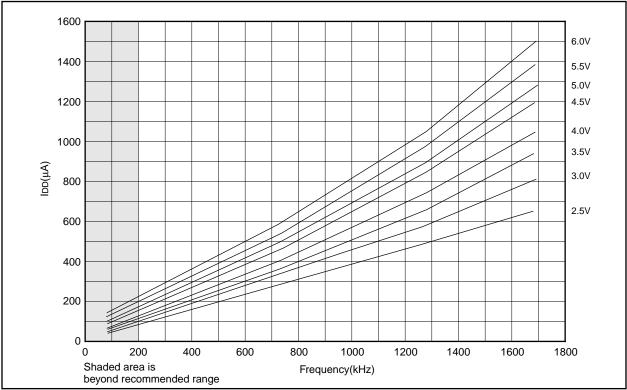

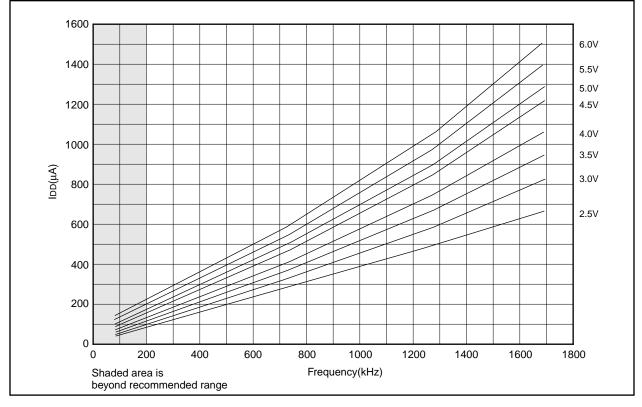

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

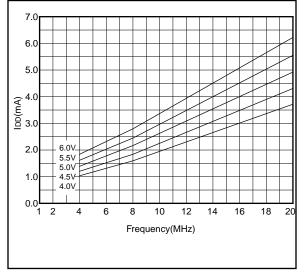

### FIGURE 12-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

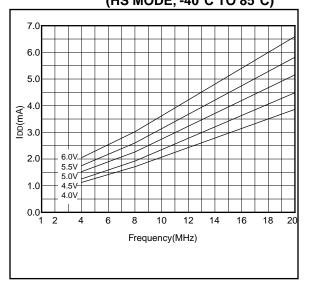

#### FIGURE 12-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

| OSC |                               | PIC16C715-04                                                                        | •                             | PIC16C715-10                                                                                                   |              | PIC16C715-20                                                           |              | PIC16LC715-04                                                                     |                               | PIC16C715/JW                                                                      |

|-----|-------------------------------|-------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------|

| RC  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max.                                         | IDD:<br>IPD: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max. | IDD:<br>IPD: | 2.5V to 5.5V<br>2.0 mA typ. at 3.0V<br>0.9 μA typ. at 3V<br>4 MHz max.            | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.               |

| хт  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 μA typ. at 4V<br>4 MHz max.                                         | IDD:<br>NPD: | 4.5V to 5.5V<br>2.7 mA typ. at 5.5V<br>1.5 µA typ. at 4V<br>4.MHz max, | IDD:<br>IPD: | 2.5V to 5.5V<br>2.0 mA typ. at 3.0V<br>0.9 μA typ. at 3V<br>4 MHz max.            | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>5 mA max. at 5.5V<br>21 μA max. at 4V<br>4 MHz max.               |

| HS  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>13.5 mA typ. at 5.5V<br>1.5 μA typ. at 4.5V<br>4 MHz max.           | VDD:<br>IDD:<br>IPD:<br>Freq: | <ul> <li>4.5V to 5.5V</li> <li>30 mA max. at 5.5V</li> <li>1.5 μA typ. at 4.5V</li> <li>10 MHz max.</li> </ul> | · /·         | 4.5V to 5,5V<br>30 mA max. at 5.5V<br>1.5 μA typ. at 4.5V              | Do no        | nt use in HS mode                                                                 | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.5V to 5.5V<br>30 mA max. at 5.5V<br>1.5 μA typ. at 4.5V<br>10 MHz max.          |

| LP  | VDD:<br>IDD:<br>IPD:<br>Freq: | 4.0V to 5.5V<br>52.5 μA typ. at 32 kHz, 4.0V<br>0.9 μA typ. at 4.0V<br>200 kHz max. | Do no                         | t use in LP mode                                                                                               | Do no        | ot use in LP mode                                                      | 1/ /         | 2.SV to 5.5V<br>48 μA max. at 32 kHz, 3.0V<br>5.0 μA max. at 3.0V<br>200 kHz max. | VDD:<br>IDD:<br>IPD:<br>Freq: | 2.5V to 5.5V<br>48 μA max. at 32 kHz, 3.0V<br>5.0 μA max. at 3.0V<br>200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

**TABLE 13-1:**

CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

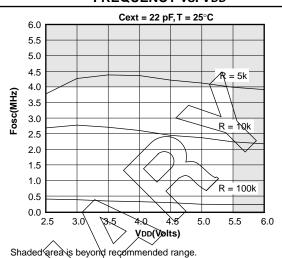

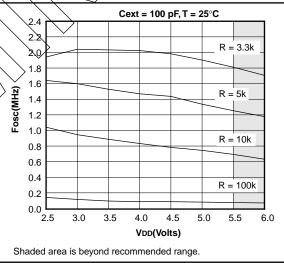

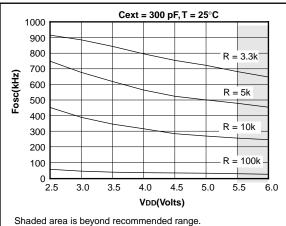

#### FIGURE 14-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

# FIGURE 14-6: TYPICAL RC OSCILLATOR

#### FIGURE 14-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

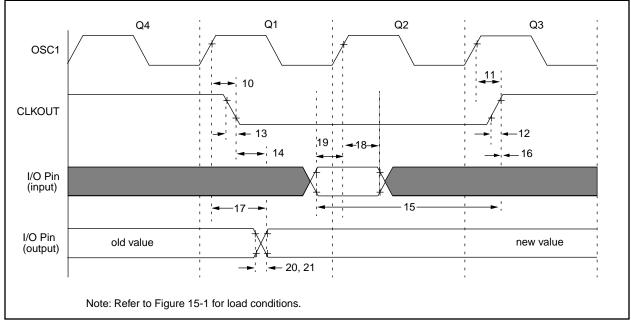

#### FIGURE 15-3: CLKOUT AND I/O TIMING

| TABLE 15-3: CLKOUT AND I/O TIMING REQUIREMENTS | TABLE 15-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|------------------------------------------------|-------------|-------------------------------------------|

|------------------------------------------------|-------------|-------------------------------------------|

| Parameter<br>No. | Sym      | Characteristic                                            |                    | Min | Тур†        | Мах      | Units  | Conditions |

|------------------|----------|-----------------------------------------------------------|--------------------|-----|-------------|----------|--------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                                          |                    | _   | 15          | 30       | ns     | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>                  | —                  | 15  | 30          | ns       | Note 1 |            |

| 12*              | TckR     | CLKOUT rise time                                          | —                  | 5   | 15          | ns       | Note 1 |            |

| 13*              | TckF     | CLKOUT fall time                                          |                    | —   | 5           | 15       | ns     | Note 1     |

| 14*              | TckL2ioV | CLKOUT $\downarrow$ to Port out vali                      | —                  | —   | 0.5Tcy + 20 | ns       | Note 1 |            |

| 15*              | TioV2ckH | Port in valid before CLKOU                                | 0.25Tcy + 25       | —   |             | ns       | Note 1 |            |

| 16*              | TckH2iol | Port in hold after CLKOUT                                 | 0                  | —   |             | ns       | Note 1 |            |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid         |                    | -   | _           | 80 - 100 | ns     |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                           | PIC16 <b>C</b> 71  | 100 | —           |          | ns     |            |

|                  |          | Port input invalid (I/O in hold time)                     | PIC16 <b>LC</b> 71 | 200 | —           | _        | ns     |            |

| 19*              | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in setup time) |                    | 0   | —           | -        | ns     |            |

| 20*              | TioR     | Port output rise time                                     | PIC16 <b>C</b> 71  | —   | 10          | 25       | ns     |            |

|                  |          |                                                           | PIC16 <b>LC</b> 71 | —   | —           | 60       | ns     |            |

| 21*              | TioF     | Port output fall time PIC16 <b>C</b> 71                   |                    | —   | 10          | 25       | ns     |            |

|                  |          |                                                           | PIC16 <b>LC</b> 71 | —   | —           | 60       | ns     |            |

| 22††*            | Tinp     | INT pin high or low time                                  | 20                 | —   |             | ns       |        |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                                   | 20                 | —   | _           | ns       |        |            |

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

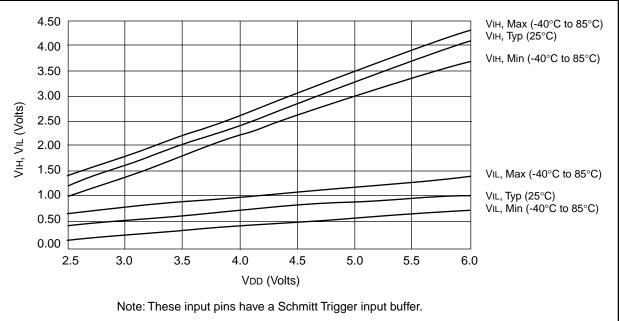

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) VS. VDD

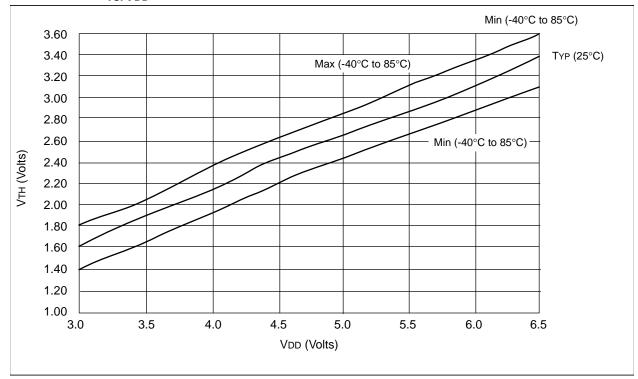

#### FIGURE 16-11: VTH (INPUT THRESHOLD VOLTAGE) OF OSC1 INPUT (IN XT, HS, AND LP MODES) VS. VDD

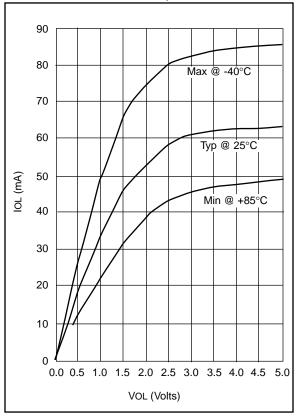

FIGURE 16-22: IOL VS. VOL, VDD = 5V

# **PIC16C71X**

| Figure 14-6:  | Typical RC Oscillator Frequency vs.                                                              |

|---------------|--------------------------------------------------------------------------------------------------|

| riguio i i o. | VDD126                                                                                           |

| Figure 14-7:  | Typical RC Oscillator Frequency vs.<br>VDD126                                                    |

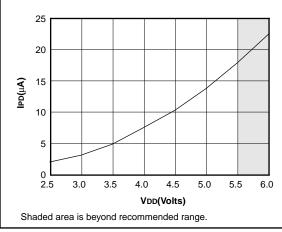

| Figure 14-8:  | Typical IPD vs. VDD Brown-out Detect<br>Enabled (RC Mode)127                                     |

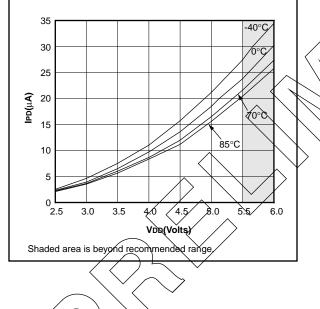

| Figure 14-9:  | Maximum IPD vs. VDD Brown-out Detect<br>Enabled                                                  |

| Figure 14-10: | (85°C to -40°C, RC Mode)                                                                         |

| Figure 14-11: | Maximum IPD vs. Timer1 Enabled<br>(32 kHz, RC0/RC1 = 33 pF/33 pF,                                |

| Figure 14-12: | 85°C to -40°C, RC Mode)                                                                          |

| Figure 14-13: | (RC Mode @ 22 pF, 25 C) 128<br>Maximum IDD vs. Frequency<br>(RC Mode @ 22 pF, -40°C to 85°C) 128 |

| Figure 14-14: | (RC Mode @ 22 pF, -40 C to 85 C) 128<br>Typical IDD vs. Frequency<br>(RC Mode @ 100 pF, 25°C)    |

| Figure 14-15: | Maximum IDD vs. Frequency<br>(RC Mode @ 100 pF, -40°C to 85°C) 129                               |

| Figure 14-16: | Typical IDD vs. Frequency<br>(RC Mode @ 300 pF, 25°C)                                            |

| Figure 14-17: | Maximum IDD vs. Frequency<br>(RC Mode @ 300 pF, -40°C to 85°C) 130                               |

| Figure 14-18: | Typical IDD vs. Capacitance @ 500 kHz<br>(RC Mode)131                                            |

| Figure 14-19: | Transconductance(gm) of<br>HS Oscillator vs. VDD131                                              |

| Figure 14-20: | Transconductance(gm) of<br>LP Oscillator vs. VDD131                                              |

| Figure 14-21: | Transconductance(gm) of<br>XT Oscillator vs. VDD131                                              |

| Figure 14-22: | Typical XTAL Startup Time vs.<br>VDD (LP Mode, 25°C)132                                          |

| Figure 14-23: | Typical XTAL Startup Time vs.<br>VDD (HS Mode, 25°C)132                                          |

| Figure 14-24: | Typical XTAL Startup Time vs.<br>VDD (XT Mode, 25°C)132                                          |

| Figure 14-25: | Typical IDD vs. Frequency<br>(LP Mode, 25°C)133                                                  |

| Figure 14-26: | Maximum IDD vs. Frequency<br>(LP Mode, 85°C to -40°C)                                            |

| Figure 14-27: | Typical IDD vs. Frequency<br>(XT Mode, 25°C)133                                                  |

| Figure 14-28: | Maximum IDD vs. Frequency<br>(XT Mode, -40°C to 85°C)133                                         |

| Figure 14-29: | Typical IDD vs. Frequency<br>(HS Mode, 25°C)134                                                  |

| Figure 14-30: | Maximum IDD vs. Frequency<br>(HS Mode, -40°C to 85°C)134                                         |

| Figure 15-1:  | Load Conditions140                                                                               |

| Figure 15-2:  | External Clock Timing141                                                                         |

| Figure 15-3:  | CLKOUT and I/O Timing142                                                                         |

| Figure 15-4:  | Reset, Watchdog Timer, Oscillator<br>Start-up Timer and Power-up Timer                           |

| Figure 45 5   | Timing                                                                                           |

| Figure 15-5:  | Timer0 External Clock Timings                                                                    |

| Figure 15-6:  | A/D Conversion Timing146                                                                         |

| Figure 16-1:  | Typical RC Oscillator Frequency vs.                                                              |

| Figure 16-2:  | Temperature                                                                                      |

| Figure 10.0   | VDD147                                                                                           |

| Figure 16-3:  | Typical RC Oscillator Frequency vs.<br>VDD147                                                    |

| Figure 16-4:   | Typical RC Oscillator Frequency vs.<br>VDD                     |

|----------------|----------------------------------------------------------------|

| Figure 16-5:   | Typical lpd vs. VDD Watchdog Timer<br>Disabled 25°C148         |

| Figure 16-6:   | Typical Ipd vs. VDD Watchdog Timer<br>Enabled 25°C 148         |

| Figure 16-7:   | Maximum Ipd vs. VDD Watchdog<br>Disabled149                    |

| Figure 16-8:   | Maximum Ipd vs. VDD Watchdog<br>Enabled149                     |

| Figure 16-9:   | Vth (Input Threshold Voltage) of<br>I/O Pins vs. VDD149        |

| Figure 16-10:  | VIH, VIL of MCLR, TOCKI and OSC1<br>(in RC Mode) vs. VDD       |

| Figure 16-11:  | Vтн (Input Threshold Voltage)<br>of OSC1 Input (in XT, HS, and |

|                | LP Modes) vs. VDD 150                                          |

| Figure 16-12:  | Typical IDD vs. Freq (Ext Clock, 25°C) 151                     |

| Figure 16-13:  | Maximum, IDD vs. Freq (Ext Clock,<br>-40° to +85°C)151         |

| Figure 16-14:  | Maximum IDD vs. Freq with A/D Off                              |

|                | (Ext Clock, -55° to +125°C) 152                                |

| Figure 16-15:  | WDT Timer Time-out Period vs. VDD 152                          |

| Figure 16-16:  | Transconductance (gm) of                                       |

| E: 10.17       | HS Oscillator vs. VDD 152                                      |

| Figure 16-17:  | Transconductance (gm) of<br>LP Oscillator vs. VDD              |

| Figure 16-18:  | Transconductance (gm) of                                       |

| . igure te tet | XT Oscillator vs. VDD 153                                      |

| Figure 16-19:  | IOH vs. VOH, VDD = 3V 153                                      |

| Figure 16-20:  | IOH vs. VOH, VDD = 5V 153                                      |

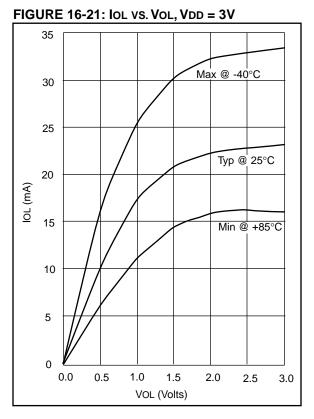

| Figure 16-21:  | IOL vs. VOL, VDD = 3V                                          |

| Figure 16-22:  | IOL vs. VOL, VDD = 5V 154                                      |

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.