#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 68 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711-04-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | General Description                                                     |      |

|-------|-------------------------------------------------------------------------|------|

| 2.0   | PIC16C71X Device Varieties                                              | 5    |

| 3.0   | Architectural Overview                                                  |      |

| 4.0   | Memory Organization                                                     | . 11 |

| 5.0   | I/O Ports                                                               | . 25 |

| 6.0   | Timer0 Module                                                           | . 31 |

| 7.0   | Analog-to-Digital Converter (A/D) Module                                | . 37 |

| 8.0   | Special Features of the CPU                                             | . 47 |

| 9.0   | Instruction Set Summary                                                 | . 69 |

| 10.0  | Development Support                                                     | . 85 |

| 11.0  | Electrical Characteristics for PIC16C710 and PIC16C711                  |      |

| 12.0  | DC and AC Characteristics Graphs and Tables for PIC16C710 and PIC16C711 | 101  |

| 13.0  | Electrical Characteristics for PIC16C715                                |      |

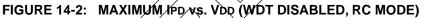

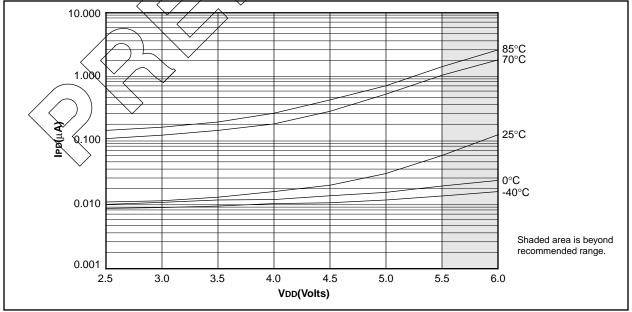

| 14.0  | DC and AC Characteristics Graphs and Tables for PIC16C715               |      |

| 15.0  | Electrical Characteristics for PIC16C71                                 | 135  |

| 16.0  | DC and AC Characteristics Graphs and Tables for PIC16C71                | 147  |

| 17.0  | Packaging Information                                                   | 155  |

| Appen | dix A:                                                                  | 161  |

|       | dix B: Compatibility                                                    |      |

| Appen | dix C: What's New                                                       | 162  |

|       | dix D: What's Changed                                                   |      |

|       | -                                                                       |      |

| PIC16 | C71X Product Identification System                                      | 173  |

|       | ·                                                                       |      |

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# <sup>(4)</sup> | SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type                  | Description                                                                                                                                                                                              |

|-----------------|-------------|-----------------------------|--------------|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 16          | 18                          | 16           | I             | ST/CMOS <sup>(3)</sup>          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT     | 15          | 17                          | 15           | 0             | _                               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp        | 4           | 4                           | 4            | I/P           | ST                              | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|                 |             |                             |              |               |                                 | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0         | 17          | 19                          | 17           | I/O           | TTL                             | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1         | 18          | 20                          | 18           | I/O           | TTL                             | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2         | 1           | 1                           | 1            | I/O           | TTL                             | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF    | 2           | 2                           | 2            | I/O           | TTL                             | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI       | 3           | 3                           | 3            | I/O           | ST                              | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                         |

|                 |             |                             |              |               |                                 | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT         | 6           | 7                           | 6            | I/O           | TTL/ST <sup>(1)</sup>           | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1             | 7           | 8                           | 7            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB2             | 8           | 9                           | 8            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB3             | 9           | 10                          | 9            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB4             | 10          | 11                          | 10           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB5             | 11          | 12                          | 11           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB6             | 12          | 13                          | 12           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7             | 13          | 14                          | 13           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss             | 5           | 4, 6                        | 5            | Р             | —                               | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd             | 14          | 15, 16                      | 14           | Р             | —                               | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I = inp |             | O = outp<br>— = Not         |              |               | /O = input/out<br>TTL = TTL inp | I I                                                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The PIC16C71 is not available in SSOP package.

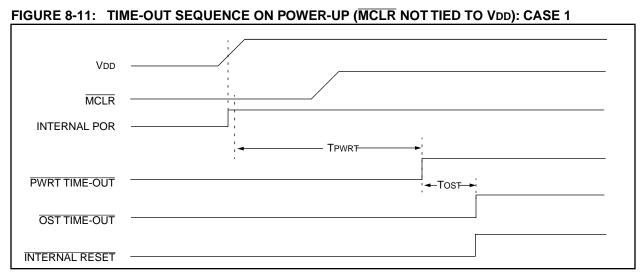

FIGURE 8-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

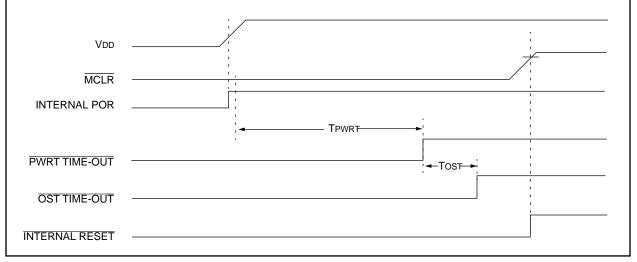

### FIGURE 8-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

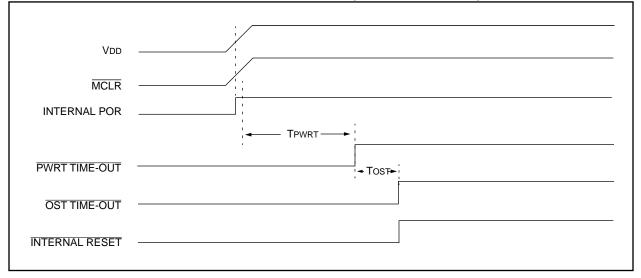

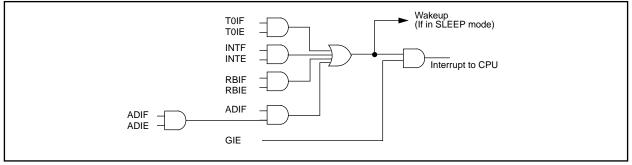

### FIGURE 8-17: INTERRUPT LOGIC, PIC16C710, 71, 711

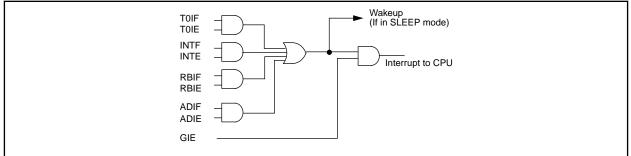

### FIGURE 8-18: INTERRUPT LOGIC, PIC16C715

#### 8.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 8.8 for details on SLEEP mode.

#### 8.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TOIE (INTCON<5>). (Section 6.0)

#### 8.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

For the PIC16C71 Note: if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

|                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                          | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                     |

|--------------------------|-------------------|-------------------|--------------------------------------------|-------------------|---------------------------------------|

| OSC1 /                   |                   |                   |                                            |                   |                                       |

| CLKOUT ③                 | (4)               |                   |                                            | /                 |                                       |

| INT pin                  |                   | 1                 | 1<br>1<br>1<br>1                           |                   | 1 1<br>1 1<br>1 1<br>1 1              |

| INTF flag<br>(INTCON<1>) |                   |                   | Interrupt Latency (2)                      |                   |                                       |

| GIE bit<br>(INTCON<7>)   |                   |                   |                                            |                   |                                       |

| INSTRUCTION              | FLOW              |                   | ,<br>, , , , , , , , , , , , , , , , , , , |                   | · · · · · · · · · · · · · · · · · · · |

| PC                       | PC                | PC+1              | PC+1                                       | X 0004h           | X 0005h                               |

| Instruction (<br>fetched | Inst (PC)         | Inst (PC+1)       | _                                          | Inst (0004h)      | Inst (0005h)                          |

| Instruction {            | Inst (PC-1)       | Inst (PC)         | Dummy Cycle                                | Dummy Cycle       | Inst (0004h)                          |

|                          |                   |                   |                                            |                   |                                       |

### FIGURE 8-19: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode. 4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                           | Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                     |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                        |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                            |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

|                   |                                                                                                                                                                                                             |                   |                                                                                                                                                                                                              |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                            |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                            |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                  |

|                   | Decode Read Process Write to data dest                                                                                                                                                                      |                   | Decode Read register data Virite to dest                                                                                                                                                                     |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                   |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                         |

### SLEEP

| [ label ]                                                       | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| None                                                            |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | ,                                                                                                                                                                                                                                                 | ller,                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                        |

| TO, PD                                                          |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |

| 00                                                              | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                                                                                 | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |

| cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with | ime-out s<br>ndog Time<br>cleared.<br>essor is pu<br>n the oscil                                                                                                                                                                                  | tatus bit, <sup>*</sup><br>er and its<br>ut into SLI<br>llator stop                                                                                                                                                                                                                                                                                                                                  | TO is<br>pres-<br>EEP<br>ped.                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                                               |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1                                                               |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |

| Q1                                                              | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |

| Decode                                                          | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                                                                                  | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |

| SLEEP                                                           |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow \overline{TO},$<br>$0 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$<br>$\boxed{00} 0000$<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1 $Q2\boxed{Decode} NOP$ | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |

| SUBLW             | Subtract              | W from             | Literal                                                                    |

|-------------------|-----------------------|--------------------|----------------------------------------------------------------------------|

| Syntax:           | [ label ]             | SUBL               | N k                                                                        |

| Operands:         | $0 \le k \le 25$      | 55                 |                                                                            |

| Operation:        | k - (W) $\rightarrow$ | • (W)              |                                                                            |

| Status Affected:  | C, DC, Z              |                    |                                                                            |

| Encoding:         | 11                    | 110x               | kkkk kkkł                                                                  |

| Description:      | ment meth             | od) from           | ubtracted (2's complet<br>the eight bit literal 'k<br>I in the W register. |

| Words:            | 1                     |                    |                                                                            |

| Cycles:           | 1                     |                    |                                                                            |

| Q Cycle Activity: | Q1                    | Q2                 | Q3 Q4                                                                      |

|                   | Decode                | Read<br>literal 'k | Process Write to data                                                      |

| Example 1:        | SUBLW                 | 0x02               |                                                                            |

|                   | Before In:            | structior          | ı                                                                          |

|                   |                       | W =<br>C =<br>Z =  | 1<br>?<br>?                                                                |

|                   | After Inst            | ruction            |                                                                            |

|                   |                       | W =<br>C =<br>Z =  | 1<br>1; result is positive<br>0                                            |

| Example 2:        | Before In:            | structior          | n                                                                          |

|                   |                       | W =<br>C =<br>Z =  | 2<br>?<br>?                                                                |

|                   | After Inst            | ruction            |                                                                            |

|                   |                       | W =<br>C =<br>Z =  | 0<br>1; result is zero<br>1                                                |

| Example 3:        | Before In             | structior          | ı                                                                          |

| Example 0.        |                       | W =                | 3                                                                          |

| Example 0.        |                       |                    |                                                                            |

| Example 0.        |                       | C =<br>Z =         | ?<br>?                                                                     |

|                   | After Inst            | Z =                |                                                                            |

|                   | After Inst            | Z =                |                                                                            |

|                   | After Inst            | Z =<br>ruction     | ?                                                                          |

| SUBWF             | Subtract                                                          | W from f                     |                                   |               |

|-------------------|-------------------------------------------------------------------|------------------------------|-----------------------------------|---------------|

| Syntax:           | [ label ]                                                         | SUBWF                        | f,d                               |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ | 7                            |                                   |               |

| Operation:        | (f) - (W) –                                                       | → (dest)                     |                                   |               |

| Status Affected:  | C, DC, Z                                                          |                              |                                   |               |

| Encoding:         | 00                                                                | 0010                         | dfff                              | ffff          |

| Description:      | Subtract (2<br>ister from r<br>stored in th<br>result is sto      | egister 'f'. I<br>e W regist | f 'd' is 0 the<br>er. If 'd' is 1 | result is the |

| Words:            | 1                                                                 |                              |                                   |               |

| Cycles:           | 1                                                                 |                              |                                   |               |

| Q Cycle Activity: | Q1                                                                | Q2                           | Q3                                | Q4            |

|                   | Decode                                                            | Read                         | Process                           | Write to      |

|                   |                                                                   | register 'f'                 | data                              | dest          |

| Example 1:        | SUBWF                                                             | reg1,1                       |                                   |               |

|                   | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 3                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?                                 |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 1                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>1; result is                 | positive      |

|                   | Z                                                                 | =                            | 0                                 | poolito       |

| Example 2:        | Before Ins                                                        | struction                    |                                   |               |

|                   | REG1                                                              | =                            | 2                                 |               |

|                   | W<br>C                                                            | =                            | 2<br>?                            |               |

|                   | Z                                                                 | =                            | ?<br>?                            |               |

|                   | After Instr                                                       | uction                       |                                   |               |

|                   | REG1                                                              | =                            | 0                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | C<br>Z                                                            | =                            | 1; result is                      | zero          |

| Example 3:        | Eefore Ins                                                        | _                            | 1                                 |               |

|                   | REG1                                                              | -                            | 1                                 |               |

|                   | W                                                                 | =                            | 2                                 |               |

|                   | С                                                                 | =                            | ?                                 |               |

|                   | Z<br>After Instr                                                  | =                            | ?                                 |               |

|                   |                                                                   |                              |                                   |               |

|                   | REG1<br>W                                                         | =                            | 0xFF<br>2                         |               |

|                   | С                                                                 | =                            | 0; result is                      | negative      |

|                   | Z                                                                 | =                            | 0                                 |               |

| SWAPF             | Swap Ni                        | bbles in                                             | f                            |                   |

|-------------------|--------------------------------|------------------------------------------------------|------------------------------|-------------------|

| Syntax:           | [ label ]                      | SWAPF                                                | i,d                          |                   |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$ | 27                                                   |                              |                   |

| Operation:        |                                | $\rightarrow$ (dest<) $\rightarrow$ (dest<)          |                              |                   |

| Status Affected:  | None                           |                                                      |                              |                   |

| Encoding:         | 00                             | 1110                                                 | dfff                         | ffff              |

| Description:      | ter 'f' are e<br>result is pl  | r and lowe<br>exchanged<br>laced in W<br>is placed i | . If 'd' is 0<br>register. I | the<br>f 'd' is 1 |

| Words:            | 1                              |                                                      |                              |                   |

| Cycles:           | 1                              |                                                      |                              |                   |

| Q Cycle Activity: | Q1                             | Q2                                                   | Q3                           | Q4                |

|                   | Decode                         | Read<br>register 'f'                                 | Process<br>data              | Write to<br>dest  |

| Example           | SWAPF                          | REG,                                                 | 0                            |                   |

|                   | Before In                      | struction                                            |                              |                   |

|                   |                                | REG1                                                 | = 0xA                        | 45                |

|                   | After Inst                     | ruction                                              |                              |                   |

|                   |                                | REG1<br>W                                            | = 0x4<br>= 0x5               |                   |

| TRIS             | Load TRIS Register                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                                   |

| Example          |                                                                                                                                                                                     |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |

|                  |                                                                                                                                                                                     |

| XORLW             | Exclusi         | ve OR Li                                  | iteral wit      | h W           |

|-------------------|-----------------|-------------------------------------------|-----------------|---------------|

| Syntax:           | [label]         | XORL                                      | V k             |               |

| Operands:         | $0 \le k \le 2$ | 255                                       |                 |               |

| Operation:        | (W) .XO         | $R.k \rightarrow (N)$                     | N)              |               |

| Status Affected:  | Z               |                                           |                 |               |

| Encoding:         | 11              | 1010                                      | kkkk            | kkkk          |

| Description:      | XOR'ed v        | ents of the<br>vith the ei<br>t is placed | ght bit lite    | ral 'k'.      |

| Words:            | 1               |                                           |                 |               |

| Cycles:           | 1               |                                           |                 |               |

| Q Cycle Activity: | Q1              | Q2                                        | Q3              | Q4            |

|                   | Decode          | Read<br>literal 'k'                       | Process<br>data | Write to<br>W |

| Example:          | XORLW           | 0xAF                                      |                 |               |

|                   | Before I        | nstructio                                 | n               |               |

|                   |                 | W =                                       | 0xB5            |               |

|                   | After Ins       | After Instruction                         |                 |               |

|                   |                 | W =                                       | 0x1A            |               |

|                   |                 |                                           |                 |               |

| XORWF             | Exclusiv                                                         | e OR W                   | with f                         |                     |

|-------------------|------------------------------------------------------------------|--------------------------|--------------------------------|---------------------|

| Syntax:           | [label]                                                          | XORWF                    | f,d                            |                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                       |                                |                     |

| Operation:        | (W) .XOF                                                         | $R.\left(f\right)\to($   | dest)                          |                     |

| Status Affected:  | Z                                                                |                          |                                |                     |

| Encoding:         | 00                                                               | 0110                     | dfff                           | ffff                |

| Description:      | Exclusive<br>register wi<br>result is st<br>is 1 the res         | th registe<br>ored in th | r 'f'. If 'd' is<br>e W regist | 0 the<br>er. If 'd' |

| Words:            | 1                                                                |                          |                                |                     |

| Cycles:           | 1                                                                |                          |                                |                     |

| Q Cycle Activity: | Q1                                                               | Q2                       | Q3                             | Q4                  |

|                   | Decode                                                           | Read<br>register<br>'f'  | Process<br>data                | Write to dest       |

| Example           | XORWF                                                            | REG                      | 1                              |                     |

|                   | Before In                                                        | struction                | 1                              |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | AF<br>B5            |

|                   | After Inst                                                       | ruction                  |                                |                     |

|                   |                                                                  | REG<br>W                 | 0/1                            | 1A<br>B5            |

### 11.5 Timing Diagrams and Specifications

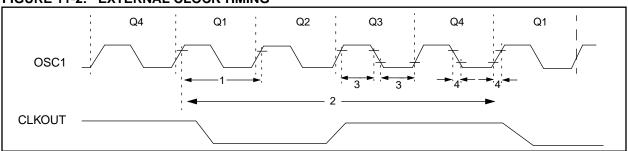

### FIGURE 11-2: EXTERNAL CLOCK TIMING

### TABLE 11-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym                                 | Characteristic                  | Min       | Тур† | Мах        | Units             | Conditions                             |

|------------------|-------------------------------------|---------------------------------|-----------|------|------------|-------------------|----------------------------------------|

|                  | Fosc                                | External CLKIN Frequency        | DC        | _    | 4          | MHz               | XT osc mode                            |

|                  |                                     | (Note 1)                        | DC        | —    | 4          | MHz               | HS osc mode (-04)                      |

|                  |                                     |                                 | DC        | —    | 10         | MHz               | HS osc mode (-10)                      |

|                  |                                     |                                 | DC        | —    | 20         | MHz               | HS osc mode (-20)                      |

|                  |                                     |                                 | DC        | —    | 200        | kHz               | LP osc mode                            |

|                  |                                     | Oscillator Frequency            | DC        | _    | 4          | MHz               | RC osc mode                            |

|                  |                                     | (Note 1)                        | 0.1       | —    | 4          | MHz               | XT osc mode                            |

|                  |                                     |                                 | 4<br>5    | —    | 20<br>200  | MHz<br>kHz        | HS osc mode<br>LP osc mode             |

| 1                | Tosc                                | External CLKIN Period           | 250       | _    | _          | ns                | XT osc mode                            |

|                  |                                     | (Note 1)                        | 250       | —    | _          | ns                | HS osc mode (-04)                      |

|                  |                                     | 100                             | —         | _    | ns         | HS osc mode (-10) |                                        |

|                  |                                     | 50                              | —         | _    | ns         | HS osc mode (-20) |                                        |

|                  |                                     |                                 | 5         | —    | _          | μs                | LP osc mode                            |

|                  |                                     | Oscillator Period               | 250       |      | _          | ns                | RC osc mode                            |

|                  |                                     | (Note 1)                        | 250       | —    | 10,000     | ns                | XT osc mode                            |

|                  |                                     |                                 | 250       | —    | 250        | ns                | HS osc mode (-04)                      |

|                  |                                     |                                 | 100<br>50 | _    | 250<br>250 | ns<br>ns          | HS osc mode (-10)<br>HS osc mode (-20) |

|                  |                                     |                                 | 5         | _    | _          | μs                | LP osc mode                            |

| 2                | Тсү                                 | Instruction Cycle Time (Note 1) | 200       |      | DC         | ns                | Tcy = 4/Fosc                           |

|                  | TosL, External Clock in (OSC1) High | 50                              | _         |      | ns         | XT oscillator     |                                        |

|                  | TosH                                | or Low Time                     | 2.5       | _    | _          | μs                | LP oscillator                          |

|                  |                                     |                                 | 10        | _    | _          | ns                | HS oscillator                          |

| 4                | TosR,                               | External Clock in (OSC1) Rise   | _         | _    | 25         | ns                | XT oscillator                          |

|                  | TosF                                | or Fall Time                    | _         | —    | 50         | ns                | LP oscillator                          |

|                  |                                     |                                 | _         |      | 15         | ns                | HS oscillator                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C710/711.

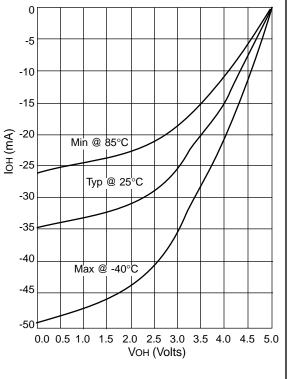

### Applicable Devices 710 71 711 715

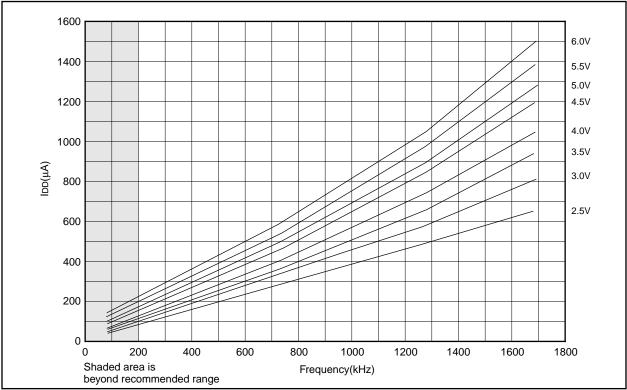

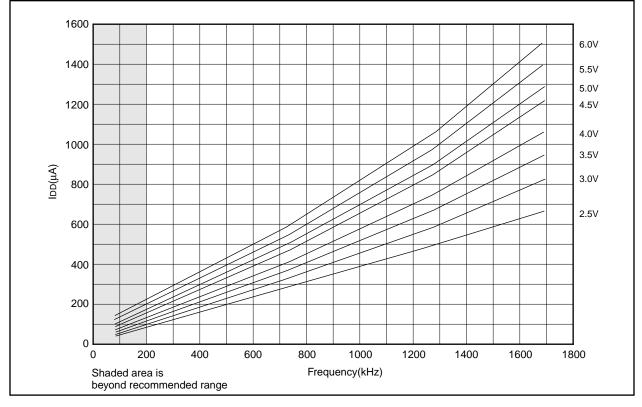

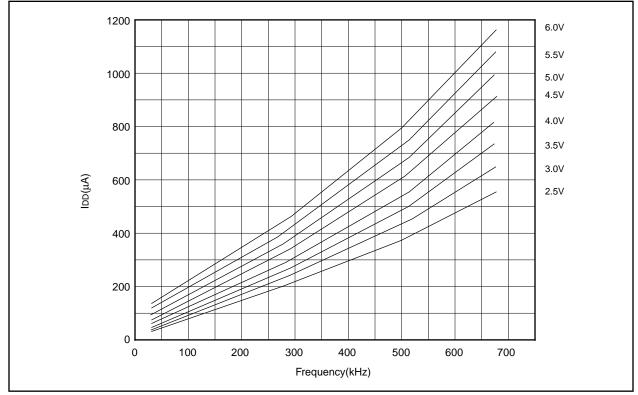

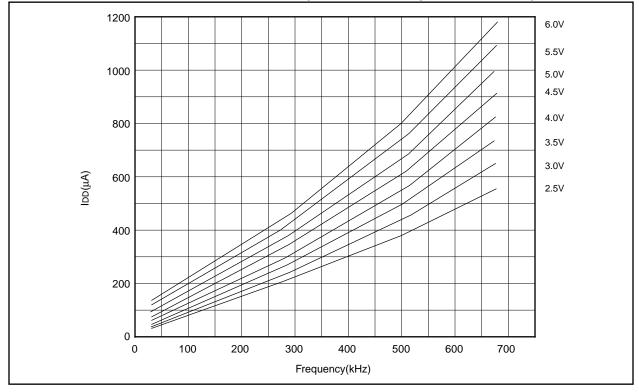

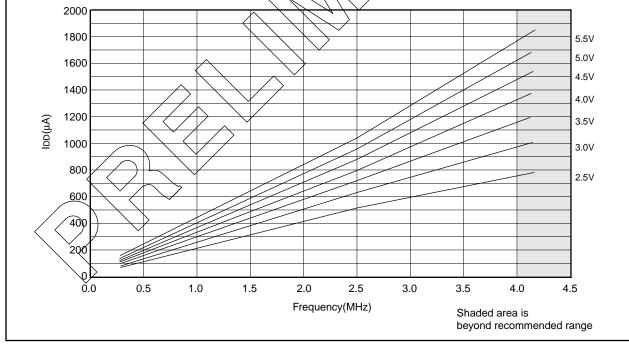

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

## Applicable Devices 710 71 711 715

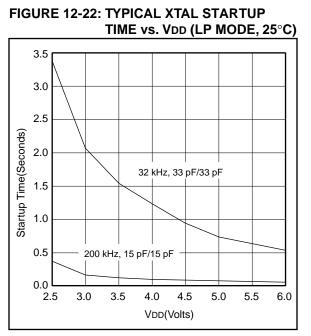

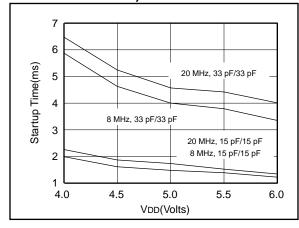

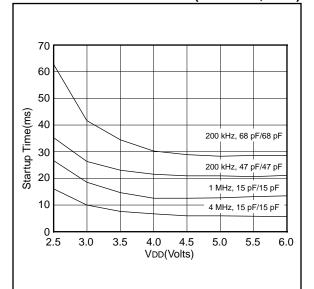

FIGURE 12-23: TYPICAL XTAL STARTUP TIME vs. VDD (HS MODE, 25°C)

### FIGURE 12-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

|                  |                 | <b>A B</b>       | <b>a b</b>       |

|------------------|-----------------|------------------|------------------|

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

| LP               | 32 kHz          | 33 pF            | 33 pF            |

|                  | 200 kHz         | 15 pF            | 15 pF            |

| ХТ               | 200 kHz         | 47-68 pF         | 47-68 pF         |

|                  | 1 MHz           | 15 pF            | 15 pF            |

|                  | 4 MHz           | 15 pF            | 15 pF            |

| HS               | 4 MHz           | 15 pF            | 15 pF            |

|                  | 8 MHz           | 15-33 pF         | 15-33 pF         |

|                  | 20 MHz          | 15-33 pF         | 15-33 pF         |

|                  |                 |                  |                  |

| Crystals<br>Used |                 |                  |                  |

| 32 kHz           | Epson C-00      | ± 20 PPM         |                  |

| 200 kHz          | STD XTL 2       | ± 20 PPM         |                  |

| 1 MHz            | ECS ECS-1       | ± 50 PPM         |                  |

| 4 MHz            | ECS ECS-4       | ± 50 PPM         |                  |

| 8 MHz            | EPSON CA        | ± 30 PPM         |                  |

| 20 MHz           | EPSON CA        | ± 30 PPM         |                  |

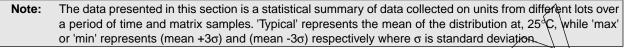

### 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C715

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

### FIGURE 14-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

### 15.2 DC Characteristics: PIC16LC71-04 (Commercial, Industrial)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)<br>OOperating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |                                                                  |      |      |                 |               |                |                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|-----------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                                                                                                                     | Characteristic                                                   | Sym  | Min  | Тур†            | Max           | Units          | Conditions                                                                                                                                                              |

| D001                                                                                                                                                                                                             | Supply Voltage                                                   | Vdd  | 3.0  | -               | 6.0           | V              | XT, RC, and LP osc configuration                                                                                                                                        |

| D002*                                                                                                                                                                                                            | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -    | 1.5             | -             | V              |                                                                                                                                                                         |

| D003                                                                                                                                                                                                             | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -    | Vss             | -             | V              | See section on Power-on Reset for details                                                                                                                               |

| D004*                                                                                                                                                                                                            | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD | 0.05 | -               | -             | V/ms           | See section on Power-on Reset for details                                                                                                                               |

| D010                                                                                                                                                                                                             | Supply Current (Note 2)                                          | IDD  | -    | 1.4             | 2.5           | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                           |

| D010A                                                                                                                                                                                                            |                                                                  |      | -    | 15              | 32            | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                         |

| D020<br>D021<br>D021A                                                                                                                                                                                            | Power-down Current<br>(Note 3)                                   | IPD  | -    | 5<br>0.6<br>0.6 | 20<br>9<br>12 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

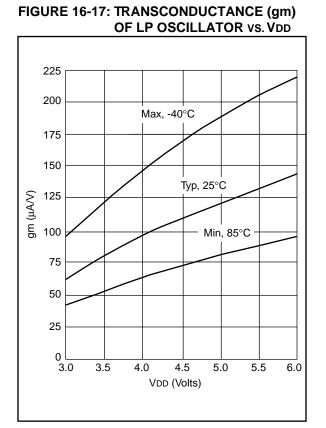

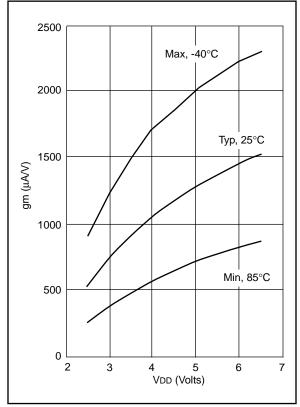

### FIGURE 16-18: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

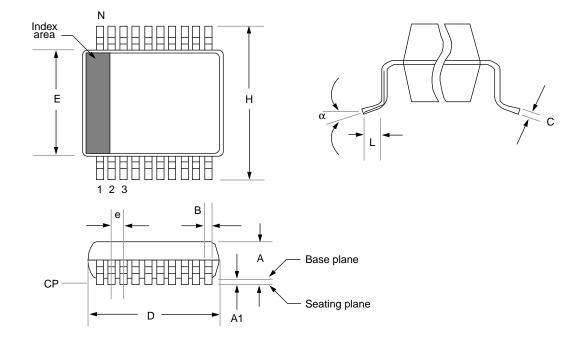

### 17.4 20-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

|        | Package Group: Plastic SSOP |             |           |       |        |           |  |

|--------|-----------------------------|-------------|-----------|-------|--------|-----------|--|

|        |                             | Millimeters |           |       | Inches |           |  |

| Symbol | Min                         | Мах         | Notes     | Min   | Max    | Notes     |  |

| α      | 0°                          | <b>8</b> °  |           | 0°    | 8°     |           |  |

| А      | 1.730                       | 1.990       |           | 0.068 | 0.078  |           |  |

| A1     | 0.050                       | 0.210       |           | 0.002 | 0.008  |           |  |

| В      | 0.250                       | 0.380       |           | 0.010 | 0.015  |           |  |

| С      | 0.130                       | 0.220       |           | 0.005 | 0.009  |           |  |

| D      | 7.070                       | 7.330       |           | 0.278 | 0.289  |           |  |

| E      | 5.200                       | 5.380       |           | 0.205 | 0.212  |           |  |

| е      | 0.650                       | 0.650       | Reference | 0.026 | 0.026  | Reference |  |

| Н      | 7.650                       | 7.900       |           | 0.301 | 0.311  |           |  |

| L      | 0.550                       | 0.950       |           | 0.022 | 0.037  |           |  |

| Ν      | 20                          | 20          |           | 20    | 20     |           |  |

| CP     | -                           | 0.102       |           | -     | 0.004  |           |  |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

- 2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

- 3: This outline conforms to JEDEC MS-026.

### **APPENDIX A:**

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (1K now as opposed to 512 before) and register file (68 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.