Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711-04e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |  |  |

|---------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|--|--|

| Clock   | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |  |  |

|         | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |  |  |

| Memory  | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |  |  |

|         | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |  |  |

|         | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |  |  |

|         | Capture/Compare/PWM<br>Module(s)                | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |  |  |

|         | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | —                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |  |  |

|         | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |  |  |

|         | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |  |  |

|         | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |  |  |

|         | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |  |  |

|         | Voltage Range (Volts)                           | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-6.0                    | 3.0-5.5                    |  |  |

| eatures | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |

|         | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |

|         | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |  |  |

### TABLE 1-1: PIC16C71X FAMILY OF DEVICES

|            |                                                 | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|------------|-------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory     | EPROM Program Memory<br>(x14 words)             | 4K                          | 4K                                        | 8K                          | 8K                                        |

|            | Data Memory (bytes)                             | 192                         | 192                                       | 376                         | 376                                       |

|            | Timer Module(s)                                 | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| eripherals | Capture/Compare/PWM<br>Module(s)                | 2                           | 2                                         | 2                           | 2                                         |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|            | Parallel Slave Port                             | —                           | Yes                                       | —                           | Yes                                       |

|            | A/D Converter (8-bit) Channels                  | 5                           | 8                                         | 5                           | 8                                         |

|            | Interrupt Sources                               | 11                          | 12                                        | 11                          | 12                                        |

|            | I/O Pins                                        | 22                          | 33                                        | 22                          | 33                                        |

|            | Voltage Range (Volts)                           | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| atures     | In-Circuit Serial Programming                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|            | Brown-out Reset                                 | Yes                         | Yes                                       | Yes                         | Yes                                       |

|            | Packages                                        | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C71X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C710 | 512 x 14          | 36 x 8      |

| PIC16C71  | 1K x 14           | 36 x 8      |

| PIC16C711 | 1K x 14           | 68 x 8      |

| PIC16C715 | 2K x 14           | 128 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# <sup>(4)</sup> | SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type                  | Description                                                                                                                                                                                              |

|-----------------|-------------|-----------------------------|--------------|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 16          | 18                          | 16           | I             | ST/CMOS <sup>(3)</sup>          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT     | 15          | 17                          | 15           | 0             | _                               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp        | 4           | 4                           | 4            | I/P           | ST                              | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|                 |             |                             |              |               |                                 | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0         | 17          | 19                          | 17           | I/O           | TTL                             | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1         | 18          | 20                          | 18           | I/O           | TTL                             | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2         | 1           | 1                           | 1            | I/O           | TTL                             | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF    | 2           | 2                           | 2            | I/O           | TTL                             | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI       | 3           | 3                           | 3            | I/O           | ST                              | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                         |

|                 |             |                             |              |               |                                 | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT         | 6           | 7                           | 6            | I/O           | TTL/ST <sup>(1)</sup>           | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1             | 7           | 8                           | 7            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB2             | 8           | 9                           | 8            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB3             | 9           | 10                          | 9            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB4             | 10          | 11                          | 10           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB5             | 11          | 12                          | 11           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB6             | 12          | 13                          | 12           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7             | 13          | 14                          | 13           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss             | 5           | 4, 6                        | 5            | Р             | —                               | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd             | 14          | 15, 16                      | 14           | Р             | —                               | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I = inp |             | O = outp<br>— = Not         |              |               | /O = input/out<br>TTL = TTL inp | I I                                                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The PIC16C71 is not available in SSOP package.

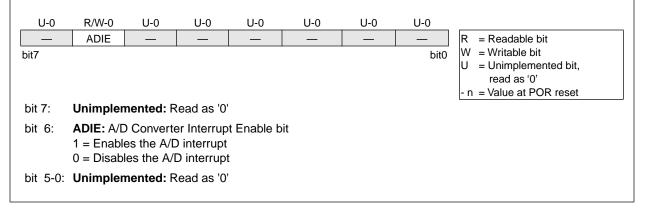

#### 4.2.2.4 PIE1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual enable bits for the Peripheral interrupts.

#### FIGURE 4-10: PIE1 REGISTER (ADDRESS 8Ch)

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

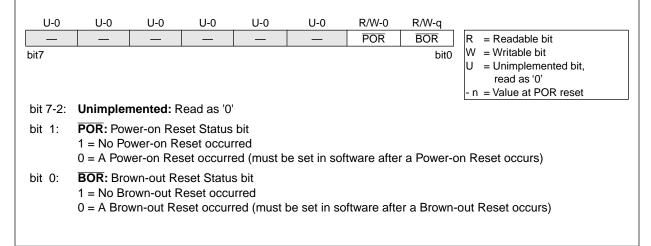

#### 4.2.2.6 PCON REGISTER

#### Applicable Devices71071711715

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset (BOR) condition from a Power-on Reset condition. For the PIC16C715 the PCON register also contains status bits MPEEN and PER. MPEEN reflects the value of the MPEEN bit in the configuration word. PER indicates a parity error reset has occurred. Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### FIGURE 4-12: PCON REGISTER (ADDRESS 8Eh), PIC16C710/711

#### FIGURE 4-13: PCON REGISTER (ADDRESS 8Eh), PIC16C715

| R-U<br>MPEEN | U-0                                         | U-0        | U-0        | U-0  | R/W-1                   | R/W-0       | R/W-q<br>BOR <sup>(1)</sup> | R = Readable bit                                                                      |

|--------------|---------------------------------------------|------------|------------|------|-------------------------|-------------|-----------------------------|---------------------------------------------------------------------------------------|

| bit7         |                                             |            |            |      |                         |             | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:       | MPEEN: I<br>Reflects the                    |            |            |      | Status bit<br>bit, MPEE | N           |                             |                                                                                       |

| bit 6-3:     | Unimplen                                    | nented: R  | ead as '0' |      |                         |             |                             |                                                                                       |

| bit 2:       | <b>PER</b> : Mer<br>1 = No Er<br>0 = Progra | ror occurr | ed         |      |                         | must be s   | et in softwa                | re after a Parity Error Reset)                                                        |

| bit 1:       | <b>POR:</b> Pow<br>1 = No Po<br>0 = A Pow   | wer-on Re  | eset occur | red  | e set in sof            | tware afte  | er a Power-c                | on Reset occurs)                                                                      |

| bit 0:       | <b>BOR:</b> Bro<br>1 = No Bro<br>0 = A Bro  | own-out R  | eset occu  | rred | be set in sc            | oftware aft | er a Brown-                 | out Reset occurs)                                                                     |

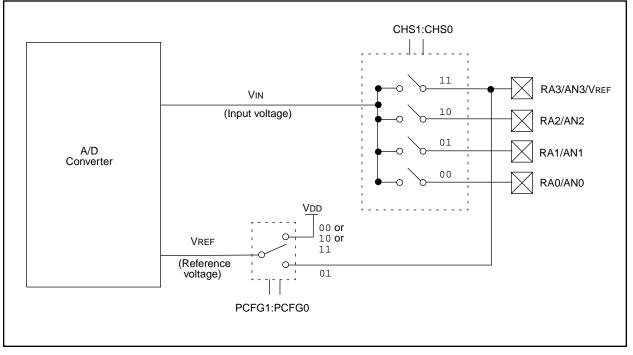

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 7-4.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 7.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- Set GIE bit

- 3. Wait the required acquisition time.

2. Configure A/D interrupt (if desired):

4. Start conversion:

Clear ADIF bit

Set ADIE bit

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 7-4: A/D BLOCK DIAGRAM

#### 7.4 <u>A/D Conversions</u>

Example 7-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0). **Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 7-2: A/D CONVERSION

| BSF    | STATUS,     | RP0        | ; Select Bank 1                                          |

|--------|-------------|------------|----------------------------------------------------------|

| CLRF   | ADCON1      |            | ; Configure A/D inputs                                   |

| BCF    | STATUS,     | RP0        | ; Select Bank 0                                          |

| MOVL   | W 0xCl      |            | ; RC Clock, A/D is on, Channel 0 is selected             |

| MOVW   | F ADCON0    |            | ;                                                        |

| BSF    | INTCON,     | ADIE       | ; Enable A/D Interrupt                                   |

| BSF    | INTCON,     | GIE        | ; Enable all interrupts                                  |

|        |             |            |                                                          |

| Ensure | that the re | equired sa | ampling time for the selected input channel has elapsed. |

Then the conversion may be started.

;

;;

;

| BSF | ADCON0, GO | ; Start A/D Conversion                              |

|-----|------------|-----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit      |

| :   |            | ; is cleared upon completion of the A/D Conversion. |

#### 8.5 Interrupts

#### Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |  |  |  |

|-------------------------------------------------------|--|--|--|

| External interrupt RB0/INT                            |  |  |  |

| TMR0 overflow interrupt                               |  |  |  |

| PORTB change interrupts (pins RB7:RB4)                |  |  |  |

| A/D Interrupt                                         |  |  |  |

| The interrupt control register (INTCON) records indi- |  |  |  |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~    |                  |                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No   | l<br>r<br>(<br>t | For the PIC16C71<br>If an interrupt occurs while the Global Inter-<br>rupt Enable (GIE) bit is being cleared, the<br>GIE bit may unintentionally be re-enabled<br>by the user's Interrupt Service Routine (the<br>RETFIE instruction). The events that<br>would cause this to occur are: |  |  |  |  |  |

|      | 1                | . An instruction clears the GIE bit while<br>an interrupt is acknowledged.                                                                                                                                                                                                               |  |  |  |  |  |

|      | 2                | . The program branches to the Interrupt vector and executes the Interrupt Service Routine.                                                                                                                                                                                               |  |  |  |  |  |

|      | 3                | . The Interrupt Service Routine com-<br>pletes with the execution of the RET-<br>FIE instruction. This causes the GIE<br>bit to be set (enables interrupts), and<br>the program returns to the instruction<br>after the one which was meant to dis-<br>able interrupts.                  |  |  |  |  |  |

|      |                  | Perform the following to ensure that inter-<br>upts are globally disabled:                                                                                                                                                                                                               |  |  |  |  |  |

| LOOP | BCF              | INTCON, GIE ; Disable global<br>; interrupt bit                                                                                                                                                                                                                                          |  |  |  |  |  |

|      |                  | INTCON, GIE ; Global interrupt<br>; disabled?                                                                                                                                                                                                                                            |  |  |  |  |  |

|      | GOTO             | LOOP ; NO, try again                                                                                                                                                                                                                                                                     |  |  |  |  |  |

:

Yes, continue

with program

flow

#### TABLE 9-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | Э    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIEI |        | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL AN |        | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| OUDLIN     |        |                              |        |     |        |        |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# PIC16C71X

| BCF               | Bit Clear f                            | BTFSC             | Bit Test, Skip if Clear                                                       |

|-------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] BCF f,b               | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                    |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$   | Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                             |

| Operation:        | $0 \rightarrow (f < b >)$              | Operation:        | skip if (f <b>) = 0</b>                                                       |

| Status Affected:  | None                                   | Status Affected:  | None                                                                          |

| Encoding:         | 01 00bb bfff ffff                      | Encoding:         | 01 10bb bfff ffff                                                             |

| Description:      | Bit 'b' in register 'f' is cleared.    | Description:      | If bit 'b' in register 'f' is '1' then the next                               |

| Words:            | 1                                      |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next |

| Cycles:           | 1                                      |                   | instruction is discarded, and a NOP is                                        |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                            |                   | executed instead, making this a 2TCY instruction.                             |

|                   | Decode Read Process Write register 'f' | Words:<br>Cycles: | 1<br>1(2)                                                                     |

| Example           | BCF FLAG REG, 7                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

| Example           | Before Instruction                     |                   | Decode Read Process NOP register 'f' data                                     |

|                   | FLAG_REG = 0xC7<br>After Instruction   | If Skip:          | (2nd Cycle)                                                                   |

|                   | $FLAG_REG = 0x47$                      | ·                 | Q1 Q2 Q3 Q4                                                                   |

|                   |                                        |                   | NOP NOP NOP NOP                                                               |

|                   |                                        | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                   |

| •                     |      |

|-----------------------|------|

| Before Instruction    |      |

| PC = address          | HERE |

| After Instruction     |      |

| if $FLAG < 1 > = 0$ , |      |

|          | 0,      |       |

|----------|---------|-------|

| PC =     | address | TRUE  |

| if FLAG< | :1>=1,  |       |

| PC =     | address | FALSE |

| BSF               | Bit Set f                                                                                        |                          |                 |                       |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|--------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                                              | [ <i>label</i> ] BSF f,b |                 |                       |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                              |                          |                 |                       |  |  |  |

| Operation:        | $1 \rightarrow (f < b >)$                                                                        |                          |                 |                       |  |  |  |

| Status Affected:  | None                                                                                             |                          |                 |                       |  |  |  |

| Encoding:         | 01 01bb bfff ff:                                                                                 |                          |                 |                       |  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is            | s set.          | ·                     |  |  |  |

| Words:            | 1                                                                                                |                          |                 |                       |  |  |  |

| Cycles:           | 1                                                                                                |                          |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                       | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f'  | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                          |                 |                       |  |  |  |

| NOP               | No Operation           |       |      |      |  |  |

|-------------------|------------------------|-------|------|------|--|--|

| Syntax:           | [ label ]              | NOP   |      |      |  |  |

| Operands:         | None                   |       |      |      |  |  |

| Operation:        | No opera               | ition |      |      |  |  |

| Status Affected:  | None                   |       |      |      |  |  |

| Encoding:         | 00                     | 0000  | 0xx0 | 0000 |  |  |

| Description:      | ription: No operation. |       |      |      |  |  |

| Words:            | 1                      |       |      |      |  |  |

| Cycles:           | 1                      |       |      |      |  |  |

| Q Cycle Activity: | Q1                     | Q2    | Q3   | Q4   |  |  |

|                   | Decode                 | NOP   | NOP  | NOP  |  |  |

| Example           | NOP                    |       |      |      |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                                                               |        |                    |                    |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                           | RETFIE |                    |                    |  |  |

| Operands:         | None                                                                                                                                                                                                                |        |                    |                    |  |  |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                                                               | PC,    |                    |                    |  |  |

| Status Affected:  | None                                                                                                                                                                                                                |        |                    |                    |  |  |

| Encoding:         | 00 0000 0000 1001                                                                                                                                                                                                   |        |                    |                    |  |  |

| Monda             | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |        |                    |                    |  |  |

| Words:            | 1                                                                                                                                                                                                                   |        |                    |                    |  |  |

| Cycles:           | 2                                                                                                                                                                                                                   |        |                    |                    |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                  | Q2     | Q3                 | Q4                 |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                                              | NOP    | Set the<br>GIE bit | Pop from the Stack |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                                                 | NOP    | NOP                | NOP                |  |  |

| Example           | RETFIE                                                                                                                                                                                                              |        |                    |                    |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | OPTION Load Option Register                                                                                                                                                                                                                        |        |      |      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                          | OPTION | ٧    |      |  |

| Operands:        | None                                                                                                                                                                                                                                               |        |      |      |  |

| Operation:       | $(W)\toOF$                                                                                                                                                                                                                                         | PTION  |      |      |  |

| Status Affected: | None                                                                                                                                                                                                                                               |        |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                                 | 0000   | 0110 | 0010 |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |        |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                  |        |      |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |        |      |      |  |

| Example          |                                                                                                                                                                                                                                                    |        |      |      |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                 |        |      |      |  |

# PIC16C71X

#### SLEEP

| [ label ]                                                                                                                                                              | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| None                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$             |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TO, PD                                                                                                                                                                 |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00 0000 0110 0                                                                                                                                                         |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                                                                                                                     | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                                                                                                                 | NOP NOF                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SLEEP                                                                                                                                                                  |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                        | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow \overline{TO},$<br>$0 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$<br>$\boxed{00} 0000$<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1 $Q2\boxed{Decode} NOP$ | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |

| SUBLW             | Subtract                                                                                                                             | W from              | Literal                |            |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------------|--|--|

| Syntax:           | [ label ]                                                                                                                            | SUBLW               | / k                    |            |  |  |

| Operands:         | $0 \le k \le 25$                                                                                                                     | 55                  |                        |            |  |  |

| Operation:        | k - (W) →                                                                                                                            | • (W)               |                        |            |  |  |

| Status Affected:  | C, DC, Z                                                                                                                             |                     |                        |            |  |  |

| Encoding:         | 11                                                                                                                                   | 110x                | kkkk                   | kkkk       |  |  |

| Description:      | The W register is subtracted (2's comple-<br>ment method) from the eight bit literal 'k'.<br>The result is placed in the W register. |                     |                        |            |  |  |

| Words:            | 1                                                                                                                                    |                     |                        |            |  |  |

| Cycles:           | 1                                                                                                                                    |                     |                        |            |  |  |

| Q Cycle Activity: | Q1                                                                                                                                   | Q2                  | Q3                     | Q4         |  |  |

|                   | Decode                                                                                                                               | Read<br>literal 'k' | Process<br>data        | Write to W |  |  |

| Example 1:        | SUBLW                                                                                                                                | 0x02                |                        |            |  |  |

|                   | Before Instruction                                                                                                                   |                     |                        |            |  |  |

|                   |                                                                                                                                      | W =<br>C =<br>Z =   | 1<br>?<br>?            |            |  |  |

|                   | After Inst                                                                                                                           | ruction             |                        |            |  |  |

|                   |                                                                                                                                      | W =<br>C =<br>Z =   | 1<br>1; result is<br>0 | s positive |  |  |

| Example 2:        | Before In                                                                                                                            | Before Instruction  |                        |            |  |  |

| Example 2.        | Delete III                                                                                                                           | W =                 | 2                      |            |  |  |

|                   |                                                                                                                                      | C =                 | ?                      |            |  |  |

|                   |                                                                                                                                      | Z =                 | ?                      |            |  |  |

|                   | After Inst                                                                                                                           |                     | 0                      |            |  |  |

|                   |                                                                                                                                      | W =<br>C =<br>Z =   | 0<br>1; result i<br>1  | s zero     |  |  |

| Example 3:        | Before In                                                                                                                            | struction           |                        |            |  |  |

|                   |                                                                                                                                      | W =                 | 3                      |            |  |  |

|                   |                                                                                                                                      | C =<br>Z =          | ?<br>?                 |            |  |  |

|                   | After Inst                                                                                                                           | _                   |                        |            |  |  |

|                   |                                                                                                                                      | W =                 | 0xFF                   |            |  |  |

|                   |                                                                                                                                      | C =                 | 0; result is           | s nega-    |  |  |

|                   |                                                                                                                                      | tive<br>Z =         | 0                      |            |  |  |

|                   |                                                                                                                                      |                     |                        |            |  |  |

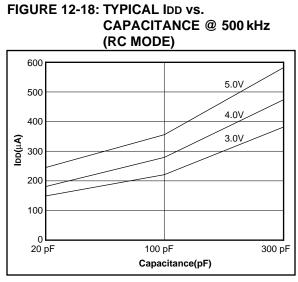

#### TABLE 12-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average      |        |  |