Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 68 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711-04e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC16C71X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C71X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C71X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**71. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC71. These devices have EPROM type memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C71X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

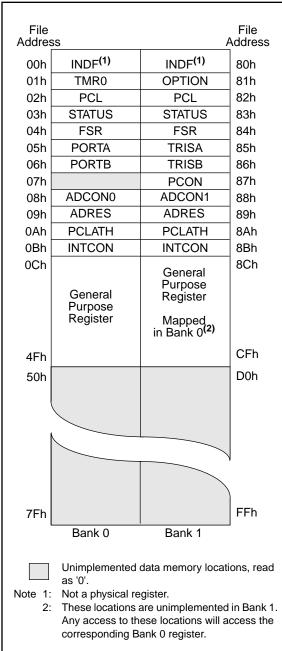

#### 4.2 Data Memory Organization

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow \text{Bank } 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

|                                                                                                                                                                                                                                                                                                                         | 1117 \                         |                                                                      |                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|-----------------|--|

| File<br>Addres                                                                                                                                                                                                                                                                                                          | s                              | ,                                                                    | File<br>Address |  |

| 00h                                                                                                                                                                                                                                                                                                                     | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>                                                  | 80h             |  |

| 01h                                                                                                                                                                                                                                                                                                                     | TMR0                           | OPTION                                                               | 81h             |  |

| 02h                                                                                                                                                                                                                                                                                                                     | PCL                            | PCL                                                                  | 82h             |  |

| 03h                                                                                                                                                                                                                                                                                                                     | STATUS                         | STATUS                                                               | 83h             |  |

| 04h                                                                                                                                                                                                                                                                                                                     | FSR                            | FSR                                                                  | 84h             |  |

| 05h                                                                                                                                                                                                                                                                                                                     | PORTA                          | TRISA                                                                | 85h             |  |

| 06h                                                                                                                                                                                                                                                                                                                     | PORTB                          | TRISB                                                                | 86h             |  |

| 07h                                                                                                                                                                                                                                                                                                                     |                                | PCON <sup>(2)</sup>                                                  | 87h             |  |

| 08h                                                                                                                                                                                                                                                                                                                     | ADCON0                         | ADCON1                                                               | 88h             |  |

| 09h                                                                                                                                                                                                                                                                                                                     | ADRES                          | ADRES                                                                | 89h             |  |

| 0Ah                                                                                                                                                                                                                                                                                                                     | PCLATH                         | PCLATH                                                               | 8Ah             |  |

| 0Bh                                                                                                                                                                                                                                                                                                                     | INTCON                         | INTCON                                                               | 8Bh             |  |

| 0Ch                                                                                                                                                                                                                                                                                                                     | General<br>Purpose<br>Register | General<br>Purpose<br>Register<br>Mapped<br>in Bank 0 <sup>(3)</sup> | 8Ch             |  |

| 2Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | AFh             |  |

| 30h                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | B0h             |  |

| 3011                                                                                                                                                                                                                                                                                                                    |                                |                                                                      |                 |  |

| l                                                                                                                                                                                                                                                                                                                       | <                              |                                                                      |                 |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |

| Ν                                                                                                                                                                                                                                                                                                                       |                                |                                                                      |                 |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      | )               |  |

| 7Fh                                                                                                                                                                                                                                                                                                                     |                                |                                                                      | FFh             |  |

| L                                                                                                                                                                                                                                                                                                                       | Bank 0                         | Bank 1                                                               | 1               |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>Note 1: Not a physical register.</li> <li>2: The PCON register is not implemented on the PIC16C71.</li> <li>3: These locations are unimplemented in Bank 1. Any access to these locations will access the corresponding Bank 0 register.</li> </ul> |                                |                                                                      |                 |  |

|                                                                                                                                                                                                                                                                                                                         |                                |                                                                      |                 |  |

# FIGURE 4-5: PIC16C711 REGISTER FILE MAP

# FIGURE 4-6: PIC16C715 REGISTER FILE MAP

| File<br>Address                                                                          | 3                              |                                | File<br>Address |  |  |

|------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|-----------------|--|--|

| 00h                                                                                      | INDF <sup>(1)</sup>            | INDF <sup>(1)</sup>            | 80h             |  |  |

| 01h                                                                                      | TMR0                           | OPTION                         | 81h             |  |  |

| 02h                                                                                      | PCL                            | PCL                            | 82h             |  |  |

| 03h                                                                                      | STATUS                         | STATUS                         | 83h             |  |  |

| 04h                                                                                      | FSR                            | FSR                            |                 |  |  |

| 05h                                                                                      | PORTA                          | TRISA                          |                 |  |  |

| 06h                                                                                      | PORTB                          | TRISB                          |                 |  |  |

| 07h                                                                                      |                                |                                | 87h             |  |  |

| 08h                                                                                      |                                |                                |                 |  |  |

| 09h                                                                                      |                                |                                |                 |  |  |

| 0Ah                                                                                      | PCLATH                         | PCLATH                         | 8Ah             |  |  |

| 0Bh                                                                                      | INTCON                         | INTCON                         | 8Bh             |  |  |

| 0Ch                                                                                      | PIR1                           | PIE1                           | 8Ch             |  |  |

| 0Dh                                                                                      |                                |                                | 8Dh             |  |  |

| 0Eh                                                                                      |                                | PCON                           | 8Eh             |  |  |

| 0Fh                                                                                      |                                |                                | 8Fh             |  |  |

| 10h                                                                                      |                                |                                | 90h             |  |  |

| 11h                                                                                      |                                |                                | 91h             |  |  |

| 12h                                                                                      |                                |                                |                 |  |  |

| 13h                                                                                      |                                |                                | 93h             |  |  |

| 14h                                                                                      |                                |                                | 94h             |  |  |

| 15h                                                                                      |                                |                                | 95h             |  |  |

| 16h                                                                                      |                                |                                | 96h             |  |  |

| 17h                                                                                      |                                |                                |                 |  |  |

| 18h                                                                                      |                                |                                | 98h             |  |  |

| 19h                                                                                      |                                |                                | 99h             |  |  |

| 1Ah                                                                                      |                                |                                | 9Ah             |  |  |

| 1Bh                                                                                      |                                |                                | 9Bh             |  |  |

| 1Ch                                                                                      |                                |                                | 9Ch             |  |  |

| 1Dh                                                                                      |                                |                                | 9Dh             |  |  |

| 1Eh                                                                                      | ADRES                          |                                | 9Eh             |  |  |

| 1Fh                                                                                      | ADCON0                         | ADCON1                         | 9Fh             |  |  |

| 20h                                                                                      | General<br>Purpose<br>Register | General<br>Purpose<br>Register | A0h             |  |  |

|                                                                                          | rtogiotor                      |                                | BFh             |  |  |

|                                                                                          |                                |                                | C0h             |  |  |

|                                                                                          |                                |                                |                 |  |  |

| l                                                                                        |                                |                                |                 |  |  |

|                                                                                          |                                |                                |                 |  |  |

| 7Fh                                                                                      | Deels                          | Bank 1                         | _ FFh           |  |  |

|                                                                                          | Bank 0                         | Bank 1                         |                 |  |  |

| Unimplemented data memory locations, read<br>as '0'.<br>Note 1: Not a physical register. |                                |                                |                 |  |  |

|                                                                                          |                                |                                |                 |  |  |

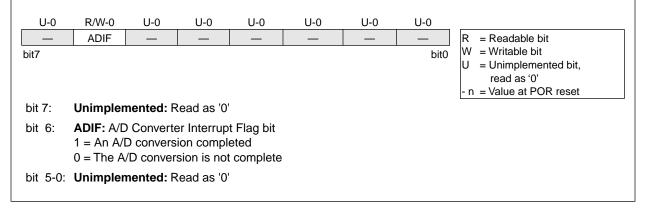

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

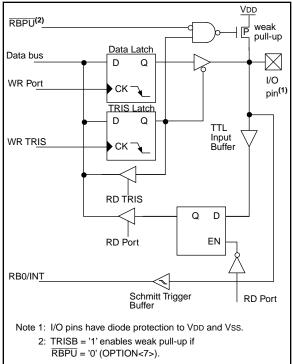

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

#### EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, RPC | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPC | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

| Note: | For the PIC16C71                                 |

|-------|--------------------------------------------------|

|       | if a change on the I/O pin should occur          |

|       | when the read operation is being executed        |

|       | (start of the Q2 cycle), then interrupt flag bit |

|       | RBIF may not get set.                            |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

## 6.0 TIMER0 MODULE

#### Applicable Devices71071711715

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

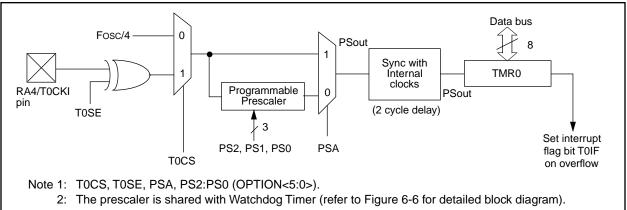

Figure 6-1 is a simplified block diagram of the Timer0 module.

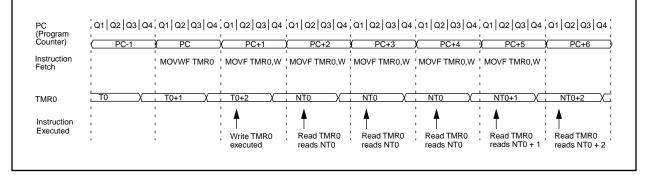

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION<4>). Clearing

FIGURE 6-1: TIMER0 BLOCK DIAGRAM

bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

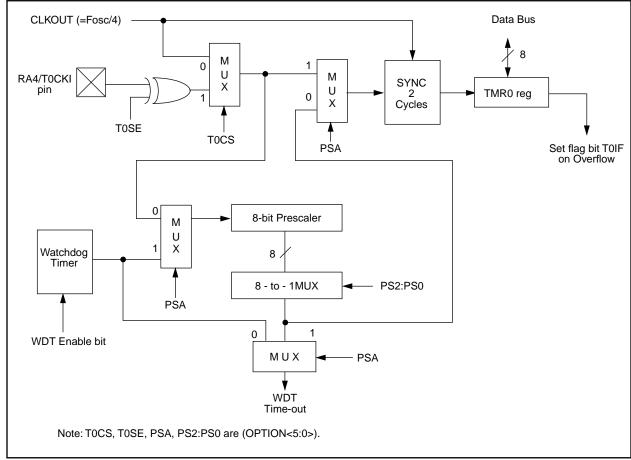

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

#### 6.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

#### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

#### 6.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 6-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 6-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

NOTES:

## 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Applicable Devices 710 71 711 715

The analog-to-digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 7-1 and Figure 7-2, controls the operation of the A/D module. The ADCON1 register, shown in Figure 7-3 configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0<br>ADCS1 | R/W-0<br>ADCS0                      | U-0                                                                                | R/W-0<br>CHS1             | R/W-0<br>CHS0 | R/W-0<br>GO/DONE                   | R/W-0<br>ADIF | R/W-0<br>ADON | R = Readable bit                                                                     |

|----------------|-------------------------------------|------------------------------------------------------------------------------------|---------------------------|---------------|------------------------------------|---------------|---------------|--------------------------------------------------------------------------------------|

| bit7           | ADCSU                               |                                                                                    | CHST                      | CHSU          | GO/DONE                            | ADIF          | bit0          | W = Writable bit<br>U = Unimplemented<br>bit, read as '0'<br>- n =Value at POR reset |

| bit 7-6:       | 00 = Fos<br>01 = Fos<br>10 = Fos    | c/8                                                                                |                           |               |                                    |               |               |                                                                                      |

| bit 5:         | Unimple                             | <b>nented:</b> Re                                                                  | ad as '0'.                |               |                                    |               |               |                                                                                      |

| bit 4-3:       | 00 = char<br>01 = char<br>10 = char | <b>IS0:</b> Analog<br>nnel 0, (RA0<br>nnel 1, (RA1<br>nnel 2, (RA2<br>nnel 3, (RA3 | )/AN0)<br>/AN1)<br>2/AN2) | Select bits   | i                                  |               |               |                                                                                      |

| bit 2:         | GO/DON                              | E: A/D Con                                                                         | version Sta               | atus bit      |                                    |               |               |                                                                                      |

|                |                                     | onversion ir<br>onversion r                                                        |                           |               | is bit starts th<br>bit is automat |               |               | are when the A/D conver-                                                             |

|                | 1 = conve                           | D Conversio<br>ersion is cor<br>ersion is not                                      | nplete (mu                |               | t Flag bit<br>red in softwar       | e)            |               |                                                                                      |

|                |                                     | onverter mo                                                                        | •                         | •             | consumes no                        | operating o   | current       |                                                                                      |

| Note 1:        |                                     | DCON0 is a nented, read                                                            |                           | Purpose R     | /W bit for the                     | PIC16C71      | 0/711 only. I | For the PIC16C71, this bit is                                                        |

## FIGURE 7-1: ADCON0 REGISTER (ADDRESS 08h), PIC16C710/71/711

| Register | Power-on Reset,<br>Brown-out Reset<br>Parity Error Reset | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|----------|----------------------------------------------------------|--------------------------|------------------------------------|

| W        | XXXX XXXX                                                | นนนน นนนน                | นนนน นนนน                          |

| INDF     | N/A                                                      | N/A                      | N/A                                |

| TMR0     | xxxx xxxx                                                | <u>uuuu</u> uuuu         | uuuu uuuu                          |

| PCL      | 0000 0000                                                | 0000 0000                | PC + 1(2)                          |

| STATUS   | 0001 1xxx                                                | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR      | xxxx xxxx                                                | uuuu uuuu                | uuuu uuuu                          |

| PORTA    | x 0000                                                   | u 0000                   | u uuuu                             |

| PORTB    | XXXX XXXX                                                | uuuu uuuu                | uuuu uuuu                          |

| PCLATH   | 0 0000                                                   | 0 0000                   | u uuuu                             |

| INTCON   | 0000 000x                                                | 0000 000u                | uuuu uuuu(1)                       |

| PIR1     | -0                                                       | -0                       | _ <sub>u</sub> _(1)                |

| ADCON0   | 0000 00-0                                                | 0000 00-0                | uuuu uu-u                          |

| OPTION   | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| TRISA    | 1 1111                                                   | 1 1111                   | u uuuu                             |

| TRISB    | 1111 1111                                                | 1111 1111                | นนนน นนนน                          |

| PIE1     | -0                                                       | -0                       | -u                                 |

| PCON     | वेर्वेवे                                                 | luu                      | luu                                |

| ADCON1   | 00                                                       | 00                       |                                    |

#### TABLE 8-13: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C715

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-11 for reset value for specific condition.

#### 8.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 8.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. A/D conversion (when A/D clock source is RC).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the subset (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 8.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    | Syntax:           | [label] RRF f,d                                                                                                                                                                                                                                                                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                  | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                    |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                                                                                                |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                                                                                                    |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                                    |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>$(C \rightarrow C \rightarrow C)$ Register f                         |

|                   |                                                                                                                                                                                                             |                   |                                                                                                                                                                                                                                                                                      |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                                                                                                    |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                                                                                                    |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                          |

|                   | Decode Read Process Write to data dest                                                                                                                                                                      |                   | Decode Read register 'f' Virie to dest                                                                                                                                                                                                                                               |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                                                                                           |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | Before Instruction       REG1       =       1110       0110         C       =       0       -       -         After Instruction       -       -       -       -         REG1       =       1110       0110         W       =       0111       0011         C       =       0       - |

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 10.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 10.12 <u>C Compiler (MPLAB-C)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

#### 10.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 10.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 10.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# PIC16C71X

Applicable Devices 710 71 711 715

## 11.0 ELECTRICAL CHARACTERISTICS FOR PIC16C710 AND PIC16C711

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                            | 55 to +125°C                         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Storage temperature                                                                                       |                                      |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                        |                                      |

| Voltage on VDD with respect to VSS                                                                        |                                      |

| Voltage on MCLR with respect to Vss                                                                       | 0 to +14V                            |

| Voltage on RA4 with respect to Vss                                                                        |                                      |

| Total power dissipation (Note 1)                                                                          |                                      |

| Maximum current out of Vss pin                                                                            |                                      |

| Maximum current into VDD pin                                                                              |                                      |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                              |                                      |

| Output clamp current, Ioк (Vo < 0 or Vo > Voo)                                                            | ±20 mA                               |

| Maximum output current sunk by any I/O pin                                                                | 25 mA                                |

| Maximum output current sourced by any I/O pin                                                             | 25 mA                                |

| Maximum current sunk by PORTA                                                                             | 200 mA                               |

| Maximum current sourced by PORTA                                                                          | 200 mA                               |

| Maximum current sunk by PORTB                                                                             |                                      |

| Maximum current sourced by PORTB                                                                          | 200 mA                               |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | - VOH) x IOH} + $\Sigma$ (VOI x IOL) |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# TABLE 11-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C710-04<br>PIC16C711-04                                                                                | PIC16C710-10<br>PIC16C711-10                                                                     | PIC16C710-20<br>PIC16C711-20                                                                    | PIC16LC710-04<br>PIC16LC711-04                                                                            | PIC16C710/JW<br>PIC16C711/JW                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V IDD: 5 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                         | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.      | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.     | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA typ. at 3.0V<br>IPD: 5.0 μA typ. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V IDD: 5 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                          |

| хт  | VDD: 4.0V to 6.0V IDD: 5 mA max. at 5.5V IPD: 21 $\mu A$ max. at 4V Freq: 4 MHz max.                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.      | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.     | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA typ. at 3.0V<br>IPD: 5.0 μA typ. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                     |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.           | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq:20 MHz max. | Not recommended for<br>use in HS mode                                                                     | VDD: 4.5V to 5.5V<br>IDD: 30 mA max. at<br>5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max.             |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for<br>use in LP mode                                                            | Not recommended for<br>use in LP mode                                                           | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at<br>3.0V<br>Freq: 200 kHz max. |

## Applicable Devices 710 71 711 715

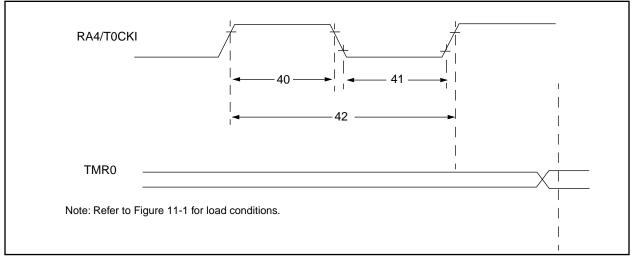

#### FIGURE 11-6: TIMER0 EXTERNAL CLOCK TIMINGS

#### TABLE 11-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                 |                      | Min                                            | Тур† | Max   | Units | Conditions                         |  |

|--------------|-----------|--------------------------------|----------------------|------------------------------------------------|------|-------|-------|------------------------------------|--|

| 40           | Tt0H      | T0CKI High Pulse Width         | No Prescaler         | 0.5Tcy + 20*                                   | —    | _     |       | Must also meet                     |  |

|              |           |                                | With Prescaler       | 10*                                            | —    | _     | ns    | parameter 42                       |  |

| 41           | TtOL      | T0CKI Low Pulse Width          | No Prescaler         | 0.5Tcy + 20*                                   | —    | -     | ns    |                                    |  |

|              |           |                                | With Prescaler       | 10*                                            | —    | _     | ns    |                                    |  |

| 42           | Tt0P      | T0CKI Period                   |                      | Greater of:<br>20 ns or <u>Tcy + 40</u> *<br>N |      | _     |       | N = prescale value<br>(2, 4,, 256) |  |

| 48           | Tcke2tmrl | Delay from external clock edge | e to timer increment | 2Tosc                                          | —    | 7Tosc | —     |                                    |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

20 MHz

DS30272A-page 132

± 30 PPM

EPSON CA-301 20.000M-C

6.0

# PIC16C71X

Applicable Devices 710 71 711 715

## 15.0 ELECTRICAL CHARACTERISTICS FOR PIC16C71

#### Absolute Maximum Ratings †

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55 to +125°C                         |

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65°C to +150°C                       |