Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | - ·                                                                        |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | ·                                                                          |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR, PER | Value on all<br>other resets<br>(3) |

|----------------------|--------|--------------------|--------------------|---------------|---------------|----------------|-----------------|---------------|-----------|-------------------------------|-------------------------------------|

| Bank 1               |        | •                  |                    |               |               |                |                 |               |           | -                             |                                     |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location      | uses conter   | ts of FSR to  | address data   | a memory (n     | ot a physical | register) | 0000 0000                     | 0000 0000                           |

| 81h                  | OPTION | RBPU               | INTEDG             | TOCS          | TOSE          | PSA            | PS2             | PS1           | PS0       | 1111 1111                     | 1111 1111                           |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)      |               | 0000 0000     | 0000 0000      |                 |               |           |                               |                                     |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO            | PD             | Z               | DC            | С         | 0001 1xxx                     | 000q quuu                           |

| 84h <sup>(1)</sup>   | FSR    | Indirect dat       | a memory ac        | ldress pointe | er            |                |                 |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 85h                  | TRISA  | -                  | -                  | PORTA Dat     | a Direction F | Register       |                 |               |           | 11 1111                       | 11 1111                             |

| 86h                  | TRISB  | PORTB Da           | ta Direction F     | Register      |               |                |                 |               |           | 1111 1111                     | 1111 1111                           |

| 87h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 88h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 89h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 8Ah <sup>(1,2)</sup> | PCLATH | —                  | _                  | —             | Write Buffe   | r for the uppe | er 5 bits of th | e PC          |           | 0 0000                        | 0 0000                              |

| 8Bh <b>(1)</b>       | INTCON | GIE                | PEIE               | TOIE          | INTE          | RBIE           | TOIF            | INTF          | RBIF      | 0000 000x                     | 0000 000u                           |

| 8Ch                  | PIE1   | —                  | ADIE               | —             | —             | —              | —               | —             | —         | -0                            | -0                                  |

| 8Dh                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 8Eh                  | PCON   | MPEEN              | —                  | —             | —             | —              | PER             | POR           | BOR       | u1qq                          | u1uu                                |

| 8Fh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 90h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 91h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 92h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 93h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 94h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 95h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 96h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 97h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 98h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 99h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Ah                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 9Bh                  | _      | Unimpleme          | nted               |               | _             | —              |                 |               |           |                               |                                     |

| 9Ch                  | —      | Unimpleme          | nted               |               | -             | —              |                 |               |           |                               |                                     |

| 9Dh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Eh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | _                                   |

| 9Fh                  | ADCON1 | —                  | _                  | —             | —             | —              | -               | PCFG1         | PCFG0     | 00                            | 00                                  |

#### TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

#### 4.2.2.1 STATUS REGISTER

#### Applicable Devices 710 71 711 715

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| <u>R/W-0</u> | R/W-0                                                                                                                  | R/W-0                                                      | <u>R-1</u><br>TO                                    | <u>R-1</u><br>PD                         | R/W-x<br>Z                                  | R/W-x                                     | R/W-x<br>C                     | D. Deedeble hit                                                                                           |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|------------------------------------------|---------------------------------------------|-------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| IRP<br>bit7  | RP1                                                                                                                    | RP0                                                        | 10                                                  | <u>PD</u>                                | 2                                           | DC                                        | bitO                           | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:       | <b>IRP:</b> Regi<br>1 = Bank<br>0 = Bank                                                                               | 2, 3 (100h                                                 | - 1FFh)                                             | (used for                                | indirect add                                | Iressing)                                 |                                |                                                                                                           |  |  |

| bit 6-5:     | <b>RP1:RP0</b><br>11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank<br>Each ban                                         | x 3 (180h -<br>x 2 (100h -<br>x 1 (80h - 1<br>x 0 (00h - 3 | 1FFh)<br>17Fh)<br>FFh)<br>7Fh)                      | ect bits (us                             | ed for dired                                | ct addressi                               | ing)                           |                                                                                                           |  |  |

| bit 4:       | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred |                                                            |                                                     |                                          |                                             |                                           |                                |                                                                                                           |  |  |

| bit 3:       | <b>PD</b> : Power $1 = \text{After } \mu$<br>0 = By exercised                                                          | power-up o                                                 | or by the c                                         |                                          |                                             |                                           |                                |                                                                                                           |  |  |

| bit 2:       |                                                                                                                        | sult of an                                                 |                                                     | •                                        | peration is                                 |                                           |                                |                                                                                                           |  |  |

| bit 1:       | 1 = A carr                                                                                                             | y-out from                                                 | the 4th lo                                          | w order b                                | w,SUBLW,S<br>it of the res<br>bit of the re | ult occurre                               |                                | borrow the polarity is reversed                                                                           |  |  |

| bit 0:       | 1 = A carr<br>0 = No ca<br>Note: For                                                                                   | y-out from<br>rry-out fro<br>borrow th<br>d operand        | the most<br>m the most<br>e polarity<br>. For rotat | significan<br>st significa<br>is reverse |                                             | result occu<br>result occ<br>ction is exe | irred<br>curred<br>ecuted by a | adding the two's complement of with either the high or low orde                                           |  |  |

#### FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h)

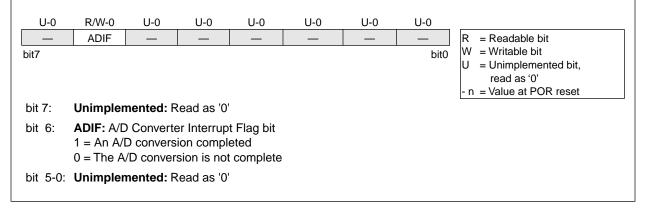

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

#### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |  |  |  |

|--------------|------|--------|-------------------------------------------------|--|--|--|

| RA0/AN0      | bit0 | TTL    | nput/output or analog input                     |  |  |  |

| RA1/AN1      | bit1 | TTL    | nput/output or analog input                     |  |  |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                    |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |  |  |  |

|              |      |        | Output is open drain type                       |  |  |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3       | Bit 2       | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|---------|-------------|-------------|-------|--------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | —     | _     | RA4     | RA3         | RA2         | RA1   | RA0    | x 0000                   | u 0000                    |

| 85h     | TRISA  | —     | —     | _     | PORTA D | Data Direct | ion Registe |       | 1 1111 | 1 1111                   |                           |

| 9Fh     | ADCON1 | _     | _     | _     | _       | _           |             | PCFG1 | PCFG0  | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| Address   | Name   | Bit 7 | Bit 6         | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------|---------------|-------|-----------|-----------|-------|-------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7   | RB6           | RB5   | RB4       | RB3       | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB | Data Directic |       | 1111 1111 | 1111 1111 |       |       |       |                          |                           |

| 81h, 181h | OPTION | RBPU  | INTEDG        | TOCS  | TOSE      | PSA       | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

NOTES:

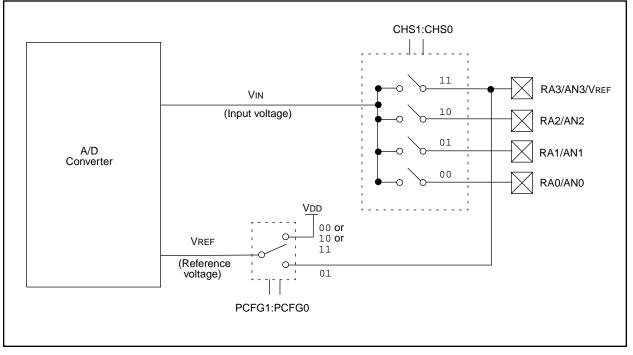

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 7-4.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 7.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- Set GIE bit

- 3. Wait the required acquisition time.

2. Configure A/D interrupt (if desired):

4. Start conversion:

Clear ADIF bit

Set ADIE bit

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 7-4: A/D BLOCK DIAGRAM

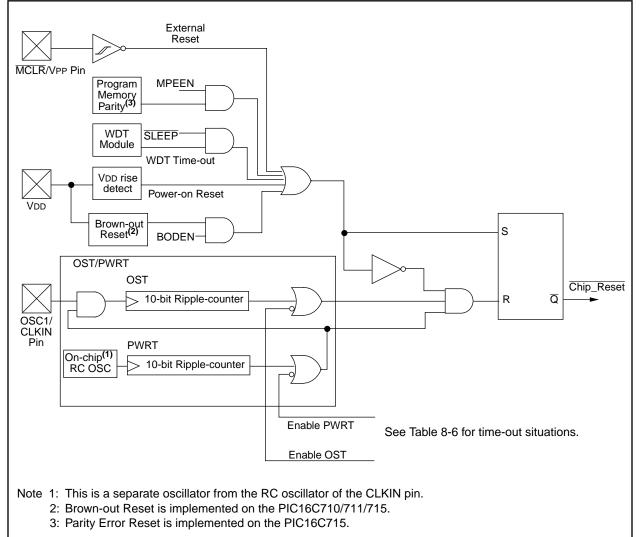

#### 8.0 SPECIAL FEATURES OF THE CPU

#### Applicable Devices 710 71 711 715

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PER) (PIC16C715)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 8.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 8-1: CONFIGURATION WORD FOR PIC16C71

| bit13     | -   -                                                                                                                     | —                                   | —       | —        | _        | _    | — | CP0 | PWRTE | WDTE | FOSC1 | FOSC0<br>bit0 | Register:<br>Address | CONFIG<br>2007h |

|-----------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|----------|----------|------|---|-----|-------|------|-------|---------------|----------------------|-----------------|

| bit 13-5: | Unimpler                                                                                                                  | nented                              | : Read  | as '1'   |          |      |   |     |       |      |       |               |                      |                 |

| bit 4:    | <b>CP0:</b> Code protection bit<br>1 = Code protection off<br>0 = All memory is code protected, but 00h - 3Fh is writable |                                     |         |          |          |      |   |     |       |      |       |               |                      |                 |

| bit 3:    | <b>PWRTE:</b><br>1 = Power<br>0 = Power                                                                                   | -up Tin                             | ner ena | bled     | le bit   |      |   |     |       |      |       |               |                      |                 |

| bit 2:    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                                                                                      | enabled                             | ł       | Enable   | e bit    |      |   |     |       |      |       |               |                      |                 |

| bit 1-0:  | FOSC1:F<br>11 = RC c<br>10 = HS c<br>01 = XT c<br>00 = LP o                                                               | oscillato<br>oscillato<br>oscillato | or<br>r | tor Sele | ection b | vits |   |     |       |      |       |               |                      |                 |

#### 8.3 <u>Reset</u>

#### Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and

WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

#### FIGURE 8-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

#### TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

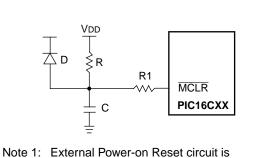

#### FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

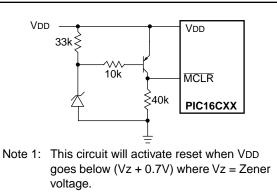

#### FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

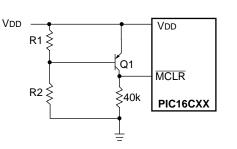

#### FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

| RETLW             | Return w                                                                | ith Lite                                                                                                                                                                           | ral in W   |                                         |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                               | RETLW                                                                                                                                                                              | k          |                                         |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                       |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

| Operation:        | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow F \end{array}$  | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                       |            |                                         |  |  |  |  |  |

| Status Affected:  | None                                                                    |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

| Encoding:         | 11                                                                      | 01xx                                                                                                                                                                               | kkkk       | kkkk                                    |  |  |  |  |  |

| Description:      | bit literal 'k<br>loaded fro                                            | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction |            |                                         |  |  |  |  |  |

| Words:            | 1                                                                       |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

| Cycles:           | 2                                                                       |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                      | Q2                                                                                                                                                                                 | Q3         | Q4                                      |  |  |  |  |  |

| 1st Cycle         | Decode                                                                  | Read<br>literal 'k'                                                                                                                                                                | NOP        | Write to<br>W, Pop<br>from the<br>Stack |  |  |  |  |  |

| 2nd Cycle         | NOP                                                                     | NOP                                                                                                                                                                                | NOP        | NOP                                     |  |  |  |  |  |

| Example           | CALL TABLE ;W contains table<br>;offset value<br>;W now has table value |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

| TABLE             | fset<br>table<br>f table                                                |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

|                   | RETLW kn<br>Before In                                                   |                                                                                                                                                                                    |            |                                         |  |  |  |  |  |

|                   |                                                                         | W =                                                                                                                                                                                | 0x07       |                                         |  |  |  |  |  |

|                   | After Inst                                                              | ruction<br>W =                                                                                                                                                                     | value of k | 8                                       |  |  |  |  |  |

| Syntax:                     | [label] RETURN                                                                                                                                          |      |      |                       |  |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------|--|--|--|--|--|

| Operands:                   | None                                                                                                                                                    |      |      |                       |  |  |  |  |  |

| Operation:                  | $TOS \rightarrow PC$                                                                                                                                    |      |      |                       |  |  |  |  |  |

| Status Affected:            | None                                                                                                                                                    |      |      |                       |  |  |  |  |  |

| Encoding:                   | 00                                                                                                                                                      | 0000 | 0000 | 1000                  |  |  |  |  |  |

| Description:                | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |      |      |                       |  |  |  |  |  |

| Words:                      | 1                                                                                                                                                       |      |      |                       |  |  |  |  |  |

| Cycles:                     | 2                                                                                                                                                       |      |      |                       |  |  |  |  |  |

| Q Cycle Activity:           | Q1                                                                                                                                                      | Q2   | Q3   | Q4                    |  |  |  |  |  |

| 1st Cycle                   | Decode                                                                                                                                                  | NOP  | NOP  | Pop from<br>the Stack |  |  |  |  |  |

| 2nd Cycle                   | NOP                                                                                                                                                     | NOP  | NOP  | NOP                   |  |  |  |  |  |

| Example                     | RETURN                                                                                                                                                  |      |      |                       |  |  |  |  |  |

| After Interrupt<br>PC = TOS |                                                                                                                                                         |      |      |                       |  |  |  |  |  |

#### Applicable Devices 710 71 711 715

## TABLE 11-6:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C710/711-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Param<br>No. | Sym  | Characteristic                                 | Min       | Тур†       | Мах        | Units | Conditions                                                                                              |

|--------------|------|------------------------------------------------|-----------|------------|------------|-------|---------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                     | —         | _          | 8-bits     | bit   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A02          | EABS | Absolute error                                 | —         | —          | <±1        | LSb   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A03          | EIL  | Integral linearity error                       | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A04          | Edl  | Differential linearity error                   | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A05          | Efs  | Full scale error                               | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A06          | EOFF | Offset error                                   | _         | _          | <±1        | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A10          | —    | Monotonicity                                   | —         | guaranteed | -          | —     | $VSS \leq VAIN \leq VREF$                                                                               |

| A20          | Vref | Reference voltage                              | 2.5V      | —          | Vdd + 0.3  | V     |                                                                                                         |

| A25          | VAIN | Analog input voltage                           | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                         |

| A30          | ZAIN | Recommended impedance of analog voltage source | —         | _          | 10.0       | kΩ    |                                                                                                         |

| A40          | IAD  | A/D conversion current (VDD)                   | _         | 180        | _          | μA    | Average current consumption<br>when A/D is on. (Note 1)                                                 |

| A50          | IREF | VREF input current (Note 2)                    | 10        | _          | 1000       | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN.<br>To charge CHOLD see Section 7.1. |

|              |      |                                                | —         | _          | 10         | μΑ    | During A/D Conversion cycle                                                                             |

These parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

## PIC16C71X

#### Applicable Devices 710 71 711 715

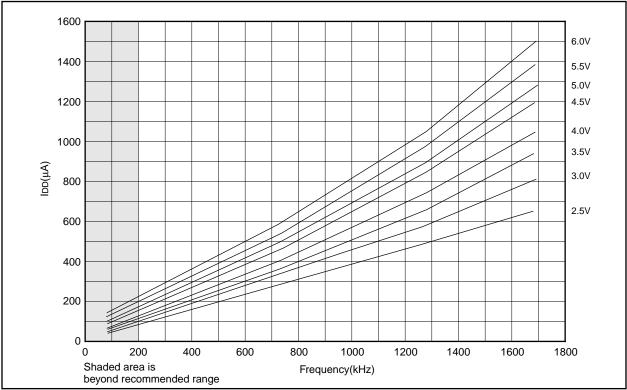

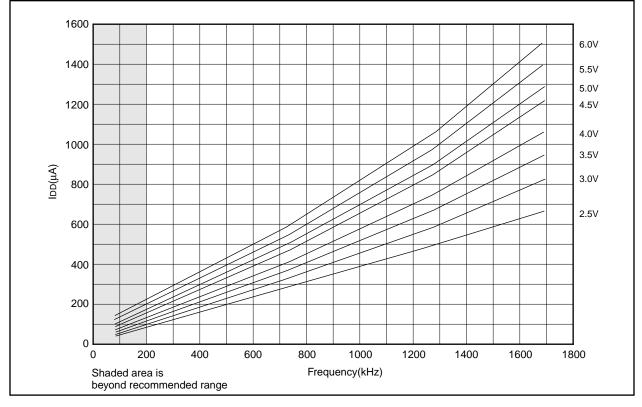

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

#### Applicable Devices 710 71 711 715

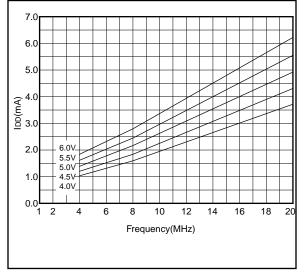

#### FIGURE 12-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

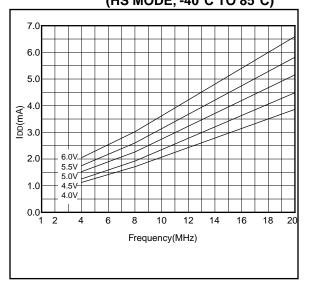

#### FIGURE 12-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

#### Applicable Devices 710 71 711 715

## 13.1 DC Characteristics: PIC16C715-04 (Commercial, Industrial, Extended) PIC16C715-10 (Commercial, Industrial, Extended) PIC16C715-20 (

| DC CHARACTERISTICS             |                                                                   |               |            | lard Op<br>ating ter      |                      | ture (               | ditions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)<br>$40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)                                                                                           |

|--------------------------------|-------------------------------------------------------------------|---------------|------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                  | Characteristic                                                    | Sym           | Min        | Тур†                      | Мах                  | Units                | Conditions                                                                                                                                                                                                                                                                                        |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd           | 4.0<br>4.5 | -                         | 5.5<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                           |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr           | -          | 1.5                       | -                    | V                    | Device in SLEEP mode                                                                                                                                                                                                                                                                              |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset signal | VPOR          | -          | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal      | SVDD          | 0.05       | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                                                                                         |

| D005                           | Brown-out Reset Voltage                                           | Bvdd          | 3.7        | 4.0                       | 4.3                  | V                    | BODEN configuration bit is enabled                                                                                                                                                                                                                                                                |

| D010                           | Supply Current (Note 2)                                           | IDD           | -          | 2.7                       | 5                    | mA .                 | XT, RC osc configuration (PIC16C715-04)<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                      |

| D013                           |                                                                   |               | -          | 13.5                      | 30                   | mA                   | HS øsc configuration (PIC16C715-20)<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                  |

| D015                           | Brown-out Reset Current<br>(Note 5)                               | $\Delta$ IBOR | -<         | 300*                      | 500                  | ha `                 | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3)                                    | IPD <         | -          | 10,5<br>1.5<br>1.5<br>1.5 | 42<br>21<br>24<br>30 | μΑ<br>μΑ<br>μΑ<br>μΑ | $VDD = 4.0V, WDT enabled, -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -0^{\circ}C \text{ to } +70^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +85^{\circ}C$ $VDD = 4.0V, WDT \text{ disabled, } -40^{\circ}C \text{ to } +125^{\circ}C$ |

| D023                           | Brown-out Reset Current<br>(Note 5)                               | ALBOR         |            | >300*                     | 500                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 51, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which Vod can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

(The)test conditions for all IDD measurements in active operation mode are:

OSCT = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## PIC16C71X

#### Applicable Devices71071711715

#### 13.5 <u>Timing Diagrams and Specifications</u>

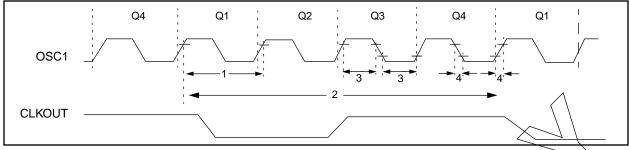

#### FIGURE 13-2: EXTERNAL CLOCK TIMING

#### TABLE 13-2: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym       | Characteristic                  | Min | Тур†                     | Мах      | Units | Conditions                 |

|------------------|-----------|---------------------------------|-----|--------------------------|----------|-------|----------------------------|

|                  | Fos       | External CLKIN Frequency        | DC  | _                        | 4        | MHz   | XT osc mode                |

|                  |           | (Note 1)                        | DC  | _                        | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |           |                                 | DC  | _                        | 20/      | MHz   | HS osc mode (PIC16C715-20) |

|                  |           |                                 | DC  | _                        | 200      | kHz   | LP osc mode                |

|                  |           | Oscillator Frequency            | DC  | —                        | 1        | MHz   | RØ osc mode                |

|                  |           | (Note 1)                        | 0.1 |                          | <u> </u> | MHz   | XT osc mode                |

|                  |           |                                 | 4   | $  \langle \rangle$      | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |           |                                 | 4   | $\wedge - \land$         | 10       | MHz   | HS osc mode (PIC16C715-10) |

|                  |           |                                 | 4   | $\langle \not F \rangle$ | 20       | MHz   | HS osc mode (PIC16C715-20) |

|                  |           |                                 | 5   | $\overline{M}$           | 200      | kHz   | LP osc mode                |

| 1                | Tosc      | External CLKIN Period           | 250 | $ \rightarrow $          | _        | ns    | XT osc mode                |

|                  |           | (Note 1)                        | 250 | Ň                        | -        | ns    | HS osc mode (PIC16C715-04) |

|                  |           |                                 | 100 | $ ^{\sim}-$              | _        | ns    | HS osc mode (PIC16C715-10) |

|                  |           |                                 | 50  | _                        | —        | ns    | HS osc mode (PIC16C715-20) |

|                  |           |                                 | 5   | _                        | —        | μs    | LP osc mode                |

|                  |           | Oscillator Períod               | 250 | —                        | —        | ns    | RC osc mode                |

|                  |           | (Note 1)                        | 250 | _                        | 10,000   | ns    | XT osc mode                |

|                  |           |                                 | 250 | _                        | 250      | ns    | HS osc mode (PIC16C715-04) |

|                  | /         |                                 | 100 | _                        | 250      | ns    | HS osc mode (PIC16C715-10) |

|                  |           | $() \leftarrow \vee$            | 50  | _                        | 250      | ns    | HS osc mode (PIC16C715-20) |

|                  |           | $\sim$                          | 5   | _                        | -        | μs    | LP osc mode                |

| 2                | Tgy       | Instruction Cycle Time (Note 1) | 200 | _                        | DC       | ns    | Tcy = 4/Fosc               |

| 3                | TosĻ,     | External Clock in (OSC1) High   | 50  | —                        | —        | ns    | XT oscillator              |

| $\setminus$      | TosH      | or Low Time                     | 2.5 | —                        | —        | μs    | LP oscillator              |

| $\searrow$       | $\langle$ |                                 | 10  | _                        | —        | ns    | HS oscillator              |

| 4                | TosR,     | External Clock in (OSC1) Rise   | _   | —                        | 25       | ns    | XT oscillator              |

|                  | TosF      | or Fall Time                    | —   | _                        | 50       | ns    | LP oscillator              |

|                  |           |                                 | _   | _                        | 15       | ns    | HS oscillator              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C715.

| Applicable Devices 710 71 711 715 |                                                                  |                   |                                                                            |                |                  |                |                                                                |  |  |

|-----------------------------------|------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------|----------------|------------------|----------------|----------------------------------------------------------------|--|--|

| 15.3 [                            | DC Characteristics: PIC16C71<br>PIC16C71<br>PIC16C71<br>PIC16LC7 | -20 (0<br>1-04 (0 | Commero<br>Commero                                                         | cial,<br>cial, | Indust<br>Indust | rial)<br>rial) |                                                                |  |  |

|                                   |                                                                  |                   |                                                                            |                |                  |                | nless otherwise stated)                                        |  |  |

|                                   |                                                                  | OOpera            | OOperating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) |                |                  |                |                                                                |  |  |

| DC CHAP                           | RACTERISTICS                                                     | Oporati           |                                                                            |                | -40°             | -              | TA $\leq$ +85°C (industrial)<br>cribed in DC spec Section 15.1 |  |  |

|                                   |                                                                  |                   | ction 15.2                                                                 |                | Diange           | as uesi        | chibed in DC spec Section 15.1                                 |  |  |

| Param                             | Characteristic                                                   | Sym               | Min                                                                        | Тур            | Max              | Units          | Conditions                                                     |  |  |

| No.                               |                                                                  |                   |                                                                            | t              |                  |                |                                                                |  |  |

|                                   | Input Low Voltage                                                |                   |                                                                            |                |                  |                |                                                                |  |  |

|                                   | I/O ports                                                        | VIL               |                                                                            |                |                  |                |                                                                |  |  |

| D030                              | with TTL buffer                                                  |                   | Vss                                                                        | -              | 0.15V            | V              | For entire VDD range                                           |  |  |

| D031                              | with Schmitt Trigger buffer                                      |                   | Vss                                                                        | -              | 0.8V             | V              | $4.5 \leq VDD \leq 5.5V$                                       |  |  |

| D032                              | MCLR, OSC1 (in RC mode)                                          |                   | Vss                                                                        | -              | 0.2Vdd           | V              |                                                                |  |  |

| D033                              | OSC1 (in XT, HS and LP)                                          |                   | Vss                                                                        | -              | 0.3Vdd           | V              | Note1                                                          |  |  |

|                                   | Input High Voltage                                               |                   |                                                                            |                |                  |                |                                                                |  |  |

|                                   | I/O ports (Note 4)                                               | Vih               |                                                                            | -              |                  |                |                                                                |  |  |

| D040                              | with TTL buffer                                                  |                   | 2.0                                                                        | -              | Vdd              | V              | $4.5 \leq VDD \leq 5.5V$                                       |  |  |

| D040A                             |                                                                  |                   | 0.25VDD<br>+ 0.8V                                                          | -              | Vdd              |                | For entire VDD range                                           |  |  |

| D041                              | with Schmitt Trigger buffer                                      |                   | 0.85Vdd                                                                    | -              | Vdd              |                | For entire VDD range                                           |  |  |

| D042                              | MCLR, RB0/INT                                                    |                   | 0.85Vdd                                                                    | -              | Vdd              | V              |                                                                |  |  |

| D042A                             | OSC1 (XT, HS and LP)                                             |                   | 0.7Vdd                                                                     | -              | Vdd              | V              | Note1                                                          |  |  |

| D043                              | OSC1 (in RC mode)                                                |                   | 0.9Vdd                                                                     | -              | Vdd              | V              |                                                                |  |  |

| D070                              | PORTB weak pull-up current                                       | IPURB             | 50                                                                         | 250            | †400             | μΑ             | VDD = 5V, VPIN = VSS                                           |  |  |

|                                   | Input Leakage Current (Notes 2, 3)                               |                   |                                                                            |                |                  |                |                                                                |  |  |

| D060                              | I/O ports                                                        | lı∟               | -                                                                          | -              | ±1               | μA             | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance            |  |  |

| D061                              | MCLR, RA4/T0CKI                                                  |                   | -                                                                          | -              | ±5               | μΑ             | $Vss \le VPIN \le VDD$                                         |  |  |

| D063                              | OSC1                                                             |                   | -                                                                          | -              | ±5               | μA             | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration    |  |  |

|                                   | Output Low Voltage                                               |                   |                                                                            |                |                  |                |                                                                |  |  |

| D080                              | I/O ports                                                        | Vol               | -                                                                          | -              | 0.6              | V              | IOL = 8.5mA, VDD = 4.5V,<br>-40°C to +85°C                     |  |  |

| D083                              | OSC2/CLKOUT (RC osc config)                                      |                   | -                                                                          | -              | 0.6              | V              | IOL = 1.6mA, VDD = 4.5V,<br>-40°C to +85°C                     |  |  |

|                                   | Output High Voltage                                              |                   |                                                                            |                |                  |                |                                                                |  |  |

| D090                              | I/O ports (Note 3)                                               | Vон               | Vdd - 0.7                                                                  | -              | -                | V              | IOH = -3.0mA, VDD = 4.5V,<br>-40°С to +85°С                    |  |  |

| D092                              | OSC2/CLKOUT (RC osc config)                                      |                   | Vdd - 0.7                                                                  | -              | -                | V              | IOH = -1.3mA, VDD = 4.5V,<br>-40°С to +85°С                    |  |  |

| D130*                             | Open-Drain High Voltage                                          | Vod               | -                                                                          | -              | 14               | V              | RA4 pin                                                        |  |  |

| + [                               | Data in "Typ" column is at 5V, 25°C unl                          | ooo oth           | nuico oto                                                                  | tod            | Those n          | oromo          |                                                                |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt trigger input. It is not recommended that the PIC16C71 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

3: Negative current is defined as current sourced by the pin.

4: PIC16C71 Rev. "Ax" INT pin has a TTL input buffer. PIC16C71 Rev. "Bx" INT pin has a Schmitt Trigger input buffer.

#### I

| I/O Ports                                     |    |

|-----------------------------------------------|----|

| PORTA2                                        |    |

| PORTB2                                        |    |

| Section2                                      |    |

| I/O Programming Considerations                |    |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator |    |

| In-Circuit Serial Programming47, 6            | 37 |

| INDF Register                                 |    |

| Indirect Addressing2                          |    |

| Instruction Cycle1                            |    |

| Instruction Flow/Pipelining1                  |    |

| Instruction Format                            | 36 |

| Instruction Set                               | _  |

| ADDLW7                                        |    |

| ADDWF                                         |    |

| ANDLW                                         |    |

| ANDWF                                         |    |

| BCF                                           |    |

| BSF                                           | '2 |

| BTFSC7                                        |    |

| BTFSS                                         |    |

| CALL                                          | 73 |

| CLRF                                          |    |

| CLRWDT                                        |    |

| COMF                                          |    |

| DECF                                          |    |

| DECFSZ                                        |    |

| GOTO                                          |    |

| INCF                                          |    |

| INCFSZ                                        |    |

| IORLW                                         |    |

| IORWF                                         |    |

| MOVF7                                         |    |

| MOVLW7                                        |    |

| MOVWF7                                        | 78 |

| NOP7                                          | 79 |

| OPTION7                                       | 79 |

| RETFIE7                                       |    |

| RETLW8                                        | 30 |

| RETURN8                                       |    |

| RLF8                                          |    |

| RRF                                           |    |

| SLEEP                                         |    |

| SUBLW                                         |    |

| SUBWF                                         |    |

| SWAPF8                                        |    |

| TRIS                                          |    |

| XORLW                                         |    |

| XORWF                                         |    |

| Section                                       |    |

| INT Interrupt                                 |    |

| INTCON Register                               |    |

| INTE bit                                      |    |

| INTEDG bit                                    |    |

| Internal Sampling Switch (Rss) Impedence      |    |

| Interrupts                                    |    |

| A/D                                           |    |

| External6                                     |    |

| PORTB Change6                                 |    |

| PortB Change6                                 |    |

| RB7:RB4 Port Change2                          |    |

| Section6                                      | 51 |

| TMR06                                         | 32 |

| TMR0 Overflow                                         | 61     |

|-------------------------------------------------------|--------|