Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 68 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

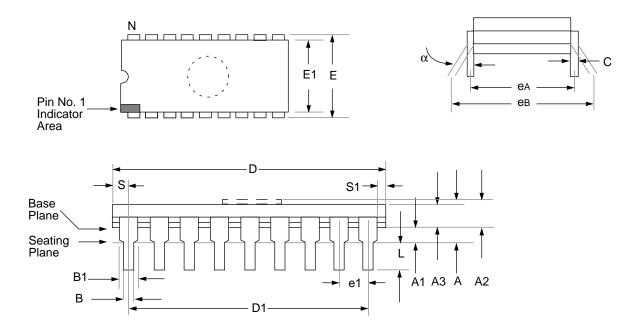

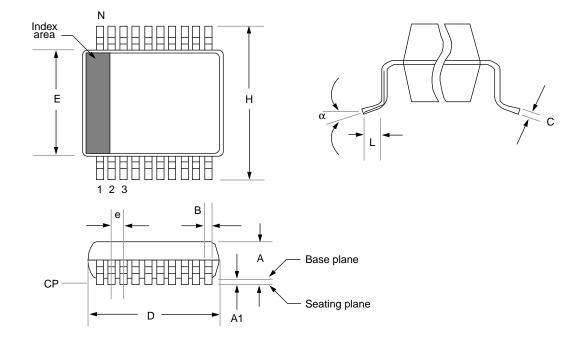

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711t-04-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|-------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|             | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |

| Memory      | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |

|             | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|             | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| Peripherals | Capture/Compare/PWM<br>Module(s)                | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | —                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|             | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |

|             | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|             | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|             | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|             | Voltage Range (Volts)                           | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| eatures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

## TABLE 1-1: PIC16C71X FAMILY OF DEVICES

|            |                                                 | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|------------|-------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory     | EPROM Program Memory<br>(x14 words)             | 4K                          | 4K                                        | 8K                          | 8K                                        |

|            | Data Memory (bytes)                             | 192                         | 192                                       | 376                         | 376                                       |

|            | Timer Module(s)                                 | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| eripherals | Capture/Compare/PWM<br>Module(s)                | 2                           | 2                                         | 2                           | 2                                         |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|            | Parallel Slave Port                             | —                           | Yes                                       | —                           | Yes                                       |

|            | A/D Converter (8-bit) Channels                  | 5                           | 8                                         | 5                           | 8                                         |

|            | Interrupt Sources                               | 11                          | 12                                        | 11                          | 12                                        |

|            | I/O Pins                                        | 22                          | 33                                        | 22                          | 33                                        |

|            | Voltage Range (Volts)                           | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| atures     | In-Circuit Serial Programming                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|            | Brown-out Reset                                 | Yes                         | Yes                                       | Yes                         | Yes                                       |

|            | Packages                                        | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

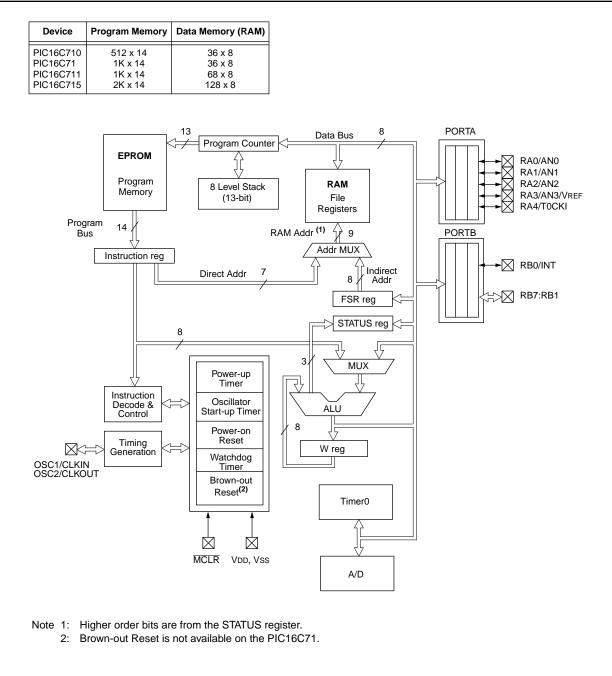

## FIGURE 3-1: PIC16C71X BLOCK DIAGRAM

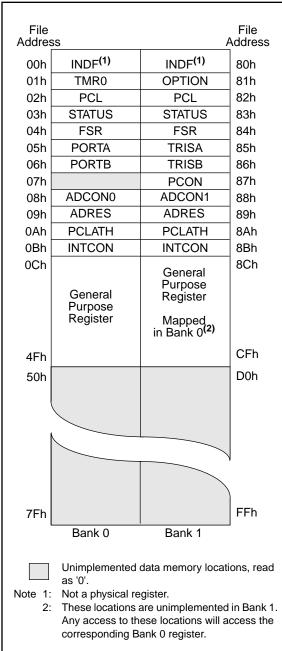

## FIGURE 4-5: PIC16C711 REGISTER FILE MAP

## FIGURE 4-6: PIC16C715 REGISTER FILE MAP

| File<br>Address | 3                                                    |                                | File<br>Address |

|-----------------|------------------------------------------------------|--------------------------------|-----------------|

| 00h             | INDF <sup>(1)</sup>                                  | INDF <sup>(1)</sup>            | 80h             |

| 01h             | TMR0                                                 | OPTION                         | 81h             |

| 02h             | PCL                                                  | PCL                            | 82h             |

| 03h             | STATUS                                               | STATUS                         | 83h             |

| 04h             | FSR                                                  | FSR                            |                 |

| 05h             | PORTA                                                | TRISA                          |                 |

| 06h             | PORTB                                                | TRISB                          |                 |

| 07h             |                                                      |                                | 87h             |

| 08h             |                                                      |                                |                 |

| 09h             |                                                      |                                |                 |

| 0Ah             | PCLATH                                               | PCLATH                         | 8Ah             |

| 0Bh             | INTCON                                               | INTCON                         | 8Bh             |

| 0Ch             | PIR1                                                 | PIE1                           | 8Ch             |

| 0Dh             |                                                      |                                | 8Dh             |

| 0Eh             |                                                      | PCON                           | 8Eh             |

| 0Fh             |                                                      |                                | 8Fh             |

| 10h             |                                                      |                                | 90h             |

| 11h             |                                                      |                                | 91h             |

| 12h             |                                                      |                                |                 |

| 13h             |                                                      |                                | 93h             |

| 14h             |                                                      |                                | 94h             |

| 15h             |                                                      |                                | 95h             |

| 16h             |                                                      |                                | 96h             |

| 17h             |                                                      |                                | 97h             |

| 18h             |                                                      |                                | 98h             |

| 19h             |                                                      |                                | 99h             |

| 1Ah             |                                                      |                                | 9Ah             |

| 1Bh             |                                                      |                                | 9Bh             |

| 1Ch             |                                                      |                                | 9Ch             |

| 1Dh             |                                                      |                                | 9Dh             |

| 1Eh             | ADRES                                                |                                | 9Eh             |

| 1Fh             | ADCON0                                               | ADCON1                         | 9Fh             |

| 20h             | General<br>Purpose<br>Register                       | General<br>Purpose<br>Register | A0h             |

|                 | rtogiotor                                            |                                | BFh             |

|                 |                                                      |                                | C0h             |

|                 |                                                      |                                |                 |

| l               |                                                      |                                |                 |

|                 |                                                      |                                |                 |

| 7Fh             | Deels                                                | Bank 1                         | _ FFh           |

|                 | Bank 0                                               | Bank 1                         |                 |

| e a             | Jnimplemented dat<br>as '0'.<br>Not a physical regis | -                              | ns, read        |

|                 |                                                      |                                |                 |

PIC16C71X

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x   | 500      |                                                      |

|----------|----------|------------------------------------------------------|

| BSF      | pclath,3 | ;Select page 1 (800h-FFFh)                           |

| BCF      | pclath,4 | ;Only on >4K devices                                 |

| CALL     | SUB1_P1  | ;Call subroutine in                                  |

|          | :        | ;page 1 (800h-FFFh)                                  |

|          | :        |                                                      |

|          | :        |                                                      |

| ORG 0x   | 900      |                                                      |

| SUB1_P1: |          | ;called subroutine                                   |

|          | :        | ;page 1 (800h-FFFh)                                  |

|          | :        |                                                      |

| RETURN   |          | ;return to Call subroutine<br>;in page 0 (000h-7FFh) |

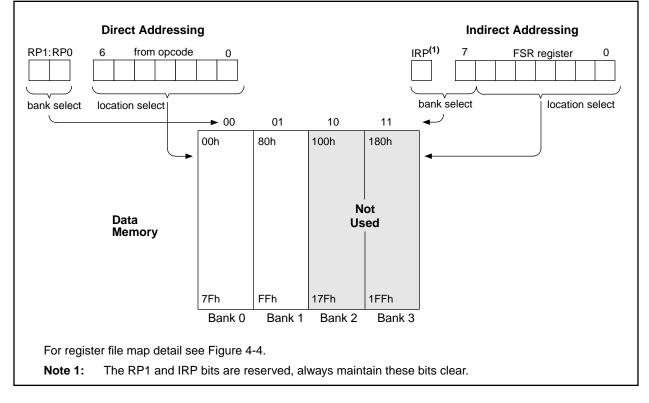

## 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-15. However, IRP is not used in the PIC16C71X devices.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

### EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | 0x20<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |                                               |                                                                                                    |

|          | :                     |                                               | ;yes continue                                                                                      |

## FIGURE 4-15: DIRECT/INDIRECT ADDRESSING

## 5.0 I/O PORTS

## Applicable Devices 710 71 711 715

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

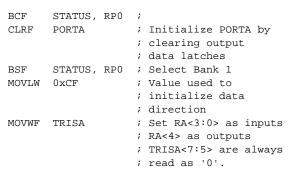

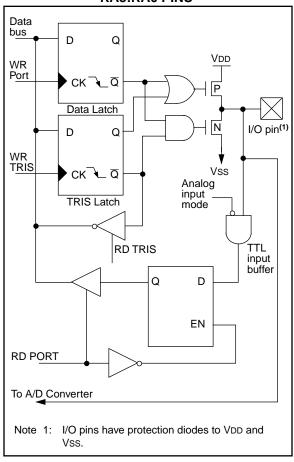

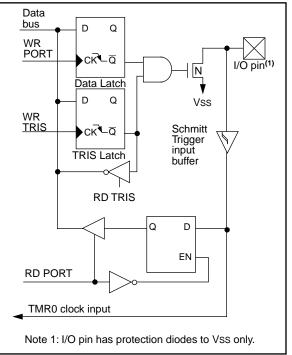

### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 5-1: INITIALIZING PORTA

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 PINS

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

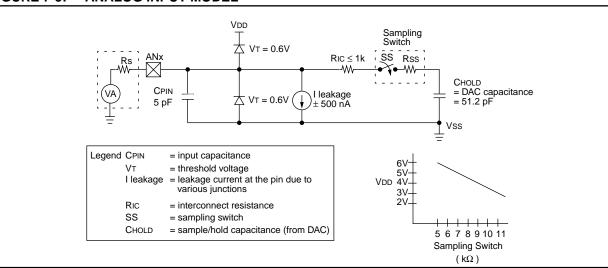

## 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

### EQUATION 7-1: A/D MINIMUM CHARGING TIME

$\mathsf{VHOLD} = (\mathsf{VREF} - (\mathsf{VREF}/\mathsf{512})) \bullet (1 - e^{(\mathsf{-TCAP/CHOLD}(\mathsf{Ric} + \mathsf{Rss} + \mathsf{Rs}))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 \ k\Omega$

1/2 LSb error

$V\text{DD} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

## FIGURE 7-5: ANALOG INPUT MODEL

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

## EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (RIC + RSS + RS) ln(1/511)

- -51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 μs (-6.2364)

5.747 μs

TACQ = 5 μs + 5.747 μs + [(50°C - 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

| TABLE 8-7: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C7 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| TO | PD |                                                         |  |

|----|----|---------------------------------------------------------|--|

| 1  | 1  | Power-on Reset                                          |  |

| 0  | x  | Illegal, TO is set on POR                               |  |

| x  | 0  | Illegal, PD is set on POR                               |  |

| 0  | 1  | WDT Reset                                               |  |

| 0  | 0  | WDT Wake-up                                             |  |

| u  | u  | MCLR Reset during normal operation                      |  |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

## TABLE 8-8: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C710/711

| POR | BOR | TO | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | х  | x  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | /DT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

## TABLE 8-9: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C715

| PER | POR | BOR | TO | PD |                                                         |

|-----|-----|-----|----|----|---------------------------------------------------------|

| 1   | 0   | х   | 1  | 1  | Power-on Reset                                          |

| x   | 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| x   | 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

| 0   | 1   | 1   | 1  | 1  | Parity Error Reset                                      |

| 0   | 0   | x   | x  | x  | Illegal, PER is set on POR                              |

| 0   | x   | 0   | x  | x  | Illegal, PER is set on BOR                              |

## 8.5 Interrupts

## Applicable Devices71071711715

The PIC16C71X family has 4 sources of interrupt.

| Interrupt Sources                                     |

|-------------------------------------------------------|

| External interrupt RB0/INT                            |

| TMR0 overflow interrupt                               |

| PORTB change interrupts (pins RB7:RB4)                |

| A/D Interrupt                                         |

| The interrupt control register (INTCON) records indi- |

vidual interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-19). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

| ~    |                                                                                                                                                                                                                                                                                                |                                                                                             |  |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| No   | Note: For the PIC16C71<br>If an interrupt occurs while the Global Inter-<br>rupt Enable (GIE) bit is being cleared, the<br>GIE bit may unintentionally be re-enabled<br>by the user's Interrupt Service Routine (the<br>RETFIE instruction). The events that<br>would cause this to occur are: |                                                                                             |  |  |  |  |  |  |  |  |

|      | <ol> <li>An instruction clears the GIE bit while<br/>an interrupt is acknowledged.</li> </ol>                                                                                                                                                                                                  |                                                                                             |  |  |  |  |  |  |  |  |

|      | 2                                                                                                                                                                                                                                                                                              | 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine. |  |  |  |  |  |  |  |  |

|      | <ol> <li>The Interrupt Service Routine completes with the execution of the RET-<br/>FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.</li> </ol>                        |                                                                                             |  |  |  |  |  |  |  |  |

|      |                                                                                                                                                                                                                                                                                                | Perform the following to ensure that inter-<br>upts are globally disabled:                  |  |  |  |  |  |  |  |  |

| LOOP | BCF                                                                                                                                                                                                                                                                                            | INTCON, GIE ; Disable global<br>; interrupt bit                                             |  |  |  |  |  |  |  |  |

|      |                                                                                                                                                                                                                                                                                                | INTCON, GIE ; Global interrupt<br>; disabled?                                               |  |  |  |  |  |  |  |  |

|      | GOTO                                                                                                                                                                                                                                                                                           | LOOP ; NO, try again                                                                        |  |  |  |  |  |  |  |  |

:

Yes, continue

with program

flow

| INCFSZ            | Increme                                                                                                                                                                                                                                                                                                           | nt f, Skip               | o if O          |               |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|---------------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | INCFSZ                   | f,d             |               |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | 0 ≤ f ≤ 127<br>d ∈ [0,1] |                 |               |  |  |  |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (dest), s                | kip if resu     | ult = 0       |  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              |                          |                 |               |  |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                     | dfff            | ffff          |  |  |  |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                          |                 |               |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                          |                 |               |  |  |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                          |                 |               |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                       | Q3              | Q4            |  |  |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                                                                            | Read<br>register<br>'f'  | Process<br>data | Write to dest |  |  |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                                          | le)                      |                 |               |  |  |  |  |  |  |

|                   | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                   | Q3              | Q4            |  |  |  |  |  |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                      | NOP             | NOP           |  |  |  |  |  |  |

| Example           | HERE                                                                                                                                                                                                                                                                                                              | INCF:<br>GOTO<br>UE      |                 | NT, 1<br>DOP  |  |  |  |  |  |  |

|                   | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if $CNT= 0$ ,<br>PC = address CONTINUE<br>if $CNT \neq 0$ ,<br>PC = address HERE + 1                                                                                                                                             |                          |                 |               |  |  |  |  |  |  |

| IORLW             |                                                                                                                       |                     | eral with       |               |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                             | IORLW               | К               |               |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                       | 55                  |                 |               |  |  |  |  |

| Operation:        | (W) .OR.                                                                                                              | $k \rightarrow (W)$ | )               |               |  |  |  |  |

| Status Affected:  | Z                                                                                                                     |                     |                 |               |  |  |  |  |

| Encoding:         | 11                                                                                                                    | 1000                | kkkk            | kkkk          |  |  |  |  |

| Description:      | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                     |                 |               |  |  |  |  |

| Words:            | 1                                                                                                                     |                     |                 |               |  |  |  |  |

| Cycles:           | 1                                                                                                                     |                     |                 |               |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                    | Q2                  | Q3              | Q4            |  |  |  |  |

|                   | Decode                                                                                                                | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |  |

| Example           | IORLW                                                                                                                 | 0x35                |                 |               |  |  |  |  |

|                   | Before In                                                                                                             |                     | 1               |               |  |  |  |  |

|                   |                                                                                                                       | W =                 | 0x9A            |               |  |  |  |  |

|                   | After Instruction                                                                                                     |                     |                 |               |  |  |  |  |

|                   |                                                                                                                       | W =                 | 0xBF            |               |  |  |  |  |

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                                   |                                                                               |                                                |                                    |                                                          |                                                  | 、                                                   |                                   |                                      |          |          |            |                                       |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----------------------------------|--------------------------------------|----------|----------|------------|---------------------------------------|

|                            |                                                    |                                       |                                                    |                                   |                                                                               |                                                |                                    |                                                          |                                                  | 7                                                   | 2                                 |                                      |          |          |            | 7                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                                   |                                                                               |                                                | 2                                  |                                                          |                                                  | 7                                                   |                                   | 2                                    |          |          |            |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 2                                 |                                                                               |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC17C4X                   | 2                                                  |                                       | 7                                                  | 2                                 | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C9XX                  | 2                                                  |                                       | 7                                                  | 7                                 | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          | 7          |                                       |

| PIC16C8X                   | 7                                                  | 7                                     | 7                                                  | 7                                 | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC16C7XX                  | 7                                                  | 7                                     | 7                                                  | 2                                 | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16C6X                   | 7                                                  | 7                                     | 7                                                  | 2                                 | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      |          | 7        |            |                                       |

| PIC16CXXX                  | 7                                                  | 7                                     | 7                                                  | 7                                 | 7                                                                             | 7                                              |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      | 2        |          |            |                                       |

| PIC16C5X                   | 7                                                  | 7                                     | 7                                                  | 7                                 | 7                                                                             | 7                                              |                                    | 7                                                        | 7                                                | 7                                                   |                                   |                                      | 7        |          |            |                                       |

| PIC14000                   | 2                                                  |                                       | 7                                                  | 7                                 | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

| PIC12C5XX                  | >                                                  | 7                                     | 7                                                  | >                                 | 7                                                                             |                                                |                                    |                                                          | 7                                                | 7                                                   |                                   |                                      |          |          |            |                                       |

|                            | PICMASTER®/<br>PICMASTER-CE<br>In-Circuit Emulator | CEPIC Low-Cost<br>In-Circuit Emulator | MPLAB™<br>Integrated<br>Development<br>Environment | MPLAB <sup>TM</sup> C<br>Compiler | Lo fuzzyTECH <sup>®</sup> .MP<br>Explorer/Edition<br>Fuzzy Logic<br>Dev. Tool | MP-DriveWay™<br>Applications<br>Code Generator | Total Endurance™<br>Software Model | PICSTART <sup>®</sup><br>Lite Ultra Low-Cost<br>Dev. Kit | PICSTART®<br>Plus Low-Cost<br>Universal Dev. Kit | PRO MATE <sup>®</sup> II<br>Universal<br>Programmer | KEELOQ <sup>®</sup><br>Programmer | SEEVAL <sup>®</sup><br>Designers Kit | PICDEM-1 | PICDEM-2 | e PICDEM-3 | KEELOQ <sup>®</sup><br>Evaluation Kit |

## TABLE 10-1: DEVELOPMENT TOOLS FROM MICROCHIP

# PIC16C71X

| Applica | ble Devices 710 71 711 715                      |                                                |                                                          |                                                    |                                                                            |                                                                      |                                                             |

|---------|-------------------------------------------------|------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|

| 11.3    |                                                 | 1-04<br>0-10<br>1-10<br>0-20<br>1-20<br>'10-04 | (Comme<br>(Comme<br>(Comme<br>(Comme<br>(Comme<br>(Comme | ercia<br>ercia<br>ercia<br>ercia<br>ercia<br>ercia | II, Indus<br>II, Indus<br>II, Indus<br>II, Indus<br>II, Indus<br>II, Indus | trial, E<br>trial, E<br>trial, E<br>trial, E<br>trial, E<br>trial, E | Extended)<br>Extended)<br>Extended)<br>Extended)            |

|         |                                                 |                                                |                                                          |                                                    |                                                                            |                                                                      | less otherwise stated)                                      |

|         |                                                 | Operati                                        | ng tempe                                                 | ratur                                              |                                                                            |                                                                      | $A \le +70^{\circ}C$ (commercial)                           |

| DC CHA  | RACTERISTICS                                    |                                                |                                                          |                                                    | -40°C<br>-40°C                                                             |                                                                      | A ≤ +85°C (industrial)<br>A ≤ +125°C (extended)             |

|         |                                                 | Operati                                        | na voltaa                                                | e Vdi                                              |                                                                            |                                                                      | ribed in DC spec Section 11.1 and                           |

|         |                                                 | Section                                        |                                                          |                                                    | <b>J</b>                                                                   |                                                                      |                                                             |

| Param   | Characteristic                                  | Sym                                            | Min                                                      | Тур                                                | Max                                                                        | Units                                                                | Conditions                                                  |

| No.     |                                                 |                                                |                                                          | 1                                                  |                                                                            |                                                                      |                                                             |

|         | Input Low Voltage                               |                                                |                                                          |                                                    |                                                                            |                                                                      |                                                             |

|         | I/O ports                                       | Vi∟                                            |                                                          |                                                    |                                                                            |                                                                      |                                                             |

| D030    | with TTL buffer                                 |                                                | Vss                                                      | -                                                  | 0.15VDD                                                                    |                                                                      | For entire VDD range                                        |

| D030A   |                                                 |                                                | Vss                                                      | -                                                  | 0.8V                                                                       | V                                                                    | $4.5 \leq VDD \leq 5.5V$                                    |

| D031    | with Schmitt Trigger buffer                     |                                                | Vss                                                      | -                                                  | 0.2VDD                                                                     | V                                                                    |                                                             |

| D032    | MCLR, OSC1<br>(in RC mode)                      |                                                | Vss                                                      | -                                                  | 0.2Vdd                                                                     | V                                                                    |                                                             |

| D033    | OSC1 (in XT, HS and LP)                         |                                                | Vss                                                      | -                                                  | 0.3Vdd                                                                     | V                                                                    | Note1                                                       |

| 0033    | Input High Voltage                              |                                                | V 35                                                     | -                                                  | 0.3700                                                                     | V                                                                    |                                                             |

|         | I/O ports                                       | VIH                                            |                                                          | -                                                  |                                                                            |                                                                      |                                                             |

| D040    | with TTL buffer                                 |                                                | 2.0                                                      | -                                                  | Vdd                                                                        | V                                                                    | $4.5 \le VDD \le 5.5V$                                      |

| D040A   |                                                 |                                                | 0.25VDD                                                  | -                                                  | VDD                                                                        | V                                                                    | For entire VDD range                                        |

| -       |                                                 |                                                | + 0.8V                                                   |                                                    |                                                                            |                                                                      |                                                             |

| D041    | with Schmitt Trigger buffer                     |                                                | 0.8Vdd                                                   | -                                                  | Vdd                                                                        | V                                                                    | For entire VDD range                                        |

| D042    | MCLR, RB0/INT                                   |                                                | 0.8Vdd                                                   | -                                                  | Vdd                                                                        | V                                                                    |                                                             |

| D042A   | OSC1 (XT, HS and LP)                            |                                                | 0.7Vdd                                                   | -                                                  | Vdd                                                                        | V                                                                    | Note1                                                       |

| D043    | OSC1 (in RC mode)                               |                                                | 0.9Vdd                                                   | -                                                  | Vdd                                                                        | V                                                                    |                                                             |

| D070    | PORTB weak pull-up current                      | IPURB                                          | 50                                                       | 250                                                | 400                                                                        | μΑ                                                                   | VDD = 5V, VPIN = VSS                                        |

| D060    | Input Leakage Current (Notes 2, 3)<br>I/O ports | lı∟                                            | -                                                        | -                                                  | ±1                                                                         | μA                                                                   | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance         |

| D061    | MCLR, RA4/T0CKI                                 |                                                | -                                                        | -                                                  | ±5                                                                         | μA                                                                   | $V_{SS} \leq V_{PIN} \leq V_{DD}$                           |

| D063    | OSC1                                            |                                                | -                                                        | -                                                  | ±5                                                                         | μA                                                                   | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LF osc configuration |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 710 71 711 715

## 11.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

### 1. TppS2ppS

2. TppS

| т      |                                      |     |              |  |

|--------|--------------------------------------|-----|--------------|--|

| F      | Frequency                            | Т   | Time         |  |

| Lowerc | ase letters (pp) and their meanings: |     |              |  |

| рр     |                                      |     |              |  |

| сс     | CCP1                                 | osc | OSC1         |  |

| ck     | CLKOUT                               | rd  | RD           |  |

| CS     | CS                                   | rw  | RD or WR     |  |

| di     | SDI                                  | sc  | SCK          |  |

| do     | SDO                                  | SS  | SS           |  |

| dt     | Data in                              | tO  | TOCKI        |  |

| io     | I/O port                             | t1  | T1CKI        |  |

| mc     | MCLR                                 | wr  | WR           |  |

| Upperc | case letters and their meanings:     |     |              |  |

| S      |                                      |     |              |  |

| F      | Fall                                 | P   | Period       |  |

| н      | High                                 | R   | Rise         |  |

| I      | Invalid (Hi-impedance)               | V   | Valid        |  |

| L      | Low                                  | Z   | Hi-impedance |  |

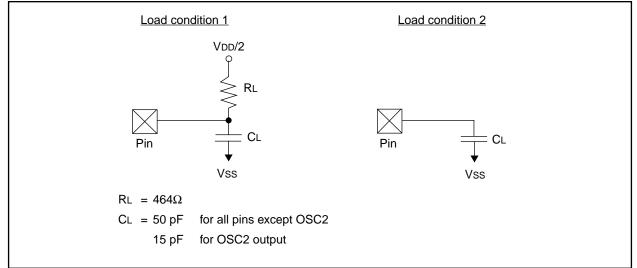

## FIGURE 11-1: LOAD CONDITIONS

Applicable Devices 710 71 711 715

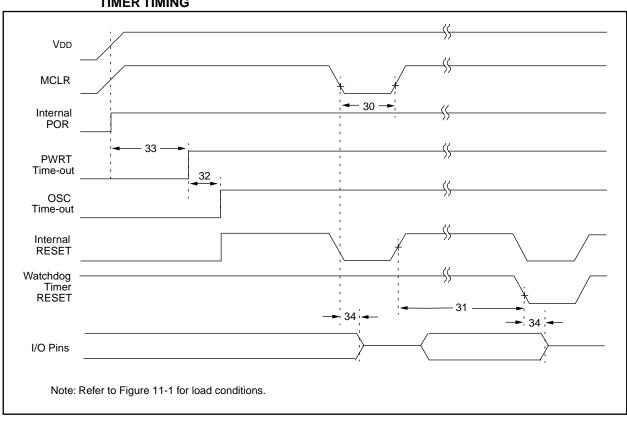

## FIGURE 11-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

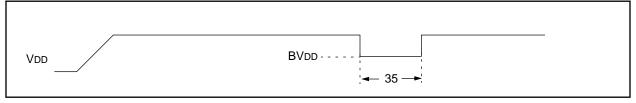

### FIGURE 11-5: BROWN-OUT RESET TIMING

## TABLE 11-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max  | Units | Conditions                       |

|------------------|-------|--------------------------------------------------------|-----|----------|------|-------|----------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 1   | _        | _    | μs    | VDD = 5V, -40°C to +125°C        |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7*  | 18       | 33*  | ms    | VDD = 5V, -40°C to +125°C        |

| 32               | Tost  | Oscillation Start-up Timer Period                      | —   | 1024Tosc | _    | _     | Tosc = OSC1 period               |

| 33               | Tpwrt | Power up Timer Period                                  | 28* | 72       | 132* | ms    | VDD = 5V, -40°C to +125°C        |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 1.1  | μs    |                                  |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | _    | μs    | $3.8V \leq V\text{DD} \leq 4.2V$ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C71X

## Applicable Devices71071711715

## 13.5 <u>Timing Diagrams and Specifications</u>

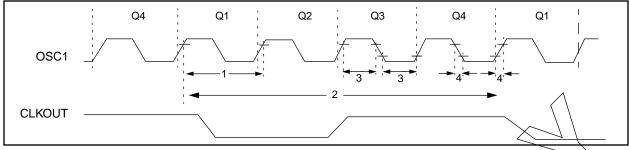

## FIGURE 13-2: EXTERNAL CLOCK TIMING

## TABLE 13-2: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym    | Characteristic                  | Min | Тур†                | Мах      | Units | Conditions                 |

|------------------|--------|---------------------------------|-----|---------------------|----------|-------|----------------------------|

|                  | Fos    | External CLKIN Frequency        | DC  | _                   | 4        | MHz   | XT osc mode                |

|                  |        | (Note 1)                        | DC  | _                   | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |        |                                 | DC  | _                   | 20/      | MHz   | HS osc mode (PIC16C715-20) |

|                  |        |                                 | DC  | _                   | 200      | kHz ` | LP osc mode                |

|                  |        | Oscillator Frequency            | DC  | —                   | <b>A</b> | MHz   | RØ osc mode                |

|                  |        | (Note 1)                        | 0.1 |                     | <u> </u> | MHz   | XT osc mode                |

|                  |        |                                 | 4   | $  \langle \rangle$ | 4        | MHz   | HS osc mode (PIC16C715-04) |

|                  |        |                                 | 4   | $\wedge - \land$    | 10       | MHz   | HS osc mode (PIC16C715-10) |

|                  |        |                                 | 4   | $\mathbb{P}$        | 20       | MHz   | HS osc mode (PIC16C715-20) |

|                  |        |                                 | 5   | $\overline{M}$      | 200      | kHz   | LP osc mode                |

| 1                | Tosc   | External CLKIN Period           | 250 | $ \rightarrow $     | _        | ns    | XT osc mode                |

|                  |        | (Note 1)                        | 250 | Ň                   | —        | ns    | HS osc mode (PIC16C715-04) |

|                  |        |                                 | 100 | $ ^{\sim}-$         | —        | ns    | HS osc mode (PIC16C715-10) |

|                  |        |                                 | 50  | _                   | —        | ns    | HS osc mode (PIC16C715-20) |

|                  |        |                                 | 5   | _                   | —        | μs    | LP osc mode                |

|                  |        | Oscillator Períod               | 250 | —                   | —        | ns    | RC osc mode                |

|                  |        | (Note 1)                        | 250 | _                   | 10,000   | ns    | XT osc mode                |

|                  |        |                                 | 250 | _                   | 250      | ns    | HS osc mode (PIC16C715-04) |

|                  | /      |                                 | 100 | _                   | 250      | ns    | HS osc mode (PIC16C715-10) |

|                  |        | $() \leq \vee$                  | 50  | _                   | 250      | ns    | HS osc mode (PIC16C715-20) |

|                  |        | $\bigvee \bigvee \bigvee$       | 5   | —                   | —        | μs    | LP osc mode                |

| 2                | TGY    | Instruction Cycle Time (Note 1) | 200 | —                   | DC       | ns    | TCY = 4/FOSC               |

| 3                | Jost,  | External Clock in (OSC1) High   | 50  | _                   |          | ns    | XT oscillator              |

| $\setminus$      | TosH   | or Low Time                     | 2.5 | —                   | —        | μs    | LP oscillator              |

|                  | $\leq$ |                                 | 10  |                     |          | ns    | HS oscillator              |

| 4                | TosR,  | External Clock in (OSC1) Rise   | _   | _                   | 25       | ns    | XT oscillator              |

|                  | TosF   | or Fall Time                    |     | —                   | 50       | ns    | LP oscillator              |

|                  |        |                                 | —   | _                   | 15       | ns    | HS oscillator              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC16C715.