Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 68 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | A/D 4x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc711t-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR, PER | Value on all<br>other resets<br>(3) |

|----------------------|--------|--------------------|--------------------|---------------|---------------|----------------|-----------------|---------------|-----------|-------------------------------|-------------------------------------|

| Bank 1               |        | •                  |                    |               |               |                |                 |               |           | -                             |                                     |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location      | uses conter   | ts of FSR to  | address data   | a memory (n     | ot a physical | register) | 0000 0000                     | 0000 0000                           |

| 81h                  | OPTION | RBPU               | INTEDG             | TOCS          | TOSE          | PSA            | PS2             | PS1           | PS0       | 1111 1111                     | 1111 1111                           |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)      | Least Signif  | icant Byte    |                |                 |               |           | 0000 0000                     | 0000 0000                           |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO            | PD             | Z               | DC            | С         | 0001 1xxx                     | 000q quuu                           |

| 84h <sup>(1)</sup>   | FSR    | Indirect dat       | a memory ac        | ldress pointe | er            |                |                 |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 85h                  | TRISA  | -                  | -                  | PORTA Dat     | a Direction F | Register       |                 |               |           | 11 1111                       | 11 1111                             |

| 86h                  | TRISB  | PORTB Da           | ta Direction F     | Register      |               |                |                 |               |           | 1111 1111                     | 1111 1111                           |

| 87h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 88h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 89h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 8Ah <sup>(1,2)</sup> | PCLATH | —                  | _                  | —             | Write Buffe   | r for the uppe | er 5 bits of th | e PC          |           | 0 0000                        | 0 0000                              |

| 8Bh <b>(1)</b>       | INTCON | GIE                | PEIE               | TOIE          | INTE          | RBIE           | TOIF            | INTF          | RBIF      | 0000 000x                     | 0000 000u                           |

| 8Ch                  | PIE1   | —                  | ADIE               | —             | —             | —              | —               | —             | —         | -0                            | -0                                  |

| 8Dh                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 8Eh                  | PCON   | MPEEN              | —                  | —             | —             | —              | PER             | POR           | BOR       | u1qq                          | u1uu                                |

| 8Fh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 90h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 91h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 92h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 93h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 94h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 95h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 96h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 97h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 98h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 99h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Ah                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 9Bh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 9Ch                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 9Dh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Eh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | _                                   |

| 9Fh                  | ADCON1 | —                  | _                  | —             | —             | —              | -               | PCFG1         | PCFG0     | 00                            | 00                                  |

### TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

### 4.3 PCL and PCLATH

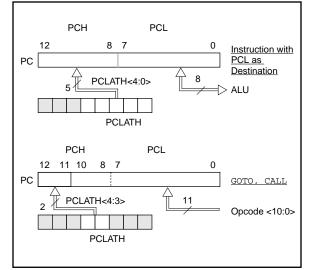

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-14 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### FIGURE 4-14: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc- | Note 1: | There are no status bits to indicate stack overflow or stack underflow conditions.                                                                                   |

|----------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  | Note 2: | called PUSH or POP. These are actions<br>that occur from the execution of the CALL,<br>RETURN, RETLW, and RETFIE instruc-<br>tions, or the vectoring to an interrupt |

### 4.4 <u>Program Memory Paging</u>

The PIC16C71X devices ignore both paging bits (PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC16C71X is not recommended since this may affect upward compatibility with future products.

| Address   | Name   | Bit 7 | Bit 6         | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------|---------------|------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7   | RB6           | RB5        | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB | Data Directic | on Registe | ər    |       |       |       |       | 1111 1111                | 1111 1111                 |

| 81h, 181h | OPTION | RBPU  | INTEDG        | TOCS       | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

### 6.0 TIMER0 MODULE

### Applicable Devices71071711715

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

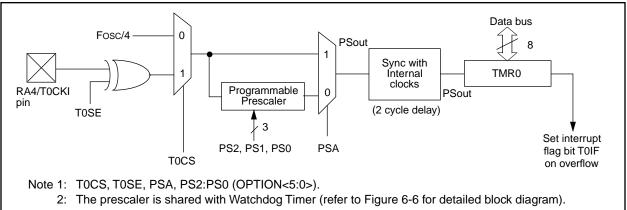

Figure 6-1 is a simplified block diagram of the Timer0 module.

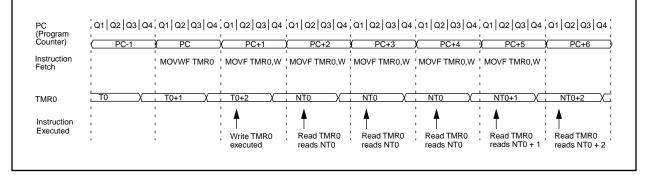

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION<4>). Clearing

FIGURE 6-1: TIMER0 BLOCK DIAGRAM

bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

### 6.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP. See Figure 6-4 for Timer0 interrupt timing.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

### 8.2 <u>Oscillator Configurations</u>

### 8.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

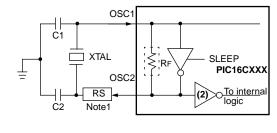

### 8.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

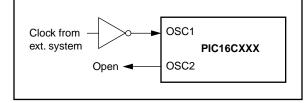

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-4). The PIC16CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 8-5).

### FIGURE 8-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 8-1 and Table 8-1 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: The buffer is on the OSC2 pin.

### FIGURE 8-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 8-1: CERAMIC RESONATORS, PIC16C71

| Ranges Tested:                                                          |                                                       |                                         |                                         |  |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|

| Mode                                                                    | Freq                                                  | OSC2                                    |                                         |  |  |  |  |

| ХТ                                                                      | 455 kHz<br>2.0 MHz<br>4.0 MHz                         | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 47 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |

| HS                                                                      | 8.0 MHz<br>16.0 MHz                                   | 15 - 68 pF<br>10 - 47 pF                | 15 - 68 pF<br>10 - 47 pF                |  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                                       |                                         |                                         |  |  |  |  |

| Resonators Used:                                                        |                                                       |                                         |                                         |  |  |  |  |

| 455 kHz Panasonic EFO-A455K04B ± 0.3%                                   |                                                       |                                         |                                         |  |  |  |  |

| 2.0 MHz                                                                 | Murata Erie CSA2.00MG ± 0.5%                          |                                         |                                         |  |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5%                          |                                         |                                         |  |  |  |  |

| 8.0 MHz                                                                 | Murata Erie CS                                        | SA8.00MT                                | ± 0.5%                                  |  |  |  |  |

| 16.0 MHz                                                                | Murata Erie CS                                        | SA16.00MX                               | ± 0.5%                                  |  |  |  |  |

| All reso                                                                | All resonators used did not have built-in capacitors. |                                         |                                         |  |  |  |  |

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16C71

| Mode | Freq                                     | OSC1                                | OSC2            |

|------|------------------------------------------|-------------------------------------|-----------------|

| LP   | 32 kHz                                   | 33 - 68 pF                          | 33 - 68 pF      |

|      | 200 kHz                                  | 15 - 47 pF                          | 15 - 47 pF      |

| XT   | 100 kHz                                  | 47 - 100 pF                         | 47 - 100 pF     |

|      | 500 kHz                                  | 20 - 68 pF                          | 20 - 68 pF      |

|      | 1 MHz                                    | 15 - 68 pF                          | 15 - 68 pF      |

|      | 2 MHz                                    | 15 - 47 pF                          | 15 - 47 pF      |

|      | 4 MHz                                    | 15 - 33 pF                          | 15 - 33 pF      |

| HS   | 8 MHz                                    | 15 - 47 pF                          | 15 - 47 pF      |

|      | 20 MHz                                   | 15 - 47 pF                          | 15 - 47 pF      |

|      | <b>tese values ar</b><br>tes at bottom o | <b>e for design guic</b><br>f page. | lance only. See |

### TABLE 8-10: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C710/71/711

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C710/711 |

|------------------------------------|-----------------------|--------------------|-----------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x                                |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu                                |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu                                |

| WDT Reset                          | 000h                  | 0000 luuu          | uu                                |

| WDT Wake-up                        | PC + 1                | นนน0 0นนน          | uu                                |

| Brown-out Reset (PIC16C710/711)    | 000h                  | 0001 luuu          | u0                                |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu                                |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### TABLE 8-11: RESET CONDITION FOR SPECIAL REGISTERS, PIC16C715

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | u10x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uuuu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | uuuu             |

| WDT Reset                          | 000h                  | 0000 luuu          | uuuu             |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uuuu             |

| Brown-out Reset                    | 000h                  | 0001 luuu          | uuu0             |

| Parity Error Reset                 | 000h                  | uuul Ouuu          | u0uu             |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register            | Power-on Reset,<br>Brown-out Reset <sup>(5)</sup> | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or<br>Interrupt |

|---------------------|---------------------------------------------------|--------------------------|------------------------------------|

| W                   | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| INDF                | N/A                                               | N/A                      | N/A                                |

| TMR0                | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCL                 | 0000h                                             | 0000h                    | PC + 1 <sup>(2)</sup>              |

| STATUS              | 0001 1xxx                                         | 000g quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>           |

| FSR                 | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PORTA               | x 0000                                            | u 0000                   | u uuuu                             |

| PORTB               | XXXX XXXX                                         | uuuu uuuu                | นนนน นนนน                          |

| PCLATH              | 0 0000                                            | 0 0000                   | u uuuu                             |

| INTCON              | 0000 000x                                         | 0000 000u                | uuuu uuuu <sup>(1)</sup>           |

| ADRES               | XXXX XXXX                                         | นนนน นนนน                | นนนน นนนน                          |

| ADCON0              | 00-0 0000                                         | 00-0 0000                | uu-u uuuu                          |

| OPTION              | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| TRISA               | 1 1111                                            | 1 1111                   | u uuuu                             |

| TRISB               | 1111 1111                                         | 1111 1111                | นนนน นนนน                          |

| PCON <sup>(4)</sup> | 0u                                                | uu                       |                                    |

| ADCON1              | 00                                                | 00                       |                                    |

### TABLE 8-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS, PIC16C710/71/711

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 8-10 for reset value for specific condition.

4: The PCON register is not implemented on the PIC16C71.

5: Brown-out reset is not implemented on the PIC16C71.

| FIGURE 8-22: WAKE-UP FROM SLEEP THROUGH INTERRUP |

|--------------------------------------------------|

|--------------------------------------------------|

| CLKOUT(4)                                                                          | ////               | (            | //                    | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u> |                  | /           |

|------------------------------------------------------------------------------------|--------------------|--------------|-----------------------|-----------------------------------------------|------------------|-------------|

| · .                                                                                | 1                  | 1 1          |                       |                                               | / IN             | /           |

| INTE flag                                                                          |                    | 1 1          | 1                     | 1 I<br>1 I                                    | 1<br>1           |             |

| (INTCON<1>)                                                                        | <br> <br>          |              | 1<br><del> </del><br> | Interrupt Latency<br>(Note 2)                 |                  |             |

| GIE bit<br>(INTCON<7>)                                                             | <br> <br> <br>     | Processor in | 1<br>1<br>1           |                                               |                  |             |

| STRUCTION FLOW                                                                     | 1<br>1<br>1        | SLEEP        | <br> <br>             | 1 1<br>1 1<br>1 1                             | 1                |             |

| PC X PC                                                                            | PC+1               | PC+2         | V PC+2                | ↓<br>↓ PC + 2 ↓                               | ( <u>0004h</u> ) | 0005h       |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | SLEEP Inst(PC + 1) |              | Inst(PC + 2)          | 1 1<br>1 1<br>1 1                             | Inst(0004h)      | Inst(0005h) |

| Instruction { Inst(PC                                                              | - 1) SLEEP         |              | Inst(PC + 1)          | Dummy cycle                                   | Dummy cycle      | Inst(0004h) |

Δ. CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 8.9 **Program Verification/Code Protection**

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 8.10 **ID** Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

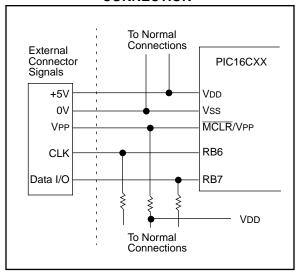

#### 8.11 In-Circuit Serial Programming

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

### FIGURE 8-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| GOTO                                                          | Unconditional Branch                                                                                                                                                                          |                     |                 |                |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------|--|--|--|--|

| Syntax:                                                       | [ label ]                                                                                                                                                                                     | GOTO                | k               |                |  |  |  |  |

| Operands:                                                     | $0 \le k \le 20$                                                                                                                                                                              | 047                 |                 |                |  |  |  |  |

| Operation:                                                    | $k \rightarrow PC < PCLATH$                                                                                                                                                                   |                     | PC<12:1         | 1>             |  |  |  |  |

| Status Affected:                                              | None                                                                                                                                                                                          |                     |                 |                |  |  |  |  |

| Encoding:                                                     | 10                                                                                                                                                                                            | 1kkk                | kkkk            | kkkk           |  |  |  |  |

| Description:                                                  | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                 |                |  |  |  |  |

| Words:                                                        | 1                                                                                                                                                                                             |                     |                 |                |  |  |  |  |

| Cycles:                                                       | 2                                                                                                                                                                                             |                     |                 |                |  |  |  |  |

| Q Cycle Activity:                                             | Q1                                                                                                                                                                                            | Q2                  | Q3              | Q4             |  |  |  |  |

| 1st Cycle                                                     | Decode                                                                                                                                                                                        | Read<br>literal 'k' | Process<br>data | Write to<br>PC |  |  |  |  |

| 2nd Cycle                                                     | NOP                                                                                                                                                                                           | NOP                 | NOP             | NOP            |  |  |  |  |

| Example GOTO THERE<br>After Instruction<br>PC = Address THERE |                                                                                                                                                                                               |                     |                 |                |  |  |  |  |

| INCF              | Increment f                                                                                                                  |               |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|

| Syntax:           | [label] INCF f,d                                                                                                             |               |  |  |  |  |  |

| Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                     |               |  |  |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$ (dest)                                                                                                 |               |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                            |               |  |  |  |  |  |

| Encoding:         | 00 1010 dfff                                                                                                                 | ffff          |  |  |  |  |  |

| Description:      | The contents of register 'f' a mented. If 'd' is 0 the result in the W register. If 'd' is 1 th placed back in register 'f'. | is placed     |  |  |  |  |  |

| Words:            | 1                                                                                                                            |               |  |  |  |  |  |

| Cycles:           | 1                                                                                                                            |               |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3                                                                                                                     | Q4            |  |  |  |  |  |

|                   | Decode Read register data                                                                                                    | Write to dest |  |  |  |  |  |

| Example           | INCF CNT, 1                                                                                                                  |               |  |  |  |  |  |

|                   | Before Instruction<br>CNT = 0<br>Z = 0                                                                                       | ٢F            |  |  |  |  |  |

|                   | After Instruction                                                                                                            |               |  |  |  |  |  |

|                   | $\begin{array}{rcl} CNT &=& 0;\\ Z &=& 1 \end{array}$                                                                        | <00           |  |  |  |  |  |

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                                                                                                            |                         |                 |               |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|---------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                         | INCFSZ                  | f,d             |               |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                  | 27                      |                 |               |  |  |  |

| Operation:        | (f) + 1 $\rightarrow$                                                                                                                                                                                                                                                                                             | (dest), s               | kip if resu     | ult = 0       |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                              |                         |                 |               |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                                                                                | 1111                    | dfff            | ffff          |  |  |  |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a 2Tcy<br>instruction. |                         |                 |               |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                 |                         |                 |               |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                              |                         |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                                                | Q2                      | Q3              | Q4            |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                                                                            | Read<br>register<br>'f' | Process<br>data | Write to dest |  |  |  |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                                       |                         |                 |               |  |  |  |

|                   | `Q1                                                                                                                                                                                                                                                                                                               | <br>Q2                  | Q3              | Q4            |  |  |  |

|                   | NOP                                                                                                                                                                                                                                                                                                               | NOP                     | NOP             | NOP           |  |  |  |

| Example           |                                                                                                                                                                                                                                                                                                                   | NT, 1<br>DOP            |                 |               |  |  |  |

|                   | S<br>FINUE<br>E +1                                                                                                                                                                                                                                                                                                |                         |                 |               |  |  |  |

| IORLW             |                 |                     | eral with                                  |               |

|-------------------|-----------------|---------------------|--------------------------------------------|---------------|

| Syntax:           | [ label ]       | IORLW               | К                                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                                            |               |

| Operation:        | (W) .OR.        | $k \rightarrow (W)$ | )                                          |               |

| Status Affected:  | Z               |                     |                                            |               |

| Encoding:         | 11              | 1000                | kkkk                                       | kkkk          |

| Description:      | OR'ed wit       | h the eigh          | W register<br>t bit literal<br>ne W regist | 'k'. The      |

| Words:            | 1               |                     |                                            |               |

| Cycles:           | 1               |                     |                                            |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                                         | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data                            | Write to<br>W |

| Example           | IORLW           | 0x35                |                                            |               |

|                   | Before In       |                     | 1                                          |               |

|                   |                 | W =                 | 0x9A                                       |               |

|                   | After Inst      |                     |                                            |               |

|                   |                 | W =                 | 0xBF                                       |               |

| NOP               | No Operation |       |      |      |  |  |  |  |

|-------------------|--------------|-------|------|------|--|--|--|--|

| Syntax:           | [ label ]    | NOP   |      |      |  |  |  |  |

| Operands:         | None         |       |      |      |  |  |  |  |

| Operation:        | No opera     | ition |      |      |  |  |  |  |

| Status Affected:  | None         |       |      |      |  |  |  |  |

| Encoding:         | 00           | 0000  | 0xx0 | 0000 |  |  |  |  |

| Description:      | No operat    | ion.  |      |      |  |  |  |  |

| Words:            | 1            |       |      |      |  |  |  |  |

| Cycles:           | 1            |       |      |      |  |  |  |  |

| Q Cycle Activity: | Q1           | Q2    | Q3   | Q4   |  |  |  |  |

|                   | Decode       | NOP   | NOP  | NOP  |  |  |  |  |

| Example           | NOP          |       |      |      |  |  |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                                                               |        |                    |                    |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                           | RETFIE |                    |                    |  |  |  |

| Operands:         | None                                                                                                                                                                                                                |        |                    |                    |  |  |  |

| Operation:        | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                             |        |                    |                    |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                |        |                    |                    |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                  | 0000   | 0000               | 1001               |  |  |  |

| Monda             | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |        |                    |                    |  |  |  |

| Words:            | 1                                                                                                                                                                                                                   |        |                    |                    |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                                   |        |                    |                    |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                  | Q2     | Q3                 | Q4                 |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                                              | NOP    | Set the<br>GIE bit | Pop from the Stack |  |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                                                                 | NOP    | NOP                | NOP                |  |  |  |

| Example           | RETFIE                                                                                                                                                                                                              |        |                    |                    |  |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                           | tion Reg                                       | gister                                               |                                         |  |  |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|--|--|

| Syntax:          | [ label ]                                                                                          | OPTION                                         | ٧                                                    |                                         |  |  |

| Operands:        | None                                                                                               |                                                |                                                      |                                         |  |  |

| Operation:       | $(W)\toOF$                                                                                         | PTION                                          |                                                      |                                         |  |  |

| Status Affected: | None                                                                                               |                                                |                                                      |                                         |  |  |

| Encoding:        | 00                                                                                                 | 0000                                           | 0110                                                 | 0010                                    |  |  |

| Description:     | The conter<br>loaded in the<br>instruction<br>patibility with<br>Since OPT<br>register, the<br>it. | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |  |  |

| Words:           | 1                                                                                                  |                                                |                                                      |                                         |  |  |

| Cycles:          | 1                                                                                                  |                                                |                                                      |                                         |  |  |

| Example          |                                                                                                    |                                                |                                                      |                                         |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction. |                                                |                                                      |                                         |  |  |

### SLEEP

| [ label ]                                                                                                                                                                                                                                      | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| None                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                           |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TO, PD                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 00                                                                                                                                                                                                                                             | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 8.8 for more details |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 1                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 1                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Q1                                                                                                                                                                                                                                             | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Decode                                                                                                                                                                                                                                         | NOP                                                                                                                                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                      | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| SLEEP                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |  |

| SUBLW             | Subtract         | W from              | Literal                                      |             |

|-------------------|------------------|---------------------|----------------------------------------------|-------------|

| Syntax:           | [ label ]        | SUBLW               | / k                                          |             |

| Operands:         | $0 \le k \le 25$ | 55                  |                                              |             |

| Operation:        | k - (W) →        | • (W)               |                                              |             |

| Status Affected:  | C, DC, Z         |                     |                                              |             |

| Encoding:         | 11               | 110x                | kkkk                                         | kkkk        |

| Description:      | ment meth        | od) from t          | otracted (2's<br>he eight bit<br>n the W reg | iteral 'k'. |

| Words:            | 1                |                     |                                              |             |

| Cycles:           | 1                |                     |                                              |             |

| Q Cycle Activity: | Q1               | Q2                  | Q3                                           | Q4          |

|                   | Decode           | Read<br>literal 'k' | Process<br>data                              | Write to W  |

| Example 1:        | SUBLW            | 0x02                |                                              |             |

|                   | Before In        | struction           |                                              |             |

|                   |                  | W =<br>C =<br>Z =   | 1<br>?<br>?                                  |             |

|                   | After Inst       | ruction             |                                              |             |

|                   |                  | W =<br>C =<br>Z =   | 1<br>1; result is<br>0                       | s positive  |

| Example 2:        | Before In        | -                   | 0                                            |             |

| Example 2.        | Delete III       | W =                 | 2                                            |             |

|                   |                  | C =                 | ?                                            |             |

|                   |                  | Z =                 | ?                                            |             |

|                   | After Inst       |                     | 0                                            |             |

|                   |                  | W =<br>C =<br>Z =   | 0<br>1; result i<br>1                        | s zero      |

| Example 3:        | Before In        | struction           |                                              |             |

|                   |                  | W =                 | 3                                            |             |

|                   |                  | C =<br>Z =          | ?<br>?                                       |             |

|                   | After Inst       | _                   |                                              |             |

|                   |                  | W =                 | 0xFF                                         |             |