Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc715-04-so |

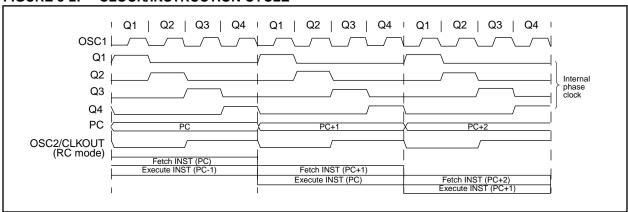

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

### 3.2 <u>Instruction Flow/Pipelining</u>

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### 4.2 <u>Data Memory Organization</u>

The data memory is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow Bank 1$

RP0 (STATUS<5>) =  $0 \rightarrow Bank 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain special function registers. Some "high use" special function registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

FIGURE 4-4: PIC16C710/71 REGISTER FILE MAP

| File          |                     |                                    | File         |

|---------------|---------------------|------------------------------------|--------------|

| Addres        | ss                  | I                                  | Address      |

| 00h           | INDF <sup>(1)</sup> | INDF <sup>(1)</sup>                | 80h          |

| 01h           | TMR0                | OPTION                             | 81h          |

| 02h           | PCL                 | PCL                                | 82h          |

| 03h           | STATUS              | STATUS                             | 83h          |

| 04h           | FSR                 | FSR                                | 84h          |

| 05h           | PORTA               | TRISA                              | 85h          |

| 06h           | PORTB               | TRISB                              | 86h          |

| 07h           |                     | PCON <sup>(2)</sup>                | 87h          |

| 08h           | ADCON0              | ADCON1                             | 88h          |

| 09h           | ADRES               | ADRES                              | 89h          |

| 0Ah           | PCLATH              | PCLATH                             | 8Ah          |

| 0Bh           | INTCON              | INTCON                             | 8Bh          |

| 0Ch           |                     | General                            | 8Ch          |

|               |                     | Purpose                            |              |

|               | General<br>Purpose  | Register                           |              |

|               | Register            | Mapped                             |              |

|               | · ·                 | Mapped<br>in Bank 0 <sup>(3)</sup> |              |

| 2Fh           |                     |                                    | AFh          |

| 30h           |                     |                                    | B0h          |

|               |                     |                                    |              |

| '             |                     |                                    |              |

| l .           |                     |                                    |              |

|               |                     |                                    |              |

|               |                     | `                                  | 1            |

|               |                     |                                    |              |

|               |                     |                                    |              |

| 7Fh           |                     |                                    | FFh          |

| '             | Bank 0              | Bank 1                             |              |

|               | -                   |                                    |              |

|               | Unimplemented of    | data memory loca                   | tions, read  |

|               | as '0'.             |                                    |              |

| Note 1:<br>2: | Not a physical re   |                                    | ntad on the  |

| 2:            | PIC16C71.           | ter is not impleme                 | nted on the  |

| 3:            |                     | are unimplemented                  | d in Bank 1. |

|               | •                   | ese locations will a               | access the   |

|               | corresponding Ba    | ank 0 register.                    |              |

|               |                     |                                    |              |

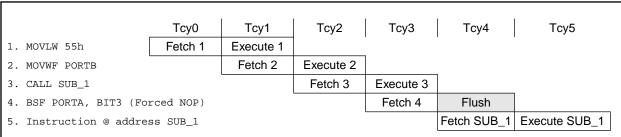

#### 4.2.2.5 PIR1 REGISTER

### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

Note:

### **5.0 I/O PORTS**

### Applicable Devices 710 71 711 715

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit latch.

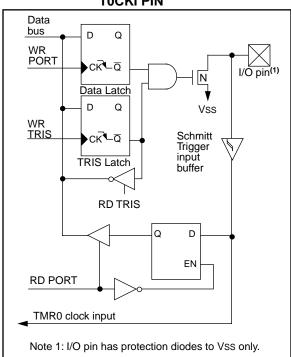

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### **EXAMPLE 5-1: INITIALIZING PORTA**

```

BCF

STATUS, RP0

CLRF

PORTA

; Initialize PORTA by

; clearing output

; data latches

STATUS, RPO

; Select Bank 1

BSF

MOVLW

0xCF

; Value used to

; initialize data

; direction

MOVWF

TRISA

; Set RA<3:0> as inputs

; RA<4> as outputs

; TRISA<7:5> are always

; read as '0'.

```

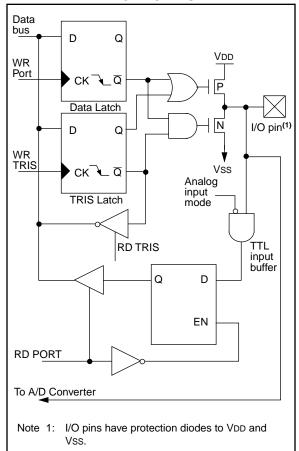

## FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 PINS

FIGURE 5-2: BLOCK DIAGRAM OF RA4/ TOCKI PIN

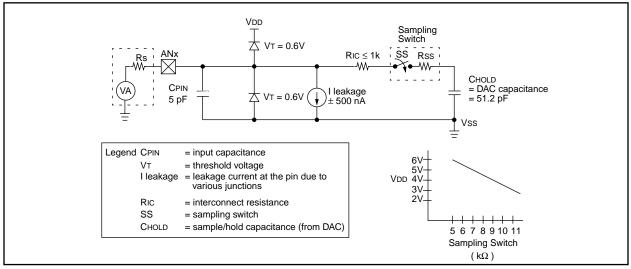

### 7.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 7-5. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is  $10~\text{k}\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

## EQUATION 7-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-TCAP/CHOLD(RIC + RSS + RS))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 pF)(1 k\Omega + Rss + Rs) ln(1/511)$

Example 7-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

$Rs = 10 k\Omega$

1/2 LSb error

$\text{Vdd} = 5\text{V} \rightarrow \text{Rss} = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

**Note 2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

Note 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

Note 4: After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

## EXAMPLE 7-1: CALCULATING THE MINIMUM REQUIRED AQUISITION TIME

TACQ = Amplifier Settling Time +

Holding Capacitor Charging Time +

Temperature Coefficient

TACQ =  $5 \mu s + TCAP + [(Temp - 25°C)(0.05 \mu s/°C)]$

TCAP = -CHOLD (Ric + Rss + Rs) In(1/511)

-51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020)

-51.2 pF (18 k $\Omega$ ) ln(0.0020)

-0.921 μs (-6.2364)

$5.747 \mu s$

TACQ =  $5 \mu s + 5.747 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

$10.747 \,\mu s + 1.25 \,\mu s$

$11.997 \mu s$

### FIGURE 7-5: ANALOG INPUT MODEL

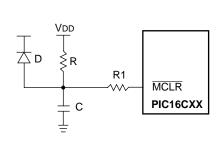

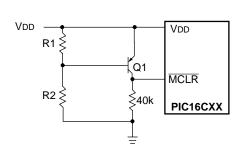

FIGURE 8-14: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

## FIGURE 8-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- Resistors should be adjusted for the characteristics of the transistor.

## FIGURE 8-16: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C710/711/715 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

| BTFSS             | Bit Test f, Skip if Set                                                                                                                           |                      |                    | _       | CALL         | Call Subroutine                                                                                                                                           |                              |                              |                                           |             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------------------------------|-------------|

| Syntax:           | [ <i>label</i> ] B                                                                                                                                | ΓFSS f,b             |                    |         |              | Syntax:                                                                                                                                                   | [label] CALL k               |                              |                                           |             |

| Operands:         | $0 \le f \le 12$                                                                                                                                  |                      |                    |         |              | Operands:                                                                                                                                                 | $0 \le k \le 2047$           |                              |                                           |             |

|                   | 0 ≤ b < 7                                                                                                                                         |                      |                    |         | Operation:   | (PC)+ 1-                                                                                                                                                  | → TOS,                       |                              |                                           |             |

| Operation:        | skip if $(f < b >) = 1$                                                                                                                           |                      |                    |         |              |                                                                                                                                                           | $k \rightarrow PC < 10:0>$ , |                              |                                           |             |

| Status Affected:  | None                                                                                                                                              |                      |                    |         |              |                                                                                                                                                           | •                            | 1<4:3>) -                    | → PC<12                                   | :11>        |

| Encoding:         | 01                                                                                                                                                | 11bb                 | bfff               | ffff    |              | Status Affected:                                                                                                                                          | None                         | 1                            | 1                                         |             |

| Description:      |                                                                                                                                                   | register 'f' i       |                    | he next | -            | Encoding:                                                                                                                                                 | 10                           | 0kkk                         | kkkk                                      | kkkk        |

|                   | instruction is executed. If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2TcY instruction. |                      |                    |         | Description: | Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of |                              |                              | ck. The<br>s loaded<br>r bits of          |             |

| Words:            | 1                                                                                                                                                 |                      |                    |         |              |                                                                                                                                                           |                              |                              | rom PCLAT                                 |             |

| Cycles:           | 1(2)                                                                                                                                              |                      |                    |         |              | Words:                                                                                                                                                    | 1                            | •                            |                                           |             |

| Q Cycle Activity: | Q1                                                                                                                                                | Q2                   | Q3                 | Q4      |              | Cycles:                                                                                                                                                   | 2                            |                              |                                           |             |

|                   | Decode                                                                                                                                            | Read<br>register 'f' | Process<br>data    | NOP     |              | Q Cycle Activity:                                                                                                                                         | Q1                           | Q2                           | Q3                                        | Q4          |

| If Skip:          | (2nd Cyc                                                                                                                                          | cle)                 |                    |         |              | 1st Cycle                                                                                                                                                 | Decode                       | Read<br>literal 'k',         | Process<br>data                           | Write to PC |

| ·                 | Q1                                                                                                                                                | Q2                   | Q3                 | Q4      | 7            |                                                                                                                                                           |                              | Push PC<br>to Stack          | data                                      |             |

|                   | NOP                                                                                                                                               | NOP                  | NOP                | NOP     |              | 2nd Cycle                                                                                                                                                 | NOP                          | NOP                          | NOP                                       | NOP         |

| Example           | After Inst                                                                                                                                        | truction             | FLAG, 1<br>PROCESS |         |              | Example                                                                                                                                                   | After Inst                   | PC = A<br>truction<br>PC = A | THERE  Address HE  Address TH  Address HE | HERE        |

|                   |                                                                                                                                                   | if FLAG<1:           | address F          |         |              |                                                                                                                                                           |                              |                              |                                           |             |

## **PIC16C71X**

| CLRF              | Clear f                                                        | Clear f                                                               |                 |                       |  |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [label] C                                                      | LRF f                                                                 |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$                                               | 27                                                                    |                 |                       |  |  |  |

| Operation:        | $00h \rightarrow (f)$ $1 \rightarrow Z$                        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                 |                       |  |  |  |

| Status Affected:  | Z                                                              |                                                                       |                 |                       |  |  |  |

| Encoding:         | 00                                                             | 0001                                                                  | 1fff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set. |                                                                       |                 |                       |  |  |  |

| Words:            | 1                                                              |                                                                       |                 |                       |  |  |  |

| Cycles:           | 1                                                              |                                                                       |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                             | Q2                                                                    | Q3              | Q4                    |  |  |  |

|                   | Decode                                                         | Read<br>register<br>'f'                                               | Process<br>data | Write<br>register 'f' |  |  |  |

|                   |                                                                |                                                                       |                 |                       |  |  |  |

| Example           | CLRF                                                           | FLAC                                                                  | E_REG           |                       |  |  |  |

|                   | Before In                                                      | struction<br>FLAG_RE                                                  |                 | 0x5A                  |  |  |  |

|                   | After Inst                                                     | ruction                                                               |                 |                       |  |  |  |

FLAG\_REG = 0x00

| CLRW              | Clear W                                                              |                                         |                 |               |  |  |

|-------------------|----------------------------------------------------------------------|-----------------------------------------|-----------------|---------------|--|--|

| Syntax:           | [ label ]                                                            | CLRW                                    |                 |               |  |  |

| Operands:         | None                                                                 |                                         |                 |               |  |  |

| Operation:        | $\begin{array}{c} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | $00h \rightarrow (W)$ $1 \rightarrow Z$ |                 |               |  |  |

| Status Affected:  | Z                                                                    |                                         |                 |               |  |  |

| Encoding:         | 00 0001 0xxx xxxx                                                    |                                         |                 |               |  |  |

| Description:      | W register is cleared. Zero bit (Z) is set.                          |                                         |                 |               |  |  |

| Words:            | 1                                                                    |                                         |                 |               |  |  |

| Cycles:           | 1                                                                    |                                         |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                   | Q2                                      | Q3              | Q4            |  |  |

|                   | Decode                                                               | NOP                                     | Process<br>data | Write to<br>W |  |  |

| Example           | CLRW                                                                 |                                         |                 |               |  |  |

|                   | Before Instruction                                                   |                                         |                 |               |  |  |

|                   | After Inst                                                           | W =<br>ruction                          | 0x5A            |               |  |  |

|                   |                                                                      | W =<br>Z =                              | 0x00<br>1       |               |  |  |

| CLRWDT            | Clear Watchdog Timer                                                                                                  |          |                 |                         |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                             | CLRWD    | Т               |                         |  |  |  |

| Operands:         | None                                                                                                                  |          |                 |                         |  |  |  |

| Operation:        | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{TO}$<br>1 → $\overline{PD}$                                         |          |                 |                         |  |  |  |

| Status Affected:  | $\overline{TO}$ , $\overline{PD}$                                                                                     |          |                 |                         |  |  |  |

| Encoding:         | 00                                                                                                                    | 0000     | 0110            | 0100                    |  |  |  |

| Description:      | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are set. |          |                 |                         |  |  |  |

| Words:            | 1                                                                                                                     |          |                 |                         |  |  |  |

| Cycles:           | 1                                                                                                                     |          |                 |                         |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                    | Q2       | Q3              | Q4                      |  |  |  |

|                   | Decode                                                                                                                | NOP      | Process<br>data | Clear<br>WDT<br>Counter |  |  |  |

| Example           | CLRWDT                                                                                                                |          |                 |                         |  |  |  |

|                   | Before Instruction  WDT counter = ?  After Instruction                                                                |          |                 |                         |  |  |  |

|                   |                                                                                                                       | WDT cou  |                 | 0x00                    |  |  |  |

|                   |                                                                                                                       | WDT pres | scaler=<br>=    | 0                       |  |  |  |

|                   |                                                                                                                       | PD       | =               | 1                       |  |  |  |

| SUBWF             | Subtract                       | W from f                      |                                                                  |                  |

|-------------------|--------------------------------|-------------------------------|------------------------------------------------------------------|------------------|

| Syntax:           | [ label ]                      | SUBWF                         | f,d                                                              |                  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$ | 7                             |                                                                  |                  |

| Operation:        | (f) - (W) -                    | → (dest)                      |                                                                  |                  |

| Status Affected:  | C, DC, Z                       |                               |                                                                  |                  |

| Encoding:         | 00                             | 0010                          | dfff                                                             | ffff             |

| Description:      | ister from r<br>stored in th   | egister 'f'. I<br>ne W regist | nent metho<br>f 'd' is 0 the<br>er. If 'd' is 1<br>n register 'f | result is<br>the |

| Words:            | 1                              |                               |                                                                  |                  |

| Cycles:           | 1                              |                               |                                                                  |                  |

| Q Cycle Activity: | Q1                             | Q2                            | Q3                                                               | Q4               |

|                   | Decode                         | Read<br>register 'f'          | Process<br>data                                                  | Write to dest    |

| Example 1:        | SUBWF                          | REG1,1                        |                                                                  |                  |

|                   | Before In:                     | struction                     |                                                                  |                  |

|                   | REG1                           |                               | 3                                                                |                  |

|                   | W<br>C                         | =                             | 2                                                                |                  |

|                   | Z                              | =                             | ?                                                                |                  |

|                   | After Inst                     | ruction                       |                                                                  |                  |

|                   | REG1                           |                               | 1                                                                |                  |

|                   | W<br>C                         | =                             | 2<br>1; result is                                                | positive         |

|                   | Z                              | =                             | 0                                                                |                  |

| Example 2:        | Before In:                     | struction                     |                                                                  |                  |

|                   | REG1<br>W                      |                               | 2                                                                |                  |

|                   | C                              | =                             | ?                                                                |                  |

|                   | Z                              | =                             | ?                                                                |                  |

|                   | After Inst                     | ruction                       |                                                                  |                  |

|                   | REG1<br>W                      | =                             | 0                                                                |                  |

|                   | C                              | =                             | 1; result is                                                     | zero             |

|                   | Z                              | =                             | 1                                                                |                  |

| Example 3:        | Before In:                     | struction                     |                                                                  |                  |

|                   | REG1<br>W                      | =                             | 1                                                                |                  |

|                   | C                              | =                             | ?                                                                |                  |

|                   | Z                              | =                             | ?                                                                |                  |

|                   | After Inst                     | ruction                       |                                                                  |                  |

|                   | REG1<br>W                      | =                             | 0xFF<br>2                                                        |                  |

|                   | С                              | =                             | 0; result is                                                     | negative         |

|                   | Z                              | =                             | 0                                                                |                  |

|                   |                                |                               |                                                                  |                  |

| SWAPF             | Swap Nibbles in f                                                                                                                                            |                      |                 |               |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|---------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                    | [ label ] SWAPF f,d  |                 |               |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                           |                      |                 |               |  |  |  |  |

| Operation:        | $(f<3:0>) \rightarrow (dest<7:4>),  (f<7:4>) \rightarrow (dest<3:0>)$                                                                                        |                      |                 |               |  |  |  |  |

| Status Affected:  | None                                                                                                                                                         |                      |                 |               |  |  |  |  |

| Encoding:         | 00                                                                                                                                                           | 1110                 | dfff            | ffff          |  |  |  |  |

| Description:      | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0 the result is placed in W register. If 'd' is 1 the result is placed in register 'f'. |                      |                 |               |  |  |  |  |

| Words:            | 1                                                                                                                                                            |                      |                 |               |  |  |  |  |

| Cycles:           | 1                                                                                                                                                            |                      |                 |               |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                           | Q2                   | Q3              | Q4            |  |  |  |  |

|                   | Decode                                                                                                                                                       | Read<br>register 'f' | Process<br>data | Write to dest |  |  |  |  |

| Example           | SWAPF                                                                                                                                                        | REG,                 | 0               |               |  |  |  |  |

|                   | Before In                                                                                                                                                    | struction            |                 |               |  |  |  |  |

|                   | REG1 = 0xA5                                                                                                                                                  |                      |                 |               |  |  |  |  |

|                   | After Inst                                                                                                                                                   | ruction              |                 |               |  |  |  |  |

|                   |                                                                                                                                                              | REG1<br>W            | = 0x/<br>= 0x5  |               |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                      |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                     |  |  |  |  |

| Operation:       | $\text{(W)} \rightarrow \text{TRIS register f;}$                                                                                                                    |  |  |  |  |

| Status Affected: | None                                                                                                                                                                |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                   |  |  |  |  |

| Description:     | The instruction is supported for code compatibility with the PIC16C5X products. Since TRIS registers are readable and writable, the user can directly address them. |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |

| Example          |                                                                                                                                                                     |  |  |  |  |

|                  | To maintain upward compatibility with future PIC16CXX products, do not use this instruction.                                                                        |  |  |  |  |

|                  |                                                                                                                                                                     |  |  |  |  |

VDD = 3.0V, WDT disabled, -40°C to +125°C

BOR enabled VDD = 5.0V

## 11.2 DC Characteristics: PIC16LC710-04 (Commercial, Industrial, Extended) PIC16LC711-04 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated) Operating temperature  $\leq$  TA  $\leq$  +70°C (commercial) 0°C **DC CHARACTERISTICS** -40°C  $\leq$  TA  $\leq$  +85°C (industrial) -40°C  $\leq$  TA  $\leq$  +125°C (extended) Conditions **Param** Characteristic Sym Min Typ† Max Units No. D001 Supply Voltage Commercial/Industrial VDD 2.5 6.0 ٧ LP, XT, RC osc configuration (DC - 4 MHz) Extended VDD 3.0 6.0 ٧ LP, XT, RC osc configuration (DC - 4 MHz) D002\* RAM Data Retention VDR V 1.5 Voltage (Note 1) D003 VDD start voltage to **VPOR** V Vss See section on Power-on Reset for details ensure internal Poweron Reset signal D004\* VDD rise rate to ensure SVDD 0.05 V/ms See section on Power-on Reset for details internal Power-on Reset signal **Brown-out Reset** D005 **B**VDD 3.7 4.0 4.3 V BODEN configuration bit is enabled Voltage D010 Supply Current IDD 2.0 3.8 mΑ XT, RC osc configuration Fosc = 4 MHz, VDD = 3.0V (Note 4) (Note 2) D010A 22.5 48 LP osc configuration μΑ Fosc = 32 kHz, VDD = 3.0V, WDT disabled D015 **Brown-out Reset** 300\* 500 BOR enabled VDD = 5.0V  $\Delta \text{IBOR}$ μΑ Current (Note 5) D020 Power-down Current 7.5 30 VDD = 3.0V, WDT enabled, -40°C to +85°C **IPD** иΑ D021 0.9 5 VDD = 3.0V. WDT disabled, 0°C to +70°C (Note 3) иΑ D021A μΑ VDD = 3.0V, WDT disabled, -40°C to +85°C 0.9 5

\* These parameters are characterized but not tested.

Brown-out Reset

Current (Note 5)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

10

500

μΑ

μΑ

0.9

300\*

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

$\Delta$ IBOR

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

D021B

D023

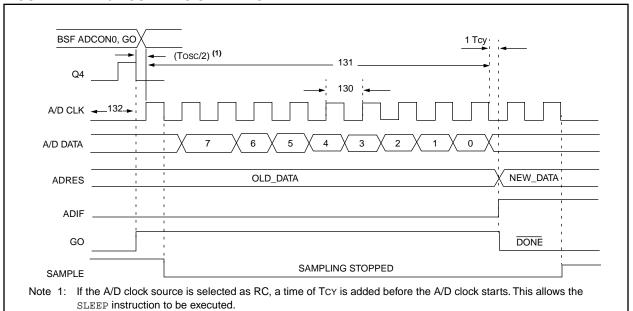

### FIGURE 11-7: A/D CONVERSION TIMING

TABLE 11-7: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                     |                                 | Min    | Тур†    | Max          | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|------------------------------------|---------------------------------|--------|---------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                   | PIC16 <b>C</b> 710/711          | 1.6    | _       | _            | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                    | PIC16 <b>LC</b> 710/711         | 2.0    | _       | _            | μs    | Tosc based, VREF full range                                                                                                                                                                                 |

|              |      |                                    | PIC16 <b>C</b> 710/711          | 2.0*   | 4.0     | 6.0          | μs    | A/D RC mode                                                                                                                                                                                                 |

|              |      |                                    | PIC16 <b>LC</b> 710/711         | 3.0*   | 6.0     | 9.0          | μs    | A/D RC mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not including S/H | time). (Note 1)                 | _      | 9.5     | _            | TAD   |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                   |                                 | Note 2 | 20      | _            | μs    |                                                                                                                                                                                                             |

|              |      |                                    |                                 | 5*     | Ι       | _            | μs    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 19.5 mV @ 5.12V) from the last sampled voltage (as stated on Chold). |

| 134          | TGO  | Q4 to AD clock sta                 | art                             | _      | Tosc/2§ | <del>_</del> | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

| 135          | Tswc | Switching from co                  | $nvert \rightarrow sample time$ | 1.5§   | _       | _            | TAD   |                                                                                                                                                                                                             |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

<sup>§</sup> This specification ensured by design.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>2:</sup> See Section 7.1 for min conditions.

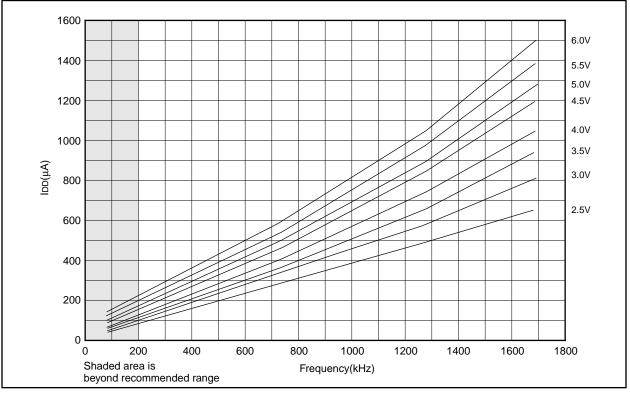

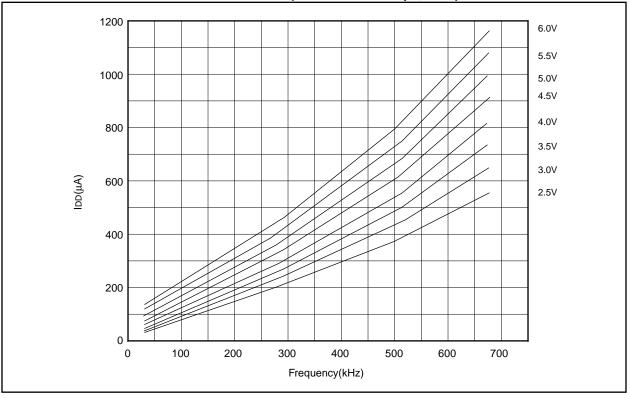

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

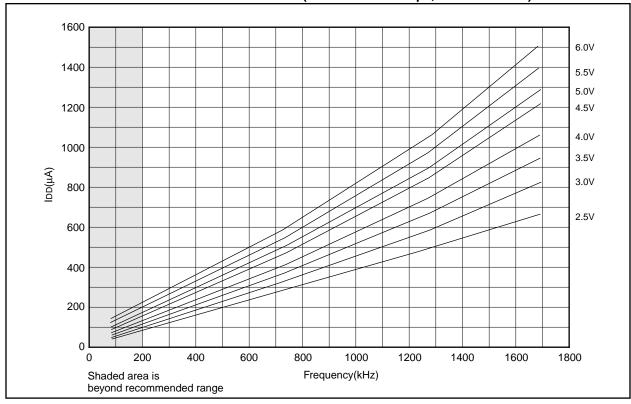

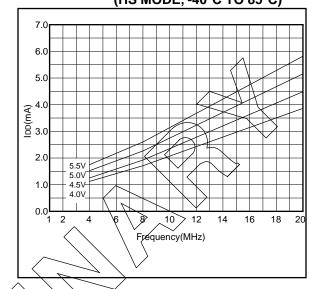

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 12-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

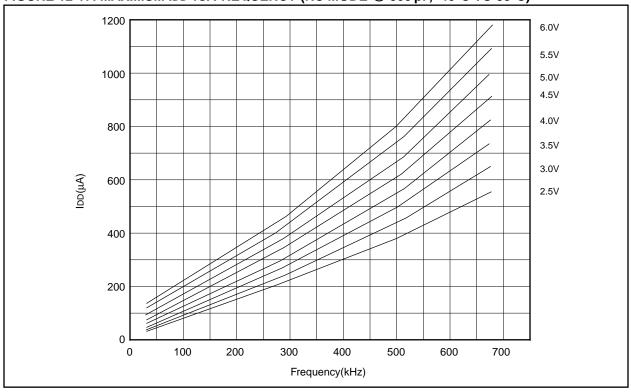

FIGURE 12-18: TYPICAL IDD vs.

CAPACITANCE @ 500 kHz

(RC MODE)

TABLE 12-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average         |        |  |  |  |

|--------|------|-----------------|--------|--|--|--|

| Cext   | Rext | Fosc @ 5V, 25°C |        |  |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |  |

|        | 100k | 268 kHz         | ± 1.1% |  |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ± 1.0% |  |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |  |

|        | 100k | 77.2 kHz        | ± 1.0% |  |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |  |

|        | 5k   | 501 kHz         | ± 1.2% |  |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

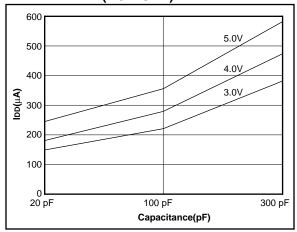

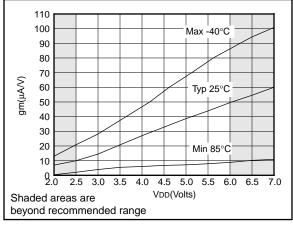

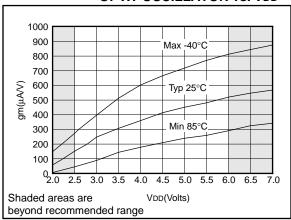

FIGURE 12-19: TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

FIGURE 12-20: TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

FIGURE 12-21: TRANSCONDUCTANCE(gm)

OF XT OSCILLATOR vs. VDD

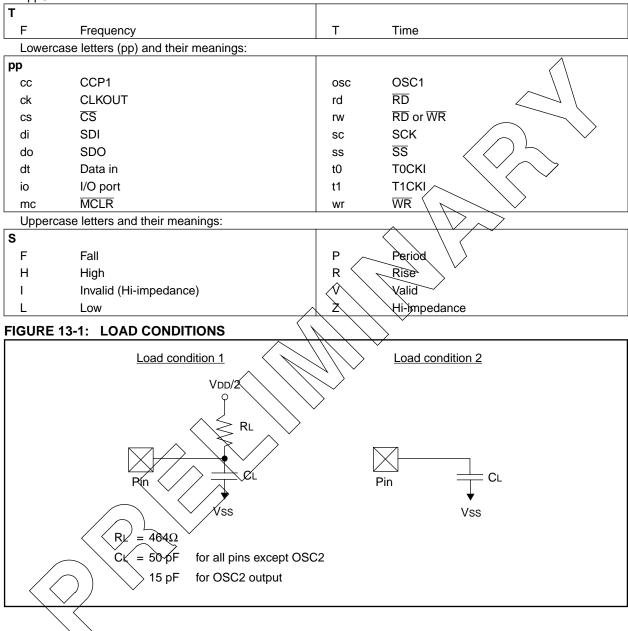

### 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

**Applicable Devices** | 710 | 71 | 711 | 715

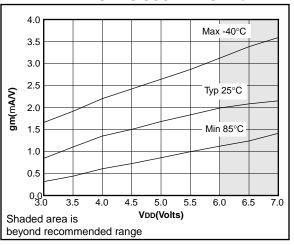

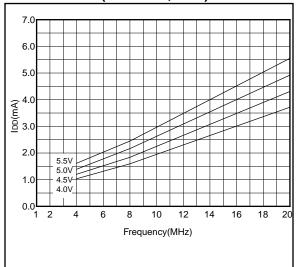

FIGURE 14-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

FIGURE 14-30: MAXIMUM IDD vs. FREQUENCY (HS MODE, -40°C TO 85°C)

### PIC16C71X

Applicable Devices 710 71 711 715

15.3 DC Characteristics: PIC16C71-04 (Commercial, Industrial)

PIC16C71-20 (Commercial, Industrial) PIC16LC71-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

OOperating temperature  $0^{\circ}C$   $\leq TA \leq +70^{\circ}C$  (commercial)

**DC CHARACTERISTICS**  $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ (industrial)}$

Operating voltage VDD range as described in DC spec Section 15.1

and Section 15.2.

| Param | Characteristic                     | Sym   | Min       | Тур | Max    | Units | Conditions                                          |

|-------|------------------------------------|-------|-----------|-----|--------|-------|-----------------------------------------------------|

| No.   |                                    |       |           | Ť   |        |       |                                                     |

|       | Input Low Voltage                  |       |           |     |        |       |                                                     |

|       | I/O ports                          | VIL   |           |     |        |       |                                                     |

| D030  | with TTL buffer                    |       | Vss       | -   | 0.15V  | V     | For entire VDD range                                |

| D031  | with Schmitt Trigger buffer        |       | Vss       | -   | 0.8V   | V     | 4.5 ≤ VDD ≤ 5.5V                                    |

| D032  | MCLR, OSC1 (in RC mode)            |       | Vss       | -   | 0.2VDD | V     |                                                     |

| D033  | OSC1 (in XT, HS and LP)            |       | Vss       | -   | 0.3VDD | V     | Note1                                               |

|       | Input High Voltage                 |       |           |     |        |       |                                                     |

|       | I/O ports (Note 4)                 | VIH   |           | -   |        |       |                                                     |

| D040  | with TTL buffer                    |       | 2.0       | -   | Vdd    | V     | 4.5 ≤ VDD ≤ 5.5V                                    |

| D040A |                                    |       | 0.25VDD   | -   | Vdd    |       | For entire VDD range                                |

|       |                                    |       | + 0.8V    |     |        |       |                                                     |

| D041  | with Schmitt Trigger buffer        |       | 0.85VDD   | -   | Vdd    |       | For entire VDD range                                |

| D042  | MCLR, RB0/INT                      |       | 0.85VDD   | -   | Vdd    | V     |                                                     |

| D042A | OSC1 (XT, HS and LP)               |       | 0.7Vdd    | -   | Vdd    | V     | Note1                                               |

| D043  | OSC1 (in RC mode)                  |       | 0.9Vdd    | -   | Vdd    | V     |                                                     |

| D070  | PORTB weak pull-up current         | IPURB | 50        | 250 | †400   | μΑ    | VDD = 5V, VPIN = VSS                                |

|       | Input Leakage Current (Notes 2, 3) |       |           |     |        |       |                                                     |

| D060  | I/O ports                          | lıL   | -         | -   | ±1     | μΑ    | Vss ≤ VPIN ≤ VDD, Pin at hi-<br>impedance           |

| D061  | MCLR, RA4/T0CKI                    |       | -         | -   | ±5     | μΑ    | Vss ≤ VPIN ≤ VDD                                    |

| D063  | OSC1                               |       | -         | -   | ±5     | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc configuration   |

|       | Output Low Voltage                 |       |           |     |        |       | -                                                   |

| D080  | I/O ports                          | Vol   | -         | -   | 0.6    | V     | IOL = $8.5$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C |

| D083  | OSC2/CLKOUT (RC osc config)        |       | -         | -   | 0.6    | V     | IOL = 1.6mA, VDD = 4.5V,<br>-40°C to +85°C          |

|       | Output High Voltage                |       |           |     |        |       |                                                     |

| D090  | I/O ports (Note 3)                 | Vон   | VDD - 0.7 | -   | -      | V     | IOH = -3.0mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D092  | OSC2/CLKOUT (RC osc config)        |       | VDD - 0.7 | -   | -      | V     | IOH = -1.3mA, VDD = 4.5V,<br>-40°C to +85°C         |

| D130* | Open-Drain High Voltage            | Vod   | -         | -   | 14     | V     | RA4 pin                                             |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: PIC16C71 Rev. "Ax" INT pin has a TTL input buffer. PIC16C71 Rev. "Bx" INT pin has a Schmitt Trigger input buffer.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt trigger input. It is not recommended that the PIC16C71 be driven with external clock in RC mode.

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES FOR PIC16C71

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

Note: The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution while 'max' or 'min' represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

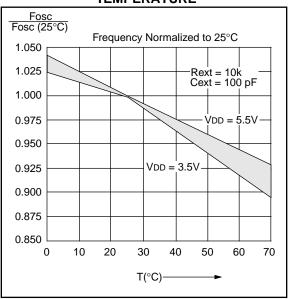

FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs.

TEMPERATURE

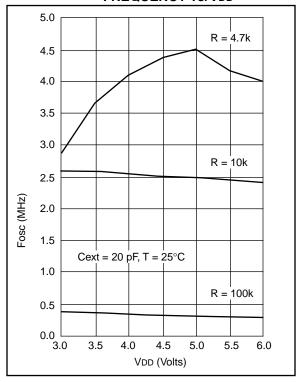

## FIGURE 16-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

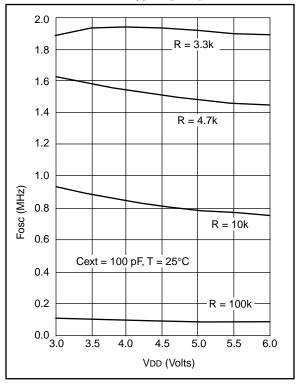

FIGURE 16-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

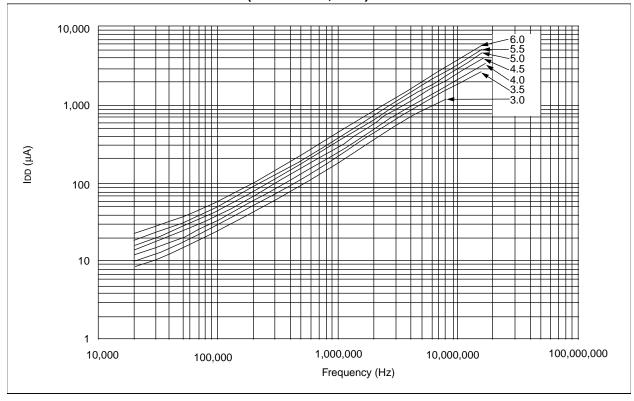

FIGURE 16-12: TYPICAL IDD Vs. FREQ (EXT CLOCK, 25°C)

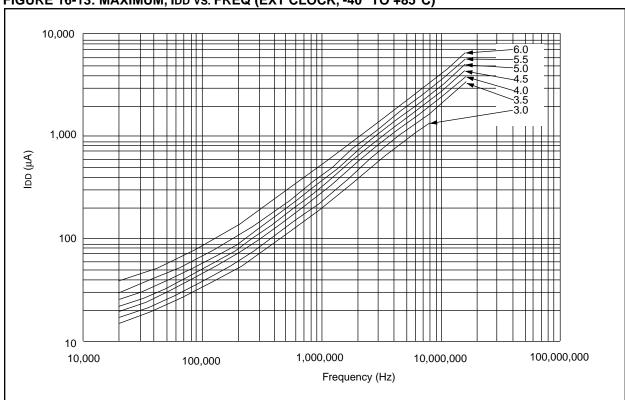

FIGURE 16-13: MAXIMUM, IDD VS. FREQ (EXT CLOCK, -40° TO +85°C)

## **PIC16C71X**

| TO bit                     |                |

|----------------------------|----------------|

| TRISA Register             | 14, 16, 25     |

| TRISB Register             |                |

| Two's Complement           | 7              |

| U                          |                |

| Upward Compatibility       | 3              |

| UV Erasable Devices        |                |

| W                          |                |

| W Register                 |                |

| ALU                        | 7              |

| Wake-up from SLEEP         | 66             |

| Watchdog Timer (WDT)       | 47, 52, 56, 65 |

| WDT                        | 56             |

| Block Diagram              | 65             |

| Programming Considerations | 65             |

| Timeout                    | 57, 58         |

| WDT Period                 |                |

| WDTE bit                   |                |

| Z                          |                |

| Z bit                      | 17             |

| Zero bit                   | 7              |

### **LIST OF EXAMPLES**

| Example 3-1:<br>Example 4-1: | Instruction Pipeline FlowCall of a Subroutine in Page 1 from | 10   |  |

|------------------------------|--------------------------------------------------------------|------|--|

| ·                            | Page 0                                                       | . 24 |  |

| Example 4-2:                 | Indirect Addressing                                          | . 24 |  |

| Example 5-1:                 | Initializing PORTA                                           |      |  |

| Example 5-2:                 | Initializing PORTB                                           | . 27 |  |

| Example 5-3:                 | Read-Modify-Write Instructions on an I/O Port                | 30   |  |

| Example 6-1:                 | Changing Prescaler (Timer0→WDT)                              |      |  |

| Example 6-2:                 | Changing Prescaler (WDT→Timer0)                              |      |  |

| Equation 7-1:                | A/D Minimum Charging Time                                    |      |  |

| Example 7-1:                 | Calculating the Minimum Required                             |      |  |

|                              | Aquisition Time                                              | . 40 |  |

| Example 7-2:                 | A/D Conversion                                               |      |  |

| Example 7-3:                 | 4-bit vs. 8-bit Conversion Times                             |      |  |

| Example 8-1:                 | Saving STATUS and W Registers                                |      |  |

|                              | in RAM                                                       | . 64 |  |

| LIST OF FIGURES              |                                                              |      |  |

| Figure 3-1:                  | PIC16C71X Block Diagram                                      | 8    |  |

| Figure 3-2:                  | Clock/Instruction Cycle                                      |      |  |

| Figure 4-1:                  | PIC16C710 Program Memory Map                                 |      |  |

| 3.                           | and Stack                                                    | . 11 |  |

| Figure 4-2:                  | PIC16C71/711 Program Memory Map                              |      |  |

| · ·                          | and Stack                                                    | . 11 |  |

| Figure 4-3:                  | PIC16C715 Program Memory Map                                 |      |  |

|                              | and Stack                                                    | . 11 |  |

| Figure 4-4:                  | PIC16C710/71 Register File Map                               | . 12 |  |

| Figure 4-5:                  | PIC16C711 Register File Map                                  | . 13 |  |

| Figure 4-6:                  | PIC16C715 Register File Map                                  |      |  |

| Figure 4-7:                  | Status Register (Address 03h, 83h)                           |      |  |

| Figure 4-8:                  | OPTION Register (Address 81h, 181h)                          |      |  |

| Figure 4-9:                  | INTCON Register (Address 0Bh, 8Bh)                           |      |  |

| Figure 4-10:                 | PIE1 Register (Address 8Ch)                                  |      |  |

| Figure 4-11:                 | PIR1 Register (Address 0Ch)                                  | . 21 |  |

| Figure 4-12:                 | PCON Register (Address 8Eh),<br>PIC16C710/711                | . 22 |  |

| Figure 4-13:                 | PCON Register (Address 8Eh),                                 |      |  |

| · ·                          | PIC16C715                                                    | . 22 |  |

| Figure 4-14:                 | Loading of PC In Different Situations                        |      |  |

| Figure 4-15:                 | Direct/Indirect Addressing                                   |      |  |

| Figure 5-1:                  | Block Diagram of RA3:RA0 Pins                                |      |  |

| Figure 5-2:                  | Block Diagram of RA4/T0CKI Pin                               |      |  |

| Figure 5-3:                  | Block Diagram of RB3:RB0 Pins                                | . 27 |  |

| Figure 5-4:                  | Block Diagram of RB7:RB4 Pins                                |      |  |

|                              | (PIC16C71)                                                   | . 28 |  |

| Figure 5-5:                  | Block Diagram of RB7:RB4 Pins                                |      |  |

| F:                           | (PIC16C710/711/715)                                          |      |  |

| Figure 5-6:                  | Successive I/O Operation                                     |      |  |

| Figure 6-1:                  | Timer0 Block Diagram                                         | J I  |  |

| Figure 6-2:                  | Timer0 Timing: Internal Clock/                               | 21   |  |

| Figure 6-3:                  | No Prescale Timer0 Timing: Internal Clock/                   | . 31 |  |

| rigule 0-3.                  | Prescale 1:2                                                 | 32   |  |

| Figure 6-4:                  | Timer0 Interrupt Timing                                      |      |  |

| Figure 6-5:                  | Timer0 Timing with External Clock                            |      |  |

| Figure 6-6:                  | Block Diagram of the Timer0/                                 | . 50 |  |

| 90.000.                      | WDT Prescaler                                                | . 34 |  |

| Figure 7-1:                  | ADCON0 Register (Address 08h),                               |      |  |

| <b>3</b>                     | PIC16C710/71/711                                             | . 37 |  |

| Figure 7-2:                  | ADCON0 Register (Address 1Fh),                               |      |  |

| -                            | PIC16C715                                                    | . 38 |  |

|                              |                                                              |      |  |