Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc715-04i-p |

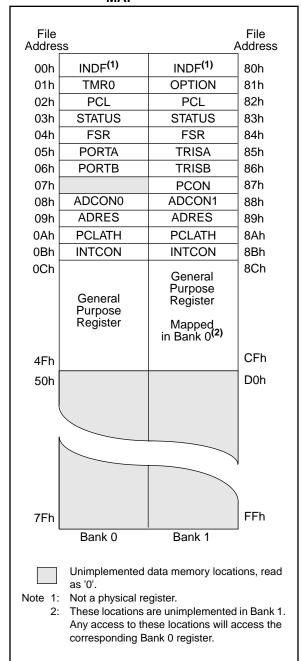

FIGURE 4-5: PIC16C711 REGISTER FILE MAP

FIGURE 4-6: PIC16C715 REGISTER FILE MAP

|                 | IVIZ                 |                     | 1               |  |  |  |  |  |  |  |

|-----------------|----------------------|---------------------|-----------------|--|--|--|--|--|--|--|

| File<br>Address | 3                    |                     | File<br>Address |  |  |  |  |  |  |  |

| 00h             | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |  |  |

| 01h             | TMR0                 | OPTION              | 81h             |  |  |  |  |  |  |  |

| 02h             | PCL                  | PCL                 | 82h             |  |  |  |  |  |  |  |

| 03h             | STATUS               | STATUS              | 83h             |  |  |  |  |  |  |  |

| 04h             | FSR                  | FSR                 | 84h             |  |  |  |  |  |  |  |

| 05h             | PORTA                | TRISA               | 85h             |  |  |  |  |  |  |  |

| 06h             | PORTB                | TRISB               | 86h             |  |  |  |  |  |  |  |

| 07h             |                      |                     | 87h             |  |  |  |  |  |  |  |

| 08h             |                      |                     | 88h             |  |  |  |  |  |  |  |

| 09h             |                      |                     | 89h             |  |  |  |  |  |  |  |

| 0Ah             | PCLATH               | PCLATH              | 8Ah             |  |  |  |  |  |  |  |

| 0Bh             | INTCON               | INTCON              | - 8Bh           |  |  |  |  |  |  |  |

| 0Ch             | PIR1                 | PIE1                | 8Ch             |  |  |  |  |  |  |  |

| 0Dh             |                      |                     | 8Dh             |  |  |  |  |  |  |  |

| 0Eh             |                      | PCON                | 8Eh             |  |  |  |  |  |  |  |

| 0Fh             |                      |                     | 8Fh             |  |  |  |  |  |  |  |

| 10h             |                      |                     | 90h             |  |  |  |  |  |  |  |

| 11h             |                      |                     | 91h             |  |  |  |  |  |  |  |

| 12h             |                      |                     | 92h             |  |  |  |  |  |  |  |

| 13h             |                      |                     | 93h             |  |  |  |  |  |  |  |

| 14h             |                      |                     | 94h             |  |  |  |  |  |  |  |

| 15h             |                      |                     | 95h             |  |  |  |  |  |  |  |

| 16h             |                      |                     | 96h             |  |  |  |  |  |  |  |

| 17h             |                      |                     | 97h             |  |  |  |  |  |  |  |

| 18h             |                      |                     | 98h             |  |  |  |  |  |  |  |

| 19h             |                      |                     | 99h             |  |  |  |  |  |  |  |

| 1Ah             |                      |                     | 9Ah             |  |  |  |  |  |  |  |

| 1Bh             |                      |                     | 9Bh             |  |  |  |  |  |  |  |

| 1Ch             |                      |                     | 9Ch             |  |  |  |  |  |  |  |

| 1Dh             |                      |                     | 9Dh             |  |  |  |  |  |  |  |

| 1Eh             | ADRES                |                     | 9Eh             |  |  |  |  |  |  |  |

| 1Fh             | ADCON0               | ADCON1              | 9Fh             |  |  |  |  |  |  |  |

| 20h             |                      |                     | A0h             |  |  |  |  |  |  |  |

|                 | General              | General             | Aon             |  |  |  |  |  |  |  |

|                 | Purpose<br>Register  | Purpose<br>Register |                 |  |  |  |  |  |  |  |

|                 | register             | Negistei            | BFh             |  |  |  |  |  |  |  |

|                 |                      |                     | C0h             |  |  |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |  |  |

|                 |                      |                     | 7               |  |  |  |  |  |  |  |

| 7Fh             | 7Fh FFh              |                     |                 |  |  |  |  |  |  |  |

| Bank 0 Bank 1   |                      |                     |                 |  |  |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |  |  |

|                 | Jnimplemented dat    | a memory locatio    | ns, read        |  |  |  |  |  |  |  |

|                 | as '0'.              |                     |                 |  |  |  |  |  |  |  |

| Note 1: N       | Not a physical regis | ter.                |                 |  |  |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |  |  |

#### 4.2.2.2 **OPTION REGISTER**

710 71 711 715 Applicable Devices

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

#### FIGURE 4-8: **OPTION REGISTER (ADDRESS 81h, 181h)**

| R/   | W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|------|-----|--------|-------|-------|-------|-------|-------|-------|

| RE   | 3PU | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit7 |     |        |       |       |       |       |       | bit0  |

= Readable bit W = Writable bit

U = Unimplemented bit, read as '0' - n = Value at POR reset

- bit 7: RBPU: PORTB Pull-up Enable bit

- 1 = PORTB pull-ups are disabled

- 0 = PORTB pull-ups are enabled by individual port latch values

- INTEDG: Interrupt Edge Select bit bit 6:

- 1 = Interrupt on rising edge of RB0/INT pin

- 0 = Interrupt on falling edge of RB0/INT pin

- bit 5: T0CS: TMR0 Clock Source Select bit

- 1 = Transition on RA4/T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- T0SE: TMR0 Source Edge Select bit bit 4:

- 1 = Increment on high-to-low transition on RA4/T0CKI pin

- 0 = Increment on low-to-high transition on RA4/T0CKI pin

- bit 3: PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0: PS2:PS0: Prescaler Rate Select bits

| Bit Value                              | TMR0 Rate                                 | WDT Rate                         |

|----------------------------------------|-------------------------------------------|----------------------------------|

| 000<br>001<br>010<br>011<br>100<br>101 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16 |

| 110<br>111                             | 1 : 128<br>1 : 256                        | 1 : 64<br>1 : 128                |

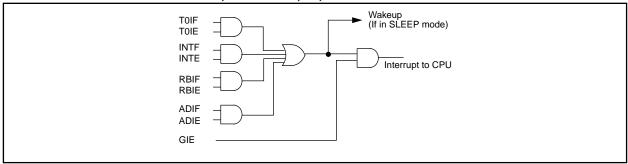

### 4.2.2.3 INTCON REGISTER

## **Applicable Devices** | 710 | 71 | 711 | 715

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

Note:

## FIGURE 4-9: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | ADIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  |

| bit7  |       |       |       |       |       |       | bit0  |

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'- n = Value at POR reset

bit 7: **GIE:**(1) Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

bit 6: ADIE: A/D Converter Interrupt Enable bit

1 = Enables A/D interrupt 0 = Disables A/D interrupt

bit 5: T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4: INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3: RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2: T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1: INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0: RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

Note 1: For the PIC16C71, if an interrupt occurs while the GIE bit is being cleared, the GIE bit may be unintentionally re-enabled by the RETFIE instruction in the user's Interrupt Service Routine. Refer to Section 8.5 for a detailed description.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 4.2.2.4 PIE1 REGISTER

Applicable Devices710 71 711 715

**Note:** Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the Peripheral interrupts.

## FIGURE 4-10: PIE1 REGISTER (ADDRESS 8Ch)

|   | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0  |

|---|-----|-------|-----|-----|-----|-----|-----|------|

|   | _   | ADIE  | _   | _   | _   | _   | _   | _    |

| b | it7 |       |     |     |     |     |     | bit0 |

R = Readable bit W = Writable bit

U = Unimplemented bit,

read as '0' n = Value at POR reset

bit 7: Unimplemented: Read as '0'

bit 6: ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D interrupt 0 = Disables the A/D interrupt bit 5-0: **Unimplemented:** Read as '0'

DS30272A-page 20

TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                        |  |  |  |

|--------------|------|--------|-------------------------------------------------|--|--|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                    |  |  |  |

| RA1/AN1      | bit1 | TTL    | put/output or analog input                      |  |  |  |

| RA2/AN2      | bit2 | TTL    | nput/output or analog input                     |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input/VREF               |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0 |  |  |  |

|              |      |        | Output is open drain type                       |  |  |  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3       | Bit 2        | Bit 2 Bit 1 |        | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|---------|-------------|--------------|-------------|--------|--------------------------|---------------------------|

| 05h     | PORTA  | _     | _     | _     | RA4     | RA3         | RA2          | RA1         | RA0    | x 0000                   | u 0000                    |

| 85h     | TRISA  | _     | _     | _     | PORTA D | Data Direct | tion Registe |             | 1 1111 | 1 1111                   |                           |

| 9Fh     | ADCON1 | _     | _     | _     | _       | _           | _            | PCFG1       | PCFG0  | 00                       | 00                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

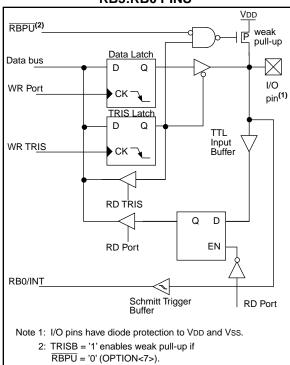

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

### **EXAMPLE 5-2: INITIALIZING PORTB**

```

BCF

STATUS, RP0

CLRF

; Initialize PORTB by

PORTR

; clearing output

; data latches

BSF

STATUS, RPO

; Select Bank 1

MOVLW

0xCF

; Value used to

; initialize data

; direction

MOVWF

TRISB

; Set RB<3:0> as inputs

; RB<5:4> as outputs

; RB<7:6> as inputs

```

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, "Implementing Wake-Up on Key Stroke" (AN552).

Note: For the PIC16C71 if a change on the I/O pin should occur

when the read operation is being executed (start of the Q2 cycle), then interrupt flag bit RBIF may not get set.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

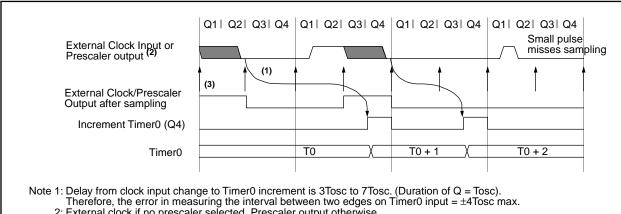

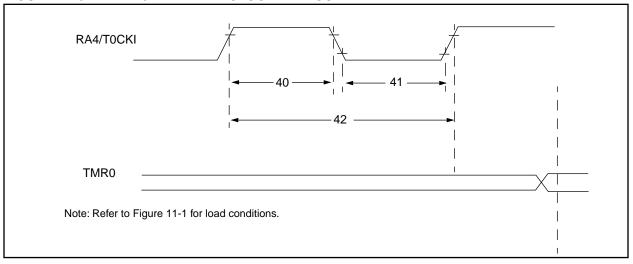

#### 6.2 **Using Timer0 with an External Clock**

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### TMR0 INCREMENT DELAY 6.2.2

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

- 2: External clock if no prescaler selected, Prescaler output otherwise.

- 3: The arrows indicate the points in time where sampling occurs.

# 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Applicable Devices 710 71 711 715

The analog-to-digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 7-1 and Figure 7-2, controls the operation of the A/D module. The ADCON1 register, shown in Figure 7-3 configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

## FIGURE 7-1: ADCONO REGISTER (ADDRESS 08h), PIC16C710/71/711

| R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R = Readable bit                                                             |

|-------|-------|-----|-------|-------|---------|-------|-------|------------------------------------------------------------------------------|

| ADCS1 | ADCS0 | (1) | CHS1  | CHS0  | GO/DONE | ADIF  | ADON  |                                                                              |

| bit7  |       |     |       |       |         |       | bit0  | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

bit 7-6: ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from an RC oscillation)

bit 5: Unimplemented: Read as '0'.

bit 4-3: CHS1:CHS0: Analog Channel Select bits

00 = channel 0, (RA0/AN0)

01 = channel 1, (RA1/AN1)

10 = channel 2, (RA2/AN2)

11 = channel 3, (RA3/AN3)

bit 2: GO/DONE: A/D Conversion Status bit

If ADON = 1:

1 = A/D conversion in progress (setting this bit starts the A/D conversion)

0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)

bit 1: ADIF: A/D Conversion Complete Interrupt Flag bit

1 = conversion is complete (must be cleared in software)

0 = conversion is not complete

bit 0: ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shutoff and consumes no operating current

**Note 1:** Bit5 of ADCON0 is a General Purpose R/W bit for the PIC16C710/711 only. For the PIC16C71, this bit is unimplemented, read as '0'.

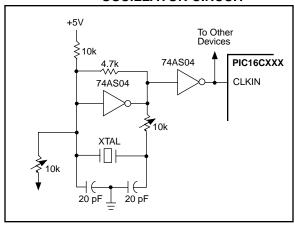

## 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 8-6 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

FIGURE 8-6: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

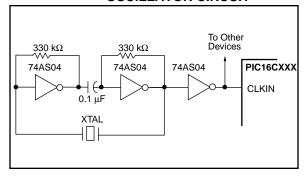

Figure 8-7 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

FIGURE 8-7: EXTERNAL SERIES

RESONANT CRYSTAL

OSCILLATOR CIRCUIT

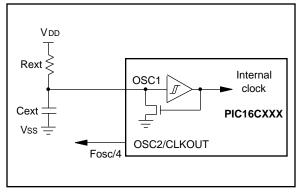

### 8.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 8-8 shows how the R/C combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

FIGURE 8-8: RC OSCILLATOR MODE

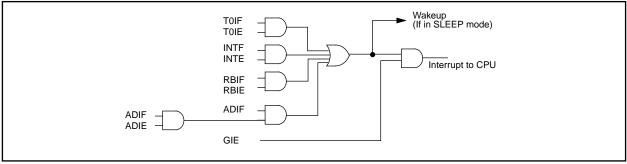

FIGURE 8-17: INTERRUPT LOGIC, PIC16C710, 71, 711

FIGURE 8-18: INTERRUPT LOGIC, PIC16C715

| INCFSZ            | Increme                                                       | nt f, Skip                                                     | o if O          |                  | IORLW             | Inclusive       | e OR Lit            | eral with                     | W             |

|-------------------|---------------------------------------------------------------|----------------------------------------------------------------|-----------------|------------------|-------------------|-----------------|---------------------|-------------------------------|---------------|

| Syntax:           | [ label ]                                                     | INCFSZ                                                         | z f,d           |                  | Syntax:           | [ label ]       | IORLW               | k                             |               |

| Operands:         | $0 \le f \le 12$                                              | 27                                                             |                 |                  | Operands:         | $0 \le k \le 2$ | 55                  |                               |               |

|                   | $d \in [0,1]$                                                 |                                                                |                 |                  | Operation:        | (W) .OR.        | $k \rightarrow (W)$ | )                             |               |

| Operation:        | $(f) + 1 \rightarrow$                                         | (dest), s                                                      | kip if resu     | ult = 0          | Status Affected:  | Z               |                     |                               |               |

| Status Affected:  | None                                                          |                                                                |                 |                  | Encoding:         | 11              | 1000                | kkkk                          | kkkk          |

| Encoding:         | 00                                                            | 1111                                                           | dfff            | ffff             | Description:      |                 |                     | W registe                     |               |

| Description:      | The conte<br>mented. If<br>in the W re                        | 'd' is 0 the                                                   | e result is     | placed           |                   |                 | _                   | it bit literal<br>ne W regist |               |

|                   | placed bad                                                    | ck in regis                                                    | ter 'f'.        |                  | Words:            | 1               |                     |                               |               |

|                   | executed.<br>executed i                                       | If the resu                                                    | ılt is 0, a N   | IOP is           | Cycles:           | 1               |                     |                               |               |

|                   | instruction                                                   |                                                                | aking it a z    | 2101             | Q Cycle Activity: | Q1              | Q2                  | Q3                            | Q4            |

| Words:            | 1                                                             |                                                                |                 |                  |                   | Decode          | Read<br>literal 'k' | Process<br>data               | Write to<br>W |

| Cycles:           | 1(2)                                                          |                                                                |                 |                  |                   |                 | •                   |                               |               |

| Q Cycle Activity: | Q1                                                            | Q2                                                             | Q3              | Q4               | Example           | IORLW           | 0x35                |                               |               |

|                   | Decode                                                        | Read<br>register<br>'f'                                        | Process<br>data | Write to<br>dest |                   | Before Ir       | structior<br>W =    | n<br>0x9A                     |               |

| If Skip:          | (2nd Cyc                                                      |                                                                |                 |                  |                   | After Ins       | truction<br>W =     | 0xBF                          |               |

| •                 | Q1                                                            | Q2                                                             | Q3              | Q4               |                   |                 | Z =                 | 1                             |               |

|                   | NOP                                                           | NOP                                                            | NOP             | NOP              |                   |                 |                     |                               |               |

| Example           | HERE CONTINI  Before In PC After Inst CNT if CNT PC if CNT PC | struction<br>= add<br>ruction<br>= CN<br>= 0,<br>= add<br>≠ 0, | LC              | FINUE            |                   |                 |                     |                               |               |

11.3 DC Characteristics: PIC16C710-04 (Commercial, Industrial, Extended)

PIC16C711-04 (Commercial, Industrial, Extended)

PIC16C710-10 (Commercial, Industrial, Extended)

PIC16C711-10 (Commercial, Industrial, Extended)

PIC16C710-20 (Commercial, Industrial, Extended)

PIC16C711-20 (Commercial, Industrial, Extended)

PIC16LC710-04 (Commercial, Industrial, Extended)

PIC16LC711-04 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

Operating temperature 0°C  $\leq$  TA  $\leq$  +70°C (commercial) -40°C  $\leq$  TA  $\leq$  +85°C (industrial)

**DC CHARACTERISTICS**  $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C (industrial)}$   $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C (extended)}$

Operating voltage VDD range as described in DC spec Section 11.1 and

Section 11.2.

| Param | Characteristic                     | Sym   | Min     | Тур | Max     | Units | Conditions                      |

|-------|------------------------------------|-------|---------|-----|---------|-------|---------------------------------|

| No.   |                                    |       |         | †   |         |       |                                 |

|       | Input Low Voltage                  |       |         |     |         |       |                                 |

|       | I/O ports                          | VIL   |         |     |         |       |                                 |

| D030  | with TTL buffer                    |       | Vss     | -   | 0.15VDD | V     | For entire VDD range            |

| D030A |                                    |       | Vss     | -   | 0.8V    | V     | 4.5 ≤ VDD ≤ 5.5V                |

| D031  | with Schmitt Trigger buffer        |       | Vss     | -   | 0.2Vdd  | V     |                                 |

| D032  | MCLR, OSC1                         |       | Vss     | -   | 0.2Vdd  | V     |                                 |

|       | (in RC mode)                       |       |         |     |         |       |                                 |

| D033  | OSC1 (in XT, HS and LP)            |       | Vss     | -   | 0.3VDD  | V     | Note1                           |

|       | Input High Voltage                 |       |         |     |         |       |                                 |

|       | I/O ports                          | ViH   |         | -   |         |       |                                 |

| D040  | with TTL buffer                    |       | 2.0     | -   | Vdd     | V     | 4.5 ≤ VDD ≤ 5.5V                |

| D040A |                                    |       | 0.25VDD | -   | Vdd     | V     | For entire VDD range            |

|       |                                    |       | + 0.8V  |     |         |       |                                 |

| D041  | with Schmitt Trigger buffer        |       | 0.8VDD  | -   | Vdd     | V     | For entire VDD range            |

| D042  | MCLR, RB0/INT                      |       | 0.8VDD  | -   | Vdd     | V     |                                 |

| D042A | OSC1 (XT, HS and LP)               |       | 0.7Vdd  | -   | Vdd     | V     | Note1                           |

| D043  | OSC1 (in RC mode)                  |       | 0.9Vdd  | -   | Vdd     | V     |                                 |

| D070  | PORTB weak pull-up current         | IPURB | 50      | 250 | 400     | μΑ    | VDD = 5V, VPIN = VSS            |

|       | Input Leakage Current (Notes 2, 3) |       |         |     |         |       |                                 |

| D060  | I/O ports                          | lı∟   | -       | -   | ±1      | μΑ    | Vss ≤ VPIN ≤ VDD, Pin at hi-    |

|       |                                    |       |         |     |         |       | impedance                       |

| D061  | MCLR, RA4/T0CKI                    |       | -       | -   | ±5      | μΑ    | Vss ≤ VPIN ≤ VDD                |

| D063  | OSC1                               |       | -       | -   | ±5      | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS and LP |

|       |                                    |       |         |     |         |       | osc configuration               |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

FIGURE 11-6: TIMERO EXTERNAL CLOCK TIMINGS

## TABLE 11-5: TIMERO EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                 | Min                | Тур†                                   | Max | Units | Conditions |                                 |  |

|--------------|-----------|--------------------------------|--------------------|----------------------------------------|-----|-------|------------|---------------------------------|--|

| 40           | Tt0H      | T0CKI High Pulse Width         | No Prescaler       | 0.5Tcy + 20*                           | _   | _     | ns         | Must also meet                  |  |

|              |           |                                | With Prescaler     | 10*                                    | _   | _     | ns         | parameter 42                    |  |

| 41           | Tt0L      | T0CKI Low Pulse Width          | No Prescaler       | 0.5Tcy + 20*                           | _   | _     | ns         | Must also meet                  |  |

|              |           |                                | With Prescaler     | 10*                                    | _   | _     | ns         | parameter 42                    |  |

| 42           | Tt0P      | T0CKI Period                   |                    | Greater of:<br>20 ns or TCY + 40*<br>N | _   | _     | ns         | N = prescale value (2, 4,, 256) |  |

| 48           | Tcke2tmrl | Delay from external clock edge | to timer increment | 2Tosc                                  | _   | 7Tosc | _          |                                 |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

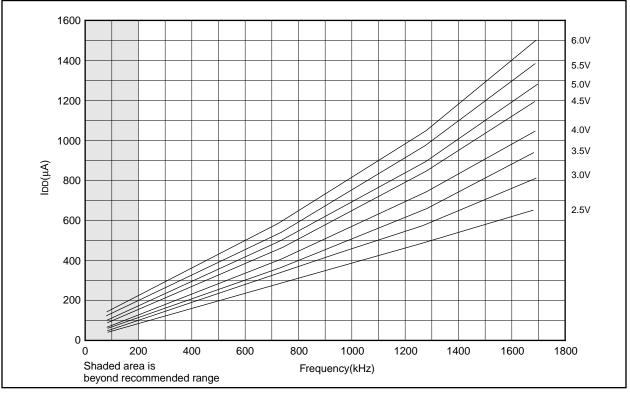

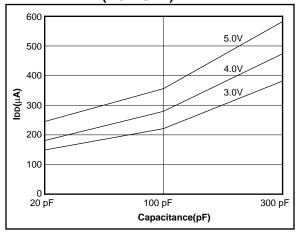

FIGURE 12-14: TYPICAL IDD vs. FREQUENCY (RC MODE @ 100 pF, 25°C)

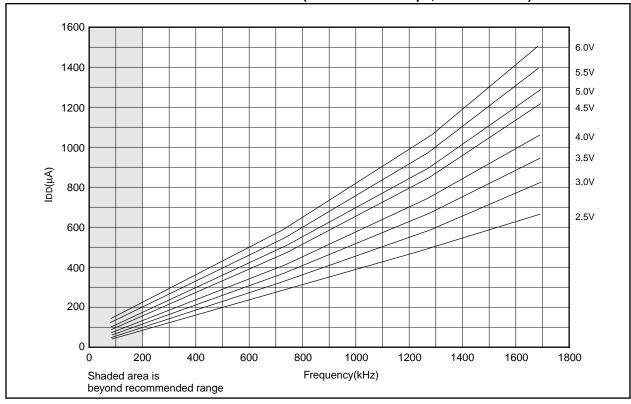

FIGURE 12-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

FIGURE 12-18: TYPICAL IDD vs.

CAPACITANCE @ 500 kHz

(RC MODE)

TABLE 12-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average         |        |  |  |

|--------|------|-----------------|--------|--|--|

| Cext   |      | Fosc @ 5V, 25°C |        |  |  |

| 22 pF  | 5k   | 4.12 MHz        | ± 1.4% |  |  |

|        | 10k  | 2.35 MHz        | ± 1.4% |  |  |

|        | 100k | 268 kHz         | ± 1.1% |  |  |

| 100 pF | 3.3k | 1.80 MHz        | ± 1.0% |  |  |

|        | 5k   | 1.27 MHz        | ± 1.0% |  |  |

|        | 10k  | 688 kHz         | ± 1.2% |  |  |

|        | 100k | 77.2 kHz        | ± 1.0% |  |  |

| 300 pF | 3.3k | 707 kHz         | ± 1.4% |  |  |

|        | 5k   | 501 kHz         | ± 1.2% |  |  |

|        | 10k  | 269 kHz         | ± 1.6% |  |  |

|        | 100k | 28.3 kHz        | ± 1.1% |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

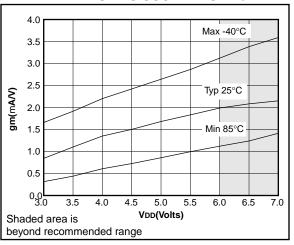

FIGURE 12-19: TRANSCONDUCTANCE(gm)

OF HS OSCILLATOR vs. VDD

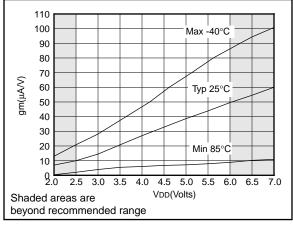

FIGURE 12-20: TRANSCONDUCTANCE(gm)

OF LP OSCILLATOR vs. VDD

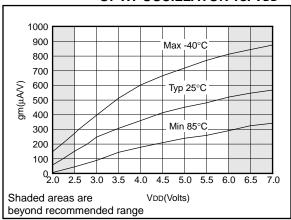

FIGURE 12-21: TRANSCONDUCTANCE(gm)

OF XT OSCILLATOR vs. VDD

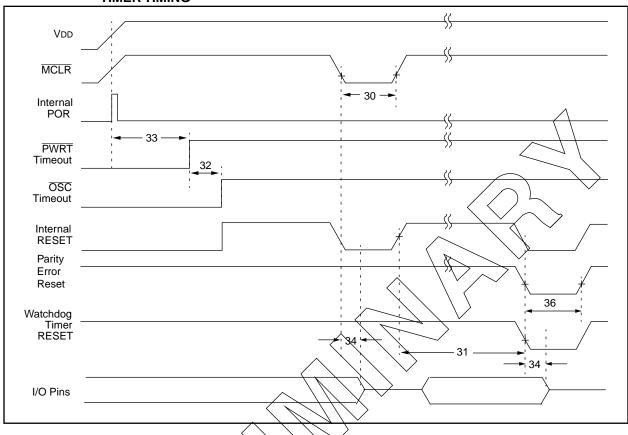

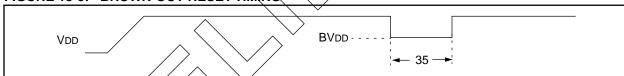

FIGURE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, AND POWER-UP TIMER TIMING

FIGURE 13-5: BROWN-OUT RESETTIMING

TABLE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter | Sym              | Characteristic                                         | Min | Typ†     | Max | Units | Conditions                                         |

|-----------|------------------|--------------------------------------------------------|-----|----------|-----|-------|----------------------------------------------------|

| No.       |                  |                                                        |     |          |     |       |                                                    |

| 30        | Zmc <sub>Z</sub> | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 31*       | Twdt             | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 32        | Tost             | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                 |

| 33*       | Tpwrt            | Power up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34        | Tıoz             | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                                                    |

| 35        | TBOR             | Brown-out Reset pulse width                            | 100 | _        | _   | μs    | VDD ≤ BVDD (D005)                                  |

| 36        | TPER             | Parity Error Reset                                     | _   | TBD      | _   | μs    |                                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

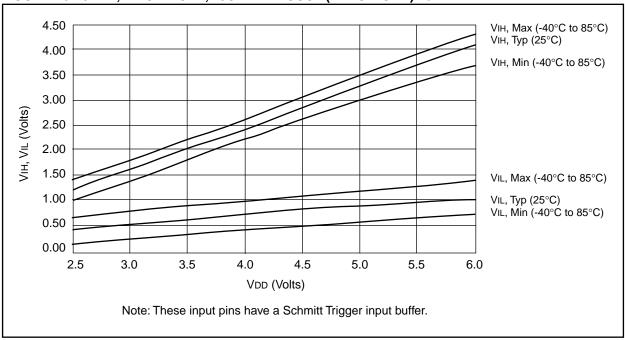

FIGURE 16-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) VS. VDD

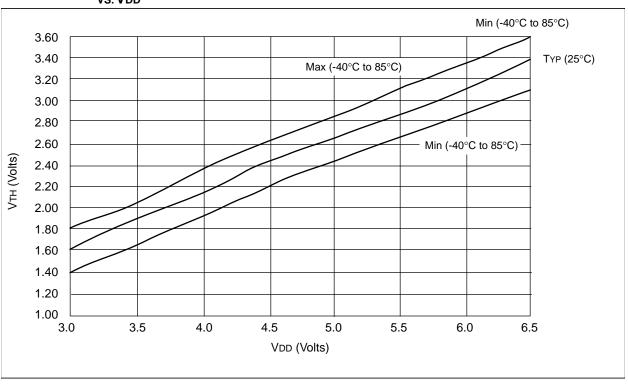

FIGURE 16-11: VTH (INPUT THRESHOLD VOLTAGE) OF OSC1 INPUT (IN XT, HS, AND LP MODES) VS. VDD

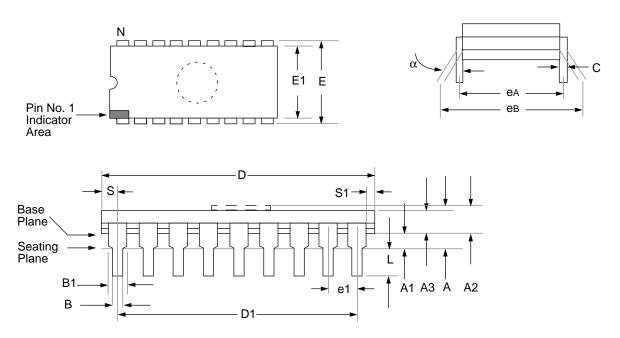

## 17.0 PACKAGING INFORMATION

## 17.1 18-Lead Ceramic CERDIP Dual In-line with Window (300 mil) (JW)

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |        |           |        |       |           |  |

|--------------------------------------------------|-------------|--------|-----------|--------|-------|-----------|--|

|                                                  | Millimeters |        |           | Inches |       |           |  |

| Symbol                                           | Min         | Max    | Notes     | Min    | Max   | Notes     |  |

| α                                                | 0°          | 10°    |           | 0°     | 10°   |           |  |

| Α                                                | _           | 5.080  |           | _      | 0.200 |           |  |

| A1                                               | 0.381       | 1.7780 |           | 0.015  | 0.070 |           |  |

| A2                                               | 3.810       | 4.699  |           | 0.150  | 0.185 |           |  |

| А3                                               | 3.810       | 4.445  |           | 0.150  | 0.175 |           |  |

| В                                                | 0.355       | 0.585  |           | 0.014  | 0.023 |           |  |

| B1                                               | 1.270       | 1.651  | Typical   | 0.050  | 0.065 | Typical   |  |

| С                                                | 0.203       | 0.381  | Typical   | 0.008  | 0.015 | Typical   |  |

| D                                                | 22.352      | 23.622 |           | 0.880  | 0.930 |           |  |

| D1                                               | 20.320      | 20.320 | Reference | 0.800  | 0.800 | Reference |  |

| E                                                | 7.620       | 8.382  |           | 0.300  | 0.330 |           |  |

| E1                                               | 5.588       | 7.874  |           | 0.220  | 0.310 |           |  |

| e1                                               | 2.540       | 2.540  | Reference | 0.100  | 0.100 | Reference |  |

| eA                                               | 7.366       | 8.128  | Typical   | 0.290  | 0.320 | Typical   |  |

| eB                                               | 7.620       | 10.160 |           | 0.300  | 0.400 |           |  |

| L                                                | 3.175       | 3.810  |           | 0.125  | 0.150 |           |  |

| N                                                | 18          | 18     |           | 18     | 18    |           |  |

| S                                                | 0.508       | 1.397  |           | 0.020  | 0.055 |           |  |

| S1                                               | 0.381       | 1.270  |           | 0.015  | 0.050 |           |  |

#### RB7:RB4 Port Pins ......28 INDEX Timer0 ......31 Timer0/WDT Prescaler ......34 Α Watchdog Timer ......65 A/D BODEN bit ......48 Accuracy/Error ......44 ADIF bit ......39 Brown-out Reset (BOR) .....53 Analog Input Model Block Diagram ......40 Analog-to-Digital Converter ......37 Configuring Analog Port Pins ......41 Configuring the Interrupt ......39 C16C71 47 Configuring the Module ......39 Carry bit ......7 Connection Considerations ......44 Conversion Clock .......41 CHS1 bit ......37 Conversion Time ......43 Clocking Scheme ......10 Conversions ......42 Code Examples Call of a Subroutine in Page 1 from Page 0 ......24 Delays ......40 Changing Prescaler (Timer0 to WDT) ......35 Effects of a Reset ......44 Changing Prescaler (WDT to Timer0) ......35 Equations ......40 Doing an A/D Conversion ......42 Faster Conversion - Lower Resolution Trade-off ...... 43 I/O Programming ......30 Flowchart of A/D Operation ......45 Indirect Addressing ......24 Initializing PORTA ......25 Internal Sampling Switch (Rss) Impedence ......40 Initializing PORTB ......27 Minimum Charging Time ......40 Saving STATUS and W Registers in RAM ......64 Operation During Sleep ......44 Sampling Requirements ......40 Computed GOTO ......23 Source Impedence ......40 Configuration Bits ......47 Time Delays ......40 Transfer Function .......45 CP1 bit ......48 Absolute Maximum Ratings ......89, 111, 135 **AC Characteristics** PIC16C710 ......101 DC bit ......17 PIC16C711 ......101 DC Characteristics ...... 147 ADCON0 Register ......37 PIC16C710 ...... 90, 101 ADCON1 ......37 PIC16C711 ...... 90, 101 ADCON1 Register ......14, 37 PIC16C715 ...... 113, 125 ADCS0 bit ......37 Development Tools ......85 Diagrams - See Block Diagrams ADIF bit ......21, 37 Digit Carry bit ......7 Direct Addressing ......24 ADRES Register ...... 15, 37, 39 Ε ALU ......7 Application Notes **Electrical Characteristics** AN552 ......27 PIC16C710 ......89 PIC16C711 ......89 AN607, Power-up Trouble Shooting ......53 PIC16C715 ...... 111 External Brown-out Protection Circuit ......60 Architecture Harvard ......7 External Power-on Reset Circuit ......60 Overview 7 F von Neumann ......7 Family of Devices MPASM Assembler ......86 PIC16C71X ......4 В **Block Diagrams** FSR Register ...... 15, 16, 24 Analog Input Model ......40 Fuzzy Logic Dev. System (fuzzyTECH®-MP) ......87 PIC16C71X ......8 RA4/T0CKI Pin ......25 RB3:RB0 Port Pins ......27 GO/DONE bit ......37

**NOTES:**