Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc715t-04-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | General Description                                                     |      |

|-------|-------------------------------------------------------------------------|------|

| 2.0   | PIC16C71X Device Varieties                                              | 5    |

| 3.0   | Architectural Overview                                                  |      |

| 4.0   | Memory Organization                                                     | . 11 |

| 5.0   | I/O Ports                                                               | . 25 |

| 6.0   | Timer0 Module                                                           | . 31 |

| 7.0   | Analog-to-Digital Converter (A/D) Module                                | . 37 |

| 8.0   | Special Features of the CPU                                             | . 47 |

| 9.0   | Instruction Set Summary                                                 | . 69 |

| 10.0  | Development Support                                                     | . 85 |

| 11.0  | Electrical Characteristics for PIC16C710 and PIC16C711                  |      |

| 12.0  | DC and AC Characteristics Graphs and Tables for PIC16C710 and PIC16C711 | 101  |

| 13.0  | Electrical Characteristics for PIC16C715                                |      |

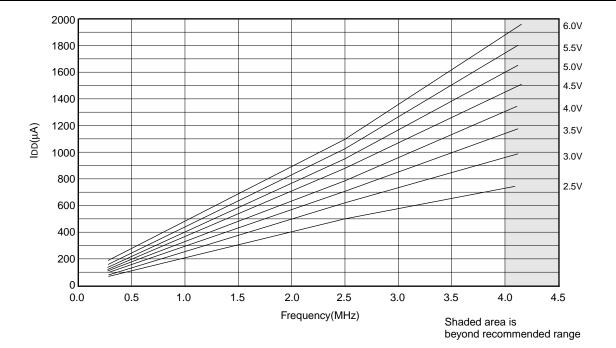

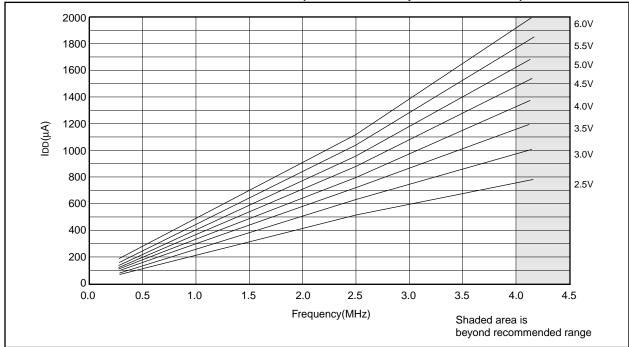

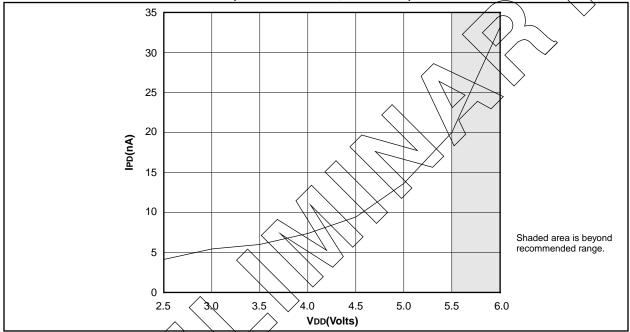

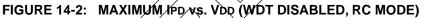

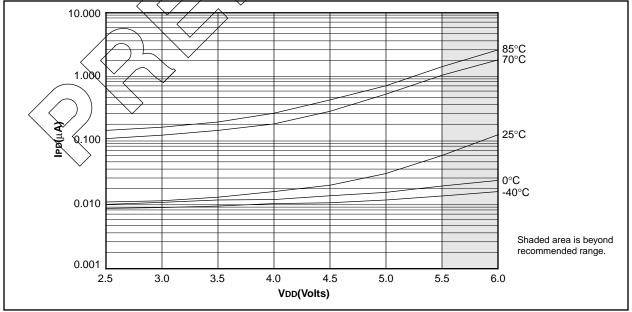

| 14.0  | DC and AC Characteristics Graphs and Tables for PIC16C715               |      |

| 15.0  | Electrical Characteristics for PIC16C71                                 | 135  |

| 16.0  | DC and AC Characteristics Graphs and Tables for PIC16C71                | 147  |

| 17.0  | Packaging Information                                                   | 155  |

| Appen | dix A:                                                                  | 161  |

|       | dix B: Compatibility                                                    |      |

| Appen | dix C: What's New                                                       | 162  |

|       | dix D: What's Changed                                                   |      |

|       | -                                                                       |      |

| PIC16 | C71X Product Identification System                                      | 173  |

|       | ·                                                                       |      |

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

| Address              | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR, PER | Value on all<br>other resets<br>(3) |

|----------------------|--------|--------------------|--------------------|---------------|---------------|----------------|-----------------|---------------|-----------|-------------------------------|-------------------------------------|

| Bank 1               |        | •                  |                    |               |               |                |                 |               |           | -                             |                                     |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location      | uses conter   | ts of FSR to  | address data   | a memory (n     | ot a physical | register) | 0000 0000                     | 0000 0000                           |

| 81h                  | OPTION | RBPU               | INTEDG             | TOCS          | TOSE          | PSA            | PS2             | PS1           | PS0       | 1111 1111                     | 1111 1111                           |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)      | Least Signif  | icant Byte    |                |                 |               |           | 0000 0000                     | 0000 0000                           |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO            | PD             | Z               | DC            | С         | 0001 1xxx                     | 000q quuu                           |

| 84h <sup>(1)</sup>   | FSR    | Indirect dat       | a memory ac        | ldress pointe | er            |                |                 |               |           | xxxx xxxx                     | uuuu uuuu                           |

| 85h                  | TRISA  | -                  | -                  | PORTA Dat     | a Direction F | Register       |                 |               |           | 11 1111                       | 11 1111                             |

| 86h                  | TRISB  | PORTB Da           | ta Direction F     | Register      |               |                |                 |               |           | 1111 1111                     | 1111 1111                           |

| 87h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 88h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 89h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | —                                   |

| 8Ah <sup>(1,2)</sup> | PCLATH | —                  | _                  | —             | Write Buffe   | r for the uppe | er 5 bits of th | e PC          |           | 0 0000                        | 0 0000                              |

| 8Bh <b>(1)</b>       | INTCON | GIE                | PEIE               | TOIE          | INTE          | RBIE           | TOIF            | INTF          | RBIF      | 0000 000x                     | 0000 000u                           |

| 8Ch                  | PIE1   | —                  | ADIE               | —             | —             | —              | —               | —             | —         | -0                            | -0                                  |

| 8Dh                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | —                             | _                                   |

| 8Eh                  | PCON   | MPEEN              | —                  | —             | —             | —              | PER             | POR           | BOR       | u1qq                          | u1uu                                |

| 8Fh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 90h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 91h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 92h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 93h                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 94h                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | —                                   |

| 95h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 96h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 97h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 98h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 99h                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Ah                  |        | Unimpleme          | nted               |               |               |                |                 |               |           |                               |                                     |

| 9Bh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | _                                   |

| 9Ch                  | —      | Unimpleme          | nted               |               |               |                |                 |               |           | -                             | —                                   |

| 9Dh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           |                               | _                                   |

| 9Eh                  | _      | Unimpleme          | nted               |               |               |                |                 |               |           | _                             | _                                   |

| 9Fh                  | ADCON1 | —                  | _                  | —             | —             | —              | -               | PCFG1         | PCFG0     | 00                            | 00                                  |

## TABLE 4-2: PIC16C715 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C715, always maintain these bits clear.

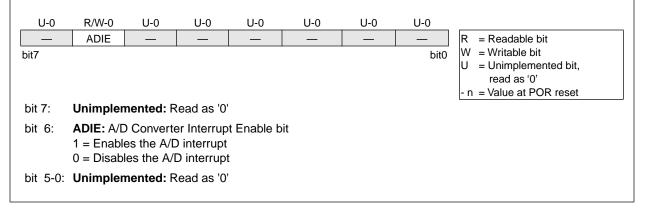

### 4.2.2.4 PIE1 REGISTER

## Applicable Devices 710 71 711 715

This register contains the individual enable bits for the Peripheral interrupts.

## FIGURE 4-10: PIE1 REGISTER (ADDRESS 8Ch)

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

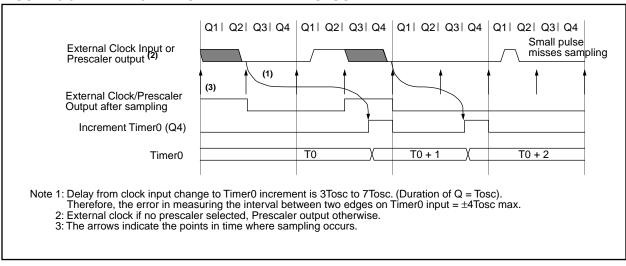

## 6.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

## TABLE 8-3:CERAMIC RESONATORS,<br/>PIC16C710/711/715

| Ranges Tested: |                                             |                                         |                                         |  |  |  |

|----------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode           | Freq                                        | OSC1                                    | OSC2                                    |  |  |  |

| XT             | 455 kHz<br>2.0 MHz<br>4.0 MHz               | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS             | 8.0 MHz<br>16.0 MHz                         | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |

|                | <b>se values are f</b><br>es at bottom of p | <b>ior design guidar</b><br>bage.       | nce only. See                           |  |  |  |

| Resonator      | rs Used:                                    |                                         |                                         |  |  |  |

| 455 kHz        | Panasonic E                                 | FO-A455K04B                             | ± 0.3%                                  |  |  |  |

| 2.0 MHz        | Murata Erie (                               | CSA2.00MG                               | ± 0.5%                                  |  |  |  |

| 4.0 MHz        | Murata Erie (                               | CSA4.00MG                               | ± 0.5%                                  |  |  |  |

| 8.0 MHz        | 0 MHz Murata Erie CSA8.00MT ± 0.5%          |                                         |                                         |  |  |  |

| 16.0 MHz       | Murata Erie CSA16.00MX ± 0.5%               |                                         |                                         |  |  |  |

| All reso       | onators used did                            | d not have built-in                     | capacitors.                             |  |  |  |

# TABLE 8-4:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR,<br/>PIC16C710/711/715

| Osc Type                                      | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |

|-----------------------------------------------|-----------------|------------------|------------------|--|--|--|--|

| LP                                            | 32 kHz          | 33 pF            | 33 pF            |  |  |  |  |

|                                               | 200 kHz         | 15 pF            | 15 pF            |  |  |  |  |

| XT                                            | 200 kHz         | 47-68 pF         | 47-68 pF         |  |  |  |  |

|                                               | 1 MHz           | 15 pF            | 15 pF            |  |  |  |  |

|                                               | 4 MHz           | 15 pF            | 15 pF            |  |  |  |  |

| HS                                            | 4 MHz           | 15 pF            | 15 pF            |  |  |  |  |

|                                               | 8 MHz           | 15-33 pF         | 15-33 pF         |  |  |  |  |

|                                               | 20 MHz          | 15-33 pF         | 15-33 pF         |  |  |  |  |

| These values are far design guidenes only See |                 |                  |                  |  |  |  |  |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |              |  |  |  |  |

|---------------|------------------------|--------------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM     |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM     |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | $\pm$ 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM     |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM     |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM     |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested table.

2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. NOTES:

# PIC16C71X

| IORWF             | Inclusive                                                                 | e OR W v                    | with f                      |                  |  |  |

|-------------------|---------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------|--|--|

| Syntax:           | [ label ]                                                                 | IORWF                       | f,d                         |                  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$ | 27                          |                             |                  |  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ (dest)                                         |                             |                             |                  |  |  |

| Status Affected:  | Z                                                                         |                             |                             |                  |  |  |

| Encoding:         | 00                                                                        | 0100                        | dfff                        | ffff             |  |  |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>the W regi<br>placed bac                | is 0 the re<br>ster. If 'd' | esult is pla<br>is 1 the re | ced in           |  |  |

| Words:            | 1                                                                         |                             |                             |                  |  |  |

| Cycles:           | 1                                                                         |                             |                             |                  |  |  |

| Q Cycle Activity: | Q1                                                                        | Q2                          | Q3                          | Q4               |  |  |

|                   | Decode                                                                    | Read<br>register<br>'f'     | Process<br>data             | Write to<br>dest |  |  |

| Example           | IORWF                                                                     |                             | RESULT,                     | 0                |  |  |

|                   |                                                                           | struction<br>RESULT<br>W    |                             | -                |  |  |

|                   | After Inst                                                                |                             |                             | 3                |  |  |

| MOVLW             | Move Literal to W                   |                     |                 |               |  |  |

|-------------------|-------------------------------------|---------------------|-----------------|---------------|--|--|

| Syntax:           | [ label ]                           | MOVLW               | / k             |               |  |  |

| Operands:         | $0 \le k \le 25$                    | 55                  |                 |               |  |  |

| Operation:        | $k \to (W)$                         |                     |                 |               |  |  |

| Status Affected:  | None                                |                     |                 |               |  |  |

| Encoding:         | 11                                  | 00xx                | kkkk            | kkkk          |  |  |

| Description:      | The eight the register. The as 0's. |                     |                 |               |  |  |

| Words:            | 1                                   |                     |                 |               |  |  |

| Cycles:           | 1                                   |                     |                 |               |  |  |

| Q Cycle Activity: | Q1                                  | Q2                  | Q3              | Q4            |  |  |

|                   | Decode                              | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |

| Example           | MOVLW                               | 0x5A                |                 |               |  |  |

|                   | After Inst                          | ruction<br>W =      | 0x5A            |               |  |  |

| Move f                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [ label ]                                                                                                                                                                                                                                                                | MOVF                                                                                                                                                                                                                                                                                          | f,d                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Z                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00                                                                                                                                                                                                                                                                       | 1000                                                                                                                                                                                                                                                                                          | dfff                                                                                                                                                                                                                                                                                                                        | ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                                                                                                                                                                                                                       | Q2                                                                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                                                                                                          | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                                                                                                                                                                                                                   | Read<br>register<br>'f'                                                                                                                                                                                                                                                                       | Process<br>data                                                                                                                                                                                                                                                                                                             | Write to<br>dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| MOVF FSR, 0<br>After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                          | $\begin{bmatrix}  abel  \\ 0 \le f \le 12 \\ d \in [0,1] \\ (f) \to (des Z \\ \hline 00 \\ \hline Decode \\ a destinati \\ tus of d. If \\ ister. If d = \\ register f it \\ file registe \\ affected. \\ 1 \\ 1 \\ \hline Q1 \\ \hline Decode \\ \hline MOVF \\ After Inst \\ \end{bmatrix}$ | $\begin{bmatrix} label \\ \end{bmatrix} MOVF$ $0 \le f \le 127$ $d \in [0,1]$ $(f) \rightarrow (dest)$ $Z$ $\boxed{00} 1000$ The contents of reg<br>a destination depentus of d. If d = 0, destister. If d = 1, the deregister f itself. d = 1<br>file register since state affected. 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | $\begin{bmatrix} label \end{bmatrix} \text{ MOVF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (f) \rightarrow (dest) \\ Z \\ \hline 00 & 1000 & dfff \\ \hline The contents of register f is m a destination dependant upon tus of d. If d = 0, destination is ister. If d = 1, the destination is register f itself. d = 1 is useful to file register since status flag Z affected. 1 \\ 1 \\ Q1 & Q2 & Q3 \\ \hline Decode & Read & Process \\ data \\ \hline MOVF & FSR, 0 \\ \hline After Instruction \\ W = value in FSR register \\ \end{bmatrix}$ |  |

| MOVWF             | Move W                | to f                    |                  |                       |

|-------------------|-----------------------|-------------------------|------------------|-----------------------|

| Syntax:           | [ label ]             | MOVW                    | = f              |                       |

| Operands:         | $0 \le f \le 12$      | 27                      |                  |                       |

| Operation:        | $(W) \rightarrow (f)$ |                         |                  |                       |

| Status Affected:  | None                  |                         |                  |                       |

| Encoding:         | 00                    | 0000                    | lfff             | ffff                  |

| Description:      | Move data<br>'f'.     | from W r                | egister to       | register              |

| Words:            | 1                     |                         |                  |                       |

| Cycles:           | 1                     |                         |                  |                       |

| Q Cycle Activity: | Q1                    | Q2                      | Q3               | Q4                    |

|                   | Decode                | Read<br>register<br>'f' | Process<br>data  | Write<br>register 'f' |

| Example           | MOVWF                 | OPTIC                   | N_REG            |                       |

|                   | Before In             |                         |                  | _                     |

|                   |                       | OPTION<br>W             | = 0xFF<br>= 0x4F |                       |

|                   | After Inst            | ••                      | - 0741           |                       |

|                   |                       | OPTION                  |                  |                       |

|                   |                       | W                       | = 0x4F           | -                     |

| NOP               | No Operation |      |      |      |  |

|-------------------|--------------|------|------|------|--|

| Syntax:           | [ label ]    | NOP  |      |      |  |

| Operands:         | None         |      |      |      |  |

| Operation:        | No operation |      |      |      |  |

| Status Affected:  | None         |      |      |      |  |

| Encoding:         | 00           | 0000 | 0xx0 | 0000 |  |

| Description:      | No operat    | ion. |      |      |  |

| Words:            | 1            |      |      |      |  |

| Cycles:           | 1            |      |      |      |  |

| Q Cycle Activity: | Q1           | Q2   | Q3   | Q4   |  |

|                   | Decode       | NOP  | NOP  | NOP  |  |

| Example           | NOP          |      |      |      |  |

| RETFIE            | Return from Interrupt                                                                                                                                                      |        |                    |                    |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                                  | RETFIE |                    |                    |  |  |

| Operands:         | None                                                                                                                                                                       |        |                    |                    |  |  |

| Operation:        | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                    |        |                    |                    |  |  |

| Status Affected:  | None                                                                                                                                                                       |        |                    |                    |  |  |

| Encoding:         | 00                                                                                                                                                                         | 0000   | 0000               | 1001               |  |  |

| Monda             | and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |        |                    |                    |  |  |

| Words:            | 1                                                                                                                                                                          |        |                    |                    |  |  |

| Cycles:           | 2                                                                                                                                                                          |        |                    |                    |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                         | Q2     | Q3                 | Q4                 |  |  |

| 1st Cycle         | Decode                                                                                                                                                                     | NOP    | Set the<br>GIE bit | Pop from the Stack |  |  |

| 2nd Cycle         | NOP                                                                                                                                                                        | NOP    | NOP                | NOP                |  |  |

| Example           | RETFIE                                                                                                                                                                     |        |                    |                    |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                           | tion Reg                                       | gister                                               |                                         |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|

| Syntax:          | [ label ]                                                                                          | OPTION                                         | ١                                                    |                                         |

| Operands:        | None                                                                                               |                                                |                                                      |                                         |

| Operation:       | $(W)\toOF$                                                                                         | PTION                                          |                                                      |                                         |

| Status Affected: | None                                                                                               |                                                |                                                      |                                         |

| Encoding:        | 00                                                                                                 | 0000                                           | 0110                                                 | 0010                                    |

| Description:     | The conter<br>loaded in the<br>instruction<br>patibility with<br>Since OPT<br>register, the<br>it. | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |

| Words:           | 1                                                                                                  |                                                |                                                      |                                         |

| Cycles:          | 1                                                                                                  |                                                |                                                      |                                         |

| Example          |                                                                                                    |                                                |                                                      |                                         |

|                  | To mainta<br>with futur<br>not use th                                                              | re PIC16                                       | CXX prod                                             |                                         |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                 | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                         |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:           | [label] RLF f,d                                                                                                                                                                                             | Syntax:           | [label] RRF f,d                                                                                                                                                                                                                                                      |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                          | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                           |  |  |

| Operation:        | See description below                                                                                                                                                                                       | Operation:        | See description below                                                                                                                                                                                                                                                |  |  |

| Status Affected:  | С                                                                                                                                                                                                           | Status Affected:  | С                                                                                                                                                                                                                                                                    |  |  |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                           | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                    |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.                                                         |  |  |

|                   |                                                                                                                                                                                                             |                   | C Register f                                                                                                                                                                                                                                                         |  |  |

| Words:            | 1                                                                                                                                                                                                           | Words:            | 1                                                                                                                                                                                                                                                                    |  |  |

| Cycles:           | 1                                                                                                                                                                                                           | Cycles:           | 1                                                                                                                                                                                                                                                                    |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                          |  |  |

|                   | Decode Read register data Write to dest                                                                                                                                                                     |                   | Decode Read register 'f' Vite to dest                                                                                                                                                                                                                                |  |  |

| Example           | RLF REG1,0                                                                                                                                                                                                  | Example           | RRF REG1,0                                                                                                                                                                                                                                                           |  |  |

|                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                        |                   | Before Instruction       REG1       =       1110       0110         C       =       0       -         After Instruction       -       -       -         REG1       =       1110       0110         W       =       0111       0011         C       =       0       - |  |  |

# PIC16C71X

## SLEEP

| [ label ]                                                                                                                                                              | SLEEF                                                                                                                                                                                                                                             | )                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| None                                                                                                                                                                   |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                        | ,                                                                                                                                                                                                                                                 | ller,                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TO, PD                                                                                                                                                                 |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 00                                                                                                                                                                     | 0000                                                                                                                                                                                                                                              | 0110                                                                                                                                                                                                                                                                                                                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1                                                                                                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Q1                                                                                                                                                                     | Q2                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                       | Q4                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Decode                                                                                                                                                                 | NOP                                                                                                                                                                                                                                               | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SLEEP                                                                                                                                                                  |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                        | None<br>$00h \rightarrow W$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watch<br>caler are<br>The proce<br>mode with<br>See Section<br>1<br>1<br>Q1<br>Decode | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT \text{ prescal}$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000<br>The power-down st<br>cleared. Time-out s<br>set. Watchdog Time<br>caler are cleared.<br>The processor is pr<br>mode with the oscill<br>See Section 8.8 for<br>1<br>1<br>Q1  Q2<br>Decode NOP | None<br>$00h \rightarrow WDT,$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow TO,$<br>$0 \rightarrow PD$<br>TO, PD<br>00  0000  0110<br>The power-down status bit, F<br>cleared. Time-out status bit, Set. Watchdog Timer and its<br>caler are cleared.<br>The processor is put into SLI<br>mode with the oscillator stop<br>See Section 8.8 for more det<br>1<br>1<br>Q1 Q2 Q3<br>Decode NOP NOP |  |

| SUBLW             | Subtract              | W from                                                                                                                               | Literal                         |  |  |  |  |